# Non-Interactive Cryptography in the RAM Model of Computation

DANIEL APON\* XIONG FAN\* JONATHAN KATZ\* FENG-HAO LIU\* ELAINE SHI\* HONG-SHENG ZHOU<sup>†</sup>

#### Abstract

Using recently developed techniques for program obfuscation, we show several constructions of non-interactive cryptosystems in the random-access machine (RAM) model of computation that are asymptotically more efficient than what would be obtained using generic RAM-tocircuit compilation. In particular, let T denote the running time and n the memory size of a RAM program. We show that using differing-inputs obfuscation, functional encryption for arbitrary RAM programs can be achieved with evaluation time  $\tilde{O}(T+n)$ .

Additionally, we provide a number of RAM-model constructions assuming the stronger notion of virtual black-box (VBB) obfuscation. We view these as initial feasibility results and leave instantiating similar protocols from weaker assumptions for future work. Specifically, using VBB obfuscation we show how to construct RAM-model functional encryption with function privacy, fully homomorphic encryption, and stateful, privacy-preserving verifiable computation in the memory-delegation model.

**Keywords.** random access machine; program obfuscation; functional encryption; fully homomorphic encryption; verifiable computation

## 1 Introduction

Most cryptographic feasibility results that apply to arbitrary (polynomial-time computable) functions begin by modeling the function of interest as a polynomial-size *circuit*. In contrast, most real-life computations are expressed in terms of programs working on a *von Neumann architecture*, which resembles the *random-access machine* (RAM) model of computation. Working with a circuit-based model of computation can reduce the efficiency of cryptographic constructions relative to their non-cryptographic counterparts. In particular, the running time T of a RAM program can be sublinear in the length n of its memory array D, whereas the circuit corresponding to this program (assuming the function it computes is non-trivial) must have size at least n. Even when  $T = \Omega(n)$ , generic RAM-to-circuit compilation [41] results in a circuit of size O(nT), a blowup compared to the original running time T. Moreover, RAM programs may run in a different number of steps on different inputs, while circuits must run in the worst-case time on all inputs.

To overcome the drawbacks of using a circuit-based representation, several recent works have investigated cryptography based on alternative models of computation [31, 6, 7, 27, 15, 9, 36]. In particular, the RAM model has attracted considerable attention, and a flurry of recent works have demonstrated the feasibility of constructing SNARKs [6, 7, 9], verifiable computation (without privacy) [6, 7, 15, 9], attribute-based encryption [26], and secure multi-party computation [31, 36] in the RAM model.

<sup>\*</sup>Dept. of Computer Science, University of Maryland.

<sup>&</sup>lt;sup>†</sup>Dept. of Computer Science, Virginia Commonwealth University.

This line of research has left open the question of how to evaluate RAM programs *non-interactively* over encrypted data; this is explicitly mentioned as an open question by Goldwasser et al. [26]. What makes this problem challenging is the inherent tension arising from (1) the need for data to remain encrypted, and (2) the need for the evaluator to securely "decrypt" intermediate memory addresses during the evaluation. Relying on recently developed tools for program obfuscation [20, 14, 4], we show constructions for several cryptographic tasks related to this goal. We summarize our results, as well as our techniques, below.

#### 1.1 Functional Encryption in the RAM Model

In a functional encryption (FE) scheme [10], roughly speaking, secret keys correspond to functions; a user in possession of a ciphertext ct = Enc(x) and a secret key  $sk_f$  for a function f can compute f(x) but nothing else about x. In most prior work, the time required to compute f(x) depends on the circuit size of f. Here, we explore constructions whose complexity depends instead on the time to compute f in the RAM model. (We focus on indistinguishability-based security, though techniques from De Caro et al. [19] could be used to achieve simulation-based security.)

We identify a RAM program with a memory array D; the program takes an input x, reads/writes data from/to D, and eventually outputs a result. (The function computed by the program is stored in the initial portion of D.) Relying on differing-inputs obfuscation<sup>1</sup> (di $\mathcal{O}$ ) [2], we show a construction of functional encryption for RAM programs in which the evaluation time for a RAM program that runs in time T and uses memory of size n is<sup>2</sup>  $\tilde{O}(T + n)$  (omitting  $poly(\lambda)$  terms for simplicity). Our scheme imposes no *a priori* bounds on T or n.

**Techniques.** We describe the high-level intuition of our construction. Given a RAM program specified by its memory array D, we first use standard oblivious-RAM techniques to compile this into a functionally equivalent program in which memory-access patterns are independent of the input. Both the input x and the CPU states will be encrypted using a fully homomorphic encryption (FHE) scheme. This way, the evaluator can homomorphically evaluate every step of the next-instruction circuit, obtaining new (encrypted) CPU states, (encrypted) memory addresses, and (encrypted) values to write to memory. The missing ingredient is that the evaluator must obtain values of the next memory addresses to read and write *in the clear*. Our idea is to obfuscate (using di $\mathcal{O}$ ) homomorphic evaluation of the next-instruction function, followed by decryption of the needed memory addresses. The evaluator can use this obfuscated function to generate the memory addresses, one-by-one, without learning any additional information.

Intuitively, the above suffices as long as the evaluator behaves honestly. To prevent a dishonst evaluator from feeding arbitrary inputs to the obfuscated program and learning additional information, the obfuscated next-instruction circuit at time step  $\tau$  will check that its inputs represent results from an honest execution of the previous  $\tau - 1$  steps. To achieve this we use a succinct proof—constructed using the idea of proof-carrying data (PCD) [9] combined with a Merkle-tree construction to verify correctness of memory accesses—to verify that all previous steps of the evaluation were carried out correctly. Getting this high-level idea to work is non-trivial. One obstacle is circular dependence: the obfuscated circuit must include a PCD verifier to check the legitimacy of the inputs before evaluation; on the other hand, the PCD's statement includes the requirement that the obfuscated circuit itself was evaluated correctly in the previous step. To break this circular

<sup>&</sup>lt;sup>1</sup>Although Garg et al. [21] show the implausibility of differing-inputs obfuscation in the presence of general auxiliary inputs, there is no evidence that their attack on the differing-inputs property applies to the specific circuits considered in our construction. In any case, we discuss further below how our construction can be adapted to be based on indistinguishability obfuscation.

<sup>&</sup>lt;sup>2</sup>Throughout the paper,  $\tilde{O}(f(\cdot))$  means  $O(f(\cdot) \cdot \mathsf{polylog}(f(\cdot)))$ .

dependence, we have the obfuscated circuit output a signature for the next-memory addresses it outputs. (For technical reasons, this signature must be deterministic.)

Aside from resolving the circular dependence challenge, other technical challenges also arise in our constructions. For example, we rely on the double-encryption and NIZK trick [20, 39, 37] to ensure some form of non-malleability property in our construction. We further borrow ideas from the randomized Functional Encryption construction by Goyal et al. [33] to handle the randomness of ORAM.

Using indistinguishability obfuscation. We can adapt our construction so that it is based on the (presumably) weaker assumption of indistinguishability obfuscation  $(i\mathcal{O})$  [20]. Instead of using PCD proofs and Merkle trees, the obfuscated next-instruction circuit now takes the entire previous evaluation trace as input and checks its correctness. The resulting construction, described in Appendix D, has evaluation time  $\tilde{O}((T+n)^2)$ . Although this does not offer any asymptotic improvement over what can be obtained by converting the RAM to a circuit, it still has the advantage of having *input-specific* running time as defined by Goldwasser et al. for the case of programs specified as Turing machines [26, 27]. (This leaks information, but may be acceptable in some scenarios.) In comparison with the results of Goldwasser et al. [26], our  $i\mathcal{O}$ -based construction does not rely on non-falsifiable assumptions. We also remark that working in the RAM model is inherently more challenging precisely because of the random memory accesses. It was previously unknown how to construct a functional encryption scheme in the RAM model, even based on non-falsifiable assumptions or in idealized models (without converting the RAM to a circuit).

#### 1.2 Additional Results Using Virtual Black-Box Obfuscation

We view the preceding results as the main contributions of this paper. For completeness, however, we also show how to realize additional tasks in the RAM model based on the stronger notion of virtual black-box (VBB) obfuscation. Although VBB obfuscation is known not to exist for general functions, recent results have demonstrated the feasibility of constructing general-purpose VBB obfuscators in certain idealized models [14, 4] or in the real-world for restricted functions [3]. VBB obfuscation can also be realized using hardware tokens [14, 16, 28]. Our results relying on VBB obfuscation are subject to the same caveats as in those works, and can be viewed as initial feasibility results secure against "generic" or "algebraic-only" attacks. A natural direction of future research is to explore whether similar results can be achieved under weaker assumptions, akin perhaps to our  $i\mathcal{O}$ - or di $\mathcal{O}$ -based FE-RAM schemes.

Functional encryption with function privacy. Using VBB obfuscation we can add function privacy to our functional encryption scheme while maintaining evaluation time  $\tilde{O}(T+n)$ .

Fully homomorphic encryption for RAM programs. A fully homomorphic encryption (FHE) scheme provides a public evaluation method that enables anyone holding a ciphertext ct = Enc(x) to compute a ciphertext Enc(f(x)) for any desired function f. In existing schemes, the complexity of this evaluation procedure depends on the size of the circuit computing f. Here, we give constructions in which the complexity instead depends on the time to compute f on a RAM. Specifically, if f can be computed by a RAM program in T time steps using memory of size n, then evaluation takes time  $\tilde{O}(T+n)$  (again omitting terms that depend on the security parameter). As in the case of our functional encryption schemes, our FHE scheme imposes no a priori bounds on T or n.

Similar to the Turing machine FHE of [26], this provides the option of FHE with input-specific run-time, but also has the additional property of random access to working memory, which can provide polynomial speed-ups for specific algorithms.

Stateful verifiable computation of RAM programs, with privacy. In a stateful verifiablecomputation (VC) scheme, a client outsources some data D to an untrusted server. The client then makes a series of queries to the server. The queries can include *updates* to the data (i.e., inserting, deleting, or modifying entries in the database); other queries require the server to compute some function over the current contents of the data. The challenge is to guarantee the *integrity* of the computation performed by the server. We require *privacy* of the outsourced data as well. (Prior work on verifiable computation in the RAM model [6, 7, 15, 9] does not achieve privacy.) To make the problem interesting, the client should perform asymptotically less work per function evaluation than the time to compute the function on its own, locally. In prior work, efficiency was measured in terms of the circuit size of the function(s) being computed. Here, we focus on the time complexity of the function(s) in the RAM model.

We show that a stateful VC scheme with nearly optimal online performance: for a function that can be implemented by a RAM program in time T using memory of size n, the server's online cost for computing the function is  $\tilde{O}(T)$ , and the client's overhead for verification is linear in the input and output lengths only. (Once again, we omit dependence on the security parameter.)

## 2 Definitions

We present some definitions specific to our work, and refer the reader to Appendix A for general background and various additional building blocks.

#### 2.1 The RAM Model of Computation

We use the following notation to denote parameters associated with a random access machine (RAM): NEXTINS is the next instruction circuit; n is the maximum number of memory words consumed by the RAM;  $\ell$  is the bit length of each memory word; and |cpustate| is the bit length of the cpustate.

A random access machine  $\mathsf{RAM} := D$  is defined by initial memory array  $D \in \{0, 1\}^{n\ell}$ . Throughout the paper, we assume that a  $\mathsf{RAM}$ 's initial  $\mathsf{cpustate}_0 := 0$ . We assume that the  $\mathsf{RAM}$ 's program f is stored in the memory array D, and that the NEXTINS circuit is independent of the program text size. We use the following notation to denote a RAM's execution.

| waddr <sub>t</sub> | write address at time $t$ | $data_t$     | memory word to write at time $t$ |

|--------------------|---------------------------|--------------|----------------------------------|

| raddr <sub>t</sub> | read address at time $t$  | $fetched_t$  | memory word fetched at time $t$  |

| x                  | input of RAM              | $cpustate_t$ | CPU state at time $t$            |

| y                  | output of RAM             | T            | RAM's execution time             |

Based on this notation, our RAM's execution can be described as below. Without loss of generality, we assume  $cpustate_0 := 0$  throughout the paper.

$\begin{array}{l} \mathsf{fetched}_0 = x \\ \mathrm{For} \ t = 1, 2, \dots : \\ (\mathsf{data}_t, \mathsf{waddr}_t, \mathsf{raddr}_t, \mathsf{cpustate}_t) := \mathrm{NEXTINS} \left( \mathsf{fetched}_{t-1}, \mathsf{cpustate}_{t-1} \right) \\ \mathsf{fetched}_t := D[\mathsf{raddr}_t] \\ D[\mathsf{waddr}_t] := \mathsf{data}_t \end{array}$

For simplicity, we adopt the convention that in the final step t = T of the execution, the NEXTINS circuit additionally outputs the final output value y. This assumes that the RAM always

runs for exactly T steps on all inputs x. One can also allow input-specific run-time on a perapplication basis, under the condition that this information will leak to an adversary in any of our cryptosystems, by modifying the above in the natural way.

We use the notation  $y := \mathsf{RAM}(x)$  to denote that executing RAM on input x yields outcome y. We use  $\{(\mathsf{waddr}_t, \mathsf{raddr}_t)\}_{1 \le t \le T} := \mathsf{addresses}(\mathsf{RAM}, x)$  to represent the memory address sequence (both read and write addresses) accessed during the execution of RAM.

## 2.2 Oblivious RAM

An Oblivious RAM (ORAM) is a special random-access machine with a special, deterministic next instruction circuit that takes in a random seed rk:

$(data_t, waddr_t, raddr_t, cpustate_t) := NEXTINS (fetched_{t-1}, cpustate_{t-1}, rk)$

Informally, an adversary who can observe the memory address sequence emitted during the ORAM's execution cannot gain any additional information about the input to the ORAM. Here we use the notation  $y := \text{ORAM}[\mathsf{rk}](x)$  denotes the outcome of the ORAM on input x and random seed  $\mathsf{rk}$ . We use  $\{(\mathsf{waddr}_t, \mathsf{raddr}_t)\}_{1 \le t \le T_{\mathsf{ORAM}}} := \mathsf{addresses}(\mathsf{ORAM}, x; \mathsf{rk})$  to represent the memory address sequence (both read and write addresses) accessed during the execution of ORAM on input x and random seed  $\mathsf{rk}$ .

As mentioned earlier, we assume that the initial CPU state of any RAM or ORAM is  $\vec{0}$ . Therefore, a RAM can be characterized by its initial memory array D. Any (non-oblivious) RAM := D can be compiled into an equivalent oblivious RAM, denoted ORAM :=  $D||\vec{0}$ . In particular, the ORAM's initial memory array is just the RAM's initial memory array padded to the desired number of words, and the desired bit-length for each memory word, which we denote with the short-hand  $D||\vec{0}$ . We stress that the ORAM has different parameters, including memory word size, number of memory words, and CPU state size than the original RAM. Further, note that the ORAM also has a different next instruction circuit than that of the RAM.

**Definition 2.1** (Secure ORAM). We say  $ORAM := D || \vec{0}$  is a secure oblivious RAM for RAM := D, if the following properties are satisfied:

- Correctness. For any input x, for any rk, it holds that ORAM[rk](x) = RAM(x).

- Address simulatability<sup>3</sup>. The security of ORAM states that there exists a simulator Sim such that no PPT adversary can distinguish between a real address sequence (obtained by executing ORAM on input x over a randomly-chosen seed rk) and a simulated address sequence. We assume that both A and Sim know the parameters of the RAM and ORAM and their next instruction circuits. Note that the A does not see the random seed rk that used by the ORAM's next instruction circuit.

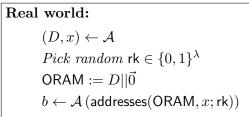

Simulated world:  $(D, x) \leftarrow \mathcal{A}$  $b \leftarrow \mathcal{A}(Sim())$

$<sup>^{3}</sup>$ Our security definition does not stipulate the encryption of memory contents since memory contents will be separately encrypted later in our construction.

• Overhead. The new ORAM has number of memory words  $n_{\mathsf{ORAM}} = \tilde{O}(n)$ ; word bit-length  $\ell_{\mathsf{ORAM}} = \max(\ell, c \log T)$  for some appropriate constant c > 2, and where T is the original RAM's maximum run-time; bit-length of CPU state  $|\mathsf{cpustate}_{\mathsf{ORAM}}| = O(|\mathsf{cpustate}| + \lambda)$ ; and  $|\mathsf{NExtIns}_{\mathsf{ORAM}}| := O(|\mathsf{NExtIns}|) \cdot \mathsf{poly}(\lambda)$ . Additionally, the new ORAM runs in  $\tilde{O}(T + n)$  number of time steps if the original RAM runs in T number of time steps.

**Lemma 2.2** (Restatement of [25, 35, 42, 44, 23, 18]). Assuming the existence of PRF, then for any RAM := D, there exists a secure oblivious RAM ORAM :=  $D||\vec{0}$  with an appropriate next instruction circuit.

**Remark:** Prevent correlated randomness of multiple executions of the same ORAM. In our FE schemes, the same ORAM (defined by its initial memory array) will be used to evaluate multiple ciphertexts. In order for the addresses of these multiple executions of the same ORAM to be uncorrelated, we assume that the ORAM shuffles its entire memory prior to starting executing the logic. More specifically, our ORAM does the following:

- 1. **ORAM setup.** At the start of the its execution, the ORAM first shuffles the entire memory. In other words, the ORAM shuffles the original data array D and builds an ORAM data structure. This takes  $\tilde{O}(n)$  time, and explains the added  $\tilde{O}(n)$  run-time on top of T in our FE-RAM.

- 2. Execution. The ORAM then executes the logic of the original RAM, reading and writing data from and to the memory oblivious as needed.

Note also that in our construction, the seed  $\mathsf{rk}$  is generated pseudorandomly by computing  $\mathsf{PRF}(K,\mathsf{ct})$ ; this will ensure that each ciphertext  $\mathsf{ct}$  leads to a different seed, thus preventing correlated randomness of multiple executions.

## 2.3 Functional Encryption

**Syntax.** A functional encryption scheme for RAM programs (FE-RAM) consists of the following algorithms FE = FE.(Setup, KeyGen, Enc, Dec).

- Setup: FE.Setup $(1^{\lambda})$  is a PPT algorithm that takes as input a security parameter  $1^{\lambda}$  and outputs a pair of master public and secret keys (mpk, msk).

- Key Generation: FE.KeyGen(msk, RAM) is a PPT algorithm that takes as input the master secret key msk and a RAM program RAM and outputs a corresponding secret key  $sk_{RAM}$ .

- Encryption: FE.Enc(mpk, x) is a PPT algorithm that takes as input the master public key mpk and a message x and outputs a ciphertext ct.

- **Decryption:** FE.Dec( $sk_{RAM}$ , ct) is a deterministic algorithm that takes as input the secret key  $sk_{RAM}$  and a ciphertext ct = Enc(mpk, x) and outputs RAM(x).

**Definition 2.3** (Correctness). A functional encryption scheme FE is correct if for every  $\lambda \in \mathbb{N}$ , RAM, x,

$$\Pr\left[\begin{array}{c} (\mathsf{mpk},\mathsf{msk}) \leftarrow \mathsf{FE}.\mathsf{Setup}(1^{\lambda});\\ \mathsf{FE}.\mathsf{Dec}(\mathsf{FE}.\mathsf{KeyGen}(\mathsf{msk},\mathsf{RAM}),\mathsf{FE}.\mathsf{Enc}(\mathsf{mpk},x)) \neq \mathsf{RAM}(x) \end{array}\right] = \mathsf{negl}(\lambda)$$

where the probability is taken over the coins of FE.Setup, FE.KeyGen, and FE.Enc.

We consider both indistinguishability- and simulation-based notions of security for RAM-model functional encryption, following [10, 38]. See Appendix B for a full treatment. Here, we state the definition under which we prove security directly.

**Definition 2.4** (Selective Indistinguishability, Multiple-Key). Let FE be a functional encryption scheme for RAM programs computing a functionality class  $\mathcal{F}$ . For every PPT stateful adversary  $\mathcal{A}$ , consider the following experiment.

$\begin{aligned} \mathbf{Expt}_{\mathcal{A}}^{\text{selective}}(1^{\lambda}) \\ \hline 1: & (x_0, x_1) \leftarrow \mathcal{A}(1^{\lambda}); \\ 2: & (\text{mpk}, \text{msk}) \leftarrow \text{FE.Setup}(1^{\lambda}); \\ 3: & b \leftarrow \{0, 1\}; \\ 4: & \text{ct} \leftarrow \text{FE.Enc}(\text{mpk}, x_b); \\ 5: & b' \leftarrow \mathcal{A}^{\text{FE.KeyGen}(\text{msk}, \cdot)}(\text{mpk}, \text{ct}); \end{aligned}$

Define an adversary to be non-trivial if  $\mathsf{RAM}(x_0) = \mathsf{RAM}(x_1)$ , for every query  $\mathsf{RAM}$  made to the KeyGen oracle. We say that an FE-RAM scheme is selectively IND-secure if for all PPT stateful non-trivial adversaries  $\mathcal{A}$ , it holds that  $\Pr[b' = b] \leq \frac{1}{2} + \mathsf{negl}(\lambda)$  in the above experiment.

# 3 RAM-Model Functional Encryption from Differing-Inputs Obfuscation

## 3.1 Intuition

As mentioned earlier in the introduction, the main idea is to 1) homomorphically encrypt the input and the CPU state; and 2) create obfuscated next-instruction circuits that will emit next memory addresses to read and write. When a token is being generated for a RAM, the RAM is first converted into an ORAM. The ORAM's memory contents are initially not encrypted (since function privacy is not our goal here); however, contents newly written to memory will be homomorphically encrypted. As a result, data fetched from memory can be a cleartext or ciphertext, depending on whether the memory location has been written during the evaluation.

One key challenge is to secure against a malicious evaluator. For this reason, every obfuscated next instruction circuit must only yield output if the evaluator is behaving correctly. We therefore rely on Proof-Carrying-Data (PCD) [9] to ensure that all previous steps of the encrypted RAM evaluation are done correctly. Unfortunately, if done naively, a *circularity* issue arises:

- We must check a PCD proof inside the obfuscated next-instruction circuit before releasing any output; since otherwise an adversary can supply malicious inputs to the obfuscated nextinstruction circuit and learn additional information;

- The PCD proof must verify that the obfuscated next instruction circuit is evaluated correctly.

In order for us to fix the PCD verifier circuit to embed in the obfuscated next-instruction circuit, we must fix the PCD predicate first, which requires fixing the obfuscated next-instruction circuit first.

**Ideas.** To fix this problem, our idea is to have the obfuscated next instruction circuit additionally output a signature for the  $(raddr_{\tau}, waddr_{\tau})$  addresses it outputs. Therefore, in the PCD predicate, we simply need to verify that this signature is correct, instead of having the entire obfuscated next-instruction circuit in the PCD predicate.

However, to leverage the properties of  $d\mathcal{O}$  in our proof, this signature output by the  $d\mathcal{O}$  must be deterministic, such that at time step  $\tau$  of evaluating the ciphertext ct, there is one unique proof for a tuple (ct,  $\tau$ , raddr<sub> $\tau$ </sub>, waddr<sub> $\tau$ </sub>). To construct this signature, we borrow ideas from the NIZK construction of Sahai and Waters [40]. Although this scheme has only non-adaptive soundness, this suffices for our setting because the space of possible (valid) statements has polynomial size.

## 3.2 Construction

Notational convention. We explain our notational conventions below.

| var                                                          | double-encrypted ciphertext based on $cFHE$ , under public keys $hpk$    |

|--------------------------------------------------------------|--------------------------------------------------------------------------|

|                                                              | and $hpk'$ respectively                                                  |

| var                                                          | This variable (in particular $fetched_t$ ) is sometimes double-encrypted |

|                                                              | and sometimes in cleartext. Memory contents fetched during the           |

|                                                              | RAM's evaluation are in cleartext if this is the first time they are     |

|                                                              | accessed; otherwise, they are double-encrypted under $hpk$ and $hpk'$ .  |

| $\{var\} \text{ or } \{\overline{var}\} \text{ or } \{var\}$ | We use {} to denote either that the variable has a Merkle proof or a     |

|                                                              | PCD proof vouching for its correctness.                                  |

We introduce the notation  $\mathsf{cFHE}.\mathsf{Eval}_{hpk,hpk'}$  as a short-hand to express simultaneously evaluating two copies of the FHE ciphertexts, encrypted under hpk and hpk' respectively. Concretely, we use  $w = \mathsf{cFHE}.\mathsf{Eval}_{hpk,hpk'}(g(v))$  to denote the homomorphic evaluation of function  $g(\cdot)$  on double-encrypted ciphertext  $v = (c_v, c'_v)$  to obtain a new double-encrypted ciphertext  $w = (c_w, c'_w)$ , where  $c_v = \mathsf{cFHE}.\mathsf{Enc}(hpk, v)$  and  $c'_v = \mathsf{cFHE}.\mathsf{Enc}(hpk', v))$ , and  $c_w = \mathsf{cFHE}.\mathsf{Eval}(hpk, g(\cdot), c_v)$  and  $c'_w = \mathsf{cFHE}.\mathsf{Eval}(hpk', g(\cdot), c'_v)$ .

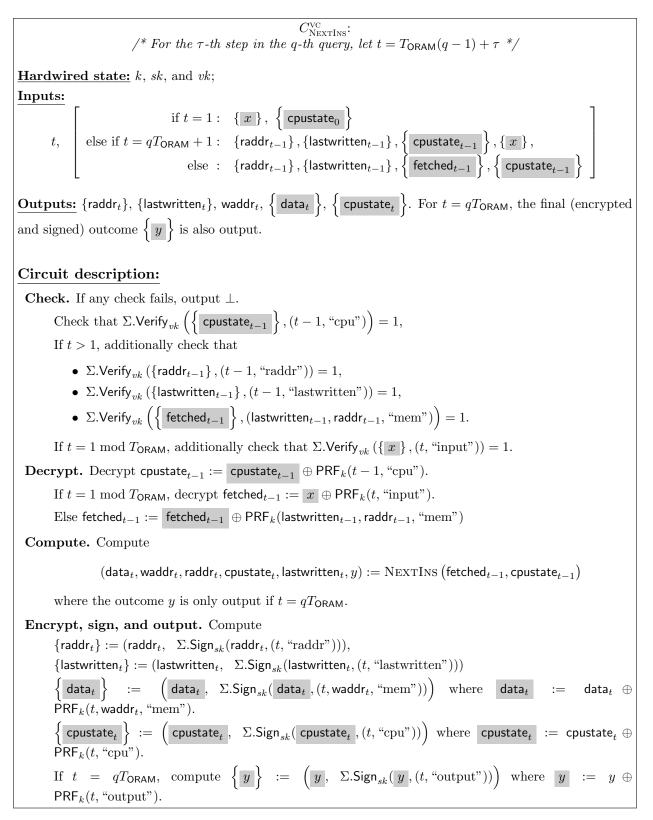

**Detailed construction.** We now describe our di $\mathcal{O}$ -based FE-RAM construction. Besides the differing-inputs obfuscation di $\mathcal{O}$ , we use an FHE scheme cFHE.(Gen, Enc, Dec, Eval), and a *simulation sound* NIZK scheme NIZK.(Setup, Prove, Verify). Further, we use a Proof-Carrying-Data system [9, 17] and collision-resistant Merkle hash tree construction.

- Setup. On input  $1^{\lambda}$ , compute  $(hpk, hsk) \leftarrow \mathsf{cFHE}.\mathsf{Gen}(1^{\lambda}), (hpk', hsk') \leftarrow \mathsf{cFHE}.\mathsf{Gen}(1^{\lambda}), crs \leftarrow \mathsf{NIZK}.\mathsf{Setup}(1^{\lambda}), and (\mathsf{rs}, \mathsf{vrs}) \leftarrow \mathsf{PCD}.\mathbb{G}(1^{\lambda}).$  Set public parameter  $\mathsf{mpk} := (hpk, hpk', crs, \mathsf{rs}, \mathsf{vrs}),$  and master secret key  $\mathsf{msk} := hsk$ .

- **Key Generation.** Convert the RAM into an ORAM, and denote ORAM := D. Compute the initial Merkle digest denoted  $digest_0$  of ORAM i.e.,

$digest_0 := MerkleDigest(D)$

### Circuit V

Hardwired: PRF key  $K_v$ .

**Inputs:** ct,  $\tau$ , raddr<sub> $\tau$ </sub>, waddr<sub> $\tau$ </sub>,  $\sigma_{\tau}$ .

Test if  $OWF(\sigma_{\tau}) = OWF(PRF(K_v, (ct, \tau, raddr_{\tau}, waddr_{\tau})))$  where OWF is a one-way function. Output accept if true, reject if false.

Figure 1: Circuit V to be obfuscated using  $i\mathcal{O}$ . This verifier circuit will be used as part of the predicate of the PCD system.

Circuit  $C_1$

**Hardwired:** mpk, hsk, PRF key K,  $K_v$ .

Inputs:  $ct = (x, \pi)$ .

**Outputs:** raddr<sub>1</sub>, waddr<sub>1</sub>,  $\sigma_1$ .

## **Computation:**

- 1. Check. Parse  $ct := (x, \pi)$ , and verify the NIZK  $\pi$ . If verification fails, output  $\bot$ .

- 2. Let  $\mathsf{rk} := \mathsf{PRF}(K, \mathsf{ct});$

- 3. Decrypt, compute, and output next addresses. Use hsk to decrypt to obtain fetched<sub>0</sub> := x; and then compute the circuit NEXTINS(fetched<sub>0</sub>,  $\vec{0}$ , rk), and output the addresses raddr<sub>1</sub>, waddr<sub>1</sub>. Further, output  $\sigma_1 := \mathsf{PRF}(K_v, (\mathsf{ct}, 1, \mathsf{raddr}_1, \mathsf{waddr}_1))$ .

Figure 2: Circuit  $C_1$  to be obfuscated using di $\mathcal{O}$ .

Sample random PRF key  $K \in \{0,1\}^{\lambda}$  to embed in the obfuscated next instruction circuits. Let K := (cFHE.Enc(hpk, K), cFHE.Enc(hpk', K)).

Circuit  $C_{\tau}$  for time steps  $\tau > 1$

**Hardwired:** initial digest<sub>0</sub>, mpk, hsk, PRF key K,  $K_v$ ,  $\tau$ . Inputs:

- { $\overline{\mathsf{fetched}}_{\tau-1}$ }, // carrying Merkle proofs w.r.t. digest<sub> $\tau-1$ </sub>

- {ct,  $\tau 1$ , digest<sub> $\tau 1$ </sub>, raddr<sub> $\tau 1$ </sub>, cpustate<sub> $\tau 1$ </sub>}, *// carrying a PCD proof*

**Outputs:** raddr<sub> $\tau$ </sub>, waddr<sub> $\tau$ </sub>,  $\sigma_{\tau}$  and optionally y

### **Computation:**

- 1. Check trace. If any of the checks fail, output  $\perp$ .

- Check that  $\{\mathsf{ct}, \tau 1, \mathsf{digest}_{\tau-1}, \mathsf{raddr}_{\tau-1}, \mathsf{cpustate}_{\tau-1}\}$  has a valid PCD proof.

- Check that { $\overline{\mathsf{fetched}}_{\tau-1}$ } is consistent with the Merkle  $\mathsf{digest}_{\tau-1}$  and  $\mathsf{raddr}_{\tau-1}$ .

- Check that the input  $\tau 1$  (when incremented) agrees with the hardwired  $\tau$ .

- 2. Let  $\mathsf{rk} := \mathsf{PRF}(K, \mathsf{ct});$

- 3. Decrypt, compute, and output next addresses. Use hsk to decrypt to obtain fetched<sub> $\tau-1$ </sub>, cpustate<sub> $\tau-1$ </sub>; then compute the circuit NEXTINS(fetched<sub> $\tau-1$ </sub>, cpustate<sub> $\tau-1$ </sub>; rk), and output the addresses raddr<sub> $\tau$ </sub> and waddr<sub> $\tau$ </sub>. Further, output  $\sigma_{\tau} := PRF(K_v, (ct, \tau, raddr_{\tau}, waddr_{\tau}))$ . If  $\tau = T_{ORAM}$ , i.e., this is the final step of the ORAM, also output the outcome y.

Figure 3: Circuit  $C_{\tau}$  to be obfuscated using di $\mathcal{O}$  for  $\tau > 1$ . Note that the PCD verifier algorithm for each time step may be different, therefore, the circuit for each time step is different.

Sample random PRF key  $K_v \in \{0,1\}^{\lambda}$ . Include  $i\mathcal{O}(V)$  in the token, where V is defined as in Figure 1.

Generate  $T_{\mathsf{ORAM}} = \tilde{O}(T)$  obfuscated circuits: 1) An obfuscated circuit  $\mathsf{di}\mathcal{O}(C_1)$  for the first step of evaluation, this circuit is of size  $\tilde{O}(T)$  as shown in Figure 2; and 2) an obfuscated circuit  $\mathsf{di}\mathcal{O}(C_{\tau})$  for each time step  $\tau > 1$  as described in Figure 3.

The token  $\mathsf{sk}_{\mathsf{ORAM}} := (\mathsf{digest}_0, K, i\mathcal{O}(V), \mathsf{di}\mathcal{O}(C_1), \mathsf{di}\mathcal{O}(C_2), \dots, \mathsf{di}\mathcal{O}(C_{T_{\mathsf{ORAM}}})).$

**Encryption.** Upon inputting the public parameter mpk and a message x, pick random  $\rho, \rho' \in \{0,1\}^{\lambda}$ , and compute  $c = \mathsf{cFHE}.\mathsf{Enc}(hpk, x; \rho), c' = \mathsf{cFHE}.\mathsf{Enc}(hpk', x; \rho')$ , then compute a NIZK (denoted  $\pi$ ) for the following statement parameterized by (c, c'):

$$\exists x, \rho, \rho' \text{ s.t. } (c = \mathsf{cFHE}.\mathsf{Enc}(hpk, x; \rho)) \land (c' = \mathsf{cFHE}.\mathsf{Enc}(hpk', x; \rho'))$$

The ciphertext  $ct := (x, \pi)$ , where x := (c, c').

# **Decryption.** Parse the token $\mathsf{sk}_{\mathsf{ORAM}} := (\mathsf{digest}_0, K, i\mathcal{O}(V), \mathsf{di}\mathcal{O}(C_1), \mathsf{di}\mathcal{O}(C_2), \dots, \mathsf{di}\mathcal{O}(C_{T_{\mathsf{ORAM}}})).$ Initialize $\overline{D} = D$ . Compute $\mathsf{rk} := \mathsf{cFHE}.\mathsf{Eval}_{hpk,hpk'} (\mathsf{PRF}(K, \mathsf{ct}))^4.$

Next, for  $\tau \in [T_{\mathsf{ORAM}}]$ ,

## • Perform homomorphic evaluation.

If  $\tau = 1$ , use homomorphic evaluation to obtain:

$$\left( \mathsf{data}_1 \,,\, \mathsf{cpustate}_1 \,\right) := \mathsf{cFHE}.\mathsf{Eval}_{hpk,hpk'}(\operatorname{NEXTINS}(x,\vec{0};\,\mathsf{rk}))$$

Else if  $\tau > 1$ , use the homomorphic evaluation to obtain:

$\left( \mathsf{data}_{\tau} \,,\, \mathsf{cpustate}_{\tau} \,\right) := \mathsf{cFHE}.\mathsf{Eval}_{hpk,hpk'}(\operatorname{NEXTINS}(\overline{\mathsf{fetched}}_{\tau-1},\, \mathsf{cpustate}_{\tau-1}\,;\,\mathsf{rk}\,))$

Here we *ignore* the encrypted addresses output by the homomorphic evaluations of the NEXTINS.

• Use di $\mathcal{O}$  to evaluate next addresses. If  $\tau = 1$ , compute

$$(\mathsf{waddr}_1, \mathsf{raddr}_1, \sigma_1) := \mathsf{di}\mathcal{O}(C_1)(\mathsf{ct})$$

Else if  $\tau > 1$ , compute

$(\mathsf{waddr}_{\tau},\mathsf{raddr}_{\tau},\sigma_{\tau}) := \mathsf{di}\mathcal{O}(C_{\tau})(\{\overline{\mathsf{fetched}}_{\tau-1}\},\{\mathsf{ct},\tau,\mathsf{digest}_{\tau-1},\mathsf{raddr}_{\tau-1},\mathsf{cpustate}_{\tau-1}\})$

If this is the final step of evaluation, an output y is additionally output from  $di\mathcal{O}(C_{\tau})$ .

• Perform memory read and write. The evaluator maintains a Merkle-tree authenticated data structure to efficiently compute the Merkle proofs for any memory location, and to efficiently update the Merkle digest upon memory writes. At this moment, the evaluator would update its Merkle-tree authenticated data structure to reflect the updated  $data_{\tau}$ , the updated cpustate<sub> $\tau$ </sub>, as well as the new time  $\tau$ . Suppose that the new Merkle digest is digest<sub> $\tau$ </sub>.

<sup>&</sup>lt;sup>4</sup>For technical reasons in the proof, here we assume that PRF is the circuit that first checks whether input K is a punctured key (which can be indicated by adding an indicator bit to the key), and if not, use real PRF evaluation algorithm; if so, use the punctured PRF evaluation algorithm.

Perform memory read and write:

$$\overline{\mathsf{fetched}}_{\tau} := \overline{D}[\mathsf{raddr}_{\tau}], \qquad \overline{D}[\mathsf{waddr}_{\tau}] := \mathsf{data}_{\tau}$$

Construct the Merkle proofs for  $\overline{\mathsf{fetched}}_{\tau}$  with respect to  $\mathsf{digest}_{\tau}$ . Let  $\{\overline{\mathsf{fetched}}_{\tau}\}$ , denote the version that has been attached with its Merkle proof w.r.t  $\mathsf{digest}_{\tau}$ .

• Compute a PCD proof for  $\{\mathsf{ct}, \tau, \mathsf{digest}_{\tau}, \mathsf{raddr}_{\tau}, \mathsf{cpustate}_{\tau}\}$ .

### 3.2.1 PCD Proof Computation Details

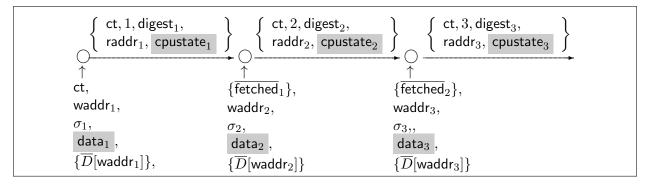

Figure 4: Our Path PCD system.

Effectively we have a Path PCD system as depicted in Figure 4. In every time step of the evaluation, a succinct proof is output vouching for the correctness of the terms { $ct, \tau, digest_{\tau}, raddr_{\tau}, cpustate_{\tau}$ } which will serve as input to the next step.

Statement for  $\tau > 1$ . At every node  $\tau > 1$ , the statement being verified is the conjunction of the following:

- The input has a valid PCD proof.

- The output ct agrees with the input ct.

- $i\mathcal{O}(V)(\mathsf{ct},\tau,\mathsf{raddr}_{\tau},\mathsf{waddr}_{\tau},\sigma_{\tau})=1.$

- { $\overline{\mathsf{fetched}}_{\tau-1}$ } has a Merkle proof consistent with  $\mathsf{digest}_{\tau-1}$  and  $\mathsf{raddr}_{\tau-1}$ .

- Values  $\mathsf{cpustate}_{\tau}$  and  $\mathsf{data}_{\tau}$  are correct homomorphic evaluations using the honest evaluator's algorithm based on  $\overline{\mathsf{fetched}}_{\tau-1}$ ,  $\mathsf{cpustate}_{\tau-1}$ , and  $\mathsf{rk} := \mathsf{cFHE}.\mathsf{Eval}_{hpk,hpk'}(K,\mathsf{ct})$ .

- The new digest digest<sub> $\tau$ </sub> is updated correctly from digest<sub> $\tau-1$ </sub>, based on { $\overline{D}$ [waddr<sub> $\tau$ </sub>]}, and the new value data<sub> $\tau$ </sub>.

Statement for  $\tau = 1$ . At node  $\tau = 1$ , the statement verified is the conjunction of the following:

- The output ct agrees with the local input ct.

- $i\mathcal{O}(V)(\mathsf{ct}, 1, \mathsf{raddr}_1, \mathsf{waddr}_1, \sigma_1) = 1.$

- Values  $\mathsf{cpustate}_1$  and  $\mathsf{data}_1$  are correct homomorphic evaluations using the honest evaluator's algorithm based on  $\mathsf{ct}$ ,  $\vec{0}$ , and  $\mathsf{rk} := \mathsf{cFHE}.\mathsf{Eval}_{hpk,hpk'}(K,\mathsf{ct}).$

- The new digest digest<sub>1</sub> is updated correctly from digest<sub>0</sub>, based on  $\{\overline{D}[waddr_1]\}$ , and the new value data<sub>1</sub>.

**Theorem 3.1.** Assuming that diO is a secure differing-inputs obfuscator, iO is a secure indistinguishability obfuscator, cFHE is a FHE scheme for circuits with perfect correctness and semantic security, NIZK is a simulation sound NIZK scheme, the PCD system is a proof of knowledge, the Merkle tree construction is collision-resistant, PRF is a correct and secure puncturable PRF, ORAM is secure as in Definition 2.1 and OWF is a one-way function, then the above FE-RAM construction is selectively IND-secure as in Definition 2.4.

The full proofs are deferred to Appendix C.

Lifting security. By a standard argument of complexity leveraging, we can achieve the (full, as opposed to selective) indistinguishability security from the selective security at a cost of stronger complexity assumptions. Then we can achieve a simulation-based security using the trapdoor circuit technique from the work of De Caro et al. [19], who showed how to construct a (selective/full) simulation secure FE from a (selective/full) indistinguishability secure one. Also, the construction supports multiple key queries. Thus, we are able to achieve the following corollary:

**Corollary 3.2** (Theorem 3.1 + (complexity leveraging) + [19]). Assume that diO is a secure differing-inputs obfuscator, iO is a secure indistinguishability obfuscator, cFHE is FHE scheme for all circuits with perfect correctness and semantic security, NIZK is a simulation sound NIZK scheme, the PCD system is a sound proof-of-knowledge system, the Merkle tree construction is collision-resistant, PRF is a correct and secure puncturable PRF, ORAM is secure as in Definition 2.1, and OWF is a one-way function. In addition, assume that these primitives remain secure when all polynomial-sized adversaries have sub-exponentially small advantages. Then the above FE-RAM can be made fully SIM-secure as defined in Definition B.1.

**Cost.** Our IND-secure construction achieves  $poly(\lambda)$  ciphertext size and  $O(n+T)poly(\lambda)$  evaluation time. For the simulation-secure setting, our cost is preserved (same as the IND-secure setting), for a scheme secure under a single key query. To support q key queries, the ciphertext size blows up by a factor of q due to the use of De Caro et al. 's compiler [19]. Again, recall that it has been shown that in the standard model, it is impossible to achieve fully SIM-secure FE with succinct ciphertexts [19]. In contrast, our IND-secure scheme can support unbounded polynomially many key queries without blowups in ciphertext size.

In the above, we assume that the underlying di $\mathcal{O}$  scheme has linear blowup. We note that for the weaker primitive of indistinguishable obfuscation, candidate  $i\mathcal{O}$  schemes with linear blowup have been proposed: Gordon et al. observe that for the construction of [20], the size of the obfuscated circuit has only linear blowup, i.e.  $|i\mathcal{O}(C)| = |C| \cdot \operatorname{poly}(\lambda)$ . Therefore, if we conjecture that the  $i\mathcal{O}$  scheme is also a secure di $\mathcal{O}$ , then it will also be linear blowup. Please also see Remark A.6 for more explanations.

# Acknowledgments

This research was funded by NSF under grant number CNS-1314857, by a Google Faculty Research Award, and by the US Army Research Laboratory and the UK Ministry of Defence under Agreement

Number W911NF-06-3-0001. The views and conclusions contained herein are those of the authors and should not be interpreted as representing the official policies, either expressed or implied, of the US Army Research Laboratory, the U.S. Government, the UK Ministry of Defense, or the UK Government. The US and UK Governments are authorized to reproduce and distribute reprints for Government purposes notwithstanding any copyright notation hereon.

## References

- Shweta Agrawal, Sergey Gorbunov, Vinod Vaikuntanathan, and Hoeteck Wee. Functional encryption: New perspectives and lower bounds. In *CRYPTO*, 2013. http://eprint.iacr. org/2012/468.

- [2] Prabhanjan Ananth, Dan Boneh, Sanjam Garg, Amit Sahai, and Mark Zhandry. Differinginputs obfuscation and applications. Cryptology ePrint Archive, Report 2013/689, 2013. http: //eprint.iacr.org/.

- [3] Boaz Barak, Nir Bitansky, Ran Canetti, Yael Tauman Kalai, Omer Paneth, and Amit Sahai. Obfuscation for evasive functions. In *TCC*, pages 26–51, 2014.

- [4] Boaz Barak, Sanjam Garg, Yael Tauman Kalai, Omer Paneth, and Amit Sahai. Protecting obfuscation against algebraic attacks. In EUROCRYPT, 2014. http://eprint.iacr.org/2013/631.

- [5] Boaz Barak, Oded Goldreich, Russell Impagliazzo, Steven Rudich, Amit Sahai, Salil P. Vadhan, and Ke Yang. On the (im)possibility of obfuscating programs. J. ACM, 59(2):6, 2012.

- [6] Eli Ben-Sasson, Alessandro Chiesa, Daniel Genkin, and Eran Tromer. Fast reductions from rams to delegatable succinct constraint satisfaction problems: extended abstract. In *Proceed*ings of the 4th conference on Innovations in Theoretical Computer Science, ITCS '13, pages 401–414, 2013.

- [7] Eli Ben-Sasson, Alessandro Chiesa, Daniel Genkin, Eran Tromer, and Madars Virza. Snarks for c: Verifying program executions succinctly and in zero knowledge. In *CRYPTO*, pages 90–108, 2013.

- [8] Nir Bitansky and Ran Canetti. On strong simulation and composable point obfuscation. In Tal Rabin, editor, Advances in Cryptology – CRYPTO 2010, volume 6223 of Lecture Notes in Computer Science, pages 520–537. Springer, August 2010.

- [9] Nir Bitansky, Ran Canetti, Alessandro Chiesa, and Eran Tromer. Recursive composition and bootstrapping for snarks and proof-carrying data. In *STOC*, 2013.

- [10] Dan Boneh, Amit Sahai, and Brent Waters. Functional encryption: Definitions and challenges. In TCC 2011: 8th Theory of Cryptography Conference, volume 6597 of Lecture Notes in Computer Science, pages 253–273. Springer, 2011.

- [11] Dan Boneh and Brent Waters. Constrained pseudorandom functions and their applications. In ASIACRYPT, pages 280–300, 2013.

- [12] Elette Boyle, Kai-Min Chung, and Rafael Pass. On extractability obfuscation. In TCC, pages 52–73, 2014.

- [13] Elette Boyle, Shafi Goldwasser, and Ioana Ivan. Functional signatures and pseudorandom functions. In *Public Key Cryptography*, 2014.

- [14] Zvika Brakerski and Guy N. Rothblum. Virtual black-box obfuscation for all circuits via generic graded encoding. In TCC, pages 1–25, 2014.

- [15] Benjamin Braun, Ariel J. Feldman, Zuocheng Ren, Srinath Setty, Andrew J. Blumberg, and Michael Walfish. Verifying computations with state. In *Proceedings of the Twenty-Fourth* ACM Symposium on Operating Systems Principles, SOSP '13, pages 341–357, 2013.

- [16] Ran Canetti and Vinod Vaikuntanathan. Obfuscating branching programs using black-box pseudo-free groups. Cryptology ePrint Archive, Report 2013/500, 2013. http://eprint.iacr.org/.

- [17] Alessandro Chiesa and Eran Tromer. Proof-carrying data and hearsay arguments from signature cards. In *ICS*, pages 310–331, 2010.

- [18] Kai-Min Chung, Zhenming Liu, and Rafael Pass. Statistically-secure oram with  $\tilde{O}(\log^2 n)$  overhead. CoRR, abs/1307.3699, 2013.

- [19] Angelo De Caro, Vincenzo Iovino, Abhishek Jain, Adam O'Neill, Omer Paneth, and Giuseppe Persiano. On the achievability of simulation-based security for functional encryption. In *CRYPTO*, 2013.

- [20] Sanjam Garg, Craig Gentry, Shai Halevi, Mariana Raykova, Amit Sahai, and Brent Waters. Candidate indistinguishability obfuscation and functional encryption for all circuits. In FOCS, 2013. http://eprint.iacr.org/2013/451.

- [21] Sanjam Garg, Craig Gentry, Shai Halevi, and Daniel Wichs. On the implausibility of differinginputs obfuscation and extractable witness encryption with auxiliary input. *IACR Cryptology ePrint Archive*, 2013:860, 2013.

- [22] Rosario Gennaro, Craig Gentry, and Bryan Parno. Non-interactive verifiable computing: Outsourcing computation to untrusted workers. In Tal Rabin, editor, Advances in Cryptology – CRYPTO 2010, volume 6223 of Lecture Notes in Computer Science, pages 465–482. Springer, August 2010.

- [23] Craig Gentry, Kenny A. Goldman, Shai Halevi, Charanjit S. Jutla, Mariana Raykova, and Daniel Wichs. Optimizing oram and using it efficiently for secure computation. In *Privacy Enhancing Technologies*, pages 1–18, 2013.

- [24] Oded Goldreich, Shafi Goldwasser, and Silvio Micali. How to construct random functions. J. ACM, 33(4):792–807, August 1986.

- [25] Oded Goldreich and Rafail Ostrovsky. Software protection and simulation on oblivious RAMs. J. ACM, 1996.

- [26] Shafi Goldwasser, Yael Kalai, Raluca Ada Popa, Vinod Vaikuntanathan, and Nickolai Zeldovich. How to run turing machines on encrypted data. In CRYPTO, 2013.

- [27] Shafi Goldwasser, Yael Kalai, Raluca Ada Popa, Vinod Vaikuntanathan, and Nickolai Zeldovich. Succinct functional encryption and applications: Reusable garbled circuits and beyond. In STOC, 2013.

- [28] Shafi Goldwasser, Yael Tauman Kalai, and Guy N. Rothblum. One-time programs. In CRYPTO, pages 39–56, 2008.

- [29] Shafi Goldwasser and Guy N. Rothblum. On best-possible obfuscation. In TCC 2007: 4th Theory of Cryptography Conference, volume 4392 of Lecture Notes in Computer Science, pages 194–213. Springer, 2007.

- [30] Sergey Gorbunov, Vinod Vaikuntanathan, and Hoeteck Wee. Functional encryption with bounded collusions via multi-party computation. In *CRYPTO*, pages 162–179, 2012.

- [31] S. Dov Gordon, Jonathan Katz, Vladimir Kolesnikov, Fernando Krell, Tal Malkin, Mariana Raykova, and Yevgeniy Vahlis. Secure two-party computation in sublinear (amortized) time. In Proceedings of the 2012 ACM conference on Computer and communications security, CCS '12, pages 513–524, 2012.

- [32] S. Dov Gordon, Jonathan Katz, Feng-Hao Liu, Elaine Shi, and Hong-Sheng Zhou. Multi-input functional encryption. Cryptology ePrint Archive, Report 2013/774, 2013. http://eprint. iacr.org/.

- [33] Vipul Goyal, Abhishek Jain, Venkata Koppula, and Amit Sahai. Functional encryption for randomized functionalities. Cryptology ePrint Archive, Report 2013/729, 2013. http:// eprint.iacr.org/.

- [34] Aggelos Kiayias, Stavros Papadopoulos, Nikos Triandopoulos, and Thomas Zacharias. Delegatable pseudorandom functions and applications. In ACM CCS, 2013.

- [35] Eyal Kushilevitz, Steve Lu, and Rafail Ostrovsky. On the (in)security of hash-based oblivious RAM and a new balancing scheme. In *SODA*, 2012.

- [36] Steve Lu and Rafail Ostrovsky. How to garble ram programs. In EUROCRYPT, pages 719–734, 2013.

- [37] Moni Naor and Moti Yung. Public-key cryptosystems provably secure against chosen ciphertext attacks. In In Proc. of the 22nd STOC, pages 427–437, 1995.

- [38] Adam O'Neill. Definitional issues in functional encryption. Cryptology ePrint Archive, Report 2010/556, 2010. http://eprint.iacr.org/.

- [39] Amit Sahai. Non-malleable non-interactive zero knowledge and adaptive chosen-ciphertext security. In 40th Annual Symposium on Foundations of Computer Science, pages 543–553. IEEE Computer Society Press, October 1999.

- [40] Amit Sahai and Brent Waters. How to use indistinguishability obfuscation: Deniable encryption, and more. Cryptology ePrint Archive, Report 2013/454, 2013. http://eprint.iacr. org/.

- [41] John E. Savage. Models of computation: Exploring the power of computing. Addison-Wesley Longman Publishing Co., Inc., 1997.

- [42] Elaine Shi, T.-H. Hubert Chan, Emil Stefanov, and Mingfei Li. Oblivious RAM with  $O((\log N)^3)$  worst-case cost. In ASIACRYPT, pages 197–214, 2011.

- [43] Emil Stefanov, Elaine Shi, and Dawn Song. Towards practical oblivious RAM. In NDSS, 2012.

[44] Emil Stefanov, Marten van Dijk, Elaine Shi, Christopher Fletcher, Ling Ren, Xiangyao Yu, and Srinivas Devadas. Path oram: An extremely simple oblivious ram protocol. In ACM CCS, 2013.

# A General Background

## A.1 Puncturable Pseudorandom Functions

Puncturable family of PRFs are a special case of constrained PRFs [11, 13, 34], where the PRF is defined on all input strings except for a set of size polynomial in the security parameter. Below we recall their definition, as given by [40].

**Syntax.** A puncturable family of PRFs is defined by a tuple of algorithms (Gen, Eval, Puncture) and a pair of polynomials n() and m():

- Key Generation  $\text{Gen}(1^{\lambda})$  is a PPT algorithm that takes as input the security parameter  $\lambda$  and outputs a PRF key K.

- Punctured Key Generation Puncture(K, S) is a PPT algorithm that takes as input a PRF key K, a set S ⊂ {0,1}<sup>n(λ)</sup> and outputs a punctured key K<sub>S</sub>.

- Evaluation Eval(K, x) is a deterministic algorithm that takes as input a key K (punctured key or PRF key), a string  $x \in \{0, 1\}^{n(\lambda)}$  and outputs  $y \in \{0, 1\}^{m(\lambda)}$

**Definition A.1.** A family of PRFs (Gen, Eval, Puncture) is puncturable if it satisfies the following properties

- Functionality preserved under puncturing. Let  $K \leftarrow \text{Gen}(1^{\lambda})$  and  $K_S \leftarrow \text{Puncture}(K, S)$ . Then for all  $x \notin S$ ,  $\text{Eval}(K, x) = \text{Eval}(K_S, x)$ .

- Pseudorandom at punctured points. For every PPT adversary  $(\mathcal{A}_1, \mathcal{A}_2)$  such that  $\mathcal{A}_1()$ outputs a set  $S \subset \{0, 1\}^{n(\lambda)}$  and  $x \in S$ , consider an experiment  $K \leftarrow \text{Gen}(1^{\lambda})$  and  $K_S \leftarrow$ Puncture(K, S). Then

$\left|\Pr[\mathcal{A}_2(K_S, x, \mathsf{Eval}(K, x)) = 1] - \Pr[\mathcal{A}_2(K_S, x, U_{m(\lambda)}) = 1]\right| \le \mathsf{negl}(\lambda)$

where  $U_{m(\lambda)}$  denotes the the uniform distribution over  $m(\lambda)$  bits.

**Theorem A.2** ( [24, 11, 13, 34]). If one-way functions exist, then for all polynomial n() and m(), there exists a puncturable PRF family that maps n() bits to m() bits.

## A.2 Fully Homomorphic Encryption

A circuit-based fully homomorphic scheme cFHE.(Setup, Enc, Dec, Eval) is a tuple of algorithms described as follows:

- $(hpk, hsk) \leftarrow \mathsf{cFHE}.\mathsf{Setup}(1^{\lambda})$  takes in the security parameter  $\lambda$ , then outputs the public and secret key pair (hpk, hsk).

- $c \leftarrow \mathsf{cFHE}.\mathsf{Enc}(hpk, x)$  takes in a plaintext message x and public key hpk, then outputs the ciphertext c.

- $x \leftarrow \mathsf{cFHE}.\mathsf{Dec}(hsk, c)$  takes in a ciphertext c and secret key hsk, then outputs the plaintext x.

- $c' \leftarrow \mathsf{cFHE}.\mathsf{Eval}(hpk, C, (c_1, \ldots, c_k))$  takes in a circuit description C, input ciphertexts  $c_1, \ldots, c_k$ and public key hpk, then outputs the ciphertext c'.

The definition of semantic security for cFHE.(Setup, Enc, Dec, Eval) follows the definition of publickey encryption; we omit a formal statement.

**Definition A.3.** A circuit-based homomorphic encryption scheme cFHE.(Setup, Enc, Dec, Eval) is (perfectly) correct if for all  $\lambda \in \mathbb{N}$ , for all polynomial-size circuits C, for all honest (hpk, hsk)  $\leftarrow$ Setup $(1^{\lambda})$ , for all honestly generated  $c_1 := \text{Enc}(hpk, x_1), \ldots, c_k := \text{Enc}(hpk, x_k)$ , it holds that  $\text{Dec}(hsk, \text{Eval}(hpk, C, c_1, \ldots, c_k)) = C(x_1, \ldots, x_k).$

**Definition A.4.** A circuit-based homomorphic encryption scheme  $c\mathcal{FHE}$  is compact, if there exists a polynomial poly such that for all  $\lambda \in \mathbb{N}$ , the ciphertexts output by Eval have size at most  $poly(\lambda)$ .

### A.3 Non-Interactive Proof Systems

A non-interactive proof system consists of three efficient algorithms (Gen, Prove, Verify). The generation algorithm  $crs \leftarrow \text{Gen}(1^{\lambda})$  produces a common random string crs. The proves algorithm  $\pi \leftarrow \text{Prove}(crs, u, w)$  produces a proof  $\pi$  for a statement u using a witness w. The verification algorithm  $\text{Verify}(crs, u, \pi)$  decides whether  $\pi$  is a valid proof for the statement u using common reference string crs.

**Definition A.5.** We say that (Gen, Prove, Verify) is a non-interactive proof system for an NP language L with a corresponding NP relation R, if it satisfies the following two properties:

**Completeness** : For all  $(u, w) \in R$ , it holds that:

$$\Pr[\operatorname{Verify}(crs, u, \pi) = 0 | crs \leftarrow \operatorname{Gen}(1^{\lambda}), \pi \leftarrow \operatorname{Prove}(crs, u, w)] = \operatorname{negl}(\lambda)$$

**Soundness** : For all efficient Prove', it holds that:

$$\Pr[\mathsf{Verify}(crs, u, \pi) = 1, u \notin L|(crs) \leftarrow \mathsf{Gen}(1^{\lambda}), \pi \leftarrow \mathsf{Prove}'(crs, u, w)] = \mathsf{negl}(\lambda)$$

**Zero-Knowledge.** We first define the syntax of the simulator:  $(crs, \tau) \leftarrow \text{Sim}_1$  outputs a simulated *crs* and trapdoor  $\tau$ ,  $\pi \leftarrow \text{Sim}_2(crs, u, \tau)$  outputs a simulated proof. The proof system is zero-knowledge if there exist a poly-time simulator (Sim<sub>1</sub>, Sim<sub>2</sub>) such for any adversary  $\mathcal{A}$ , it holds:

$\Pr[\mathcal{A}(\pi) = 1 | crs \leftarrow \mathsf{Gen}(1^{\lambda}), \pi \leftarrow \mathsf{Prove}(crs, u, w)] \approx \Pr[\mathcal{A}(\pi) = 1 | (crs, \tau) \leftarrow \mathsf{Sim}_1, \pi \leftarrow \mathsf{Sim}_2(crs, u, \tau)]$

where  $(u, w) \in R, (u, w) \leftarrow \mathcal{A}(crs)$ .

## A.4 Statistical Simulation-Sound NIZKs

Let R be a polynomial-time computable binary relation. For  $(\mathsf{stmt}, w) \in R$ , we call  $\mathsf{stmt}$  the statement, and w the witness. Let L be the language consisting of all statements in R.

A Non-Interactive Zero-knowledge Proof system (NIZK) is a collection of three algorithms NIZK = (Setup, Prove, Verify):

•  $crs \leftarrow \mathsf{Setup}(1^{\lambda})$ : Takes in the security parameter  $\lambda$ , and generates a common reference string crs.

- $\pi \leftarrow \mathsf{Prove}(crs, \mathsf{stmt}, w)$ : Takes in crs, a statement  $\mathsf{stmt}$ , and a witness w such that  $(\mathsf{stmt}, w) \in L$ , outputs a proof  $\pi$ .

- b ← Verify(crs, stmt, π): Takes in the crs, a statement stmt, and a proof π, and outputs 0 or 1, denoting rejection or acceptance. stmt, and a witness w,

**Perfect completeness.** A NIZK system is said to be perfectly complete, if an honest prover with a valid witness can always convince an honest verifier. More formally, for any  $(\mathsf{stmt}, w) \in R$ , we have

$$\Pr\left[crs \leftarrow \mathsf{Setup}(1^{\lambda}), \ \pi \leftarrow \mathsf{Prove}(crs, \mathsf{stmt}, w): \ \mathsf{Verify}(crs, \mathsf{stmt}, \pi) = 1\right] = 1$$

**Statistical soundness.** A NIZK system is said to be statistically sound, if there does not exist a valid proof for any no false statement. More formally,

$$\Pr\left[\mathit{crs} \leftarrow \mathsf{Setup}(1^{\lambda}), \ \exists (\mathsf{stmt}, \pi) \colon \ (\mathsf{stmt} \notin L) \ \land \ (\mathsf{Verify}(\mathit{crs}, \mathsf{stmt}, \pi) = 1) \right] = \mathsf{negl}(\lambda)$$

**Computational zero-knowlege.** Informally, a NIZK system is computationally zero-knowledge, if the proof does not reveal any information about the witness to any polynomial-time adversary. More formally, a NIZK system is said to computationally zero-knowledge, if there exists a simulator S = (SimSetup, SimProve), such that for all non-uniform polynomial-time adversary  $\mathcal{A}$ , for any stmt, w such that (stmt, w)  $\in \mathbb{R}$ , it holds that

$$\Pr\left[\begin{array}{c} crs \leftarrow \mathsf{Setup}(1^{\lambda}), \\ \pi \leftarrow \mathsf{Prove}(crs, \mathsf{stmt}, w) : \\ \mathcal{A}(crs, \mathsf{stmt}, \pi) = 1 \end{array}\right] - \Pr\left[\begin{array}{c} (\widetilde{crs}, \mathsf{trap}) \leftarrow \mathsf{Sim}\mathsf{Setup}(1^{\lambda}, \mathsf{stmt}), \\ \widetilde{\pi} \leftarrow \mathsf{Sim}\mathsf{Prove}(crs, \mathsf{stmt}, \mathsf{trap}) : \\ \mathcal{A}(\widetilde{crs}, \mathsf{stmt}, \widetilde{\pi}) = 1 \end{array}\right] = \mathsf{negl}(\lambda)$$

Statistical simulation soundness [20]. Informally, a NIZK system is statistically simulation sound, if under a simulated  $\widetilde{crs}$ , no proof for a false statement exists, except for the simulated proof for statement fed into the SimSetup algorithm to generate  $\widetilde{crs}$ . More formally, a NIZK system is said to be statistically simulation sound, if

$$\Pr\left[\begin{array}{c} (\widetilde{crs},\mathsf{trap}) \leftarrow \mathsf{SimSetup}(1^{\lambda},\mathsf{stmt}), \pi \leftarrow \mathsf{SimProve}(\mathit{crs},\mathsf{stmt},\mathsf{trap}):\\ \exists (\mathsf{stmt}',\pi') \text{ s.t. } \mathsf{stmt}' \neq \mathsf{stmt}) \ \land \ (\mathsf{Verify}(\widetilde{\mathit{crs}},\mathsf{stmt}',\pi')=1) \end{array}\right] = \mathsf{negl}(\lambda).$$

#### A.5 Indistinguishability Obfuscation

A uniform PPT machine  $i\mathcal{O}$  is called an indistinguishable obfucastor [5, 29, 20], for a circuit family  $\{\mathcal{C}_{\lambda}\}$ , if the following conditions hold:

• Correctness. For all  $\lambda \in \mathbb{N}$ , for all  $C \in \mathcal{C}_{\lambda}$ , for all inputs x, we have

$$\Pr\left[C' \leftarrow i\mathcal{O}(\lambda, C): C'(x) = C(x)\right] = 1$$

• For any uniform or non-uniform PPT distinguisher D, for all security parameter  $\lambda \in \mathbb{N}$ , for all pairs of circuits  $C_0, C_1 \in \mathcal{C}_{\lambda}$  such that  $C_0(x) = C_1(x)$  for all inputs x, then

$$\left|\Pr\left[D(i\mathcal{O}(\lambda, C_0)) = 1\right] - \Pr\left[D(i\mathcal{O}(\lambda, C_1)) = 1\right]\right| \le \mathsf{negl}(\lambda)$$

For simplicity, when the security parameter  $\lambda$  is clear, we write  $i\mathcal{O}(C)$  in short.

**Remark A.6.** In a recent work [32], Gordon et al. observe that for the construction of [20], the size of the obfuscated circuit has only linear blowup, i.e.  $|i\mathcal{O}(C)| = |C| \cdot \mathsf{poly}(\lambda)$ . In the construction, in order to obfuscate any poly-sized C, they consider another NC1 program P that checks the trace of the computation of the FHE evaluation, and then decrypts. Essentially P is an "and" of |C|local verifications (each of which has size  $\mathsf{poly}(\lambda)$ ), and then a decryption, which has size  $\mathsf{poly}(\lambda)$ . Gordon et al. observe that each local verification can be written as a constant width,  $\mathsf{poly}(\lambda)$ length branching program by the Barrington's theorem; also it takes an additive linear blow up to "AND" multiple branching programs. Thus, P can be transformed to a branching program of size  $O(|C|) \cdot \mathsf{poly}(\lambda)$ . Then the construction of [20] blows up the branching program by  $\mathsf{poly}(\lambda)$ . Thus, the obfuscated circuit has size  $O(|C|) \cdot \mathsf{poly}(\lambda)$ .

## A.6 Differing-Inputs Obfuscation for Circuits

Barak et al. [5] defined the notion of differing-inputs obfuscation. We present the notion of differinginputs circuit family as the formulation in the works of Ananth et al. and Boyle et. al [2, 12]

**Definition A.7** ([4, 2, 12]). A circuit family C associated with a sampler Sampler is said to be a differing-inputs circuit family if for every PPT adversary A there exists a negligible function negl such that

$\Pr[C_0(x) \neq C_1(x) : (C_0, C_1, \mathsf{aux}) \leftarrow \mathsf{Sampler}(1^\lambda), x \leftarrow \mathcal{A}(1^\lambda, C_0, C_1, \mathsf{aux})] \leq \mathsf{negl}(\lambda).$

We now define the notion of differing-inputs obfuscation for a differing-inputs circuit family.

**Definition A.8** (Differing-Inputs Obfuscators for circuits). A uniform PPT machine di $\mathcal{O}$  is called a Differing-inputs Obfuscator for a differing-inputs circuit family  $\mathcal{C} = \{C_{\lambda}\}$  if the following conditions are satisfied:

• (Correctness): For all security parameter  $\lambda$ , all  $C \in C$ , all inputs x, we have

$$\Pr[C'(x) = C(x) : C' \leftarrow \mathsf{di}\mathcal{O}(\lambda, C)] = 1.$$

- (Polynomial slowdown): There exists a universal polynomial p such that for any circuit C, we have  $|C'| \leq p(|C|)$  for all  $C' = \operatorname{di}\mathcal{O}(\lambda, C)$  under all random coins.

- (Differing-inputs): For any (not necessarily uniform) PPT distinguisher D, there exists a negligible function negl such that the following holds: for all security parameters  $\lambda$ , for  $(C_0, C_1, aux) \leftarrow Sampler(1^{\lambda})$ , we have that

$$|\Pr[D(\mathsf{di}\mathcal{O}(\lambda, C_0, \mathsf{aux})) = 1] - \Pr[D(\mathsf{di}\mathcal{O}(\lambda, C_1, \mathsf{aux})) = 1]| \le \mathsf{negl}(\lambda).$$

### A.7 Virtual Black-Box (VBB) Obfuscation

**Definition A.9** ([5]). Let  $C = \{C_n\}_{n \in \mathbb{N}}$  be a family of polynomial-size circuits, where  $C_n$  is a set of Boolean circuits operating on inputs of length n. And let  $\mathcal{O}$  be a PPTM algorithm, which takes as input an input length  $n \in \mathbb{N}$ , a circuit  $C \in C_n$ , a security parameter  $\lambda \in \mathbb{N}$ , and outputs a Boolean circuit  $\mathcal{O}(C)$  (not necessarily in C).

$\mathcal{O}$  is a black box obfuscator for the circuit family  $\mathcal{C}$  if it satisfies:

1. Preserving Functionality: For every  $n \in \mathbb{N}$ , and every  $C \in \mathcal{C}_n$ , and every  $\vec{x} \in \{0,1\}^n$ , with all but  $negl(\lambda)$  probability over the coins of  $\mathcal{O}$ :

$$(\mathcal{O}(C, 1^n, 1^\lambda))(\vec{x}) = C(\vec{x})$$

- 2. Polynomial Slowdown: For every  $n, \lambda \in \mathbb{N}$  and  $C \in \mathcal{C}$ , the circuit  $\mathcal{O}(C, 1^n, 1^{\lambda})$  is of size at most  $poly(|C|, n, \lambda)$ .

- 3. Virtual Black Box: For every (non-uniform) polynomial-size adversary  $\mathcal{A}$ , there exists a (non-uniform) polynomial-size simulator  $\mathcal{S}$ , such that for every  $n \in \mathbb{N}$  and for every  $C \in \mathcal{C}_n$ :

$$\left| \Pr_{\mathcal{O},\mathcal{A}} [\mathcal{A}(\mathcal{O}(C,1^n,1^\lambda)) = 1] - \Pr_{\mathcal{S}} [\mathcal{S}^C(1^{|C|},1^n,1^\lambda) = 1] \right| = \operatorname{negl}(\lambda)$$

### A.8 Proof-Carrying Data

For completeness, we present the Proof-Carrying-Data (PCD) definition in exactly the same way as Bitansky et al. [9].

We view a distributed computation as a directed acyclic graph G = (V, E) with node labels linp:  $V \to \{0, 1\}^*$  and edge labels data:  $E \to \{0, 1\}^*$ . The node label linp(v) of a node v represents the local input (which may include a local program) used by v in his local computation. (Whenever v is a source or a sink, we require that  $linp(v) = \bot$ .) The edge label data(u, v) of a directed edged (u, v) represents the message sent from node u to node v. Typically, a party at node v uses the local input linp(v) and input messages (data $(u_1, v), \ldots, data(u_c, v)$ ), where  $u_1, \ldots, u_c$  are the parents of vin lexicographic order, to compute an output message data(v, w) for a child node w; the party also similarly computes a message for every other child node. We can think of the messages on edges going out from sources as the "inputs" to the distributed computation, and the messages on edges going into sinks as the "outputs" of the distributed computation; for convenience we will want to identify a single distinguished output.

**Definition A.10.** A (distributed computation) transcript is a triple T = (G, linp, data), where G = (V, E) is a directed acyclic graph G,  $\text{linp} : V \to \{0, 1\}^*$  are node labels, and  $\text{data} : E \to \{0, 1\}^*$  are edge labels; we require that  $\text{linp}(v) = \bot$  whenever v is a source or a sink. The output of T, denoted out(T), is equal to  $\text{data}(\tilde{u}, \tilde{v})$  where  $(\tilde{u}, \tilde{v})$  is the lexicographically first edge such that  $\tilde{v}$  is a sink.

A proof-carrying transcript is a transcript where messages are augmented by proof strings, i.e., a function proof :  $E \to \{0,1\}^*$  provides for each edge (u, v) an additional label proof(u, v), to be interpreted as a proof string for the message data(u, v).

**Definition A.11.** A proof-carrying (distributed computation) transcript PCT is a pair (T, proof) where T is a transcript and proof :  $E \rightarrow \{0, 1\}^*$  is an edge label.

Next, we define what it means for a distributed computation to be *compliant*, which is the notion of "correctness with respect to a given local property". Compliance is captured via an efficiently-computable compliance predicate  $\mathbb{C}$ , which must be locally satisfied at each vertex; here, "locally" means with respect to a node's local input, incoming data, and outgoing data. For convenience, for any vertex v, we let children(v) and parents(v) be the vector of v's children and parents respectively, listed in lexicographic order.

**Definition A.12.** Given a polynomial-time predicate  $\mathbb{C}$ , we say that a distributed computation transcript T = (G, linp, data) is  $\mathbb{C}$ -compliant (denoted by  $\mathbb{C}(T) = 1$ ) if, for every  $v \in V$  and  $w \in \text{children}(v)$ , it holds that

$\mathbb{C}(\mathsf{data}(v, w); \mathsf{linp}(v); \mathsf{inputs}(v)) = 1$

where  $inputs(v) := (data(u_1, v), \dots, data(u_c, v))$  and  $(u_1, \dots, u_c) := parents(v)$ . Furthermore, we say that a message z is  $\mathbb{C}$ -compliant if there is T such that  $\mathbb{C}(T) = 1$  and out(T) = 1.

**Proof-Carrying Data Systems.** A proof-carrying data (PCD) system for a class of compliance predicates **C** is a triple of algorithms  $(\mathbb{G}, \mathbb{P}, \mathbb{V})$  that works as follows:

- The (probabilistic) generator G, on input the security parameter λ, outputs a reference string rs and a corresponding verification state vrs.

- For any  $\mathbb{C} \in \mathbf{C}$ , the (honest) prover  $\mathbb{P}_{\mathbb{C}} := \mathbb{P}(\mathbb{C}, \cdots)$  is given a reference string rs inputs  $\vec{z}_i$  with corresponding proofs  $\vec{\pi}_i$ , a local input linp, and an output  $z_o$ , and then produces a proof  $\pi_o$  attesting to the fact that  $z_o$  is consistent with some  $\mathbb{C}$ -compliant transcript.

- For any  $\mathbb{C} \in \mathbb{C}$ , the verifier  $\mathbb{V}_{\mathbb{C}} := \mathbb{V}(\mathbb{C}, \cdots)$  is given the verification state vrs, an output  $z_o$ , and a proof string  $\pi_o$ , and accept if it is convinced that  $z_o$  is consistent with some  $\mathbb{C}$ -compliant transcript.

After the generator  $\mathbb{G}$  has been run to obtain rs and vrs, the prover  $\mathbb{P}_{\mathbb{C}}$  is used (along with rs) at each node of a distributed computation transcript to dynamically compile it into a proof-carrying transcript by generating and adding a proof to each edge. Each of these proofs can be checked using the verifier  $\mathbb{V}_{\mathbb{C}}$  (along with vrs).

The formal definition. We now formally define the notion of PCD systems. We begin by introducing the dynamic proof-generation process, which we call ProofGen. We define ProofGen as an interactive protocol between a (not necessarily efficient) distributed-computation generator S and the PCD prover  $\mathbb{P}$ , in which both are given a compliance predicate  $\mathbb{C} \in \mathbb{C}$  and a reference string rs. Essentially, at every time step, S chooses to do one of the following actions: add a new unlabeled vertex to the computation transcript so far (this corresponds to adding a new computing node to the computation), label an unlabeled vertex (this corresponds to a choice of local input by a computing node), or add a new labeled edge (this corresponds to a new message from one node to another). In case S chooses the third action, the PCD prover  $\mathbb{P}_{\mathbb{C}}$  produces a proof for the  $\mathbb{C}$ -compliance of the new message, and adds this new proof as an additional label to the new edge. When S halts, the interactive protocol outputs the distributed computation transcript  $\mathsf{T}$ , as well as T's output and corresponding proof. Intuitively, the completeness property requires that if  $\mathsf{T}$  is compliant with  $\mathbb{C}$ , then the proof attached to the output (which is the result of dynamically invoking  $\mathbb{P}_{\mathbb{C}}$  for each message in  $\mathsf{T}$ , as T was being constructed by S) is accepted by the verifier. Formally the interactive protocol ProofGen( $\mathbb{C}$ , rs, S,  $\mathbb{P}$ ) is defined as follows:

$\mathsf{ProofGen}(\mathbb{C}, \mathsf{rs}, S, \mathbb{P})$

- 1. Set T and PCT to be "empty transcripts".

- 2. Until S halts and outputs a message-proof pair  $(z_o, \pi_o)$ , do the following:

- (a) Give ( $\mathbb{C}$ , rs, PCT) as input to S and obtain as output (b, x, y).

- (b) If  $b = \text{add unlabeled vertex and } x \notin V$ , then set  $V := V \cup \{x\}$  and  $\text{linp}(x) := \bot$ .

- (c) If  $b = \texttt{label vertex}, x \in V, x$  is nor a source or sink, and  $\texttt{linp}(x) = \bot$ , then linp(x) := y.

- (d) If  $b = \text{add labeled edge and } x \notin E$ :

- i. Parse x as (v, w) with  $v, w \in V$

- ii. Set  $E := E \cup \{(u, v)\}$

- iii. Set data(v, w) := y.

- iv. If v is a source, set  $\pi := \bot$

- v. If v is not a source, set  $\pi := \mathbb{P}_{\mathbb{C}}(\mathsf{rs}, \mathsf{data}(v, w), \mathsf{linp}(v), \mathsf{inputs}(v), \mathsf{inproofs}(v))$ , where  $\mathsf{inputs}(v) := \mathsf{data}(u_1, v), \ldots, \mathsf{data}(u_c, v)$ ,  $\mathsf{inproofs}(v) := \mathsf{proof}(u_1, v), \ldots, \mathsf{proof}(u_c, v)$ , and  $(u_1, \ldots, u_c) := \mathsf{parents}(v)$ .

- vi. Set  $proof(v, w) := \pi$

**Definition A.13.** A proof-carrying data system for a class of compliance predicates  $\mathbf{C}$  is a triple of algorithms  $(\mathbb{G}, \mathbb{P}, \mathbb{V})$ , where  $\mathbb{G}$  is probabilistic and  $\mathbb{V}$  is deterministic, such that:

1. Completeness:

For every compliance predicate  $\mathbb{C} \in \mathbf{C}$  and (possibly unbounded) distributed computation generator S,

$$\Pr\left[\begin{array}{cc} \mathsf{T} \ is \ B \ bounded \land \mathbb{C}(\mathsf{T}) = 1 \land \mathbb{V}_{\mathbb{C}}(\mathsf{vrs}, \mathsf{z}_o, \pi_o) \neq 1 \\ : (\mathsf{rs}, \mathsf{vrs}) \leftarrow \mathbb{G}(B), (\mathsf{z}_o, \pi_o, \mathsf{T}) \leftarrow \mathsf{ProofGen}(\mathbb{C}, \mathsf{rs}, S, \mathbb{P}) \end{array}\right] \le \mathsf{negl}(\lambda)$$

2. Proof of Knowledge:

For every polynomial-size prover  $\mathbb{P}^*$  there exists a polynomial-size extractor  $\mathbb{E}_{\mathbb{P}^*}$  such that for every compliance predicate  $\mathbb{C} \in \mathbb{C}$ , every large enough security parameter  $\lambda \in \mathbb{N}$ , every auxiliary input  $z \in \{0, 1\}^{\mathsf{poly}(\lambda)}$ , and every time bound  $B \in \mathbb{N}$ ,

$$\Pr\left[\begin{array}{c} \mathbb{V}_{\mathbb{C}}(\mathsf{rs},\mathsf{z},\pi) = 1 \land (\mathsf{out}(\mathsf{T}) \neq \mathsf{z} \lor \mathbb{C}(\mathsf{T}) \neq 1) \\ : (\mathsf{rs},\mathsf{vrs}) \leftarrow \mathbb{G}(B), (\mathsf{z}_o,\pi_o) \leftarrow \mathbb{P}^*(\mathsf{rs},z), \mathsf{T} \leftarrow \mathbb{E}_{\mathbb{P}^*}(\mathsf{rs},z) \end{array}\right] \leq \mathsf{negl}(\lambda)$$

3. Efficiency:

There exists a universal polynomial p such that, for every compliance predicate  $\mathbb{C} \in \mathbf{C}$ , every large enough security parameter  $\lambda \in \mathbb{N}$ , every time bound  $B \in \mathbb{N}$ , and every B-bounded distributed computation transcript  $\mathsf{T}$ ,

- the generator  $\mathbb{G}(1^{\lambda}, B)$  runs in time  $\begin{cases} p(\lambda + B) & \text{for a fully-succinct PCD} \\ p(\lambda + \log B) & \text{for a preprocessing PCD} \end{cases}$

- the prover  $\mathbb{P}_{\mathbb{C}}(\mathsf{rs}, \mathsf{data}(v, w), \mathsf{linp}(v), \mathsf{inputs}(v), \vec{\pi}_i)$  runs in time

$$\begin{cases} p(\lambda + |\mathbb{C}| + t_{\mathsf{T},\mathbb{C}}(v, w) + \log B) & \text{for a fully-succinct } PCD \\ p(\lambda + |\mathbb{C}| + B) & \text{for a preprocessing } PCD \end{cases}$$

where  $t_{\mathsf{T},\mathbb{C}}(v,w)$  denotes the time to evaluate  $\mathbb{C}(\mathsf{data}(v,w),\mathsf{linp}(v),\mathsf{inputs}(v))$  at an edge (v,w);

- the verifier  $\mathbb{V}_{\mathbb{C}}(vrs, z, \pi)$  runs in time  $p(\lambda + |\mathbb{C}| + |z| + \log B)$

- an honestly generated proof has size  $p(\lambda + \log B)$ .

We shall also consider a restricted notion of PCD system: a **path PCD** system is a PCD system where completeness is guaranteed to hold only for distributed computations transcripts T whose graph is a line.

## **B** RAM-Model Functional Encryption Security Definitions

## B.1 Simulation-Based Security

Simulation-based security for functional encryption has been defined in several prior works [10, 38, 30, 1]. Here we follow the definition in [38, 30], and define the simulation based security for functional encryption in the RAM model. Note that the Setup and the pre-challenge KeyGen are carried out honestly (not by the simulator). As demonstrated in [30], single message security defined below implies multiple-message security where the adversary is allowed to provide many messages in the challenging phase.

**Definition B.1** (Full Simulation Security, Non-Adaptive/Adaptive, Multiple-Key, Single-Message). Let FE be a functional encryption scheme for RAM programs computing a functionality class  $\mathcal{F}$ . For every PPT stateful adversary  $\mathcal{A}$  and PPT stateful simulator  $\mathcal{S}$ , consider the following two experiments.

| $\operatorname{Real}_{\mathcal{A}}(1^{\lambda})$                     | $IDEAL_{\mathcal{A},\mathcal{S}}(1^{\lambda})$                        |

|----------------------------------------------------------------------|-----------------------------------------------------------------------|

| 1: (mpk, msk) $\leftarrow$ FE.Setup $(1^{\lambda})$ ;                | 1: $(mpk, msk) \leftarrow FE.Setup(1^{\lambda});$                     |

| 2: $x \leftarrow \mathcal{A}^{FE.KeyGen(msk,\cdot)}(mpk);$           | 2: $x \leftarrow \mathcal{A}^{FE.KeyGen(msk,\cdot)}(mpk);$            |

|                                                                      | Let $RAM_1,, RAM_q$ be $\mathcal{A}$ 's oracle queries,               |

|                                                                      | $sk_{RAM_i}$ be the oracle reply to $RAM_i$ , and                     |

|                                                                      | view := $\{y_i = RAM_i(x), RAM_i, sk_{RAM_i}\}_{i \in [q]}$ .         |

| 3: ct $\leftarrow FE.Enc(mpk, x);$                                   | 3: ct $\leftarrow \mathcal{S}(mpk, view, 1^{ x });$                   |

| 4: $\alpha \leftarrow \mathcal{A}^{\mathcal{O}(msk,\cdot)}(mpk,ct);$ | 4: $\alpha \leftarrow \mathcal{A}^{\mathcal{O}'(msk,\cdot)}(mpk,ct);$ |

| 5: OUTPUT $(\alpha, x)$ ;                                            | 5: OUTPUT $(\alpha, x)$ ;                                             |

We consider two cases of the above experiments:

- 1. The non-adaptive case, where the oracles  $\mathcal{O}(\mathsf{msk}, \cdot)$  and  $\mathcal{O}'(\mathsf{msk}, \cdot)$  are both "empty oracles" that return nothing.

- 2. The adaptive case, where

- the oracle  $\mathcal{O}(\mathsf{msk}, \cdot) = \mathsf{FE}.\mathsf{KeyGen}(\mathsf{msk}, \cdot)$ , and

- the oracle  $\mathcal{O}'(\mathsf{msk}, \cdot)$  is the (stateful) second stage of the simulator; namely,  $\mathcal{O}'(\mathsf{msk}, \cdot) = \mathcal{S}^{U(\cdot, x)}(\mathsf{msk}, \cdot)$  where  $U(\mathsf{RAM}, x) = \mathsf{RAM}(x)$  for all  $\mathsf{RAM}$ .

We call a simulator algorithm S admissible if, on each of A's queries RAM to the second stage of the simulator, the simulator makes just a single query to its oracle  $U(\cdot, x)$  on RAM itself.

The functional encryption scheme FE is said to be fully SIM-secure against non-adaptive (resp. adaptive) adversaries if there is an admissible PPT stateful simulator S such that for every PPT stateful adversary A, the following two distributions are computationally indistinguishable:

$$\left\{ \operatorname{Real}_{\mathcal{A}}(1^{\lambda}) \right\}_{\lambda} \stackrel{c}{\approx} \left\{ \operatorname{IDeal}_{\mathcal{A},\mathcal{S}}(1^{\lambda}) \right\}_{\lambda}$$

We can easily define the *selective-simulation security* by enforcing the adversary to reveal the challenge messages before seeing the master public key mpk. We can also easily define the full simulation security to support multiple messages.

## B.2 Indistinguishability-Based Security

Indistinguishability-based security for functional encryption has also been considered [10, 38]. We provide a definition using our notation: