# The Oblivious Machine or: How to Put the C into MPC

Marcel Keller

Department of Computer Science, University of Bristol m.keller@bristol.ac.uk

**Abstract.** We present the oblivious machine, a concrete notion for multiparty random access machine (RAM) computation and a toolchain to allow the efficient execution of general programs written in a subset of C that allows RAM-model computation over integers. The machine only leaks the list of possible instructions and the running time. Our work is based on the oblivious array for secret-sharing-based multiparty computation by Keller and Scholl (Asiacrypt '14). This means that we only incur a polylogarithmic over the execution on a normal CPU.

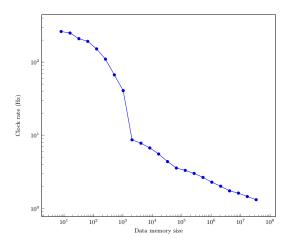

We implemented our construction using the Clang compiler from the LLVM project and the SPDZ protocol by Damgård et al. (Crypto '12). The latter provides active security against a dishonest majority and works in the preprocessing model. The online phase clock rate of the resulting machine is 41 Hz for a memory size of 1024 64-bit integers and 2.2 Hz for a memory of 2<sup>20</sup> integers. Both timings have been taken for two parties in a local network.

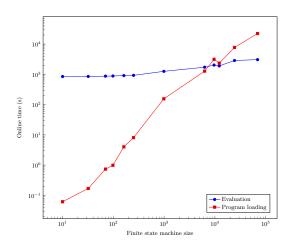

To further showcase our toolchain, we implemented and benchmarked private regular expression matching. Matching a string of length 1024 against a regular expression with 69270 transitions as a finite state machine takes seven hours online time, of which more than six hours are devoted to loading the reusable program.

Keywords: Multiparty computation, random-access machine, oblivious RAM, compilers, regular expression matching

# 1 Introduction

Multiparty computation (MPC) refers to the technique that allows a set of parties to compute on data held by them privately without revealing anything other than the desired result. The feasibility has been established for some time in two lines of work, Yao's garbled circuits [16] and secret-sharing-based multiparty computation [1, 4, 11]. The former allow two parties to compute binary circuits, and the latter enables any number of parties to compute arithmetic circuits over finite fields or rings. In this paper, we focus on secretsharing-based MPC. There are various schemes differing in the degree of adversarial power such as the number of corrupted parties or the kind of corruption. However, all of them implement the so-called arithmetic black box presented in Section 2.

While circuits are complete in the sense that they allow any computation, they generally incur an overhead over random access machine (RAM) programs. This overhead is related to the fact that, to access an array by a data-dependent index, a circuit needs to access the whole array. In terms of security, accessing only parts of such an array would reveal possibly sensitive data. A first step to remedy this was taken by Ostrovsky and Shoup [19], who proposed the oblivious random access machine (ORAM) as a mean to hide the access pattern of a memory-restricted client on a server with larger memory. They briefly mention the possibility of using their scheme in the context of secure two-party computation with one party holding the encrypted server memory. Damgård et al. [7] on the other hand suggested to secret share the server memory. However, due to the lack of efficient ORAM schemes, no concrete schemes or implementations emerged.

Only following the proposal of tree-based ORAM by Shi et al. [22], practical instantiations of oblivious data structures for multiparty computation have been proposed, both for Yao's garbled circuits [12, 17, 26] and secret-sharing based MPC [13]. These works essentially provide an implementation of an oblivious array with efficient access, that is, one access to a secret index only incurs polylogarithmic cost (in the size of

the array). Based on the oblivious array, the latter work goes on to implement an oblivious priority queue, which is then used for Dijkstra's algorithm, as well as the Gale-Shapley algorithm for stable matching. In the case of Dijkstra's algorithm, it turns out that the algorithm has to be reformulated to be implemented as a circuit with access to oblivious data structures.

On the theoretical side, Gentry et al. [10] proposed garbled RAM, which combines Yao's garbled circuit and ORAM. They present two solutions, one based on identity-based encryption, and the other based on revocable pseudorandom functions. Both approaches do not seem to be practical because they involve the mentioned cryptographic operations being executed in a garbled circuit. In comparison, the works presented in the previous paragraph use relatively lightweight operations.

#### 1.1 Our Contribution

In this work, we present a practical instantiation of an oblivious machine in the arithmetic black-box model, that is, an MPC protocol that allows efficient, oblivious computation in the RAM model. By oblivious computation we mean that the sequence of instructions executed is not revealed to the adversary, only the running time is. This enables the compilation of a subset of ANSI C (including conditional expressions, loops, arrays, and structs) and thus the execution of many algorithms in C with only polylogarithmic overhead. To the best of our knowledge, we are the first to implement this. We also present a theoretical model of an oblivious machine in the UC framework.

While previous works [12, 17] have introduced the concept of secure RAM-model computation, their notions remain rather abstract. Furthermore, Liu et al. [17] call general secure RAM-model computation "relatively inefficient" because one has to execute the universal next-instruction circuit, which must interpret every possible instruction. The motivation of this work is put a price tag on such general secure RAM-model computation.

Our construction essentially uses the oblivious array by Keller and Scholl [13] for storing data and code, and for every step, it executes all possible instructions in a way that minimizes data accesses. While this incurs some overhead, we believe that it is more efficient than using a one instruction set machine because increases the length of programs and thus the length of memory accesses, which we found to be the most expensive part in our implementation.

As an application of our concept, we highlight the case of regular expression matching. Regular expressions can be implemented as finite state machines and thus in the RAM model. Kerschbaum [14] presented two MPC protocols for regular expression matching, a secure one and one with leakage. They have complexity in O(nml) and  $O(knm^2 + ln)$  for m states, n symbols, string length l and some security parameter k. The security of our solution lies in between because it only leaks the total running time, which is less than every repetition of a previous state being leaked by Kerschbaum's algorithm. With a complexity in  $O(nm \log^3 nm + ln(\log^3 nm + \log^3 l))$ , our approach beats the previous work on regular expressions that are complex enough, that is, if  $km \gg \log^3 nm$  and  $km^2 \gg l(\log^3 nm + \log^3 l)$ . Using the same approach using a regular CPU has complexity in O(nm + ln) for loading and executing the program. Launchbury et al. [15] also mention an implementation of regular expression matching with multiparty computation. From their description, we estimate that their protocol is similar to the secure one by Kerschbaum.

With MPC, potentially corrupted parties are involved in any computation. While the oblivious machine obscures the instruction currently executed as well as the data accessed, it is inherent that the adversary learns the amount of computation. In our case, this is the number of instructions being executed. A straightforward way to obscure this to some extent is to define a maximal number of instructions and then execute exactly this many steps. However, this can only increase the computation time. We believe that there still is a use case for oblivious computation leaking the total time, for example, if the same program is not executed enough times to mount a timing attack.

Since our oblivious machine does not reveal information about the code other than the set of possible instructions, and code can also be input in secret, it also suits private function evaluation (PFE). Informally, private function evaluation allows two parties to compute a function known to one party on data known by another party without revealing either input to the other party. Previous work on PFE focuses on circuits, such as the solution by Mohassel et al. [18]. Their solution only incurs a constant overhead for circuits.

However, for RAM-model computation, our solution comes with only polylogarithmic overhead. To the best of our knowledge, our protocol is the first such proposal.

#### 1.2 Related Work

Keller and Scholl [13], while providing much of the foundation of or work, do not consider general oblivious computation but stick to oblivious data structures and specific applications thereof.

Wang et al. [26] briefly mention the idea of implementing a universal RAM instruction as a circuit. However, they do not present a more detailed account or experimental figures.

Our oblivious machine is related to the concept of an oblivious Turing machine, which is a Turing machine where the movement of the head only depends on the time. Pippenger and Fischer [20] showed that any Turing machine can be converted into an oblivious one incurring only logarithmic overhead. However, the best known result for converting a RAM program with running time T to a Turing machine results in a running time in  $O(T^2)$  [5]. Hence, this transformation is currently not suitable to achieve polylogarithmic overhead for RAM programs.

In the area of homomorphic encryption, Gentry et al. [9] have proposed to use ORAM to enable private queries to an encrypted database. They do not target general computation however.

Ben-Sasson et al. [2] proposed TinyRAM, a system for succinct verifiable non-interactive arguments to prove the correct execution of C programs. The setting of verifiable computation differs from ours in that the control flow does not need to be hidden. This is what mandates the use of oblivious RAM in our construction.

#### 1.3 Paper Organization

After introducing the concept of MPC, oblivious arrays in MPC, and the RAM model in Section 2, we present a model of our oblivious machine in Section 3. We also prove that this model implements RAM computation, and that it can be implemented using MPC with oblivious arrays. In Section 4, we the present our actual implementation and toolchain with examples in Section 5 on the application to regular expression matching. Finally, we show experimental results in Section 6, and we conclude in Section 7.

### 2 Preliminaries

In this section, we will present previous results that are related to our work.

We start with multiparty computation. MPC schemes allow a set of parties to compute public circuits on private data. All secret-sharing-based MPC protocols provide the arithmetic black box shown in Figure 1. Since most schemes use linear secret sharing where the sharing commutes with linear operations, the addition operation can often be done without communication. On the other hand, multiplication cannot be computed without communication.

Note that the arithmetic black box does not specify most the security properties achieved by a particular protocol, for example, whether it allows active or passive corruption, how many parties can be corrupted etc. This goes beyond the scope of this paper because the security depends on the protocol. The only property specified by  $\mathcal{F}_{ABB}$  is the possibility for the adversary to abort the protocol. This is required for protocols that allow a malicious, dishonest majority such as as the SPDZ protocol [8]. However, our protocols can be instantiated with any MPC scheme implementing  $\mathcal{F}_{ABB}$ , and the resulting protocol will inherit the security properties of the underlying scheme. Furthermore, because  $\mathcal{F}_{ABB}$  only outputs handles to intermediate information, it is often straight-forward to prove the security of protocols using it.

Keller and Scholl [13] proposed to use tree-based ORAM in the context of  $\mathcal{F}_{ABB}$  to get oblivious arrays with polylogarithmic overhead. Their result can be used to extend  $\mathcal{F}_{ABB}$  to  $\mathcal{F}_{ABBOA}$  as detailed in Figure 2. The proposed construction keeps both the client and the server memory of an ORAM scheme in the arithmetic black box, executes client computations using  $\mathcal{F}_{ABB}$  addition and multiplication, and uses the public output of  $\mathcal{F}_{ABB}$  to reveal the address for server memory accesses (and hence the  $\mathcal{F}_{ABB}$  handle). In the realm of the UC framework, their result can be stated as  $\mathcal{P}_{ABBOA}$  in Figure 3. **Initialize:** On input  $(Init, \mathbb{F})$  from all parties, store  $\mathbb{F}$ .

**Public Input:** On input (PublicInput, a) from all parties, store a and return a handle [a] to all parties.

**Private Input:** On input (PrivateInput, i, a) from Party  $P_i$  and (PrivateInput, i) from all other parties, store a and return a handle [a] to all parties.

Addition: On input (Add, [a], [b]) from all parties, compute c = a + b in  $\mathbb{F}$ , store it, and return a handle [c] to the parties.

**Multiplication:** On input (Multiply, [a], [b]) from all parties, compute  $c = a \cdot b$  in  $\mathbb{F}$ , store it, and return a handle [c] to the parties.

**Public Output:** On input (PublicOutput, [a]) from all parties, reveal a to all parties.

**Private Output:** On input (PrivateOutput, i, [a]) from all parties, reveal a to Party  $P_i$ .

Abort: On input Abort from the adversary, abort.

Fig. 1.  $\mathcal{F}_{ABB}$

**Initialize Array:** On input (initArray, n) from all parties, allocate an array of size n, initialize its entries to zero, and return a handle [x] to all parties.

**Read Array:** On input (readArray, [x], [a]) from all parties, read the *a*-th entry of *x*, store it, and return a handle [b] to it.

Write Array: On input (writeArray, [x], [a], [v], [f]) from all parties, write v to the a-th entry of x if f = 1.

Fig. 2.  $\mathcal{F}_{ABBOA}$  extension

$\mathcal{F}_{ABB}$  instructions: Use  $\mathcal{F}_{ABB}$  as instructed.

Initialize Array: Allocate sufficient storage according the ORAM scheme and run the ORAM initialization using  $\mathcal{F}_{ABB}$ .

**Read Array:** Read the address stored in x at a using  $\mathcal{F}_{ABB}$  as outlined above and return the resulting handle as [b].

Write Array: Read the address stored in x at a as above, and use the ORAM protocol to store  $\mathsf{lfElse}(f, v, b) = f \cdot (v - b) + b$  at address a in x.

Fig. 3.  $\mathcal{P}_{ABBOA}$

**Theorem 1.**  $\mathcal{P}_{ABBOA}$  realizes  $\mathcal{F}_{ABBOA}$  in the  $\mathcal{F}_{ABB}$ -hybrid model.

*Proof (Sketch).* We simulate the ORAM operations using an emulation of  $\mathcal{F}_{ABB}$  similarly to the protocol as follows: We use the ORAM simulator to generate the server memory addresses being revealed and abort  $\mathcal{F}_{ABB}$  in case of deviation by corrupted parties. The ORAM simulator guarantees the sequence of addresses accessed in the server memory are independent of the access pattern. Furthermore, the probability of the ORAM delivering incorrect data is negligible. Hence, the simulation is indistinguishable from the protocol.

#### 2.1 Random Access Machines

We will use the RAM model by Cook and Reckhow [5]. They define a random access machine as a machine with a memory X of integer registers that can execute a finite program consisting of the instructions listed in Table 1. The first instruction allows to load a constant to a fixed memory address, the second and the implement addition and subtraction with fixed input and output addresses. The next two instructions enable indirect addressing for loading and storing, which is required for array operations, for example. The "TRA" instruction (for transfer) allows to jump conditionally in the program code, which is needed by all control flow operations such as "if" statements and loops. Finally, "READ" and "WRITE" cover input and output operations.

$\begin{array}{lll} X_i \leftarrow C & & C \text{ any integer} \\ X_i \leftarrow X_j + X_k & & \\ X_i \leftarrow X_j - X_k & & \\ X_i \leftarrow X_j & & \\ \text{TRA } m \text{ if } X_j > 0 \text{ Jump to address } m \text{ in the program code} \\ \text{READ } X_i & & \text{Read from input} \\ \text{PRINT } X_i & & \text{Print to output} \end{array}$

Table 1. Instructions of random access machines

# 3 The Oblivious Machine

In this section, we will present our theoretical oblivious machine, prove that it implements RAM-model computation, and prove that it can implemented using the arithmetic black box with oblivious arrays. Figure 4 shows the desired functionality of the oblivious machine.

**Initialize:** On input ( $\mathsf{Init}, \mathbb{F}, n_d$ ) from all parties, store the parameters and allocate the data array of size  $n_d$ . **Instructions:** On input ( $\mathsf{Instructions}, Q, I_0, \ldots, I_{n_I}$ ) from all parties, store the list of instructions and the instruction pattern Q.

**Public Code:** On input (PublicCode,  $(c_0, \mathsf{param}_0), \ldots, (c_{n_c-1}, \mathsf{param}_{n_c-1})$ ) from all parties, store the code array. **Private Code:** On input (PrivateCode,  $i, (c_0, \mathsf{param}_0), \ldots, (c_{n_c-1}, \mathsf{param}_{n_c-1})$ ) from Party  $P_i$  and (privateCode,  $i, n_c, n_p$ ) from all other parties, check that  $|\mathsf{param}_i| = n_p$  for all j, and store the code array.

**Public Data:** On input (PublicData, a, d) from all parties, store d at address a in the data array.

**Private Data:** On input (PrivateData, a, d) from Party  $P_i$  and (PrivateData, i) from all other parties, store d at address a.

**Run:** On input (Run, pc) from all parties, execute the following:

- 1: while  $pc \neq \perp do$

- 2: Send (Tick) to the environment.

- 3: Load  $(c_{pc}, \mathsf{param}_{pc})$  from the code.

- 4:  $pc \leftarrow I_{c_{pc}}(\mathsf{param}_{pc})$

5: Send (Done) to the environment.

**Reveal:** On input (Reveal, i, a) from all parties, reveal the item at address a in the data array to Party  $P_i$ . **Abort:** At any time, the environment can request aborting.

Bounds Check: For every access to the data or instruction array, if the index is within the bound, output (WithinBounds) to the environment. Otherwise, output (OutOfBounds) to all parties and the environment and abort.

# Fig. 4. $\mathcal{F}_{machine}$

For simplicity, we only allow either public code or private code. One could think of mixing those, but this would require some intricate linking. Similarly, we decided to separate instruction and data storage to simplify the description. This results in a Harvard-like architecture, where the memory for instructions is separated from the data storage. It is straight-forward to use a Von Neumann architecture, where everything is stored in the same memory. However, due to the polylogarithmic access complexity of the underlying ORAM, two smaller oblivious arrays are slightly faster than one combined. Furthermore, code and data have different formats in our implementation, which is easier to accommodate for in two different oblivious arrays. Finally, we do not see a use case for code that can be altered by the machine.

It remains to define the notions of instruction pattern and instruction. The basic idea of an instruction pattern is that all instructions have the same access pattern. This allows to run all instructions in parallel,

accessing the data only once per instruction pattern entry, but independently of the number of distinct instructions.

**Definition 1 (Instruction pattern).** An instruction pattern is a list  $\{(n_1, t_1), \ldots, (n_L, t_L)\}$  where there is a state size  $n_i \in \mathbb{N}$  and access type  $t_i \in \{\text{Read}, \text{Write}\}$  for all  $i \in [L]$ .

**Definition 2 (Instruction).** An instruction with instruction pattern  $\{(n_1, t_1), \ldots, (n_L, t_L)\}$  and parameter size  $n_0$  is a list  $\{c_1, \ldots, c_{L+1}\}$  of arithmetic circuits over  $\mathbb{F}$  such that  $c_i$  has  $n_{i-1} + 2$  inputs and  $n_i + 3$  outputs. Let  $n_{L+1} = 1$ . The execution of an instruction is described in Algorithm 1.

| Algorithm 1 Instruction                                                                       |                                                                                        |

|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Input: Parameters param                                                                       |                                                                                        |

| Output: Address of next instruction                                                           |                                                                                        |

| $state_0 \leftarrow param$                                                                    |                                                                                        |

| $r_0 \leftarrow \bot$                                                                         |                                                                                        |

| for $i \in (1, \dots, L)$ do                                                                  |                                                                                        |

| Execute $c_i$ with input $(r_{i-1}, pc, state_{i-1})$ and output $(a_i, w_i, f_i, state_i)$ . |                                                                                        |

|                                                                                               | $\triangleright$  state <sub>i</sub>   = $n_i$ and  state <sub>i+1</sub>   = $n_{i+1}$ |

| $\mathbf{if}  t_i = Read  \mathbf{then}$                                                      |                                                                                        |

| $r_i \leftarrow$ the content of the data array at address $a_i$                               |                                                                                        |

| else                                                                                          |                                                                                        |

| $r_i \leftarrow \bot$                                                                         |                                                                                        |

| $\mathbf{if} \ f_i = 1 \ \mathbf{then}$                                                       |                                                                                        |

| Write $w_i$ to address $a_i$                                                                  |                                                                                        |

| $\mathbf{return}\ state_{L+1}$                                                                | $\triangleright  state_{L+1}  = 1$                                                     |

We will now explain our implementation in Table 2 using the instruction  $X_{X_i} \leftarrow X_j$ . The first circuit  $c_0$  gets as input the program counter a and the instruction parameters (i, j, k) as the state, and it outputs the address i to be read. The content of this address is then input to  $c_1$  as  $r_0$  in the state.  $c_1$  outputs the address j to be read and the state. The content of address j is stored as  $r_1$  in the state. The circuit  $c_2$  then requests  $r_1$  to be stored at address  $r_0$  (write flag 1). Finally,  $c_3$  simply advances the program counter by one. The first two memory accesses only require reading the memory for every instruction (if at all), and the last one writing. Hence,  $t_1 = \text{Read}$ ,  $t_2 = \text{Read}$ , and  $t_3 = \text{Write}$ .

**Theorem 2 (RAM model multiparty computation).** The oblivious machine allows the implementation of any RAM program in the model of Cook and Reckhow with the restriction that inputs are stored at the beginning of the execution and outputs are revealed at the end.

*Proof.* Let  $n_p = 3$  and L = 3. Table 2 shows the circuits to implement the first six instructions of Cook and Reckhow. Storing a constant, addition, and subtraction are done by using the relevant parameters (i, j, and k) as addresses and the constant, and indirect loading and storing by partially using previously loaded integers  $(r_1 \text{ and } possibly r_0)$  as addresses. The TRA instruction mainly uses the fact that the output of  $c_L$  is used as address of the next instruction. Finally, reading inputs and revealing outputs can be done using PrivateInput/PublicInput and PrivateOutput/PublicOutput, respectively.

**Private function evaluation.** Recall that private function evaluation (PFE) allows two parties, one knowing a function and the other knowing some data, to compute the function on the data without revealing either.  $\mathcal{F}_{machine}$  with private code input clearly facilitates this for functions formulated as a RAM-model computation. One party inputs the function using PrivateCode, and the other party inputs the data using PrivateData. The only leakage is the number of instructions computed. A malicious party can input a program

|                            | $c_0(\perp, a, (i, j, k))$         | $c_1(r_0, a, (i, j, k))$            | $c_2(r_1, a, (i, j, k, r_0))$                       | $c_3(\bot, a, (i, j, k, r_0, r_1))$ |

|----------------------------|------------------------------------|-------------------------------------|-----------------------------------------------------|-------------------------------------|

| $X_i \leftarrow C$         | $(\perp, \perp, \perp, (i, j, k))$ | $(\perp,\perp,\perp,(i,j,k,r_0))$   | $\left(i,C,1,\left(i,j,k,r_{0},r_{1}\right)\right)$ | (a+1)                               |

| $X_i \leftarrow X_j + X_k$ | $(j, \bot, \bot, (i, j, k))$       | $(k, \perp, \perp, (i, j, k, r_0))$ | $(i, r_0 + r_1, 1, (i, j, k, r_0, r_1))$            | (a+1)                               |

| $X_i \leftarrow X_j - X_k$ | $(j, \bot, \bot, (i, j, k))$       | $(k, \perp, \perp, (i, j, k, r_0))$ | $(i, r_0 - r_1, 1, (i, j, k, r_0, r_1))$            | (a+1)                               |

| $X_i \leftarrow X_{X_j}$   | $(j, \bot, \bot, (i, j, k))$       | $(r_0, \bot, \bot, (i, j, k, r_0))$ | $(i, r_1, 1, (i, j, k, r_0, r_1))$                  | (a+1)                               |

| $X_{X_i} \leftarrow X_j$   | $(i, \bot, \bot, (i, j, k))$       | $(j, \perp, \perp, (i, j, k, r_0))$ | $(r_0, r_1, 1, (i, j, k, r_0, r_1))$                | (a+1)                               |

| TRA <i>i</i> if $X_j > 0$  | $(j, \bot, \bot, (i, j, k))$       | $(\perp,\perp,\perp,(i,j,k,r_0))$   | $(\perp,\perp,0,(i,j,k,r_0,r_1))$                   | $(lfElse(r_0 > 0, i, a+1))$         |

Table 2. Implementation of the random access machine by Cook and Reckhow

that leaks some information through this number. However, we argue that this leakage is small compared to the amount of private data for practical scenarious because it only makes sense to use RAM model computation for larger data sets. Furthermore, if the parties reveal data at the end of the computation, a malicious party can input a program that leaks even more data there.

### 3.1 Implementation Using $\mathcal{F}_{ABBOA}$

We now propose protocol  $\mathcal{P}_{machine}$  in Figure 5 as an implementation of the oblivious machine using MPC with oblivious arrays. At the core of our protocol lies the execution of all possible instruction in line 8. The oblivious selection can be done multiplying the vector of results by a vector that contains 1 in one entry and 0 in the remaining entries. It is obvious that the protocol reveals the running time of the program. Note that the branching on  $t_i$  on line 9 does not reveal information because  $t_i$  is part of the instruction pattern, which is shared by all instructions.

**Theorem 3.**  $\mathcal{P}_{machine}$  implements  $\mathcal{F}_{machine}$  in the  $\mathcal{F}_{ABBOA}$ -hybrid model.

Proof (Sketch). The power of the corrupted parties in the protocol is very limited because it only consists of calls to  $\mathcal{F}_{ABBOA}$ , which only reacts if all parties input the same information. Furthermore,  $\mathcal{F}_{ABBOA}$  only reveals private data to any party in three situations. First, it does so so in the **Reveal** procedure, which corresponds to the same procedure of  $\mathcal{F}_{machine}$ . Second, the protocol reveals the result of comparison in line 1. Thirdly, it reveals if there is an access outside of array bounds. For these reasons, the simulator  $\mathcal{S}_{machine}$  in Figure 6 is relatively simple. The first revelation can be simulated because  $\mathcal{S}_{machine}$  learns the outputs of  $\mathcal{F}_{machine}$  to corrupted parties. For the second revelation, it receives (Tick) whenever  $\mathcal{F}_{machine}$ executes the loop body and (**Done**) after completion. Similarly, it receives all results of bounds checks. In the rest of the protocol, the adversary only learns handles, which  $\mathcal{S}_{machine}$  can generate like  $\mathcal{F}_{ABBOA}$  would. Hence, the view of the environment is indistinguishable.

Modeling the main loop with (Tick) and (Done) messages accounts for the fact that a program can run indefinitely. Otherwise, we would need to check whether a program halts on a given input, which is impossible for general programs due to the halting problem.

**Complexity.** The amount of communication and computation depends on the cost of accessing the oblivious array. Keller and Scholl [13] report an implementation based on Path ORAM [24] with access complexity in  $O(\log^3 N)$  for arrays of length N. Using this, the complexity of initializing the data and the code array has cost in  $O(n_c \log^3 n_c)$  and  $O(n_d \log^3 n_d)$ , respectively. The cost of running the machine is in  $O(T(\log^3 n_c + L(\log^3 n_d + n_I)))$  where T denotes the running time of the program and L denotes the number of memory accesses by instructions. In the following section, we will argue that L = 3 suffices to implement a machine that allows the compilation of arbitrary C code. Furthermore, we will show that  $n_I = 10$  different instructions suffice to implement a small program matching a regular expression. All in all, our implementation features about 30 possible instructions.

**Initialize:** Initialize  $\mathcal{F}_{ABBOA}$  for  $\mathbb{F}$  and initialize an oblivious array [D] of size  $n_d$  for the data. array [C] of size  $n_c \cdot (1 + n_p)$ and Public Code: Initialize an oblivious fill it with  $(c_0, \mathsf{param}_0), \ldots, (c_{n_c-1}, \mathsf{param}_{n_c-1}).$ **Private Code:** Initialize an oblivious array [C] of size  $n_c \cdot (1 + n_p)$  and fill itwith  $([c_0], [\mathsf{param}_0]), \ldots, ([c_{n_c-1}], [\mathsf{param}_{n_c-1}])$  input to the arithmetic black box  $\mathcal{F}_{ABB}$  by Party  $P_i$ . Public Data: Send  $(WriteArray([D], \mathcal{F}_{ABBOA}(PublicInput, a), \mathcal{F}_{ABBOA}(PublicInput, d),$  $\mathcal{F}_{ABBOA}(\mathsf{PublicInput}, 1))$  to  $\mathcal{F}_{ABBOA}$ . **Private Data:** Send (WriteArray( $[D], [a], [d], \mathcal{F}_{ABBOA}$ (PublicInput, 1)) to  $\mathcal{F}_{ABBOA}$ . **Run:** The parties execute the following: 1: while PublicOutput( $[pc] \neq \bot$ ) do Load  $([c_{pc}], [param_{pc}])$  from the oblivious code array. 2: 3:  $[r_{-1}] \leftarrow \bot$ 4:  $[\mathsf{state}_{-1}] \leftarrow [\mathsf{param}]$ 5:for i = 0, ..., L do 6: for  $j = 0, ..., n_I$  do 7: Execute  $c_i$  of instruction  $I_j$  on  $([r_{i-1}], [pc], [\mathsf{state}_{i-1}])$  in  $\mathcal{F}_{ABB}$  to get  $([a_j^i], [w_j^i], [f_j^i], [\mathsf{state}_j^i])$ .  $\text{Obliviously select the result } ([a_i^{c_{pc}}], [w_i^{c_{pc}}], [\mathsf{state}_i^{c_{pc}}]) \text{ as } ([a_i], [w_i], [f_i], [\mathsf{state}_i]).$ 8: if  $t_i = \text{Read then}$ 9: 10:  $[r_i] \leftarrow \mathcal{F}_{ABBOA}(\mathsf{ReadArray}, [a_i])$ 11:else12: $[r_i] \leftarrow \bot$ Send (WriteArray,  $[D], [a_i], [w_i], [f_i]$ ) to  $\mathcal{F}_{ABBOA}$ . 13:14:  $pc \leftarrow \mathsf{state}_L$ . **Reveal:** Instruct  $\mathcal{F}_{ABBOA}$  to open the *a*-th entry of the oblivious data array to Party  $P_i$ . Bounds Check: Check every data and instruction access against the size of the respective array and reveal the result. Abort if the check fails.

Fig. 5.

$$\mathcal{P}_{machine}$$

**Generally:** Emulate a copy of  $\mathcal{F}_{ABBOA}$  by generating handles and aborting  $\mathcal{F}_{machine}$  if the adversary demands so from  $\mathcal{F}_{ABBOA}$ .

**Run:** Whenever  $\mathcal{F}_{machine}$  sends (Tick), simulate the protocol for another step revealing 0 in line 1. If  $\mathcal{F}_{machine}$  sends (Done), reveal 1.

**Reveal:** If a corrupted party is due to receive data in the protocol, this is also the case in  $\mathcal{F}_{machine}$ . Simply forward it.

**Bounds Check:** Emulating  $\mathcal{F}_{ABBOA}$ , reveal the result according to (WithinBounds) or (OutOfBounds) received from  $\mathcal{F}_{machine}$ .

Fig. 6.  $S_{machine}$

# 4 Our Implementation

In this section, we will describe the details of our actual implementation. While the RAM model by Cook and Reckhow is powerful, more instructions are desirable to speed up computation. We begin by considering the differences between regular CPUs and our implementation.

Unlike in a regular CPU, there is no reason to have data registers because the memory has to be accessed in every step to maintain obliviousness. Therefore, all values are referred to by their addresses in the data array. The only register is the program counter referring the current instruction. Similarly, there is only one integer data type because having several types does not make sense in an oblivious execution. Because all possible instructions are executed at every step, any operation for a smaller integer type implies an operation for the larger type. Therefore, it is cheaper to execute the operation for the larger integer type only. This does not rule out the provision of floating point types. Since floating point operations are much more expensive than integer operations, and since they would have to be executed at every step, we did not implement floating point operations.

Our implementation only supports static memory allocation and no recursion due to the lack of stack pointer. However, there is no inherent reason for this limitation. The stack pointer could be implemented as another register. In such a scenario however, one has to define how to handle memory overflows. Making it public incurs the risk of leaking data while keeping it secret could lead to wasting time for a long computation on corrupted data.

Given the cost of ORAM accesses, the goal is to minimize the number thereof while still supporting all desired instructions. We found that three ORAM accesses, two reading and one writing, suffice for the the kind of instructions that classical processors support. Every such instruction can be described as a four-tuple consisting of an identification of the instruction and three parameters, which can be an address or constant depending on the instruction. Not all parameters need to have a semantic meaning for an instruction.

We use the instruction pattern (3, Read), (4, Read), (5, Write). The states are used to pass on the instructions parameters and the previously read values, that is,  $\text{state}_0 = \text{param}, \text{state}_1 = \text{param} + (r_0)$ , and  $\text{state}_2 = \text{param} + (r_0, r_1)$ . As in Table 2, all our instructions directly read the address specified by a parameter, which implies that  $c_0$  simply outputs the relevant parameter as  $a_i$ .

| Instruction         | Description                                                                                                         |

|---------------------|---------------------------------------------------------------------------------------------------------------------|

| mov x y O           | Copy the data at address y to address x.                                                                            |

| load x 0 z          | Copy the data at the address stored at address $z$ to address $x$ .                                                 |

| store O y z         | Copy the data at address $z$ to the address stored at address $y$ .                                                 |

| store_const x y 0   | Store the constant y at address x.                                                                                  |

| eq_const x y z      | Compare the number at address <b>z</b> to the constant <b>y</b> and store 1 at address <b>x</b> in case of equality |

|                     | and 0 otherwise.                                                                                                    |

| add_const x y z     | Add the number stored at address $z$ and the constant $y$ , and store the result at address $x$ .                   |

| ult_pos_const x y z | Test if the unsigned number at address $z$ is less than the positive constant $y$ and store 1 at                    |

|                     | address $\mathbf{x}$ if yes and 0 otherwise.                                                                        |

| ule_pos_const x y z | Test if the unsigned number at address $z$ is less or equal than the positive constant $y$ and                      |

|                     | store 1 at address $\mathbf{x}$ if yes and 0 otherwise.                                                             |

| jmp x O O           | Jump to the instruction at address $\mathbf{x}$ .                                                                   |

| $jmp_ind 0 0 z$     | Jump to the instruction at the address stored at $\mathbf{x}$ .                                                     |

| brxyz               | Jump to the instruction at address $\mathbf{x}$ if the number at address $\mathbf{z}$ is 1 and to the instruction   |

|                     | at address y if the number is 0. Undefined behaviour in any other case.                                             |

Fig. 7. Instructions used in Figures 10 and 17.

Figure 7 lists all instructions used in the example in Figure 17. The example represents a matching algorithm for the regular expression "ab\*[cd]" as explained in Section 5. To demonstrate our framework, we will now describe three instructions in detail.

We begin with "add\_const", which could be implemented combining  $X_i \leftarrow C$  and  $X_i \leftarrow X_j + X_k$ . However, we found that it is more efficient to have an extra instruction for adding a constant. As mentioned above,  $c_0$  is the same for all instructions and causes the address at parameter z being read to  $r_0$ .  $c_1$  only forwards the parameters and  $r_0$ , and  $c_2$  causes  $r_0 + y$  to be stored at address x.  $c_3$  causes the program to continue with the next instruction.

The "load" instruction corresponds to  $X_i \leftarrow X_{X_j}$  in Table 2. Again,  $c_0$  causes the address at parameter z being read to  $r_0$ .  $c_1$  then enables the dereferencing by causing the address  $r_0$  being read to  $r_1$ , and  $c_2$  causes  $r_1$  to being written at address x. Finally,  $c_3$  causes the execution to continue with the next instruction in the code memory.

Finally, the "br" instruction is similar to the TRA instruction in Table 2. It again starts with  $c_0$  causing the address z being read to  $r_0$ .  $c_1$  and  $c_2$  do nothing but forward the parameters and  $r_0$ .  $c_3$  then causes the execution to jump to either x or y in the code memory, depending on  $r_0$ . If Else denotes the selection circuit If Else $(c, a, b) = c \cdot (b - a) + a$ .

It is easy to see that our framework allows for most instructions one expects in a CPU because they fall in one of three categories represented by the above descriptions. Binary operations can be implemented similar to add\_const by loading the operands and storing the result, indirect memory are similar to load, and conditional and unconditional jumps can be specified similarly to br.

#### 4.1 Compilation

To compile C code, we use Clang from the LLVM project [25]. The LLVM project provides a modular compiler toolchain. Clang parses C code and can compile it to the LLVM internal representation. This representation consists of CPU-like instructions for an abstract CPU with indefinitely many registers.

We use a Python script to compile this internal representation for our machine. This allows to compile simple C programs without having to write an LLVM specification of our machine.

Since our machine does not support registers, the compiler has to allocate memory space for every register. For simplicity, every register is put in a separate space in memory. One could use static analysis to reduce the amount of space used.

We will now present a few examples of the compilation process. The first example is a "for" loop populating an array. As one would expect, the code is divided in five basic blocks: the code before the loop, the loop condition check, the loop body, the loop increment, and the code after the loop. The code for our machine contains less instructions than the LLVM code because the compiler gets rid of unnecessary instructions, such as jumping to the next instruction in the code and loading from memory to register. For the latter case, note that our machine does not support registers. The loop variable **i** is stored in position 8 in the memory, initialized to 0 and compared to the constant 5 in instruction 2. The result of this comparison goes to position 9 in memory, which is used by the branching instruction in instruction 3. Furthermore, memory position 10 holds the address of the array element accessed in the loop body. The array starts at position 3; hence, instruction 4 adds 3 to the loop variable to determine the address of the array element. The loop variable is then stored in the address by instruction 5. For incrementing, instruction 6 adds 1 to the loop variable and stores the result in position 11, which is then copied to position 8 by instruction 7. The execution then jumps back to the condition check in instruction 2.

```

1 int main() {

2     unsigned long a[5];

3     for (unsigned long i = 0; i < 5; i++)

4        a[i] = i;

5  }</pre>

```

Fig. 8. A "for" loop populating an array in C.

# 5 Efficient Private Regular Expression Matching with Minimal Leakage

Consider the problem of two parties wanting to decide whether a string known by one party matches a regular expression known by the other. A regular expression can be modelled by a finite state machine, which in turn can be implemented in C using mainly switch and goto statements. Bumbulis and Cowan [3] provide an implementation of such a compilation. Therefore, the oblivious machine solves the problem by the party holding the regular expression inputting an appropriate program using PrivateCode. In the full version, we will show an example of the resulting C, LLVM, and machine code.

```

1

define i32 @main() #0 {

\mathbf{2}

entry:

3

%retval = alloca i32, align 4

%a = alloca [5 x i64], align 16

4

5

%i = alloca i64, align 8

6

store i32 0, i32* %retval

\overline{7}

store i64 0, i64* %i, align 8

br label %for.cond

8

9

10

for.cond:

; preds = %for.inc, %entry

%0 = load i64* %i, align 8

11

12

%cmp = icmp ult i64 %0, 5

13

br i1 %cmp, label %for.body, label %for.end

14

15

for.body:

; preds = %for.cond

16

%1 = load i64* %i, align 8

17

%2 = load i64* %i, align 8

%arrayidx = getelementptr inbounds [5 x i64]* %a, i32 0, i64 %2

18

19

store i64 %1, i64* %arrayidx, align 8

20

br label %for.inc

21

22

for.inc:

; preds = %for.body

23

%3 = load i64* %i, align 8

%inc = add i64 %3, 1

24

25

store i64 %inc, i64* %i, align 8

26

br label %for.cond

27

28

; preds = %for.cond

for.end:

29

%4 = load i32* %retval

30

ret i32 %4

31

}

```

Fig. 9. A "for" loop populating an array in the LLVM intermediate representation.

```

1

# main()

\mathbf{2}

# entry:

3

store_const 2 0 0 # 0

store_const 8 0 0 # 1

4

5

# for.cond:

6

ult_pos_const 9 5 8 # 2

7

br 4 9 9 # 3

8

# for.body:

9

add_const 10 3 8 # 4

10

store 0 8 10 # 5

11

# for.inc:

12

add_const 11 1 8 # 6

13

mov 8 11 0 # 7

14

jmp 2 0 0 # 8

15

# for.end:

16

mov 0 2 0 # 9

17

jmp 11 0 0 # 10

```

Fig. 10. A "for" loop populating an array in our machine code.

#### 5.1 Complexity

Using Path ORAM for the oblivious arrays, loading the code and the input string takes time in  $O(n \log^3 n)$ in both cases with n denoting the code size and the input size, respectively. For the regular expression, this means quasi-linear time in the size of the finite state machine. The main execution then takes time in  $O(T(\log^3 n_c + \log^3 n_d))$  for T,  $n_c$ , and  $n_d$  denoting the running time of the machine, the code size, and the size of the input string, respectively. The running time is dominated the by the comparisons made by the C code. This depends both on the input data and the ordering of the comparison within a switch statement. However, T can be upper bounded by  $O(n_d n_m)$  where  $n_m$  denotes the maximum number of comparisons in a single switch statement, which in turn is less than the number of symbols. From a certain size of switch statements, it is more efficient to use branch tables instead of consecutive comparisons. In this case, the loading complexity of the particular switch statement is in  $O(n_s)$  for  $n_s$  being the number of symbols and the execution complexity is constant. We did not follow this avenue in our implementation, but point out that it would possible using the jmp\_ind instruction.

#### 5.2 Security

The oblivious machine leaks the running time T, which is linear in the number of the comparison performed and the size of the input string. The latter is public by the fact that the usage of the oblivious machine reveals the input size. However, the former depends on the regular expression, its precise compilation, and the input string. The party holding the regular expression could modify the switch statements such that they have constant size. However, this can come at considerable cost if they switch statements highly vary in size.

### 6 Experiments

In order to benchmark our construction, we have implemented it based on the so-called SPDZ scheme by Damgård et al. [8], which provides active security against an adversary corrupting all but one party. It works in the preprocessing model, that is, there is a data-independent offline phase in which correlated randomness is generated. In the case of SPDZ, the offline phase uses homomorphic encryption to generate secret sharings of random multiplicative triples (a, b, ab) in a finite field with some authentication. The online phase then uses the correlated randomness to compute the product of actual inputs.

In our implementation, we use 64-bit integers as subset of  $\mathbb{F}_p$  for a 128-bit prime p. The gap is necessary to accommodate for the statistically secure bit decomposition protocol with security parameter 40.

Figure 11 shows the online phase clock rate for a minimal program that is executed with varying sizes of the data memory. The offline phase is about in magnitude of a 1000 times slower. However, it is highly parallelizable, that is, it can distributed among several machines, which does not hold for the online phase.

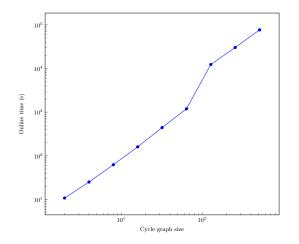

# 6.1 Comparison with Purely Using Oblivious Arrays

In order to compare the performance of the oblivious machine with programs implemented using oblivious arrays directly, we have benchmarked Dijkstra's algorithm using our toolchain. The results in Figure 12 suggest that using the oblivious machine instead of the implementation by Keller and Scholl is about 100 times slower. However, the comparison is not entirely fair because the previous implementation leaks the algorithm being computed whereas the oblivious machine does not. In other words, the price to pay to hide the computation is a factor of 100 in this case.

#### 6.2 Regular Expression Matching

We have implemented our protocol for regular expression matching for a string of length 1024 and randomly generated regular expressions of varying complexity. Figure 13 shows our results. We found that the total

Fig. 11. Online phase clock rate of the machine.

Fig. 12. Dijkstra's algorithm on cycle graphs.

number of transitions is the most appropriate measure for the complexity of a finite state machine. This coincides with the number of comparisons in the machine code. At more than ten thousand transitions, loading the code becomes the dominant part of the computation. However, if several strings are to be matched to the same regular expression, this is a one-off cost. Table 3 shows the smaller expressions we used for our experiments.

Fig. 13. Regular expression matching online time.

| FSM Size Regular Expression |

|-----------------------------|

|-----------------------------|

| 10  | [ZrqupR]                        |

|-----|---------------------------------|

| 32  | [aYoNPCI70] [Lxdo] [3jH17]      |

| 70  | (([x2YUux] [FEb6o])([ssUWGaGuD] |

|     | ?)?)[n0][LwhCA][Y0rp6xc]WkaNjg5 |

|     | M                               |

| 98  | [P]([z0xwIv48]+)([IEm][^isgQn4B |

|     | ]*)                             |

| 161 | ([M] (XP[t]*))[s1UW8XiVe][iTS2Y |

|     | 86E][ykSh9uE][fAu]9T0g(Umks(do( |

|     | [^t] [PEv3e5])+)e62e[iI1]*)     |

|     | •                               |

Table 3. Regular expressions used in our experiments.

# 7 Conclusion and Future Directions

We have presented a theoretical model for multiparty RAM computation, a concrete protocol, and an implementation as well as an application in the form of private regular expression matching. As future direction we suggest research into quantifying the leakage by the running time of a RAM program. This would allow to navigate the trade-off between the fastest execution of a program with leakage and the overhead by adding padding operations to programs in order to hide the number of comparisons in our regular expression matching scheme for example.

Our experiments have shown that the oblivious machine runs at a few Hertz for larger data memory size, which is about a billion times slower than a regular CPU. Obviously, one cannot hope to achieve a similar

speed, but recent ORAM schemes optimized for circuit implementation should allow to improve at least one or two orders of magnitude. Another issue is the round complexity of secret-sharing-based MPC schemes, which is linear in the circuit rounds. Analyzing our implementation, we come to the conclusion that this is the bottleneck. Two-party computation based on Yao's garbled circuits does not suffer from this because it has constant rounds. However, implementations using garbled circuits do not necessarily beat the ones secret sharing [6]. It remains to be seen which approach is more efficient.

### Acknowledgments

We would like to thank Peter Scholl for various comments and suggestions. This work has been supported in part by EPSRC via grant EP/I03126X.

# References

- 1. BEN-OR, M., GOLDWASSER, S., AND WIGDERSON, A. Completeness theorems for non-cryptographic faulttolerant distributed computation (extended abstract). In Simon [23], pp. 1–10.

- BEN-SASSON, E., CHIESA, A., GENKIN, D., TROMER, E., AND VIRZA, M. Snarks for C: verifying program executions succinctly and in zero knowledge. In Advances in Cryptology - CRYPTO 2013 - 33rd Annual Cryptology Conference, Santa Barbara, CA, USA, August 18-22, 2013. Proceedings, Part II (2013), R. Canetti and J. A. Garay, Eds., vol. 8043 of Lecture Notes in Computer Science, Springer, pp. 90–108.

- BUMBULIS, P., AND COWAN, D. D. RE2C a more versatile scanner generator. ACM Lett. Program. Lang. Syst 2 (1994), 70–84.

- CHAUM, D., CRÉPEAU, C., AND DAMGÅRD, I. Multiparty unconditionally secure protocols (extended abstract). In Simon [23], pp. 11–19.

- 5. COOK, S. A., AND RECKHOW, R. A. Time bounded random access machines. J. Comput. Syst. Sci. 7, 4 (1973), 354–375.

- DAMGÅRD, I., KELLER, M., LARRAIA, E., MILES, C., AND SMART, N. P. Implementing AES via an actively/covertly secure dishonest-majority MPC protocol. In Security and Cryptography for Networks - 8th International Conference, SCN 2012, Amalfi, Italy, September 5-7, 2012. Proceedings (2012), I. Visconti and R. D. Prisco, Eds., vol. 7485 of Lecture Notes in Computer Science, Springer, pp. 241–263.

- DAMGÅRD, I., MELDGAARD, S., AND NIELSEN, J. B. Perfectly secure oblivious RAM without random oracles. In *Theory of Cryptography*. Springer, 2011, pp. 144–163.

- DAMGÅRD, I., PASTRO, V., SMART, N. P., AND ZAKARIAS, S. Multiparty computation from somewhat homomorphic encryption. In Advances in Cryptology – CRYPTO 2012 (2012), R. Safavi-Naini and R. Canetti, Eds., vol. 7417 of Lecture Notes in Computer Science, Springer, pp. 643–662.

- GENTRY, C., HALEVI, S., JUTLA, C., AND RAYKOVA, M. Private database access with HE-over-ORAM architecture. Cryptology ePrint Archive, Report 2014/345, 2014. http://eprint.iacr.org/2014/345.

- GENTRY, C., HALEVI, S., LU, S., OSTROVSKY, R., RAYKOVA, M., AND WICHS, D. Garbled RAM revisited. In *EUROCRYPT* (2014), P. Q. Nguyen and E. Oswald, Eds., vol. 8441 of *Lecture Notes in Computer Science*, Springer, pp. 405–422.

- GOLDREICH, O., MICALI, S., AND WIGDERSON, A. How to play any mental game or A completeness theorem for protocols with honest majority. In *Proceedings of the 19th Annual ACM Symposium on Theory of Computing*, 1987, New York, New York, USA (1987), A. V. Aho, Ed., ACM, pp. 218–229.

- GORDON, S. D., KATZ, J., KOLESNIKOV, V., KRELL, F., MALKIN, T., RAYKOVA, M., AND VAHLIS, Y. Secure two-party computation in sublinear (amortized) time. In ACM Conference on Computer and Communications Security (2012), T. Yu, G. Danezis, and V. D. Gligor, Eds., ACM, pp. 513–524.

- 13. KELLER, M., AND SCHOLL, P. Efficient, oblivious data structures for MPC. In Sarkar and Iwata [21], pp. 506–525.

- KERSCHBAUM, F. Practical private regular expression matching. In Security and Privacy in Dynamic Environments, S. Fischer-Hübner, K. Rannenberg, L. Yngström, and S. Lindskog, Eds., vol. 201 of IFIP International Federation for Information Processing. Springer US, 2006, pp. 461–470.

- LAUNCHBURY, J., ARCHER, D., DUBUISSON, T., AND MERTENS, E. Application-scale secure multiparty computation. In *Programming Languages and Systems*, Z. Shao, Ed., vol. 8410 of *Lecture Notes in Computer Science*. Springer Berlin Heidelberg, 2014, pp. 8–26.

- LINDELL, Y., AND PINKAS, B. A proof of security of Yao's protocol for two-party computation. J. Cryptology 22, 2 (2009), 161–188.

- LIU, C., HUANG, Y., SHI, E., KATZ, J., AND HICKS, M. Automating efficient RAM-model secure computation. In Proceedings of the 2014 IEEE Symposium on Security and Privacy (Washington, DC, USA, 2014), SP '14, IEEE Computer Society, pp. 623–638.

- MOHASSEL, P., SADEGHIAN, S. S., AND SMART, N. P. Actively secure private function evaluation. In Sarkar and Iwata [21], pp. 486–505.

- 19. OSTROVSKY, R., AND SHOUP, V. Private information storage. In Proceedings of the twenty-ninth annual ACM symposium on Theory of computing (1997), ACM, pp. 294–303.

- 20. PIPPENGER, N., AND FISCHER, M. J. Relations among complexity measures. J. ACM 26, 2 (1979), 361-381.

- SARKAR, P., AND IWATA, T., Eds. Advances in Cryptology ASIACRYPT 2014 20th International Conference on the Theory and Application of Cryptology and Information Security, Kaoshiung, Taiwan, R.O.C., December 7-11, 2014, Proceedings, Part II (2014), vol. 8874 of Lecture Notes in Computer Science, Springer.

- 22. SHI, E., CHAN, T.-H. H., STEFANOV, E., AND LI, M. Oblivious RAM with O((logN)<sup>3</sup>) worst-case cost. In Advances in Cryptology-ASIACRYPT 2011. Springer, 2011, pp. 197–214.

- SIMON, J., Ed. Proceedings of the 20th Annual ACM Symposium on Theory of Computing, May 2-4, 1988, Chicago, Illinois, USA (1988), ACM.

- STEFANOV, E., VAN DIJK, M., SHI, E., FLETCHER, C. W., REN, L., YU, X., AND DEVADAS, S. Path ORAM: an extremely simple oblivious RAM protocol. In *ACM Conference on Computer and Communications Security* (2013), A.-R. Sadeghi, V. D. Gligor, and M. Yung, Eds., ACM, pp. 299–310.

- 25. THE LLVM PROJECT. clang: a C language family frontend for LLVM. http://clang.llvm.org/.

- WANG, X. S., HUANG, Y., CHAN, T. H., SHELAT, A., AND SHI, E. SCORAM: oblivious RAM for secure computation. In Proceedings of the 2014 ACM SIGSAC Conference on Computer and Communications Security, Scottsdale, AZ, USA, November 3-7, 2014 (2014), pp. 191–202.

# A Regular Expression Example

For the regular expression **ab\*[de]**, Figures 14 to 17 show its implementation as C code, LLVM intermediate representation, and instruction code for the oblivious machine.

```

long match(char* YYCURSOR) {

1

\mathbf{2}

char* YYMARKER;

3

4

while (1)

5

{

6

char yych;

7

8

yych = *YYCURSOR;

9

switch (yych) {

10

case 'a': goto yy2;

default: goto yy5;

11

12

}

13

yy2:

14

++YYCURSOR;

15

yych = *YYCURSOR;

16

switch (yych) {

case 'b': goto yy2;

17

case 'c':

18

case 'd': goto yy7;

19

default: goto yy4;

20

21

}

22

yy4:

23

уу5:

24

++YYCURSOR;

25

{ return 0; }

26

уу7:

27

++YYCURSOR;

28

{ return 1; }

29

}

30

}

```

Fig. 14. The regular expression "ab\*[de]" compiled to C

```

1

define i64 @match(i64* %YYCURSOR) #0 {

2

entry:

3

%retval = alloca i64, align 8

4

%YYCURSOR.addr = alloca i64*, align 8

5

%YYMARKER = alloca i64*, align 8

%yych = alloca i64, align 8

6

\overline{7}

store i64* %YYCURSOR, i64** %YYCURSOR.addr, align 8

8

br label %while.body

9

10

while.body:

; preds = %entry

%0 = load i64** %YYCURSOR.addr, align 8

11

12

%1 = load i64* %0, align 8

13

store i64 %1, i64* %yych, align 8

14

%2 = load i64* %yych, align 8

15

br label %LeafBlock

16

17

LeafBlock:

; preds = %while.body

18

%SwitchLeaf = icmp eq i64 %2, 97

19

br i1 %SwitchLeaf, label %sw.bb, label %NewDefault

20

21

sw.bb:

; preds = %LeafBlock

22

br label %yy2

23

24

NewDefault:

; preds = %LeafBlock

25

br label %sw.default

26

27

sw.default:

; preds = %NewDefault

28

br label %yy5

29

30

yy2:

; preds = %sw.bb1, %sw.bb

31

%3 = load i64** %YYCURSOR.addr, align 8

32

%incdec.ptr = getelementptr inbounds i64* %3, i32 1

store i64* %incdec.ptr, i64** %YYCURSOR.addr, align 8

33

34

%4 = load i64** %YYCURSOR.addr, align 8

%5 = load i64* %4, align 8

35

store i64 %5, i64* %yych, align 8

36

37

%6 = load i64* %yych, align 8

br label %NodeBlock

38

```

Fig. 15. The regular expression "ab\*[de]" compiled to LLVM code (part one)

```

1

NodeBlock:

; preds = %yy2

\mathbf{2}

%Pivot = icmp ult i64 %6, 99

3

br i1 %Pivot, label %LeafBlock2, label %LeafBlock4

4

5

LeafBlock4:

; preds = %NodeBlock

6

%.off = add i64 %6, -99

7

%SwitchLeaf5 = icmp ule i64 %.off, 1

8

br i1 %SwitchLeaf5, label %sw.bb2, label %NewDefault1

9

10

LeafBlock2:

; preds = %NodeBlock

%SwitchLeaf3 = icmp eq i64 %6, 98

11

12

br i1 %SwitchLeaf3, label %sw.bb1, label %NewDefault1

13

sw.bb1:

; preds = %LeafBlock2

14

br label %yy2

15

16

17

sw.bb2:

; preds = %LeafBlock4

18

br label %yy7

19

20

NewDefault1:

; preds = LeafBlock2, \leftrightarrow

%LeafBlock4

21

br label %sw.default3

22

23

sw.default3:

; preds = %NewDefault1

24

br label %yy4

25

26

; preds = %sw.default3

yy4:

27

br label %yy5

28

29

; preds = %yy4, %sw. \leftrightarrow

уу5:

default

30

%7 = load i64** %YYCURSOR.addr, align 8

31

%incdec.ptr4 = getelementptr inbounds i64* %7, i32 1

32

store i64* %incdec.ptr4, i64** %YYCURSOR.addr, align 8

33

store i64 0, i64* %retval

34

br label %return

35

36

уу7:

; preds = %sw.bb2

37

%8 = load i64** %YYCURSOR.addr, align 8

%incdec.ptr5 = getelementptr inbounds i64* %8, i32 1

38

store i64* %incdec.ptr5, i64** %YYCURSOR.addr, align 8

39

40

store i64 1, i64* %retval

41

br label %return

42

43

return:

; preds = %yy7, %yy5

44

%9 = load i64* %retval

45

ret i64 <mark>%9</mark>

46

}

```

Fig. 16. The regular expression "ab\*[de]" compiled to LLVM code (part two)

```

1

# match()

\mathbf{2}

# entry:

3

mov 1028 1026 0 # 0

4

# while.body:

load 1031 0 1028 # 1

5

mov 1030 1031 0 # 2

6

7

# LeafBlock:

eq_const 1032 97 1030 # 3

8

br 5 16 1032 # 4

9

10

# yy2:

11

add_const 1033 1 1028 # 5

12

mov 1028 1033 0 # 6

13

load 1034 0 1028 # 7

14

mov 1030 1034 0 # 8

15

# NodeBlock:

ult_pos_const 1035 99 1030 # 9

16

17

br 14 11 1035 # 10

18

# LeafBlock4:

19

add_const 1036 -99 1030 # 11

ule_pos_const 1037 1 1036 # 12

20

21

br 20 16 1037 # 13

22

# LeafBlock2:

23

eq_const 1038 98 1030 # 14

24

br 5 16 1038 # 15

25

# yy5:

26

add_const 1039 1 1028 # 16

27

mov 1028 1039 0 # 17

28

store_const 1027 0 0 # 18

29

jmp 23 0 0 # 19

30

# yy7:

31

add_const 1040 1 1028 # 20

32

mov 1028 1040 0 # 21

33

store_const 1027 1 0 # 22

34

# return:

35

mov 1024 1027 0 # 23

36

jmp_ind 0 0 1025 # 24

```

Fig. 17. The regular expression "ab\*[de]" compiled for the oblivious machine