# Intel SGX Explained

Victor Costan and Srinivas Devadas victor@costan.us, devadas@mit.edu Computer Science and Artificial Intelligence Laboratory Massachusetts Institute of Technology

# ABSTRACT

Intel's Software Guard Extensions (SGX) is a set of extensions to the Intel architecture that aims to provide integrity and confidentiality guarantees to securitysensitive computation performed on a computer where all the privileged software (kernel, hypervisor, etc) is potentially malicious.

This paper analyzes Intel SGX, based on the 3 papers [14, 79, 139] that introduced it, on the Intel Software Developer's Manual [101] (which supersedes the SGX manuals [95, 99]), on an ISCA 2015 tutorial [103], and on two patents [110, 138]. We use the papers, reference manuals, and tutorial as primary data sources, and only draw on the patents to fill in missing information.

This paper does not reflect the information available in two papers [74, 109] that were published after the first version of this paper.

This paper's contributions are a summary of the Intel-specific architectural and micro-architectural details needed to understand SGX, a detailed and structured presentation of the publicly available information on SGX, a series of intelligent guesses about some important but undocumented aspects of SGX, and an analysis of SGX's security properties.

# **1 OVERVIEW**

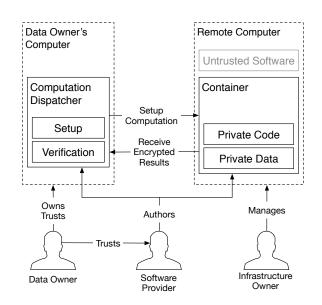

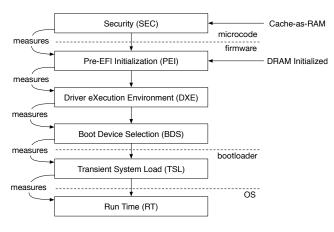

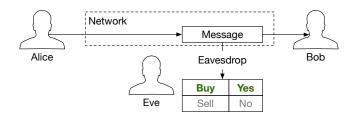

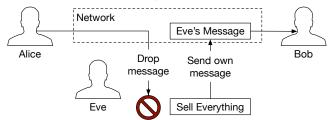

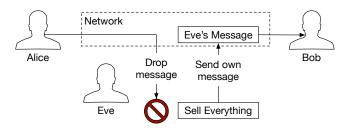

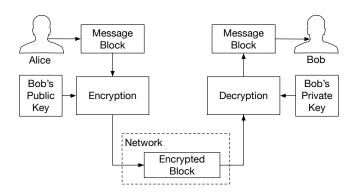

Secure remote computation (Figure 1) is the problem of executing software on a remote computer **owned and maintained by an untrusted party**, with some integrity and confidentiality guarantees. In the general setting, secure remote computation is an unsolved problem. Fully Homomorphic Encryption [61] solves the problem for a limited family of computations, but has an impractical performance overhead [140].

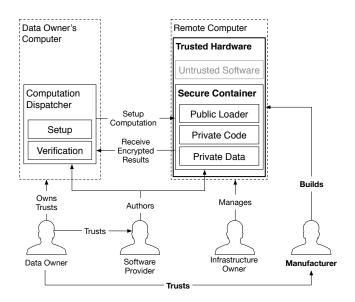

Intel's Software Guard Extensions (SGX) is the latest iteration in a long line of trusted computing (Figure 2) designs, which aim to solve the secure remote computation problem by leveraging trusted hardware in the remote computer. The trusted hardware establishes a secure container, and the remote computation service user

**Figure 1**: Secure remote computation. A user relies on a remote computer, owned by an untrusted party, to perform some computation on her data. The user has some assurance of the computation's integrity and confidentiality.

uploads the desired computation and data into the secure container. The trusted hardware protects the data's confidentiality and integrity while the computation is being performed on it.

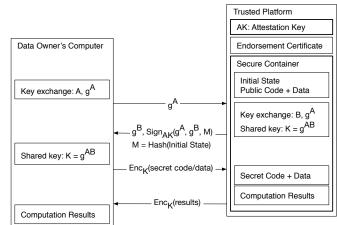

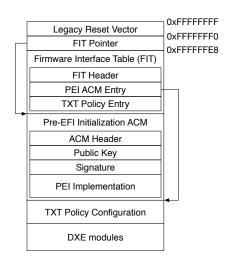

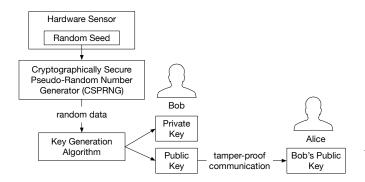

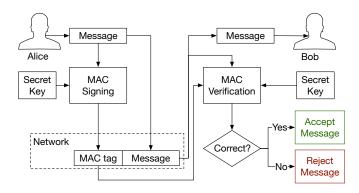

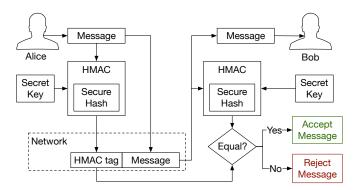

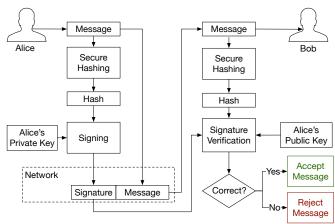

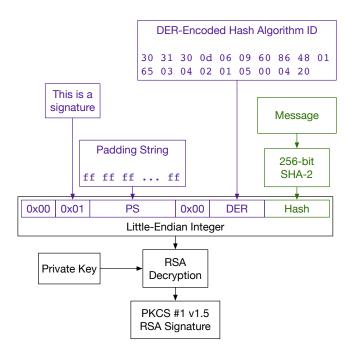

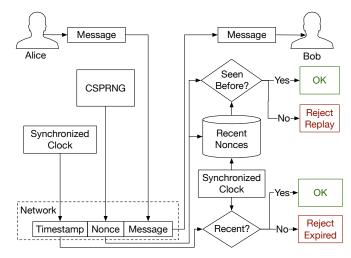

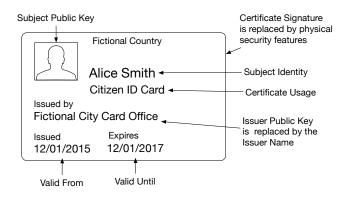

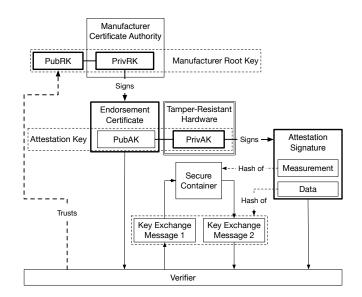

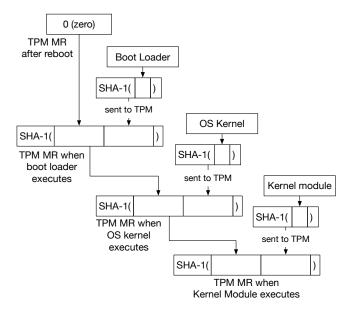

SGX relies on *software attestation*, like its predecessors, the TPM [71] and TXT [70]. Attestation (Figure 3) proves to a user that she is communicating with a specific piece of software running in a secure container hosted by the trusted hardware. The proof is a cryptographic signature that certifies the hash of the secure container's contents. It follows that the remote computer's owner can load any software in a secure container, but the remote computation service user will refuse to load her data into a secure container whose contents' hash does not match the expected value.

The remote computation service user verifies the *at*testation key used to produce the signature against an *endorsement certificate* created by the trusted hardware's manufacturer. The certificate states that the attestation key is only known to the trusted hardware, and only used

**Figure 2**: Trusted computing. The user trusts the manufacturer of a piece of hardware in the remote computer, and entrusts her data to a secure container hosted by the secure hardware.

for the purpose of attestation.

SGX stands out from its predecessors by the amount of code covered by the attestation, which is in the Trusted Computing Base (TCB) for the system using hardware protection. The attestations produced by the original TPM design covered all the software running on a computer, and TXT attestations covered the code inside a VMX [181] virtual machine. In SGX, an *enclave* (secure container) only contains the private data in a computation, and the code that operates on it.

For example, a cloud service that performs image processing on confidential medical images could be implemented by having users upload encrypted images. The users would send the encryption keys to software running inside an enclave. The enclave would contain the code for decrypting images, the image processing algorithm, and the code for encrypting the results. The code that receives the uploaded encrypted images and stores them would be left outside the enclave.

An SGX-enabled processor protects the integrity and confidentiality of the computation inside an enclave by isolating the enclave's code and data from the outside environment, including the operating system and hypervisor, and hardware devices attached to the system bus. At the same time, the SGX model remains compatible with the traditional software layering in the Intel architecture, where the OS kernel and hypervisor manage the computer's resources.

This work discusses the original version of SGX, also referred to as SGX 1. While SGX 2 brings very useful

**Figure 3**: Software attestation proves to a remote computer that it is communicating with a specific secure container hosted by a trusted platform. The proof is an attestation signature produced by the platform's secret attestation key. The signature covers the container's initial state, a challenge nonce produced by the remote computer, and a message produced by the container.

improvements for enclave authors, it is a small incremental improvement, from a design and implementation standpoint. After understanding the principles behind SGX 1 and its security properties, the reader should be well equipped to face Intel's reference documentation and learn about the changes brought by SGX 2.

# 1.1 SGX Lightning Tour

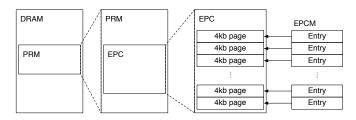

SGX sets aside a memory region, called the *Processor Reserved Memory* (PRM, § 5.1). The CPU protects the PRM from all non-enclave memory accesses, including kernel, hypervisor and SMM (§ 2.3) accesses, and DMA accesses (§ 2.9.1) from peripherals.

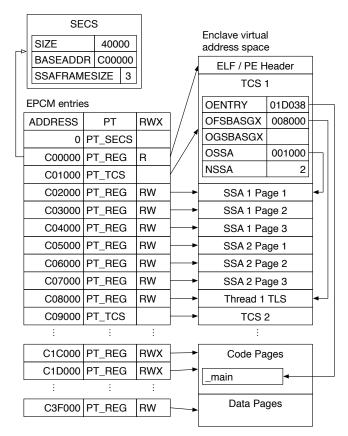

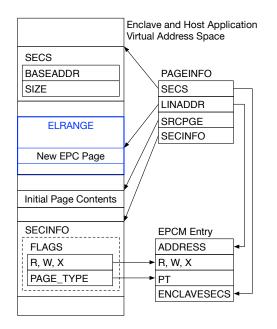

The PRM holds the *Enclave Page Cache* (EPC, § 5.1.1), which consists of 4 KB pages that store enclave code and data. The system software, which is untrusted, is in charge of assigning EPC pages to enclaves. The CPU tracks each EPC page's state in the *Enclave Page Cache Metadata* (EPCM, § 5.1.2), to ensure that each EPC page belongs to exactly one enclave.

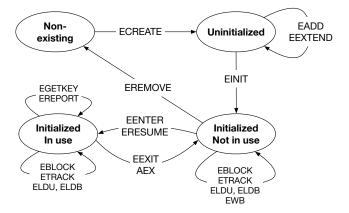

The initial code and data in an enclave is loaded by untrusted system software. During the loading stage (§ 5.3), the system software asks the CPU to copy data from unprotected memory (outside PRM) into EPC pages, and assigns the pages to the enclave being setup (§ 5.1.2). It follows that the initial enclave state is known to the system software.

After all the enclave's pages are loaded into EPC, the system software asks the CPU to mark the enclave as initialized ( $\S$  5.3), at which point application software can run the code inside the enclave. After an enclave is

initialized, the loading method described above is disabled.

While an enclave is loaded, its contents is cryptographically hashed by the CPU. When the enclave is initialized, the hash is finalized, and becomes the enclave's *measurement hash* ( $\S$  5.6).

A remote party can undergo a *software attestation* process ( $\S$  5.8) to convince itself that it is communicating with an enclave that has a specific measurement hash, and is running in a secure environment.

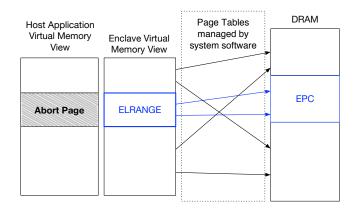

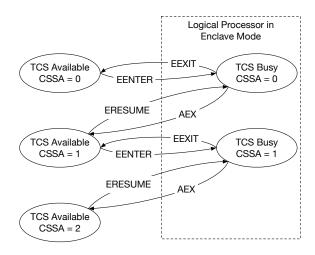

Execution flow can only enter an enclave via special CPU instructions (§ 5.4), which are similar to the mechanism for switching from user mode to kernel mode. Enclave execution always happens in protected mode, at ring 3, and uses the address translation set up by the OS kernel and hypervisor.

To avoid leaking private data, a CPU that is executing enclave code does not directly service an interrupt, fault (e.g., a page fault) or VM exit. Instead, the CPU first performs an Asynchronous Enclave Exit (§ 5.4.3) to switch from enclave code to ring 3 code, and then services the interrupt, fault, or VM exit. The CPU performs an AEX by saving the CPU state into a predefined area inside the enclave and transfers control to a pre-specified instruction outside the enclave, replacing CPU registers with synthetic values.

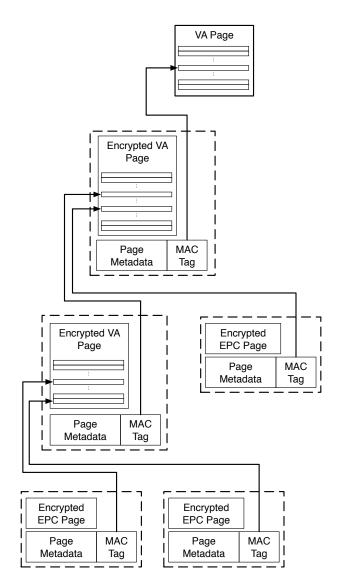

The allocation of EPC pages to enclaves is delegated to the OS kernel (or hypervisor). The OS communicates its allocation decisions to the SGX implementation via special ring 0 CPU instructions (§ 5.3). The OS can also evict EPC pages into untrusted DRAM and later load them back, using dedicated CPU instructions. SGX uses cryptographic protections to assure the confidentiality, integrity and freshness of the evicted EPC pages while they are stored in untrusted memory.

### 1.2 Outline and Troubling Findings

Reasoning about the security properties of Intel's SGX requires a significant amount of background information that is currently scattered across many sources. For this reason, a significant portion of this work is dedicated to summarizing this prerequisite knowledge.

Section 2 summarizes the relevant subset of the Intel architecture and the micro-architectural properties of recent Intel processors. Section 3 outlines the security landscape around trusted hardware system, including cryptographic tools and relevant attack classes. Last, section 4 briefly describes the trusted hardware systems that make up the context in which SGX was created. After having reviewed the background information, section 5 provides a (sometimes painstakingly) detailed description of SGX's programming model, mostly based on Intel's Software Development Manual.

Section 6 analyzes other public sources of information, such as Intel's SGX-related patents, to fill in some of the missing details in the SGX description. The section culminates in a detailed review of SGX's security properties that draws on information presented in the rest of the paper. This review outlines some troubling gaps in SGX's security guarantees, as well as some areas where no conclusions can be drawn without additional information from Intel.

That being said, perhaps the most troubling finding in our security analysis is that Intel added a launch control feature to SGX that forces each computer's owner to gain approval from a third party (which is currently Intel) for any enclave that the owner wishes to use on the computer. § 5.9 explains that the only publicly documented intended use for this launch control feature is a licensing mechanism that requires software developers to enter a (yet unspecified) business agreement with Intel to be able to author software that takes advantage of SGX's protections. All the official documentation carefully sidesteps this issue, and has a minimal amount of hints that lead to the Intel's patents on SGX. Only these patents disclose the existence of licensing plans.

The licensing issue might not bear much relevance right now, because our security analysis reveals that the limitations in SGX's guarantees mean that a securityconscious software developer cannot in good conscience rely on SGX for secure remote computation. At the same time, should SGX ever develop better security properties, the licensing scheme described above becomes a major problem, given Intel's near-monopoly market share of desktop and server CPUs. Specifically, the licensing limitations effectively give Intel the power to choose winners and losers in industries that rely on cloud computing.

# 2 COMPUTER ARCHITECTURE BACK-GROUND

This section attempts to summarize the general architectural principles behind Intel's most popular computer processors, as well as the peculiarities needed to reason about the security properties of a system running on these processors. Unless specified otherwise, the information here is summarized from Intel's *Software Development Manual* (SDM) [101].

Analyzing the security of a software system requires

understanding the interactions between all the parts of the software's execution environment, so this section is quite long. We do refrain from introducing any security concepts here, so readers familiar with x86's intricacies can safely skip this section and refer back to it when necessary.

We use the terms *Intel processor* or *Intel CPU* to refer to the server and desktop versions of Intel's Core lineup. In the interest of space and mental sanity, we ignore Intel's other processors, such as the embedded line of Atom CPUs, or the failed Itanium line. Consequently, the terms *Intel computers* and *Intel systems* refers to computer systems built around Intel's Core processors.

In this paper, the term *Intel architecture* refers to the x86 architecture described in Intel's SDM. The x86 architecture is overly complex, mostly due to the need to support executing legacy software dating back to 1990 directly on the CPU, without the overhead of software interpretation. We only cover the parts of the architecture visible to modern 64-bit software, also in the interest of space and mental sanity.

The 64-bit version of the x86 architecture, covered in this section, was actually invented by Advanced Micro Devices (AMD), and is also known as AMD64,  $x86_64$ , and x64. The term "Intel architecture" highlights our interest in the architecture's implementation in Intel's chips, and our desire to understand the mindsets of Intel SGX's designers.

#### 2.1 Overview

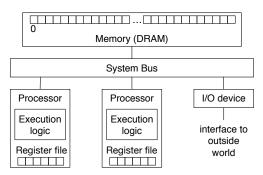

A computer's main resources (§ 2.2) are *memory* and *processors*. On Intel computers, *Dynamic Random*-*Access Memory* (DRAM) chips (§ 2.9.1) provide the memory, and one or more CPU chips expose *logical processors* (§ 2.9.4). These resources are managed by *system software*. An Intel computer typically runs two kinds of system software, namely operating systems and hypervisors.

The Intel architecture was designed to support running multiple application software instances, called *processes*. An *operating system* (§ 2.3), allocates the computer's resources to the running processes. Server computers, especially in cloud environments, may run multiple operating system instances at the same time. This is accomplished by having a *hypervisor* (§ 2.3) partition the computer's resources between the operating system instances running on the computer.

System software uses virtualization techniques to isolate each piece of software that it manages (process or operating system) from the rest of the software running on the computer. This isolation is a key tool for keeping software complexity at manageable levels, as it allows application and OS developers to focus on their software, and ignore the interactions with other software that may run on the computer.

A key component of virtualization is address translation (§ 2.5), which is used to give software the impression that it owns all the memory on the computer. Address translation provides isolation that prevents a piece of buggy or malicious software from directly damaging other software, by modifying its memory contents.

The other key component of virtualization is the software privilege levels (§ 2.3) enforced by the CPU. Hardware privilege separation ensures that a piece of buggy or malicious software cannot damage other software indirectly, by interfering with the system software managing it.

Processes express their computing power requirements by creating execution *threads*, which are assigned by the operating system to the computer's logical processors. A thread contains an execution context (§ 2.6), which is the information necessary to perform a computation. For example, an execution context stores the address of the next instruction that will be executed by the processor.

Operating systems give each process the illusion that it has an infinite amount of logical processors at its disposal, and multiplex the available logical processors between the threads created by each process. Modern operating systems implement *preemptive multithreading*, where the logical processors are rotated between all the threads on a system every few milliseconds. Changing the thread assigned to a logical processor is accomplished by an execution context switch (§ 2.6).

Hypervisors expose a fixed number of virtual processors (vCPUs) to each operating system, and also use context switching to multiplex the logical CPUs on a computer between the vCPUs presented to the guest operating systems.

The execution core in a logical processor can execute instructions and consume data at a much faster rate than DRAM can supply them. Many of the complexities in modern computer architectures stem from the need to cover this speed gap. Recent Intel CPUs rely on hyper-threading ( $\S$  2.9.4), out-of-order execution ( $\S$  2.10), and caching ( $\S$  2.11), all of which have security implications.

An Intel processor contains many levels of intermediate memories that are much faster than DRAM, but also orders of magnitude smaller. The fastest intermediate memory is the logical processor's register file (§ 2.2, § 2.4, § 2.6). The other intermediate memories are called caches (§ 2.11). The Intel architecture requires application software to explicitly manage the register file, which serves as a high-speed scratch space. At the same time, caches transparently accelerate DRAM requests, and are mostly invisible to software.

Intel computers have multiple logical processors. As a consequence, they also have multiple caches distributed across the CPU chip. On multi-socket systems, the caches are distributed across multiple CPU chips. Therefore, Intel systems use a cache coherence mechanism (§ 2.11.3), ensuring that all the caches have the same view of DRAM. Thanks to cache coherence, programmers can build software that is unaware of caching, and still runs correctly in the presence of distributed caches. However, cache coherence does not cover the dedicated caches used by address translation (§ 2.11.5), and system software must take special measures to keep these caches consistent.

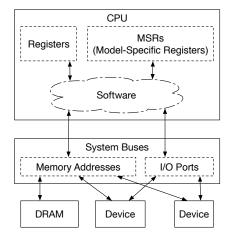

CPUs communicate with the outside world via I/O devices (also known as peripherals), such as network interface cards and display adapters (§ 2.9). Conceptually, the CPU communicates with the DRAM chips and the I/O devices via a *system bus* that connects all these components.

Software written for the Intel architecture communicates with I/O devices via the I/O address space (§ 2.4) and via the memory address space, which is primarily used to access DRAM. System software must configure the CPU's caches (§ 2.11.4) to recognize the memory address ranges used by I/O devices. Devices can notify the CPU of the occurrence of events by dispatching interrupts (§ 2.12), which cause a logical processor to stop executing its current thread, and invoke a special handler in the system software (§ 2.8.2).

Intel systems have a highly complex computer initialization sequence (§ 2.13), due to the need to support a large variety of peripherals, as well as a multitude of operating systems targeting different versions of the architecture. The initialization sequence is a challenge to any attempt to secure an Intel computer, and has facilitated many security compromises (§ 2.3).

Intel's engineers use the processor's microcode facility ( $\S$  2.14) to implement the more complicated aspects of the Intel architecture, which greatly helps manage the hardware's complexity. The microcode is completely invisible to software developers, and its design is mostly undocumented. However, in order to evaluate the feasibility of any architectural change proposals, one must be able to distinguish changes that can be implemented in microcode from changes that can only be accomplished by modifying the hardware.

#### 2.2 Computational Model

This section pieces together a highly simplified model for a computer that implements the Intel architecture, illustrated in Figure 4. This simplified model is intended to help the reader's intuition process the fundamental concepts used by the rest of the paper. The following sections gradually refine the simplified model into a detailed description of the Intel architecture.

**Figure 4:** A computer's core is its processors and memory, which are connected by a system bus. Computers also have I/O devices, such as keyboards, which are also connected to the processor via the system bus.

The building blocks for the model presented here come from [165], which introduces the key abstractions in a computer system, and then focuses on the techniques used to build software systems on top of these abstractions.

The memory is an array of storage cells, addressed using natural numbers starting from 0, and implements the abstraction depicted in Figure 5. Its salient feature is that the result of reading a memory cell at an address must equal the most value written to that memory cell.

| WRITE( <i>addr</i> , <i>value</i> ) $\rightarrow \emptyset$        |

|--------------------------------------------------------------------|

| Store <i>value</i> in the storage cell identified by <i>addr</i> . |

| $READ(addr) \rightarrow value$                                     |

| Return the <i>value</i> argument to the most recent WRITE          |

| call referencing addr.                                             |

#### Figure 5: The memory abstraction

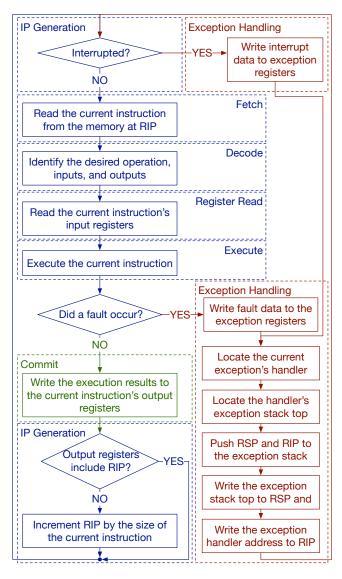

A logical processor repeatedly reads *instructions* from the computer's memory and executes them, according to the flowchart in Figure 6.

The processor has an internal memory, referred to as the *register file*. The register file consists of *Static Random Access Memory* (SRAM) cells, generally known

**Figure 6**: A processor fetches instructions from the memory and executes them. The RIP register holds the address of the instruction to be executed.

as *registers*, which are significantly faster than DRAM cells, but also a lot more expensive.

An instruction performs a simple computation on its inputs and stores the result in an output location. The processor's registers make up an *execution context* that provides the inputs and stores the outputs for most instructions. For example, ADD RDX, RAX, RBX performs an integer addition, where the inputs are the registers RAX and RBX, and the result is stored in the output register RDX.

The registers mentioned in Figure 6 are the *instruction pointer* (RIP), which stores the memory address of the next instruction to be executed by the processor, and the *stack pointer* (RSP), which stores the memory address of the topmost element in the call stack used by the

processor's procedural programming support. The other execution context registers are described in  $\S$  2.4 and  $\S$  2.6.

Under normal circumstances, the processor repeatedly reads an instruction from the memory address stored in RIP, executes the instruction, and updates RIP to point to the following instruction. Unlike many RISC architectures, the Intel architecture uses a variable-size instruction encoding, so the size of an instruction is not known until the instruction has been read from memory.

While executing an instruction, the processor may encounter a *fault*, which is a situation where the instruction's preconditions are not met. When a fault occurs, the instruction does not store a result in the output location. Instead, the instruction's result is considered to be the fault that occurred. For example, an integer division instruction DIV where the divisor is zero results in a Division Fault (#DIV).

When an instruction results in a fault, the processor stops its normal execution flow, and performs the fault handler process documented in § 2.8.2. In a nutshell, the processor first looks up the address of the code that will handle the fault, based on the fault's nature, and sets up the execution environment in preparation to execute the fault handler.

The processors are connected to each other and to the memory via a *system bus*, which is a broadcast network that implements the abstraction in Figure 7.

| $SEND(op, addr, data) \rightarrow \emptyset$                    |

|-----------------------------------------------------------------|

| Place a message containing the operation code <i>op</i> , the   |

| bus address <i>addr</i> , and the value <i>data</i> on the bus. |

| $READ() \to (op, addr, value)$                                  |

| Return the message that was written on the bus at the           |

| beginning of this clock cycle.                                  |

#### Figure 7: The system bus abstraction

During each clock cycle, at most one of the devices connected to the system bus can send a message, which is received by all the other devices connected to the bus. Each device attached to the bus decodes the operation codes and addresses of all the messages sent on the bus and ignores the messages that do not require its involvement.

For example, when the processor wishes to read a memory location, it sends a message with the operation code READ-REQUEST and the bus address corresponding to the desired memory location. The memory sees the message on the bus and performs the READ operation. At a later time, the memory responds by sending a message with the operation code READ-RESPONSE, the same address as the request, and the data value set to the result of the READ operation.

The computer communicates with the outside world via I/O devices, such as keyboards, displays, and network cards, which are connected to the system bus. Devices mostly respond to requests issued by the processor. However, devices also have the ability to issue *interrupt requests* that notify the processor of outside events, such as the user pressing a key on a keyboard.

Interrupt triggering is discussed in § 2.12. On modern systems, devices send interrupt requests by issuing writes to special bus addresses. Interrupts are considered to be *hardware exceptions*, just like faults, and are handled in a similar manner.

# 2.3 Software Privilege Levels

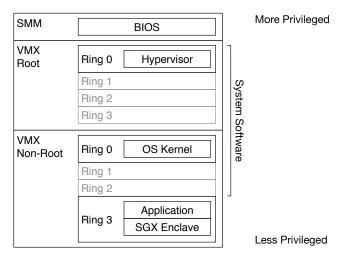

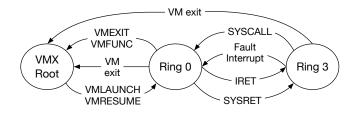

In an Infrastructure-as-a-Service (IaaS) cloud environment, such as Amazon EC2, commodity CPUs run software at four different privilege levels, shown in Figure 8.

**Figure 8**: The privilege levels in the x86 architecture, and the software that typically runs at each security level.

Each privilege level is strictly more powerful than the ones below it, so a piece of software can freely read and modify the code and data running at less privileged levels. Therefore, a software module can be compromised by any piece of software running at a higher privilege level. It follows that a software module implicitly trusts all the software running at more privileged levels, and a system's security analysis must take into account the software at all privilege levels.

System Management Mode (SMM) is intended for use by the motherboard manufacturers to implement features such as fan control and deep sleep, and/or to emulate missing hardware. Therefore, the bootstrapping software (§ 2.13) in the computer's firmware is responsible for setting up a continuous subset of DRAM as *System Management RAM* (SMRAM), and for loading all the code that needs to run in SMM mode into SMRAM. The SM-RAM enjoys special hardware protections that prevent less privileged software from accessing the SMM code.

IaaS cloud providers allow their customers to run their operating system of choice in a virtualized environment. Hardware virtualization [181], called *Virtual Machine Extensions* (VMX) by Intel, adds support for a *hypervisor*, also called a *Virtual Machine Monitor* (VMM) in the Intel documentation. The hypervisor runs at a higher privilege level (VMX root mode) than the operating system, and is responsible for allocating hardware resources across multiple operating systems that share the same physical machine. The hypervisor uses the CPU's hardware virtualization features to make each operating system believe it is running in its own computer, called a *virtual machine* (VM). Hypervisor code generally runs at ring 0 in VMX root mode.

Hypervisors that run in VMX root mode and take advantage of hardware virtualization generally have better performance and a smaller codebase than hypervisors based on binary translation [161].

The systems research literature recommends breaking up an operating system into a small *kernel*, which runs at a high privilege level, known as the *kernel mode* or *supervisor mode* and, in the Intel architecture, as *ring 0*. The kernel allocates the computer's resources to the other system components, such as device drivers and services, which run at lower privilege levels. However, for performance reasons<sup>1</sup>, mainstream operating systems have large amounts of code running at ring 0. Their *monolithic kernels* include device drivers, filesystem code, networking stacks, and video rendering functionality.

Application code, such as a Web server or a game client, runs at the lowest privilege level, referred to as *user mode (ring 3* in the Intel architecture). In IaaS cloud environments, the virtual machine images provided by customers run in VMX non-root mode, so the kernel runs in VMX non-root ring 0, and the application code runs in VMX non-root ring 3.

# 2.4 Address Spaces

Software written for the Intel architecture accesses the computer's resources using four distinct physical address spaces, shown in Figure 9. The address spaces overlap

<sup>&</sup>lt;sup>1</sup>Calling a procedure in a different ring is much slower than calling code at the same privilege level.

partially, in both purpose and contents, which can lead to confusion. This section gives a high-level overview of the physical address spaces defined by the Intel architecture, with an emphasis on their purpose and the methods used to manage them.

**Figure 9**: The four physical address spaces used by an Intel CPU. The registers and MSRs are internal to the CPU, while the memory and I/O address spaces are used to communicate with DRAM and other devices via system buses.

The *register* space consists of names that are used to access the CPU's register file, which is the only memory that operates at the CPU's clock frequency and can be used without any latency penalty. The register space is defined by the CPU's architecture, and documented in the SDM.

Some registers, such as the *Control Registers* (CRs) play specific roles in configuring the CPU's operation. For example, CR3 plays a central role in address translation (§ 2.5). These registers can only be accessed by system software. The rest of the registers make up an application's *execution context* (§ 2.6), which is essentially a high-speed scratch space. These registers can be accessed at all privilege levels, and their allocation is managed by the software's compiler. Many CPU instructions only operate on data in registers, and only place their results in registers.

The *memory* space, generally referred to as *the address space*, or *the physical address space*, consists of  $2^{36}$  (64 GB) -  $2^{40}$  (1 TB) addresses. The memory space is primarily used to access DRAM, but it is also used to communicate with *memory-mapped devices* that read memory requests off a system bus and write replies for the CPU. Some CPU instructions can read their inputs from the memory space, or store the results using the memory space.

A better-known example of memory mapping is that

at computer startup, memory addresses 0xFFFFF000 -0xFFFFFFFF (the 64 KB of memory right below the 4 GB mark) are mapped to a flash memory device that holds the first stage of the code that bootstraps the computer.

The memory space is partitioned between devices and DRAM by the computer's firmware during the bootstrapping process. Sometimes, system software includes motherboard-specific code that modifies the memory space partitioning. The OS kernel relies on address translation, described in § 2.5, to control the applications' access to the memory space. The hypervisor relies on the same mechanism to control the guest OSs.

The *input/output* (I/O) space consists of  $2^{16}$  I/O addresses, usually called *ports*. The I/O ports are used exclusively to communicate with devices. The CPU provides specific instructions for reading from and writing to the I/O space. I/O ports are allocated to devices by formal or de-facto standards. For example, ports 0xCF8 and 0xCFC are always used to access the PCI express (§ 2.9.1) configuration space.

The CPU implements a mechanism for system software to provide fine-grained I/O access to applications. However, all modern kernels restrict application software from accessing the I/O space directly, in order to limit the damage potential of application bugs.

The *Model-Specific Register* (MSR) space consists of  $2^{32}$  MSRs, which are used to configure the CPU's operation. The MSR space was initially intended for the use of CPU model-specific firmware, but some MSRs have been promoted to *architectural MSR* status, making their semantics a part of the Intel architecture. For example, architectural MSR 0x10 holds a high-resolution monotonically increasing time-stamp counter.

The CPU provides instructions for reading from and writing to the MSR space. The instructions can only be used by system software. Some MSRs are also exposed by instructions accessible to applications. For example, applications can read the time-stamp counter via the RDTSC and RDTSCP instructions, which are very useful for benchmarking and optimizing software.

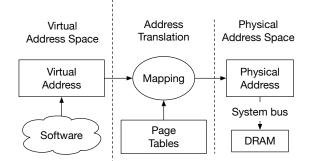

# 2.5 Address Translation

System software relies on the CPU's address translation mechanism for implementing isolation among less privileged pieces of software (applications or operating systems). Virtually all secure architecture designs bring changes to address translation. We summarize the Intel architecture's address translation features that are most relevant when establishing a system's security properties, and refer the reader to [108] for a more general presentation of address translation concepts and its other uses.

#### 2.5.1 Address Translation Concepts

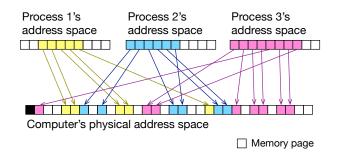

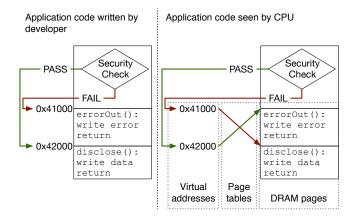

From a systems perspective, address translation is a layer of indirection (shown in Figure 10) between the *virtual addresses*, which are used by a program's memory load and store instructions, and the *physical addresses*, which reference the physical address space (§ 2.4). The mapping between virtual and physical addresses is defined by *page tables*, which are managed by the system software.

**Figure 10**: Virtual addresses used by software are translated into physical memory addresses using a mapping defined by the page tables.

Operating systems use address translation to implement the *virtual memory abstraction*, illustrated by Figure 11. The virtual memory abstraction exposes the same interface as the memory abstraction in § 2.2, but each process uses a separate virtual address space that only references the memory allocated to that process. From an application developer standpoint, virtual memory can be modeled by pretending that each process runs on a separate computer and has its own DRAM.

**Figure 11**: The virtual memory abstraction gives each process its own virtual address space. The operating system multiplexes the computer's DRAM between the processes, while application developers build software as if it owns the entire computer's memory.

Address translation is used by the operating system to

multiplex DRAM among multiple application processes, isolate the processes from each other, and prevent application code from accessing memory-mapped devices directly. The latter two protection measures prevent an application's bugs from impacting other applications or the OS kernel itself. Hypervisors also use address translation, to divide the DRAM among operating systems that run concurrently, and to virtualize memory-mapped devices.

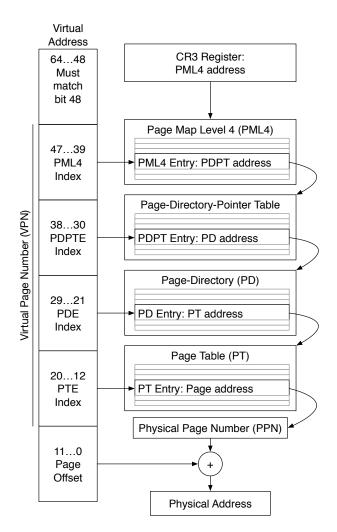

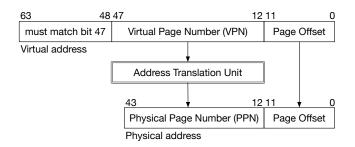

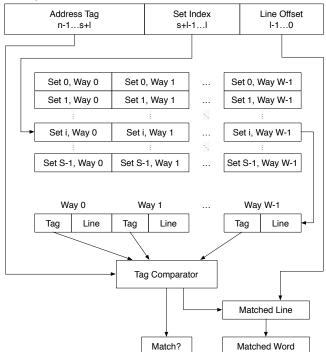

The address translation mode used by 64-bit operating systems, called IA-32e by Intel's documentation, maps 48-bit *virtual addresses* to *physical addresses* of at most 52 bits<sup>2</sup>. The translation process, illustrated in Figure 12, is carried out by dedicated hardware in the CPU, which is referred to as the *address translation unit* or the *memory management unit* (MMU).

**Figure 12**: IA-32e address translation takes in a 48-bit virtual address and outputs a 52-bit physical address.

<sup>&</sup>lt;sup>2</sup>The size of a physical address is CPU-dependent, and is 40 bits for recent desktop CPUs and 44 bits for recent high-end server CPUs.

The bottom 12 bits of a virtual address are not changed by the translation. The top 36 bits are grouped into four 9-bit indexes, which are used to index into the page tables. Despite its name, the page tables data structure closely resembles a full 512-ary search tree where nodes have fixed keys. Each node is represented in DRAM as an array of 512 8-byte entries that contain the physical addresses of the next-level children as well as some flags. The physical address of the root node is stored in the CR3 register. The arrays in the last-level nodes contain the physical addresses that are the result of the address translation.

The address translation function, which does not change the bottom bits of addresses, partitions the memory address space into *pages*. A page is the set of all memory locations that only differ in the bottom bits which are not impacted by address translation, so all the memory addresses in a virtual page translate to corresponding addresses in the same physical page. From this perspective, the address translation function can be seen as a mapping between *Virtual Page Numbers* (VPN) and *Physical Page Numbers* (PPN), as shown in Figure 13.

**Figure 13**: Address translation can be seen as a mapping between virtual page numbers and physical page numbers.

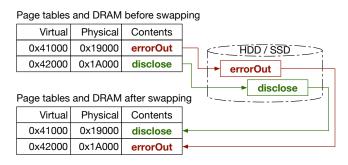

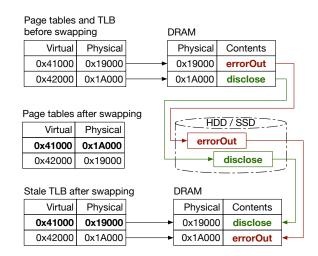

In addition to isolating application processes, operating systems also use the address translation feature to run applications whose collective memory demands exceed the amount of DRAM installed in the computer. The OS evicts infrequently used memory pages from DRAM to a larger (but slower) memory, such as a hard disk drive (HDD) or solid-state drive (SSD). For historical reason, this slower memory is referred to as the *disk*.

The OS ability to over-commit DRAM is often called *page swapping*, for the following reason. When an application process attempts to access a page that has been evicted, the OS "steps in" and reads the missing page back into DRAM. In order to do this, the OS might have to evict a different page from DRAM, effectively swapping the contents of a DRAM page with a disk page. The details behind this high-level description are covered in

the following sections.

The CPU's address translation is also referred to as "paging", which is a shorthand for "page swapping".

# 2.5.2 Address Translation and Virtualization

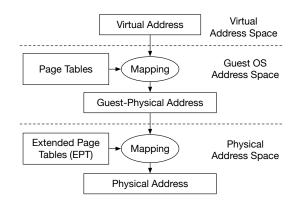

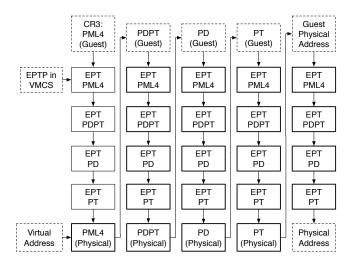

Computers that take advantage of hardware virtualization use a hypervisor to run multiple operating systems at the same time. This creates some tension, because each operating system was written under the assumption that it owns the entire computer's DRAM. The tension is solved by a second layer of address translation, illustrated in Figure 14.

**Figure 14**: Virtual addresses used by software are translated into physical memory addresses using a mapping defined by the page tables.

When a hypervisor is active, the page tables set up by an operating system map between virtual addresses and *guest-physical addresses* in a *guest-physical address space*. The hypervisor multiplexes the computer's DRAM between the operating systems' guest-physical address spaces via the second layer of address translations, which uses *extended page tables* (EPT) to map guest-physical addresses to physical addresses.

The EPT uses the same data structure as the page tables, so the process of translating guest-physical addresses to physical addresses follows the same steps as IA-32e address translation. The main difference is that the physical address of the data structure's root node is stored in the extended page table pointer (EPTP) field in the *Virtual Machine Control Structure* (VMCS) for the guest OS. Figure 15 illustrates the address translation process in the presence of hardware virtualization.

#### 2.5.3 Page Table Attributes

Each page table entry contains a physical address, as shown in Figure 12, and some Boolean values that are referred to as *flags* or *attributes*. The following attributes

**Figure 15**: Address translation when hardware virtualization is enabled. The kernel-managed page tables contain guest-physical addresses, so each level in the kernel's page table requires a full walk of the hypervisor's extended page table (EPT). A translation requires up to 20 memory accesses (the bold boxes), assuming the physical address of the kernel's PML4 is cached.

are used to implement page swapping and software isolation.

The *present* (P) flag is set to 0 to indicate unused parts of the address space, which do not have physical memory associated with them. The system software also sets the P flag to 0 for pages that are evicted from DRAM. When the address translation unit encounters a zero P flag, it aborts the translation process and issues a hardware exception, as described in § 2.8.2. This hardware exception gives system software an opportunity to step in and bring an evicted page back into DRAM.

The *accessed* (A) flag is set to 1 by the CPU whenever the address translation machinery reads a page table entry, and the *dirty* (D) flag is set to 1 by the CPU when an entry is accessed by a memory write operation. The A and D flags give the hypervisor and kernel insight into application memory access patterns and inform the algorithms that select the pages that get evicted from RAM.

The main attributes supporting software isolation are the *writable* (W) flag, which can be set to 0 to prohibit<sup>3</sup> writes to any memory location inside a page, the *disable execution* (XD) flag, which can be set to 1 to prevent instruction fetches from a page, and the *supervisor* (S) flag, which can be set to 1 to prohibit any accesses from application software running at ring 3.

### 2.6 Execution Contexts

Application software targeting the 64-bit Intel architecture uses a variety of CPU registers to interact with the processor's features, shown in Figure 16 and Table 1. The values in these registers make up an application thread's state, or *execution context*.

OS kernels multiplex each logical processor (§ 2.9.4) between multiple software threads by *context switching*, namely saving the values of the registers that make up a thread's execution context, and replacing them with another thread's previously saved context. Context switching also plays a part in executing code inside secure containers, so its design has security implications.

| 64-bit integers / pointers |         |          | 64-bit special-purpose registers |  |                   |                  |

|----------------------------|---------|----------|----------------------------------|--|-------------------|------------------|

| RAX                        | RBX     | RCX      | RDX                              |  | RIP - instruction | pointer          |

| RSI                        | RDI     | RBP      | RSP                              |  | RSP - stack poir  | nter             |

| R8                         | R9      | R10      | R11                              |  | RFLAGS - statu    | s / control bits |

| R12                        | R13     | R14      | R15                              |  | segment register  | 'S               |

| ignored                    | segment | register | S                                |  | FS                | GS               |

| CS                         | DS      | ES       | SS                               |  | 64-bit FS base    | 64-bit GS base   |

**Figure 16**: CPU registers in the 64-bit Intel architecture. RSP can be used as a general-purpose register (GPR), e.g., in pointer arithmetic, but it always points to the top of the program's stack. Segment registers are covered in  $\S$  2.7.

Integers and memory addresses are stored in 16 general-purpose registers (GPRs). The first 8 GPRs have historical names: RAX, RBX, RCX, RDX, RSI, RDI, RSP, and RBP, because they are extended versions of the 32-bit Intel architecture's GPRs. The other 8 GPRs are simply known as R9-R16. RSP is designated for pointing to the top of the procedure call stack, which is simply referred to as *the stack*. RSP and the stack that it refers to are automatically read and modified by the CPU instructions that implement procedure calls, such as CALL and RET (return), and by specialized stack handling instructions such as PUSH and POP.

All applications also use the RIP register, which contains the address of the currently executing instruction, and the RFLAGS register, whose bits (e.g., the carry flag - CF) are individually used to store comparison results and control various instructions.

Software might use other registers to interact with specific processor features, some of which are shown in Table 1.

The Intel architecture provides a future-proof method for an OS kernel to save the values of feature-specific registers used by an application. The XSAVE instruction

<sup>&</sup>lt;sup>3</sup>Writes to non-writable pages result in #GP exceptions (§ 2.8.2).

| Feature | Registers           | XCR0 bit |

|---------|---------------------|----------|

| FPU     | FP0 - FP7, FSW, FTW | 0        |

| SSE     | MM0 - MM7, XMM0 -   | 1        |

|         | XMM15, XMCSR        |          |

| AVX     | YMM0 - YMM15        | 2        |

| MPX     | BND0 - BND 3        | 3        |

| MPX     | BNDCFGU, BNDSTATUS  | 4        |

| AVX-512 | K0 - K7             | 5        |

| AVX-512 | ZMM0_H - ZMM15_H    | 6        |

| AVX-512 | ZMM16 - ZMM31       | 7        |

| РК      | PKRU                | 9        |

Table 1: Sample feature-specific Intel architecture registers.

takes in a *requested-feature bitmap* (RFBM), and writes the registers used by the features whose RFBM bits are set to 1 in a memory area. The memory area written by XSAVE can later be used by the XRSTOR instruction to load the saved values back into feature-specific registers. The memory area includes the RFBM given to XSAVE, so XRSTOR does not require an RFBM input.

Application software declares the features that it plans to use to the kernel, so the kernel knows what XSAVE bitmap to use when context-switching. When receiving the system call, the kernel sets the XCR0 register to the feature bitmap declared by the application. The CPU generates a fault if application software attempts to use features that are not enabled by XCR0, so applications cannot modify feature-specific registers that the kernel wouldn't take into account when context-switching. The kernel can use the CPUID instruction to learn the size of the XSAVE memory area for a given feature bitmap, and compute how much memory it needs to allocate for the context of each of the application's threads.

#### 2.7 Segment Registers

The Intel 64-bit architecture gained widespread adoption thanks to its ability to run software targeting the older 32bit architecture side-by-side with 64-bit software [169]. This ability comes at the cost of some warts. While most of these warts can be ignored while reasoning about the security of 64-bit software, the segment registers and vestigial segmentation model must be understood.

The semantics of the Intel architecture's instructions include the implicit use of a few segments which are loaded into the processor's *segment registers* shown in Figure 16. Code fetches use the *code segment* (CS). Instructions that reference the stack implicitly use the *stack segment* (SS). Memory references implicitly use the *data segment* (DS) or the *destination segment* (ES). Via

segment override prefixes, instructions can be modified to use the unnamed segments FS and GS for memory references.

Modern operating systems effectively disable segmentation by covering the entire addressable space with one segment, which is loaded in CS, and one data segment, which is loaded in SS, DS and ES. The FS and GS registers store segments covering *thread-local storage* (TLS).

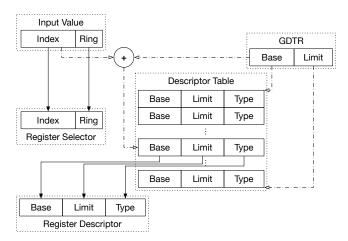

Due to the Intel architecture's 16-bit origins, segment registers are exposed as 16-bit values, called *segment selectors*. The top 13 bits in a selector are an index in a *descriptor table*, and the bottom 2 bits are the selector's ring number, which is also called requested privilege level (RPL) in the Intel documentation. Also, modern system software only uses rings 0 and 3 (see § 2.3).

Each segment register has a hidden *segment descriptor*, which consists of a *base address*, *limit*, and type information, such as whether the descriptor should be used for executable code or data. Figure 17 shows the effect of loading a 16-bit selector into a segment register. The selector's index is used to read a descriptor from the descriptor table and copy it into the segment register's hidden descriptor.

**Figure 17**: Loading a segment register. The 16-bit value loaded by software is a selector consisting of an index and a ring number. The index selects a GDT entry, which is loaded into the descriptor part of the segment register.

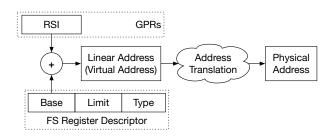

In 64-bit mode, all segment limits are ignored. The base addresses in most segment registers (CS, DS, ES, SS) are ignored. The base addresses in FS and GS are used, in order to support thread-local storage. Figure 18 outlines the address computation in this case. The instruction's address, named *logical address* in the Intel documentation, is added to the base address in the segment register's descriptor, yielding the virtual address, also named *linear address*. The virtual address is then

translated ( $\S$  2.5) to a physical address.

Figure 18: Example address computation process for MOV FS: [RDX], 0. The segment's base address is added to the address in RDX before address translation ( $\S$  2.5) takes place.

Outside the special case of using FS or GS to reference thread-local storage, the logical and virtual (linear) addresses match. Therefore, most of the time, we can get away with completely ignoring segmentation. In these cases, we use the term "virtual address" to refer to both the virtual and the linear address.

Even though CS is not used for segmentation, 64-bit system software needs to load a valid selector into it. The CPU uses the ring number in the CS selector to track the current privilege level, and uses one of the type bits to know whether it's running 64-bit code, or 32-bit code in compatibility mode.

The DS and ES segment registers are completely ignored, and can have null selectors loaded in them. The CPU loads a null selector in SS when switching privilege levels, discussed in  $\S$  2.8.2.

Modern kernels only use one descriptor table, the *Global Descriptor Table* (GDT), whose virtual address is stored in the GDTR register. Table 2 shows a typical GDT layout that can be used by 64-bit kernels to run both 32-bit and 64-bit applications.

| Descriptor            | Selector               |

|-----------------------|------------------------|

| Null (must be unused) | 0                      |

| Kernel code           | 0x08 (index 1, ring 0) |

| Kernel data           | 0x10 (index 2, ring 0) |

| User code             | 0x1B (index 3, ring 3) |

| User data             | 0x1F (index 4, ring 3) |

| TSS                   | 0x20 (index 5, ring 0) |

Table 2: A typical GDT layout in the 64-bit Intel Architecture.

The last entry in Table 2 is a descriptor for the *Task State Segment* (TSS), which was designed to implement hardware context switching, named *task switching* in the Intel documentation. The descriptor is stored in the *Task Register* (TR), which behaves like the other segment registers described above. Task switching was removed from the 64-bit architecture, but the TR segment register was preserved, and it points to a repurposed TSS data structure. The 64-bit TSS contains an *I/O map*, which indicates what parts of the I/O address space can be accessed directly from ring 3, and the *Interrupt Stack Table* (IST), which is used for privilege level switching (§ 2.8.2).

Modern operating systems do not allow application software any direct access to the I/O address space, so the kernel sets up a single TSS that is loaded into TR during early initialization, and used to represent all applications running under the OS.

# 2.8 Privilege Level Switching

Any architecture that has software privilege levels must provide a method for less privileged software to invoke the services of more privileged software. For example, application software needs the OS kernel's assistance to perform network or disk I/O, as that requires access to privileged memory or to the I/O address space.

At the same time, less privileged software cannot be offered the ability to jump arbitrarily into more privileged code, as that would compromise the privileged software's ability to enforce security and isolation invariants. In our example, when an application wishes to write a file to the disk, the kernel must check if the application's user has access to that file. If the ring 3 code could perform an arbitrary jump in kernel space, it would be able to skip the access check.

For these reasons, the Intel architecture includes privilege-switching mechanisms used to transfer control from less privileged software to well-defined entry points in more privileged software. As suggested above, an architecture's privilege-switching mechanisms have deep implications for the security properties of its software. Furthermore, securely executing the software inside a protected container requires the same security considerations as privilege level switching.

Due to historical factors, the Intel architecture has a vast number of execution modes, and an intimidating amount of transitions between them. We focus on the privilege level switching mechanisms used by modern 64-bit software, summarized in Figure 19.

#### 2.8.1 System Calls

On modern processors, application software uses the SYSCALL instruction to invoke ring 0 code, and the kernel uses SYSRET to switch the privilege level back to ring 3. SYSCALL jumps into a predefined kernel loca-

**Figure 19**: Modern privilege switching methods in the 64-bit Intel architecture.

tion, which is specified by writing to a pair of architectural MSRs ( $\S$  2.4).

All MSRs can only be read or written by ring 0 code. This is a crucial security property, because it entails that application software cannot modify SYSCALL's MSRs. If that was the case, a rogue application could abuse the SYSCALL instruction to execute arbitrary kernel code, potentially bypassing security checks.

The SYSRET instruction switches the current privilege level from ring 0 back to ring 3, and jumps to the address in RCX, which is set by the SYSCALL instruction. The SYSCALL / SYSRET pair does not perform any memory access, so it out-performs the Intel architecture's previous privilege switching mechanisms, which saved state on a stack. The design can get away without referencing a stack because kernel calls are not recursive.

# 2.8.2 Faults

The processor also performs a switch from ring 3 to ring 0 when a *hardware exception* occurs while executing application code. Some exceptions indicate bugs in the application, whereas other exceptions require kernel action.

A general protection fault (#GP) occurs when software attempts to perform a disallowed action, such as setting the CR3 register from ring 3.

A *page fault* (#PF) occurs when address translation encounters a page table entry whose P flag is 0, or when the memory inside a page is accessed in way that is inconsistent with the access bits in the page table entry. For example, when ring 3 software accesses the memory inside a page whose S bit is set, the result of the memory access is #PF.

When a hardware exception occurs in application code, the CPU performs a ring switch, and calls the corresponding *exception handler*. For example, the #GP handler typically terminates the application's process, while the #PF handler reads the swapped out page back into RAM and resumes the application's execution.

The exception handlers are a part of the OS kernel,

and their locations are specified in the first 32 entries of the Interrupt Descriptor Table (IDT), whose structure is shown in Table 3. The IDT's physical address is stored in the IDTR register, which can only be accessed by ring 0 code. Kernels protect the IDT memory using page tables, so that ring 3 software cannot access it.

| Field                             | Bits |

|-----------------------------------|------|

| Handler RIP                       | 64   |

| Handler CS                        | 16   |

| Interrupt Stack Table (IST) index | 3    |

**Table 3**: The essential fields of an IDT entry in 64-bit mode. Each entry points to a hardware exception or interrupt handler.

Each IDT entry has a 3-bit index pointing into the Interrupt Stack Table (IST), which is an array of 8 stack pointers stored in the TSS described in § 2.7.

When a hardware exception occurs, the execution state may be corrupted, and the current stack cannot be relied on. Therefore, the CPU first uses the handler's IDT entry to set up a known good stack. SS is loaded with a null descriptor, and RSP is set to the IST value to which the IDT entry points. After switching to a reliable stack, the CPU pushes the snapshot in Table 4 on the stack, then loads the IDT entry's values into the CS and RIP registers, which trigger the execution of the exception handler.

| Field          | Bits |

|----------------|------|

| Exception SS   | 64   |

| Exception RSP  | 64   |

| RFLAGS         | 64   |

| Exception CS   | 64   |

| Exception RIP  | 64   |

| Exception code | 64   |

**Table 4**: The snapshot pushed on the handler's stack when a hardware exception occurs. IRET restores registers from this snapshot.

After the exception handler completes, it uses the IRET (interrupt return) instruction to load the registers from the on-stack snapshot and switch back to ring 3.

The Intel architecture gives the fault handler complete control over the execution context of the software that incurred the fault. This privilege is necessary for handlers (e.g., #GP) that must perform context switches (§ 2.6) as a consequence of terminating a thread that encountered a bug. It follows that all fault handlers must be trusted to not leak or tamper with the information in an application's execution context.

# 2.8.3 VMX Privilege Level Switching

Intel systems that take advantage of the hardware virtualization support to run multiple operating systems at the same time use a hypervisor that manages the VMs. The hypervisor creates a *Virtual Machine Control Structure* (VMCS) for each operating system instance that it wishes to run, and uses the VMENTER instruction to assign a logical processor to the VM.

When a logical processor encounters a fault that must be handled by the hypervisor, the logical processor performs a VM exit. For example, if the address translation process encounters an EPT entry with the P flag set to 0, the CPU performs a VM exit, and the hypervisor has an opportunity to bring the page into RAM.

The VMCS shows a great application of the encapsulation principle [130], which is generally used in high-level software, to computer architecture. The Intel architecture specifies that each VMCS resides in DRAM and is 4 KB in size. However, the architecture does not specify the VMCS format, and instead requires the hypervisor to interact with the VMCS via CPU instructions such as VMREAD and VMWRITE.

This approach allows Intel to add VMX features that require VMCS format changes, without the burden of having to maintain backwards compatibility. This is no small feat, given that huge amounts of complexity in the Intel architecture were introduced due to compatibility requirements.

### 2.9 A Computer Map

This section outlines the hardware components that make up a computer system based on the Intel architecture.

§ 2.9.1 summarizes the structure of a *motherboard*. This is necessary background for reasoning about the cost and impact of physical attacks against a computing system. § 2.9.2 describes Intel's Management Engine, which plays a role in the computer's bootstrap process, and has significant security implications.

$\S$  2.9.3 presents the building blocks of an Intel processor, and  $\S$  2.9.4 models an Intel execution core at a high level. This is the foundation for implementing defenses against physical attacks. Perhaps more importantly, reasoning about software attacks based on information leakage, such as timing attacks, requires understanding how a processor's computing resources are shared and partitioned between mutually distrusting parties.

The information in here is either contained in the SDM or in Intel's Optimization Reference Manual [96].

# 2.9.1 The Motherboard

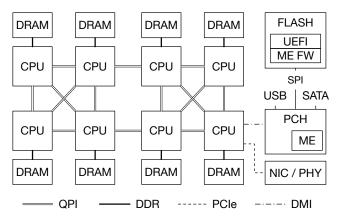

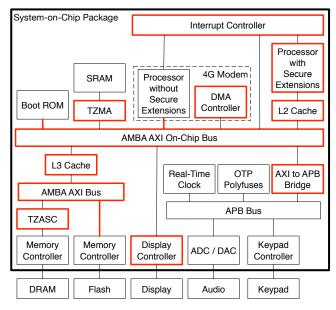

A computer's components are connected by a printed circuit board called a *motherboard*, shown in Figure 20, which consists of *sockets* connected by *buses*. Sockets connect chip-carrying *packages* to the board. The Intel documentation uses the term "package" to specifically refer to a CPU.

**Figure 20**: The motherboard structures that are most relevant in a system security analysis.

The CPU (described in § 2.9.3) hosts the execution cores that run the software stack shown in Figure 8 and described in § 2.3, namely the SMM code, the hypervisor, operating systems, and application processes. The computer's main memory is provided by *Dynamic Random-Access Memory* (DRAM) chips.

The *Platform Controller Hub* (PCH) houses (relatively) low-speed I/O controllers driving the slower buses in the system, like SATA, used by storage devices, and USB, used by input peripherals. The PCH is also known as the *chipset*. At a first approximation, the *south bridge* term in older documentation can also be considered as a synonym for PCH.

Motherboards also have a non-volatile (flash) memory chip that hosts firmware which implements the *Unified Extensible Firmware Interface* (UEFI) specification [180]. The firmware contains the boot code and the code that executes in System Management Mode (SMM, § 2.3).

The components we care about are connected by the following buses: the *Quick-Path Interconnect* (QPI [91]), a network of point-to-point links that connect processors, the *double data rate* (DDR) bus that connects a CPU to DRAM, the *Direct Media Interface* (DMI) bus that connects a CPU to the PCH, the *Peripheral Component Interconnect Express* (PCIe) bus that connects a CPU to peripherals such as a *Network Interface Card* (NIC), and

the *Serial Programming Interface* (SPI) used by the PCH to communicate with the flash memory.

The PCIe bus is an extended, point-to-point version of the PCI standard, which provides a method for any peripheral connected to the bus to perform *Direct Memory Access* (DMA), transferring data to and from DRAM without involving an execution core and spending CPU cycles. The PCI standard includes a configuration mechanism that assigns a range of DRAM to each peripheral, but makes no provisions for restricting a peripheral's DRAM accesses to its assigned range.

Network interfaces consist of a *physical* (PHY) module that converts the analog signals on the network media to and from digital bits, and a *Media Access Control* (MAC) module that implements a network-level protocol. Modern Intel-based motherboards forego a fullfledged NIC, and instead include an Ethernet [84] PHY module.

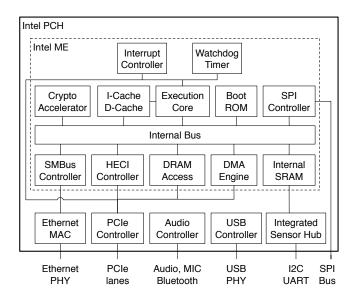

#### 2.9.2 The Intel Management Engine (ME)

Intel's *Management Engine* (ME) is an embedded computer that was initially designed for remote system management and troubleshooting of server-class systems that are often hosted in data centers. However, all of Intel's recent PCHs contain an ME [80], and it currently plays a crucial role in platform bootstrapping, which is described in detail in § 2.13. Most of the information in this section is obtained from an Intel-sponsored book [162].

The ME is part of Intel's *Active Management Technology* (AMT), which is marketed as a convenient way for IT administrators to troubleshoot and fix situations such as failing hardware, or a corrupted OS installation, without having to gain physical access to the impacted computer.

The Intel ME, shown in Figure 21, remains functional during most hardware failures because it is an entire embedded computer featuring its own execution core, bootstrap ROM, and internal RAM. The ME can be used for troubleshooting effectively thanks to an array of abilities that include overriding the CPU's boot vector and a DMA engine that can access the computer's DRAM. The ME provides remote access to the computer without any CPU support because it can use the *System Management bus* (SMBus) to access the motherboard's Ethernet PHY or an AMT-compatible NIC [100].

The Intel ME is connected to the motherboard's power supply using a power rail that stays active even when the host computer is in the *Soft Off* mode [100], known as ACPI G2/S5, where most of the computer's components

**Figure 21**: The Intel Management Engine (ME) is an embedded computer hosted in the PCH. The ME has its own execution core, ROM and SRAM. The ME can access the host's DRAM via a memory controller and a DMA controller. The ME is remotely accessible over the network, as it has direct access to an Ethernet PHY via the SMBus.

are powered off [87], including the CPU and DRAM. For all practical purposes, this means that the ME's execution core is active as long as the power supply is still connected to a power source.

In S5, the ME cannot access the DRAM, but it can still use its own internal memories. The ME can also still communicate with a remote party, as it can access the motherboard's Ethernet PHY via SMBus. This enables applications such as AMT's theft prevention, where a laptop equipped with a cellular modem can be tracked and permanently disabled as long as it has power and signal.

As the ME remains active in deep power-saving modes, its design must rely on low-power components. The execution core is an Argonaut RISC Core (ARC) clocked at 200-400MHz, which is typically used in low-power embedded designs. On a very recent PCH [100], the internal SRAM has 640KB, and is shared with the Integrated Sensor Hub (ISH)'s core. The SMBus runs at 1MHz and, without CPU support, the motherboard's Ethernet PHY runs at 10Mpbs.

When the host computer is powered on, the ME's execution core starts running code from the ME's bootstrap ROM. The bootstrap code loads the ME's software stack from the same flash chip that stores the host computer's firmware. The ME accesses the flash memory chip an embedded SPI controller.

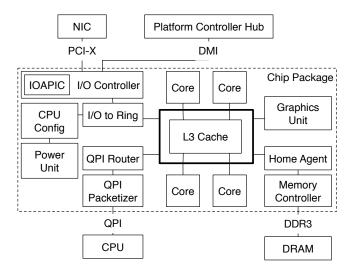

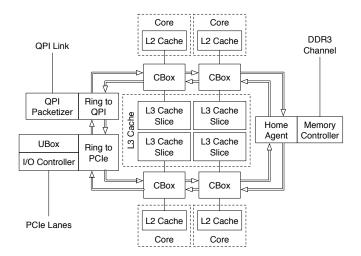

# 2.9.3 The Processor Die

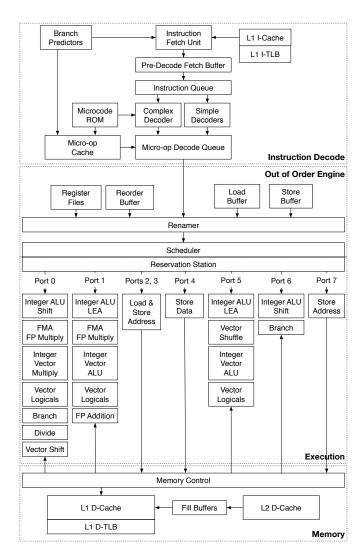

An Intel processor's die, illustrated in Figure 22, is divided into two broad areas: the *core area* implements the instruction execution pipeline typically associated with CPUs, while the *uncore* provides functions that were traditionally hosted on separate chips, but are currently integrated on the CPU die to reduce latency and power consumption.

Figure 22: The major components in a modern CPU package. § 2.9.3 gives an uncore overview. § 2.9.4 describes execution cores. § 2.11.3 takes a deeper look at the uncore.

At a conceptual level, the uncore of modern processors includes an *integrated memory controller* (iMC) that interfaces with the DDR bus, an *integrated I/O controller* (IIO) that implements PCIe bus lanes and interacts with the DMI bus, and a growing number of integrated peripherals, such as a *Graphics Processing Unit* (GPU). The uncore structure is described in some processor family datasheets [97, 98], and in the overview sections in Intel's uncore performance monitoring documentation [37, 90, 94].

Security extensions to the Intel architecture, such as Trusted Execution Technology (TXT) [70] and Software Guard Extensions (SGX) [14, 139], rely on the fact that the processor die includes the memory and I/O controller, and thus can prevent any device from accessing protected memory areas via *Direct Memory Access* (DMA) transfers. § 2.11.3 takes a deeper look at the uncore organization and at the machinery used to prevent unauthorized DMA transfers.

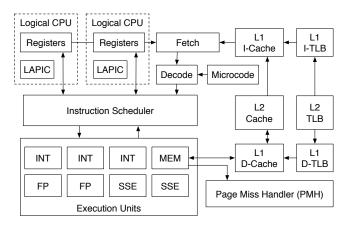

#### 2.9.4 The Core

Virtually all modern Intel processors have core areas consisting of multiple copies of the execution core circuitry, each of which is called a *core*. At the time of this writing, desktop-class Intel CPUs have 4 cores, and server-class CPUs have as many as 18 cores.

Most Intel CPUs feature *hyper-threading*, which means that a core (shown in Figure 23) has two copies of the register files backing the execution context described in § 2.6, and can execute two separate streams of instructions simultaneously. Hyper-threading reduces the impact of memory stalls on the utilization of the fetch, decode and execution units.

**Figure 23**: CPU core with two logical processors. Each logical processor has its own execution context and LAPIC (§ 2.12). All the other core resources are shared.

A hyper-threaded core is exposed to system software as two *logical processors* (LPs), also named *hardware threads* in the Intel documentation. The logical processor abstraction allows the code used to distribute work across processors in a multi-processor system to function without any change on multi-core hyper-threaded processors.

The high level of resource sharing introduced by hyper-threading introduces a security vulnerability. Software running on one logical processor can use the high-resolution performance counter (RDTSCP, § 2.4) [152] to get information about the instructions and memory access patterns of another piece of software that is executed on the other logical processor on the same core.

That being said, the biggest downside of hyperthreading might be the fact that writing about Intel processors in a rigorous manner requires the use of the cumbersome term Logical Processor instead of the shorter and more intuitive "CPU core", which can often be abbreviated to "core".

### 2.10 Out-of-Order and Speculative Execution

CPU cores can execute instructions orders of magnitude faster than DRAM can read data. Computer architects attempt to bridge this gap by using hyper-threading (§ 2.9.3), out-of-order and speculative execution, and caching, which is described in § 2.11. In CPUs that use out-of-order execution, the order in which the CPU carries out a program's instructions (*execution order*) is not necessarily the same as the order in which the instructions would be executed by a sequential evaluation system (*program order*).

An analysis of a system's information leakage must take out-of-order execution into consideration. Any CPU actions observed by an attacker match the execution order, so the attacker may learn some information by comparing the observed execution order with a known program order. At the same time, attacks that try to infer a victim's program order based on actions taken by the CPU must account for out-of-order execution as a source of noise.

This section summarizes the out-of-order and speculative execution concepts used when reasoning about a system's security properties. [150] and [76] cover the concepts in great depth, while Intel's optimization manual [96] provides details specific to Intel CPUs.

Figure 24 provides a more detailed view of the CPU core components involved in out-of-order execution, and omits some less relevant details from Figure 23.

The Intel architecture defines a *complex instruction set* (CISC). However, virtually all modern CPUs are architected following *reduced instruction set* (RISC) principles. This is accomplished by having the instruction decode stages break down each instruction into *microops*, which resemble RISC instructions. The other stages of the execution pipeline work exclusively with microops.

### 2.10.1 Out-of-Order Execution

Different types of instructions require different logic circuits, called *functional units*. For example, the arithmetic logic unit (ALU), which performs arithmetic operations, is completely different from the load and store unit, which performs memory operations. Different circuits can be used at the same time, so each CPU core can execute multiple micro-ops in parallel.

The core's out-of-order engine receives decoded micro-ops, identifies the micro-ops that can execute in parallel, assigns them to functional units, and combines the outputs of the units so that the results are equivalent to having the micro-ops executed sequentially in the order in which they come from the decode stages.

For example, consider the sequence of pseudo micro-

**Figure 24**: The structures in a CPU core that are relevant to outof-order and speculative execution. Instructions are decoded into micro-ops, which are scheduled on one of the execution unit's ports. The branch predictor enables speculative execution when a branch is encountered.

$ops^4$  in Table 5 below. The OR uses the result of the LOAD, but the ADD does not. Therefore, a good scheduler can have the load store unit execute the LOAD and the ALU execute the ADD, all in the same clock cycle.

The out-of-order engine in recent Intel CPUs works roughly as follows. Micro-ops received from the decode queue are written into a *reorder buffer* (ROB) while they are *in-flight* in the execution unit. The *register allocation table* (RAT) matches each register with the last reorder buffer entry that updates it. The *renamer* uses the RAT to rewrite the source and destination fields of micro-ops when they are written in the ROB, as illustrated in Tables

<sup>&</sup>lt;sup>4</sup>The set of micro-ops used by Intel CPUs is not publicly documented. The fictional examples in this section suffice for illustration purposes.

| # | Micro-op          | Meaning                    |

|---|-------------------|----------------------------|

| 1 | LOAD RAX, RSI     | $RAX \leftarrow DRAM[RSI]$ |

| 2 | OR RDI, RDI, RAX  | $RDI \gets RDI \lor RAX$   |

| 3 | ADD RSI, RSI, RCX | $RSI \leftarrow RSI + RCX$ |

| 4 | SUB RBX, RSI, RDX | $RBX \leftarrow RSI - RDX$ |

| Table 5: | Pseudo | micro-ops f | or the ou | t-of-order | execution example. |

|----------|--------|-------------|-----------|------------|--------------------|

|----------|--------|-------------|-----------|------------|--------------------|

6 and 7. Note that the ROB representation makes it easy to determine the dependencies between micro-ops.

| # | Ор   | Source 1 | Source 2 | Destination |

|---|------|----------|----------|-------------|

| 1 | LOAD | RSI      | Ø        | RAX         |

| 2 | OR   | RDI      | ROB #1   | RSI         |

| 3 | ADD  | RSI      | RCX      | RSI         |

| 4 | SUB  | ROB # 3  | RDX      | RBX         |

**Table 6**: Data written by the renamer into the reorder buffer (ROB), for the micro-ops in Table 5.

| Register | RAX | RBX | RCX | RDX | RSI | RDI |

|----------|-----|-----|-----|-----|-----|-----|

| ROB #    | #1  | #4  | Ø   | Ø   | #3  | #2  |

**Table 7**: Relevant entries of the register allocation table after themicro-ops in Table 5 are inserted into the ROB.

The scheduler decides which micro-ops in the ROB get executed, and places them in the *reservation station*. The reservation station has one port for each functional unit that can execute micro-ops independently. Each reservation station port port holds one micro-op from the ROB. The reservation station port waits until the micro-op's dependencies are satisfied and forwards the micro-op to the functional unit. When the functional unit completes executing the micro-op, its result is *written back* to the ROB, and forwarded to any other reservation station port that depends on it.

The ROB stores the results of completed micro-ops until they are *retired*, meaning that the results are *committed* to the register file and the micro-ops are removed from the ROB. Although micro-ops can be executed out-oforder, they must be retired in program order, in order to handle exceptions correctly. When a micro-op causes a hardware exception (§ 2.8.2), all the following micro-ops in the ROB are *squashed*, and their results are discarded.

In the example above, the ADD can complete before the LOAD, because it does not require a memory access. However, the *ADD*'s result cannot be committed before LOAD completes. Otherwise, if the *ADD* is committed and the *LOAD* causes a page fault, software will observe an incorrect value for the RSI register.

The ROB is tailored for discovering register dependencies between micro-ops. However, micro-ops that execute out-of-order can also have memory dependencies. For this reason, out-of-order engines have a *load buffer* and a *store buffer* that keep track of in-flight memory operations and are used to resolve memory dependencies.

#### 2.10.2 Speculative Execution

Branch instructions, also called *branches*, change the instruction pointer (RIP, § 2.6), if a condition is met (*the branch is taken*). They implement conditional statements (if) and looping statements, such as while and for. The most well-known branching instructions in the Intel architecture are in the jcc family, such as je (jump if equal).

Branches pose a challenge to the decode stage, because the instruction that should be fetched after a branch is not known until the branching condition is evaluated. In order to avoid stalling the decode stage, modern CPU designs include *branch predictors* that use historical information to guess whether a branch will be taken or not.

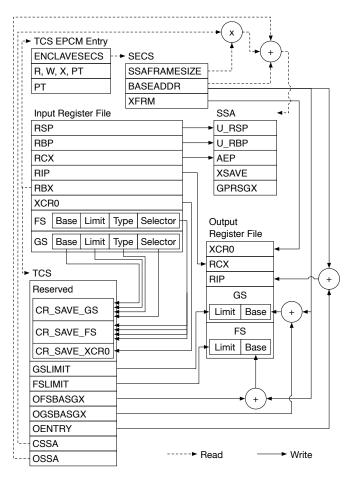

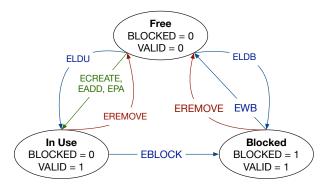

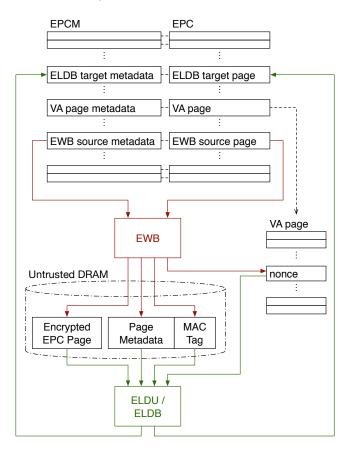

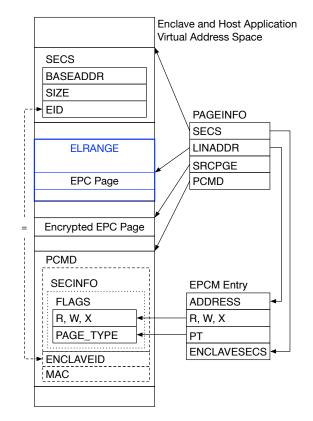

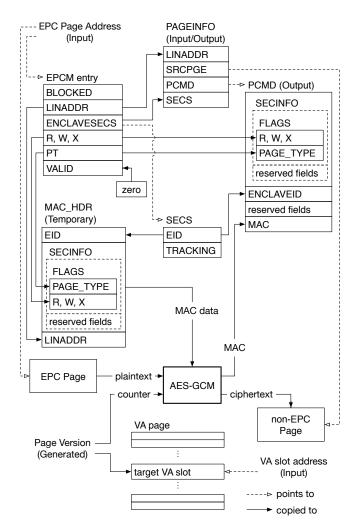

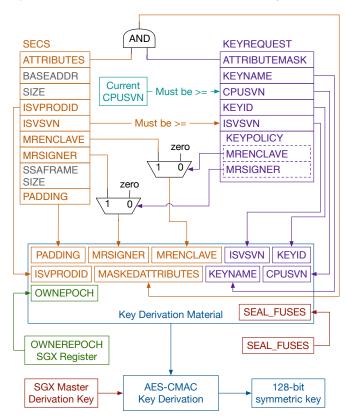

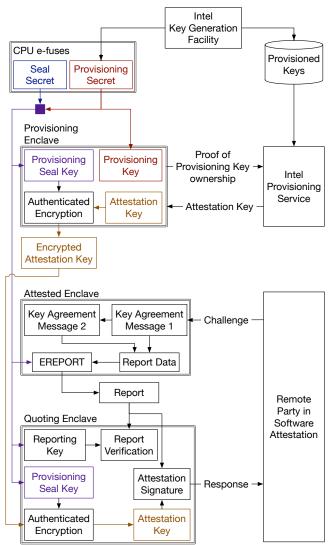

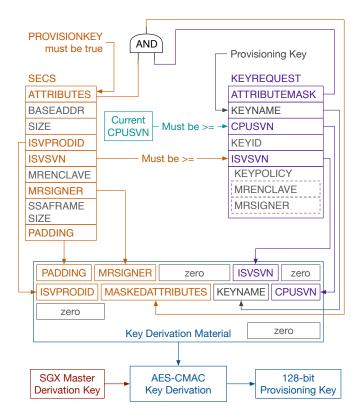

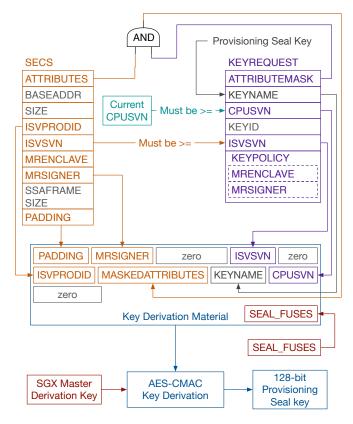

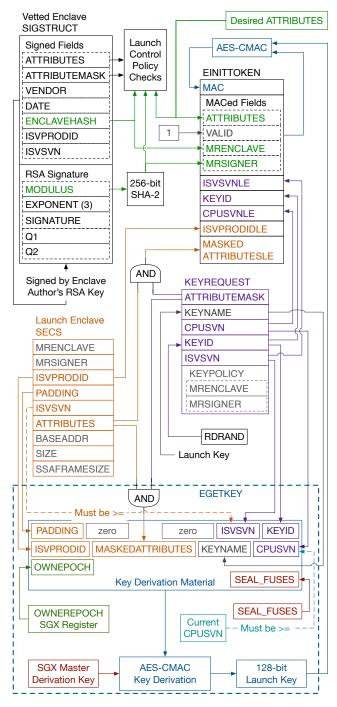

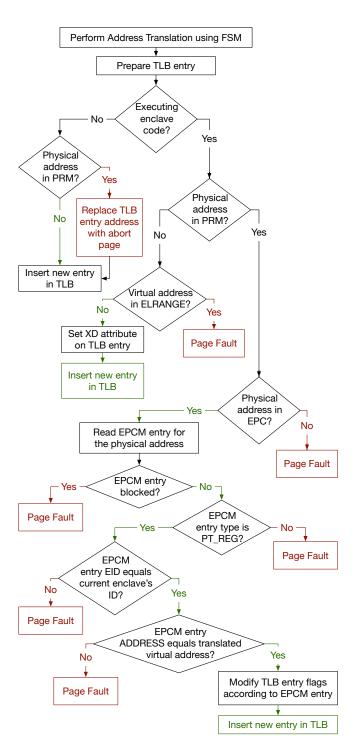

When the decode stage encounters a branch instruction, it asks the branch predictor for a guess as to whether the branch will be taken or not. The decode stage bundles the branch condition and the predictor's guess into a branch check micro-op, and then continues decoding on the path indicated by the predictor. The micro-ops following the branch check are marked as *speculative*.