# Circuit OPRAM: A (Somewhat) Tight Oblivious Parallel RAM

T-H. Hubert Chan<sup>\*</sup> Elaine Shi<sup>†</sup>

### Abstract

An Oblivious Parallel RAM (OPRAM) provides a general method to simulate any Parallel RAM (PRAM) program, such that the resulting memory access patterns leak nothing about secret inputs. OPRAM was originally proposed by Boyle et al. as the natural parallel counterpart of Oblivious RAM (ORAM), which was shown to have broad applications, e.g., in cloud outsourcing, secure processor design, and secure multiparty computation. Since parallelism is common in modern computing architectures such as multi-core processors or cluster computing, OPRAM is naturally a powerful and desirable building block as much as its sequential counterpart ORAM is.

Although prior work (in particular, Circuit ORAM) has shown how to construct ORAM schemes that are asymptotically tight under certain parameter ranges, the performance of known OPRAM schemes still do not match their sequential counterparts, leaving open two main questions: (i) whether one can construct an OPRAM scheme whose performance is competitive relative to known sequential counterparts; and (ii) whether one can construct OPRAM schemes that are asymptotically optimal.

Our paper answers the first question positively and gives partial answers to the second question. Specifically, we construct Circuit OPRAM, a new OPRAM scheme that makes the following contributions:

- 1. We achieve asymptotical improvement in terms of both total work and parallel runtime in comparison with known OPRAM schemes. More specifically, we improve the total work by a logarithmic factor and parallel runtime by poly-logarithmic factors.

- 2. We show that under sufficiently large block sizes, we can construct an OPRAM scheme that is asymptotically optimal both in total work and parallel runtime when the number of CPUs is not too small.

- 3. Our construction features a combination of novel techniques that enable us to (i) have asymptotically tight stochastic processes that do not suffer from worst-case and average-case discrepancies; and (ii) temporally reallocate work over offline and online stages of the algorithm such that we can achieve small parallel runtime overall. These techniques can be of independent interest in the design of of parallel oblivious algorithms in general.

<sup>\*</sup>The University of Hong Kong. Email: hubert@cs.hku.hk

<sup>&</sup>lt;sup>†</sup>Cornell University. Email: elaine@cs.cornell.edu

# Contents

| 1        | Introduction                                                                | 1         |

|----------|-----------------------------------------------------------------------------|-----------|

|          | 1.1 Our Results and Contributions                                           | 1         |

|          | 1.2 Technical Highlights                                                    | 3         |

|          | 1.3 Organization                                                            | 4         |

|          |                                                                             |           |

| <b>2</b> | Technical Roadmap                                                           | 5         |

|          | 2.1 Background: Circuit ORAM                                                |           |

|          | 2.2 Simplifying Assumptions and Notations                                   |           |

|          | 2.3 Pre-Warmup: The CLT OPRAM Scheme                                        |           |

|          | 2.4 Warmup: Achieve $O(\log^2 N)$ Blowup in Total Work and Parallel Runtime |           |

|          | 2.5 Achieve Small Parallel Runtime: The Challenges                          | 11        |

|          | 2.6 From Flat Pool to Semi-Structured Group Stashes                         | 12        |

|          | 2.7 Routing Fetched Position Identifiers to the Next Recursion Level        | 13        |

|          | 2.8 Putting it Altogether                                                   | 16        |

|          | 2.9 Extensions                                                              | 17        |

|          | 2.10 Related Work                                                           | 18        |

|          |                                                                             | -         |

| 3        | Preliminaries                                                               | 19        |

|          | 3.1 Parallel Random-Access Machines                                         | 19        |

|          | 3.2 Oblivious Parallel Random-Access Machines                               |           |

|          | 3.3 Building Blocks                                                         |           |

|          |                                                                             | -1        |

| <b>4</b> | Overview of OPRAM Construction                                              | <b>22</b> |

|          | 4.1 Notations                                                               | 22        |

|          | 4.2 Data Structures                                                         | 23        |

|          | 4.3 Overview of One Simulated PRAM Step                                     | 23        |

| 5        | Details of the Maintain Phase                                               | <b>25</b> |

| -        | 5.1 Removing Fetched Blocks from Subtrees and Group Stashes                 |           |

|          | 5.2 Convert Group Stashes to Pool                                           |           |

|          | 5.3 Evictions                                                               |           |

|          | 5.4 Cleanup: Reconstructing the Group Stashes                               |           |

|          | 5.5 Performance of the Maintain Phase                                       |           |

|          |                                                                             |           |

|          | 5.6 Analysis of Stash Usage                                                 | 32        |

| 6        | Details of the Fetch Phase                                                  | <b>35</b> |

|          | 6.1 Basic Building Blocks Related to Permutations                           | 35        |

|          | 6.2 Oblivious Compression (Dummy Removal)                                   |           |

|          | 6.3 Offline Phase: Conflict Resolution and Preparation                      |           |

|          | 6.4 Online Phase: Routing Position Identifiers to the Next Recursion Level  | 40        |

|          | 6.5 Performance of the Fetch Phase                                          | 40        |

| _        |                                                                             |           |

| 7        | Performance and Security of Circuit OPRAM                                   | 42        |

|          | 7.1 Performance                                                             |           |

|          | 7.2 Security                                                                | 43        |

| 8            | Extensions and Optimizations                  |      |  |  |

|--------------|-----------------------------------------------|------|--|--|

|              | 8.1 Results for Large Block Sizes             | . 43 |  |  |

|              | 8.2 Additional Extensions                     | . 45 |  |  |

| $\mathbf{A}$ | Optimizing Parallel Runtime for Path Eviction | 48   |  |  |

### 1 Introduction

Oblivious RAM (ORAM), initially proposed by Goldreich and Ostrovsky [16, 17], is a powerful primitive that allows oblivious accesses to sensitive data, such that access patterns during the computation reveal no secret information. Since its original proposal [17], ORAM has been shown to be promising in various application settings including secure processors [10, 12, 13, 24, 28], cloud outsourced storage [18, 31, 32, 38] and secure multi-party computation [14, 15, 19, 21, 23, 35].

Although ORAM is broadly useful, it is inherently sequential and does not support parallelism. On the other hand, parallelism is universal in modern architectures such as cloud platforms and multi-core processors. Motivated by this apparent discrepancy, in a recent seminal work [3], Boyle et al. extended the ORAM notion to the parallel setting. Specifically, they define Oblivious Parallel RAM (OPRAM), and demonstrated that any PRAM program can be simulated obliviously while incurring roughly  $O(\log^4 N)$  blowup in both total work and parallel runtime, where N is the total memory size. The result by Boyle et al. [3] was later improved by Chen et al. [6], who showed a logarithmic factor improvement, attaining  $O(\log^3 N)$  blowup in both total work and parallel runtime.

Before this work, we still know of no OPRAM algorithm whose performance can "match" the state-of-the-art sequential counterparts (e.g., Circuit ORAM [34], Path ORAM [33], or the KLO ORAM [22]). In particular, state-of-the-art ORAM schemes achieve  $O(\log^2 N/\log \log N)$  [22] runtime blowup for general block sizes (i.e., assuming that each memory block can store its own address). For large enough block sizes, the best known scheme Circuit ORAM [34] achieves  $O(\alpha \log N)$  runtime blowup<sup>1</sup> for any super-constant  $\alpha = \omega(1)$ . Since Goldreich and Ostrovsky proved a  $\Omega(\log N)$  ORAM lower bound [16, 17], Circuit ORAM additionally demonstrates the existence of a (somewhat) tight ORAM scheme in the sequential setting [34]. Therefore, two natural questions arise.

- Can we construct an OPRAM scheme whose asymptotical performance matches the best known sequential counterpart?

- Can we show a tight OPRAM scheme?

### 1.1 Our Results and Contributions

We now describe our contributions and how to interpret our results in light of prior work and known lower bounds.

Asymptotically more efficient OPRAM. We construct a novel OPRAM scheme called Circuit OPRAM. Circuit OPRAM shows that any PRAM that runs in parallel time T and performs a total work of W can be simulated by an equivalent OPRAM that runs in parallel time  $T \cdot O(\log N \log \log N)$ , performs  $W \cdot O(\alpha \log^2 N)$  total work, and requires that each CPU store only O(1) blocks. The above result makes no assumption about the block size except that the block must be able to store its own memory address<sup>2</sup>, and holds even if the PRAM uses a varying number of CPUs in different time steps. Since Circuit OPRAM is based on the tree-based ORAM framework [30], we achieve statistical security, i.e., security against computationally unbounded adversaries.

Circuit OPRAM achieves significant performance improvement relative to the prior state-ofthe-art [6]. Specifically, in comparison with the prior best known OPRAM scheme [6], we achieve a

<sup>&</sup>lt;sup>1</sup>In this paper, when we say that a scheme achieves  $O(\alpha f(N))$  cost, we mean that for any  $\alpha = \omega(1)$ , there exists a scheme that achieves  $O(\alpha f(N))$  cost.

<sup>&</sup>lt;sup>2</sup>Note that all previous ORAM/OPRAM works, including those based on hierarchical ORAMs [16,17,22], implicitly assume that the block must be able to at least store its own memory address; or else all previous ORAM/OPRAM schemes will incur an extra multiplicative log N factor in cost.

| Scheme              | Total work blowup                | Para. runtime blowup             | Varying CPUs |  |  |  |  |

|---------------------|----------------------------------|----------------------------------|--------------|--|--|--|--|

| Prior work          |                                  |                                  |              |  |  |  |  |

| BCP $[3]$           | $O(lpha \log^4 N)$               | $O(lpha \log^4 N)$               | $\checkmark$ |  |  |  |  |

| $CLT [6]^{\dagger}$ | $O(\alpha \log^3 N \log \log N)$ | $O(\alpha \log^3 N \log \log N)$ | ×            |  |  |  |  |

| This paper          |                                  |                                  |              |  |  |  |  |

| Circuit OPRAM       | $O(lpha \log^2 N)$               | $O(\log N \log \log N)$          |              |  |  |  |  |

|                     | $O(\log^{2+\epsilon} N)$         | $O(\log N)$                      | $\checkmark$ |  |  |  |  |

**Table 1: Our contributions.** Here we state asymptotic bounds assuming O(1) blocks of CPU cache, general block sizes, and that the failure probability is at most  $\frac{1}{N^{\Theta(\alpha)}}$ , where N denotes the total number of memory blocks and  $\alpha = \omega(1)$ .

<sup>†</sup>: CLT [6] describes their result assuming  $O(\log^2 N)$  CPU cache. For O(1) CPU cache, their bounds would incur an extra  $O(\log \log N)$  factor (since we will need oblivious sort to implement the eviction algorithm [35]). We state the bounds for O(1) CPU cache here for a fair comparison.

multiplicative  $O(\log N)$  improvement in terms of total work, and a  $O(\log^2 N)$  factor improvement in parallel runtime. Further, Chen et al. [6] assumes that the PRAM must use a (somewhat) fixed number of CPUs each time step — otherwise, their scheme can incur an extra (super-) linear in mblowup where m is the maximum number of CPUs employed by the PRAM. By contrast, we can handle varying number of CPUs efficiently while preserving all asymptotic overheads.

Table 1 summarizes our contributions relative to prior works. Most of the table is self-explanatory. We remark that Chen et al. [6] considers CPU-to-memory communication and CPU-to-CPU communication as two separate metrics, but we consider the more general PRAM model where CPU-to-CPU communication is implemented by shared memory reads and writes. Therefore, we coalesce the two metrics into one (i.e., the maximum of the two metrics).

**Theorem 1** (OPRAM for general block sizes). For any  $\alpha = \omega(1)$  and block size  $B = \Omega(\log N)$ , there exists an OPRAM scheme that has failure probability at most  $\frac{1}{N^{\Theta(\alpha)}}$  and achieves  $O(\alpha \log^2 N)$  total work blowup and  $O(\log N \log \log N)$  parallel runtime blowup.

Furthermore, our scheme can accomodate the case where each PRAM step involves a different number of CPUs, whereas the scheme by Chen et al. [6] can incur up to  $\Omega(m)$  loss in total work when the PRAM has a varying number of CPUs across time.

**Tightness under large block sizes.** Table 1 shows only the results for general block sizes. We show that for sufficiently large block sizes  $B \ge N^{\epsilon}$  and for an arbitrarily small constant  $\epsilon > 0$ , Circuit OPRAM achieves  $O(\alpha \log N)$  total work blowup and  $O(\log N)$  parallel runtime blowup. This suggests the asymptotical optimality of Circuit OPRAM under certain parameter ranges:

- Optimality in total work. Goldreich and Ostrovsky showed that any ORAM scheme must incur  $\Omega(\log N)$  total work blowup and their bound is directly applicable to the parallel setting. In this sense, Circuit OPRAM is asymptotically optimal in terms of total work for large enough blocks.

- Optimality in parallel runtime. Chan et al. [5] recently showed an  $\Omega(\log m)$  lower bound for any OPRAM's parallel runtime blowup, where m is the number of CPUs and N is the total number of memory blocks. In light of this, Circuit OPRAM is asymptotically optimal for large enough blocks and when  $m \ge N^{\epsilon}$  for any constant  $\epsilon > 0$ . With some (non-trivial) additional work, we construct another variant called Circuit OPRAM\* that achieves  $O(\log N \log \log N)$  total work blowup and  $O(\log m + \log \log N)$  parallle runtime this variant suffers from a slight  $\log \log N$  loss in total work, but is optimal in parallel runtime for a broader range, that is,  $m = \Omega(\log N)$ .

We remark that achieving  $O(\log N)$  parallel runtime is trivial if no requirement is imposed on the total work blowup — one can simply leverage  $\Theta(N)$  CPUs, one for each memory location, to obliviously route data to the request CPUs. However, the total work blowup is  $\omega(\frac{N}{m})$  in this case.

**Theorem 2** (OPRAM for large block sizes). For any constant  $\epsilon > 0$  and block size  $B \ge N^{\epsilon}$ , the following holds.

- For any  $\alpha = \omega(1)$ , there exists an OPRAM scheme that has failure probability at most  $\frac{1}{N^{\Theta(\alpha)}}$  and achieves  $O(\alpha \log N)$  total work blowup and  $O(\log N)$  parallel runtime blowup.

- There exists an OPRAM scheme that has failure probability negligible in N and achieves  $O(\log N \log \log N)$  total work blowup and  $O(\log m + \log \log N)$  parallel runtime blowup.

### 1.2 Technical Highlights

We introduce several novel techniques to achieve these asymptotic improvements.

Improving total work: avoid worst-case and average-case discrepancy. We observe that earlier OPRAM constructions often suffer from a worst-case and average-case discrepancy. We abuse the terminology slightly here: by *worst case* of a random variable, we mean an upper bound derived from some tail inequality beyond which the probability is negligible. When a secret random variable's worst-case value is asymptotically worse than its expectation, previous schemes had to pad the random variable to the worst-case value, since disclosing its true value would result in information leakage. For example, in Chen et al. [6], in expectation only O(1) blocks are assigned to each subtree; but in the worst case there can be as many as  $\Theta(\alpha \log N)$  assuming a negligible in N failure probability. To hide the number of blocks assigned to each subtree, Chen et al. [6] had to make  $\Theta(\alpha \log N)$  evictions per subtree.

Our Circuit OPRAM also relies on the disjoint subtrees approach similar to Chen et al. [6]. We solve the aforementioned worst-case and average-case discrepancy by making only O(1) evictions per subtree per access. This, however, introduces overflowing blocks. We have to handle the overflowing blocks in non-trivial manners to allow the read phase of the algorithm to be efficient (in terms of parallel runtime). Specifically, we introduce a new data structure called group stashes, where each group stash is shared by every  $\Theta(\alpha \log N)$  consecutive subtrees. The design of the group stashes again features the core idea of avoiding worst-case and average-case discrepancies. Specifically, having every  $\Theta(\alpha \log N)$  subtrees share a stash allows us to ensure that each group stash's worst-case occupancy is only O(1) factor larger than its average occupancy; and therefore padding to the worst case would only introduce a constant factor penalty.

Achieving small parallel runtime: online/offline routing. Achieving small parallel runtime turns out to be rather non-trivial. In particular, since we adopt the standard approach of recursive tree-based ORAMs [30], the fetch phase must be conducted sequentially over  $\Theta(\log N)$  recursion levels. In particular, metadata fetched must be routed to the O(m) fetch CPUs at the next recursion level, before the next level can begin its fetch.

To achieve  $O(\log N \log \log N)$  parallel runtime overall, this means that we can afford only  $O(\log \log N)$  parallel runtime per (metadata) recursion level during the online fetch phase. This requirement immediately rules out approaches that involve global oblivious sorting (over many elements) during the online fetch phase — recall that oblivious sorting is a standard building block in designing (parallel) oblivious algorithms; but to sort m elements in parallel would immediately incur  $\Theta(\log m)$  parallel runtime which is too expensive for our purpose, e.g., when  $m = \sqrt{N}$ .

One of our core ideas in achieving small parallel runtime is through temporal reallocation of work. During an offline phase, we perform preparation work to set up auxiliary data structures that will facilitate the online phase. Since the offline preparation work can be parallelized across all recursion levels, we can afford to rely on oblivious-sorting-based techniques during the offline stage. In this way, we obliviously construct the "routing permutation" between any two adjacent levels during the offline phase, such that the online phase simply needs to apply this routing permutation such that the next recursion level can receive the metadata fetched at the previous level. Applying a pre-determined permutation to an array can be trivially parallelized and takes only a single parallel step. Interestingly, as we explain in Sections 2.7 and 6, for the offline phase to construct the level-to-level routing permutations, it basically has to "emulate" the online fetch phase but leaving the fetched metadata fields blank.

Achieving small parallel runtime: localized work. We also encounter another difficulty: as we explain later in Sections 2.7 and 6, the fetched metadata must be compressed obliviously first (by removing a subset of the dummy entries) before being routed to the next recursion level. Compression can be done naïvely through oblivious sorting. However, as explained earlier, during the online stage, we cannot afford to perform global oblivious sorting over all the  $\Theta(m)$  entries of fetched metadata at a recursion level. Instead, we devise a new algorithm that localizes the work by performing compression over every  $\Theta(\alpha \log N)$ -sized group. Provided that the entries have been randomly permuted, the ratio of real and dummy elements within each group is close to the overall ratio over all elements. Since we now perform compression over much smaller groups, we can afford to perform oblivious sorting within each small group and incur only  $O(\log \log N)$  parallel runtime.

Additional techniques. Our final scheme is rather sophisticated and involves numerous additional techniques and building blocks. For example, we devise a new algorithm for performing parallel removal of fetched blocks from the OPRAM's data structure. We devise a lazy adaptation technique for adjusting our OPRAM's number of subtrees if the number of PRAM CPUs varies over time. To achieve asymptotically optimal parallel runtime for large blocks, we devise non-trivial techniques for parallelizing Circuit ORAM's eviction algorithm.

### 1.3 Organization

Our final construction is rather sophisticated, and we use the following structure to break down the complexity in our presentation.

Section 2 contains an overview of our scheme described in the order of our thought process: we start by reviewing Chen et al. [6] scheme and observing why their scheme is inefficient. Since our final construction has many inter-related components, we first describe a much simpler (but nonetheless non-trivial) warmup scheme (Section 2.4) that improves the total work by a logarithmic factor in comparison with Chen et al. [6], but does not guarantee small parallel runtime. Using the warmup scheme as a stepping stone, we then introduce non-trivial techniques to asymptotically improve the parallel runtime of the online stage (Section 2.7), by performing appropriate preparation work in the offline stage. For clarity, Section 2 makes a few simplifying assumptions, e.g., the number of PRAM CPUs is fixed.

Then, Sections 4, 5, and 6 spell out the details of the full scheme and proofs, and generalize the description to allow the number of PRAM CPUs to vary. We suggest that the reader read Section 2 first to understand the high-level intuition before looking for the details of concrete building blocks and subroutines in Sections 4, 5, and 6.

Besides those presented earlier in this section, additional related work is provided in Section 2.10.

# 2 Technical Roadmap

### 2.1 Background: Circuit ORAM

We review tree-based ORAMs [7, 30, 33, 34] originally proposed by Shi et al. [30]. We specifically focus on describing the Circuit ORAM algorithm [34] which we build upon.

We assume that memory is divided into atomic units called blocks. We first focus on describing the *non-recursive version*, in which the CPU stores in its local cache a *position map* henceforth denoted as **posmap** that gives information on the position for every block.

**Data structures.** The memory is organized in the form of a binary tree, where every tree node is a *bucket* with a capacity of O(1) blocks. Buckets hold blocks, where each block is either dummy or real. Throughout the paper, we use the notation N to denote the total number of blocks. Without loss of generality, we assume that  $N = 2^L$  is a power of two. The ORAM binary tree thus has height L.

Besides the buckets, there is also a *stash* in memory that holds overflowing blocks. The stash is of size  $O(\alpha \log N)$ , where  $\alpha = \omega(1)$  is a parameter related to the failure probability. Just like buckets, the stash may contain both real and dummy blocks. Henceforth, for convenience, we will often *treat the stash as part of the root bucket*.

Main path invariant. The main invariant of tree-based ORAMs is that every block is assigned to the path from the root to a randomly chosen leaf node. Hence, the path for each block is indicated by the *leaf identifier* or the *position identifier*, which is stored in the aforementioned position map posmap. A block with virtual address *i* must reside on the path indicated by posmap[i].

**Operations.** We describe the procedures for reading or writing a block at virtual address *i*.

- Read and remove. To read a block at virtual address *i*, the CPU looks up its assigned path indicated by posmap[*i*], and reads this entire path. If the requested block is found at some location on the path, the CPU writes a dummy block back into the location. Otherwise, the CPU simply writes the original block back. In both cases, the block written back is re-encrypted such that the adversary cannot observe which block is removed.

- Remap. Once a block at virtual address i is fetched, it is immediately assigned to a new path. To do this, a fresh random path identifier is chosen and posmap[i] is modified accordingly. The block fetched is then written to the last location in the stash (the last location is guaranteed to be empty except with negligible probability at the end of each access). If this is a write operation, the block's contents may be updated prior to writing it back to the stash.

- *Evict.* Two paths (particularly, one to the left of the root and one to the right of the root) are chosen for eviction according to an appropriate data independent criterion. Specifically, we recommend using the reverse lexicographical order approach initially proposed by Gentry et al. [14] and later adopted in other schemes such as Circuit ORAM [34].

For each path chosen (that includes the stash), the CPU performs an eviction procedure along this path. On a high level, eviction is a maintenance operation that seeks to move blocks along tree paths towards the leaves — and importantly, in a way that respects the aforementioned path invariant. The purpose of eviction is to avoid overflow at any bucket.

Specifically in Circuit ORAM, this eviction operation involves making two metadata scans of the eviction path followed by a single data block scan.

A useful property of Circuit ORAM's eviction algorithm. For the majority of this paper

with the exception of Section A, the reader needs not know the details of the eviction algorithm. However, we point out a useful observation regarding Circuit ORAM's eviction algorithm.

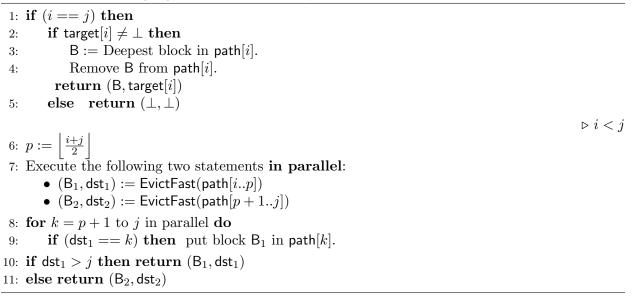

Fact 1 (Circuit ORAM eviction). Suppose Circuit ORAM's eviction algorithm is run once on some path denoted path[0..L], where by convention we use path[0] to denote the root (together with the stash) and path[L] is the leaf in the path. Then, for every height  $i \in \{1, ..., L\}$ , it holds that at most one block moves from path[0..i - 1] to path[i..L]. Further, if a block did move from path[0..i - 1] to path[i..L], then it must be the block that can be evicted the deepest along the eviction path (and if more than one such block exists, an arbitrary choice could be made).

**Recursion.** So far, we have assumed that the CPU can store the entire position map posmap in its local cache. This assumption can be removed using a standard recursion technique [30]. Specifically, instead of storing the position map in the CPU's cache, we store it in a smaller ORAM in memory — and we repeat this process until the position map is of constant size.

As long as each block can store at least two position identifiers, each level of the recursion will reduce the size of the ORAM by a constant factor. Therefore, there are at most  $O(\log N)$  levels of recursion. Several tree-based ORAM schemes also describe additional tricks in parametrizing the recursion for larger block sizes [33,34]. We will not describe these tricks in detail here, but later in Section 8 we will recast these tricks in our OPRAM context and describe further optimizations for large block sizes.

**Circuit ORAM performance.** For general block sizes, Circuit ORAM achieves  $O(\alpha \log N)$  blowup (in terms of bandwidth and the number of accesses) in the non-recursive version, and  $O(\alpha \log^2 N)$  blowup across all levels of recursion. The CPU needs to hold only O(1) blocks at any point in time.

### 2.2 Simplifying Assumptions and Notations

To aid understanding, let us first make a few simplifying assumptions — all these assumptions are not needed in our final scheme, we make them here only for ease of exposition.

- Every PRAM step contains m access requests, where m is a power of 2. For the time being, we consider that m is fixed. We will also assume that all these m access requests ask for *distinct* logical addresses if not, as Boyle et al. pointed out [3], we can easily adopt a conflict resolution algorithm to suppress and replace duplicate requests with dummy ones, and after data has been fetched, oblivious multicast techniques can send fetched data to all request CPUs. Boyle et al. [3] showed that such conflict resolution and multicast can be implemented obliviously with total  $O(m \log m)$  work and  $O(\log m)$  parallel runtime.

- Initially, it will help the reader to think of the special case where  $m = \sqrt{N}$  (or  $m = N^{\epsilon}$  for any constant  $0 < \epsilon < 1$ ). Note that in this case,  $O(\log m)$  and  $O(\log N)$  are the same. In some sense, only intermediate values of m are interesting. When m is as large as  $\Theta(N)$ , we can simply have N CPUs perform *oblivious routing* [3] to serve m simultaneous requests. On the other hand, when m is as small as O(1), the OPRAM basically degenerates to the sequential case of ORAM.

In our formal scheme description later, we will express our bounds for general m and N.

### 2.3 Pre-Warmup: The CLT OPRAM Scheme

We outline the approach of Chen et al. [6] which achieves  $O(\log^3 N)$  blowup in both total work and parallel runtime. We describe a variant of their scheme [6] that uses Circuit ORAM instead of Path ORAM, but in a way that captures all the core ideas of Chen et al. [6]. Suppose we start with Circuit ORAM [34], the state-of-the-art tree-based ORAM. Circuit ORAM is sequential, i.e., supports only one access at a time — but we now would like to support m simultaneous accesses.

Challenge for parallel accesses: write conflicts. A strawman idea for constructing OPRAM is to have m CPUs perform m ORAM access operations simultaneously. Reads are easy to handle, since the m CPUs can read m paths simultaneously. The difficulty is due to write conflicts, which arise from the need for m CPUs to 1) each remove a block from its bucket if it is the requested one; and 2) to perform eviction after the reads. In particular, observe that the paths accessed by the m CPUs overlap, and therefore it may be possible that two or more CPUs will be writing the same location at the same time. It is obvious that if such write conflicts are resolved arbitrarily where an arbitrary CPU wins, we will not be able to maintain even correctness.

Subtree partitioning to reduce write contention. Chen et al.'s core idea is to remove buckets from smaller heights of the Circuit ORAM tree, and start at a height with m buckets. In this way, we can view the Circuit ORAM tree as m disjoint subtrees — write contentions can only occur inside each subtree but not across different subtrees.

Now since there are m CPUs in the original PRAM, each batch contains m memory access requests — without loss of generality, we will assume that all of these m requests are distinct — had it not been the case, it is easy to apply the conflict resolution algorithm of Boyle at al. [3] to achieve distinctness.

Each of these *m* requests will look for its block in a random subtree independently. By the Chernoff bound, each subtree receives  $O(\alpha \log m)$  requests with all but negligible probability. Chen et al.'s algorithm proceeds as follows, where performance metrics are for the non-recursive version.

- 1. Fetch. A designated CPU per subtree performs the read phase of these  $O(\alpha \log m)$  requests sequentially, which involves reading  $O(\alpha \log m)$  paths in the tree. Since each path is  $O(\log N)$  in length, this step incurs  $O(\alpha m \log m \log N)$  total work and  $O(\alpha \log m \log N)$  parallel runtime.

- 2. Route. Obliviously route the fetch results to the requesting CPUs. This step incurs  $O(m \log m)$  total work and  $O(\log m)$  depth.

- 3. Remap. Assign each fetched block to a random new subtree and a random leaf within that subtree. Similarly, each subtree receives  $\mu = O(\alpha \log m)$  blocks with extremely high probability. Now, adopt an oblivious routing procedure to route exactly  $\mu$  blocks back to each subtree, such that each tree receives blocks destined for itself together with padded dummy blocks. This step incurs incurs  $O(\alpha m \log^2 m)$  total work and  $O(\log m)$  parallel runtime.

- 4. Evict. Each subtree CPU sequentially performs  $\mu = O(\alpha \log m)$  evictions for its own subtree. This step incurs  $O(\alpha m \log m \log N)$  total work and  $O(\alpha \log m \log N)$  parallel runtime.

Note that to make the above scheme work, Chen et al. [6] must assume that each subtree CPU additionally stores an  $O(\alpha \log N)$ -sized stash that holds all overflowing blocks that are destined for the particular subtree — later in our scheme, we will get rid of this CPU cache, such that each CPU only needs O(1) blocks of transient storage and does not need any permanent storage.

**Recursive version.** The above performance metrics assumed that all CPUs get to store, read, and update a shared position map for free. To remove this assumption, we can employ the standard recursion technique of the tree-based ORAM framework [30] to store this position map. Assuming that each block has size at least  $\Omega(\log N)$  bits, there can be up to  $\log N$  levels of recursion.

Therefore, assuming  $m = \sqrt{N}$ , the total work across all levels of recursion is  $O(\alpha m \log^3 N)$ , and the parallel runtime is  $O(\alpha \log^3 N)$  for Chen et al. [6].

# 2.4 Warmup: Achieve $O(\log^2 N)$ Blowup in Total Work and Parallel Runtime

As a warmup exercise, we describe a basic scheme that achieves  $O(\log^2 N)$  blowup in total work and parallel runtime. Since this is not our final construction, we will not formalize this warmup scheme later.

We stress that even this warmup scheme already achieves asymptotic savings in comparison with the state-of-the-art OPRAM: as mentioned, the best existing scheme Chen et al. [6] achieves  $O(\log^3 N)$  blowup in both total work and depth; and thus our warmup scheme saves a logarithmic factor in both metrics. To achieve this, we introduce a few new techniques on top of Chen et al. [6] — although the warmup scheme is not the most technically sophisticated part of our work, these new techniques are nonetheless non-trivial and interesting in their own right.

A pool and 2m subtrees: reduce write contention by partitioning. Following the approach of Chen et al. [6], we reduce write contention by partitioning the Circuit ORAM into 2m subtrees<sup>3</sup>. However, on top of Chen et al. [6], we additionally introduce the notion of a pool, a data structure that we will later utilize to amortize evictions across time<sup>4</sup>.

We restructure a standard Circuit ORAM tree in the following manner. First, we consider a height with 2m buckets, which gives us 2m disjoint subtrees. All buckets from smaller heights, including the Circuit ORAM's stash, contain at most  $O(m + \alpha \log N)$  blocks— we will simply store these  $O(m + \alpha \log N)$  blocks in an unstructured fashion in memory, henceforth referred to as a *pool*.

**Fetch.** Whenever there are m CPUs requesting (distinct) blocks, we now need to look up the blocks in two places:

• Subtree lookup: Each of the *m* requests will go to a random subtree. Clearly each subtree gets O(1) number of requests in expectation. Further, by a simple Chernoff bound, each subtree gets  $O(\alpha \log N)$  requests with all but negligible probability in *N*. Note that this already serves to reduce write contention, since each subtree now gets  $O(\alpha \log N)$  contention, as opposed to *m*, had had we used *m* disjoint subtrees. The best existing scheme by Chen et al. [6] stops here and does not further parallelize within each subtree but we will. It is easy to observe that reading up to  $O(\alpha \log N)$  paths can easily be parallelized by assigning each path to a designated path-CPU. This way, in  $O(\log N)$  steps, each path-CPU fetches the requested block (or dummy) from its own path — for the time being, we do not need to parallelize reads over a path, but we will later.

All fetched blocks are merged into the central pool. Notice that at this moment, the pool size has grown by a constant factor, but later in a cleanup step, we will compress the pool back to its original size. Also, at this moment, we have not removed the requested blocks from the subtrees yet, and we will remove them later in the maintain phase.

• Pool lookup: At this moment, all requested blocks must be in the pool. We now rely on oblivious routing to route blocks back to each requesting CPU. More specifically, we assign O(m) auxiliary CPUs, one to each block in the pool. Now, using blivious routing (described in Section 2.2), the m request CPUs can each get back the item requested, or output  $\perp$  if not found. This results in  $O(m \log m)$  total work and  $O(\log m)$  parallel runtime.

Maintain. In the maintain phase, we must 1) remove all blocks fetched from the paths read; and 2) perform eviction on each subtree.

• Efficient simultaneous removals. After reading each subtree, we need to remove up to  $\mu := O(\alpha \log N)$  blocks that are fetched. Such removal operations can lead to write contention when

<sup>&</sup>lt;sup>3</sup>Although we choose 2m for concreteness, any  $c \cdot m$  for a constant c > 1 would work.

$<sup>^{4}</sup>$ In our final scheme, this (flat) pool will be replaced with (semi-structured) group stashes — an ingredient (among several others) necessary to achieve small parallel runtime.

done in parallel: since the paths read by different CPUs overlap, up to  $\mu := O(\alpha \log N)$  CPUs may try to write to the same location in the subtree.

Therefore, we propose a new oblivious parallel algorithm for efficient simultaneous removal. Our algorithm allows removal of the m fetched blocks across all trees in  $O(m \log N)$  total work and  $O(\log m)$  parallel runtime.

We defer the detailed description of this simultaneous removal algorithm to Section 5.1.

• Lazy evictions. Simultaneous evictions are even trickier to handle than simultaneous removals. Recall that after the reads and the simultaneous removals, each block fetched is now assigned to a new random subtree (and a random new leaf). Similarly due to a simple Chernoff bound, we can show that with all but negligible probability, each subtree receives at most  $\mu := O(\alpha \log N)$ blocks to be evicted into that subtree. Notice that to retain obliviousness, the number of blocks getting reassigned to any subtree must be kept secret.

A naive approach therefore is to perform  $\mu := O(\alpha \log N)$  evictions per subtree per access. Unfortunately, this clearly incurs an extra  $\log N$  factor in total work. In particular, observe that in expectation each subtree gets reassigned only O(1) number of blocks from the current batch fetched, but we would be making every subtree suffer from an extra  $\alpha \log N$  if we made  $\mu$  evictions per subtree.

Our solution is lazy eviction. Instead of making  $\mu := O(\alpha \log N)$  evictions per access, we amortize evictions over time: with each access, we stipulate that each subtree gets to evict exactly *once*, i.e., on exactly one eviction path chosen according to some data independent criterion. Any block assigned to the subtree that cannot be evicted or simply overflows from the subtree is entered into the central pool. As we mention later, it is not hard to see that the pool size can be upper bounded by O(m) with all but negligible probability.

• Efficient pool-to-subtree routing. At this moment, it helps to think of the pool as the union of all subtrees' stashes, where each subtree's stash is the union of overflowing blocks destined for the subtree. Suppose an eviction CPU is in charge of evicting on a particular path in subtree *i*. A naive approach would require the CPU to extract the stash for subtree *i* from the pool.

Recall that with Circuit ORAM, each subtree's stash is O(1) in expectation but more than  $\Omega(\alpha \log N)$  in the rare case. To retain obliviousness, we cannot reveal how many blocks in the pool are destined for each subtree. Therefore, a naive approach is to rely on oblivious routing, such that we start out with the pool of O(m) blocks, and at the end of the routing, every subtree's eviction CPU obtains  $O(\alpha \log N)$  possibly dummy blocks. Unfortunately, this naive approach incurs an extra  $O(\alpha \log N)$  blowup due to an average-case rare-case discrepancy — effectively we are padding to the worst-case for obliviousness, and we thus incur the rare-case cost rather than the average-case.

Fortunately, this need not be the case. Here we leverage a special property of the Circuit ORAM algorithm: due to Fact 1, each eviction on a path will move at most one block — particularly the *deepest* block with respect to the eviction path — from the stash into the tree. Since we perform O(1) evictions per subtree per access, it suffices to route O(1) blocks from the pool to each subtree rather than routing the entire subtree's stash which can be as large as  $O(\alpha \log N)$ . We can achieve such routing in  $O(m \log m)$  total work and  $O(\log m)$  parallel runtime by oblivious sorting. The routing algorithm will need to use the Circuit ORAM's *deepest* criterion for selecting the blocks for each subtree.

• *Pool cleanup.* At the end of the maintain phase, we must compress the pool back to  $c \cdot m$  blocks for some fixed constant c. Otherwise, the pool will keep growing as we place more fetched blocks in them. Such compression can easily be achieved through oblivious sorting.

To make this work, we need to prove a concentration bound that the pool size will be bounded by O(m) with all but negligible probability — despite lazy eviction and possibly more blocks overflowing into the pool as a result. Since each of the 2m subtrees in expectation gets back only  $\frac{1}{2}$  block with each batch of accesses, as long as we perform at least one eviction per subtree per access, it is not hard to show that at any time, the pool size is bounded by O(m) except with negligible probability.

Later in our paper, we will also form semi-structured group stashes from this flat pool for reasons we shall explain. Therefore, rather than proving the above bound on the pool, our formal sections will instead bound the group stashes.

Notable differences from Chen et al. [6]. In summary, even our warmup scheme asymptotically improves the state-of-the-art OPRAM [6] through several non-trivial techniques. Specifically, the key new ideas are the following:

1. We avoid suffering from the average-case rare-case discrepancy by amortizing evictions across time. To enable this we need a couple techniques, including introducing an O(m)-sized pool to hold overflowing blocks; and leveraging a special property of the Circuit ORAM algorithm as mentioned above.

As a result, we perform only O(1) evictions per subtree per request, and we only need to oblivious route O(1) blocks to each subtree for eviction. In comparison, Chen et al. [6] obliviously routes  $O(\alpha \log m)$  blocks to each subtree and performs  $O(\alpha \log m)$  evictions per subtree. At the moment, we can simply think that each eviction along a path is performed sequentially by a single CPU as described in [34]. However, in Appendix A, we shall see that each path eviction can be parallelized to reduce the asymptotic parallel runtime when the block size is large.

2. While Chen et al. [6] performs up to  $\mu := O(\alpha \log m)$  read and remove operations within each subtree sequentially, we parallelize the operations within each subtree. To do this, we need to design a novel simultaneous removal algorithm to avoid write conflicts (see Section 5).

**Performance.** When we count all  $O(\log N)$  recursion levels, the above warmup scheme achieves  $O(\log^2 N)$  blowup in both total work and parallel runtime.

**Bound on pool occupancy.** To obtain a bound on the pool occupancy at the end of each batch of accesses, we need to prove the following. First, to analyze the stochastic process, we imagine that there is an imaginery big ORAM tree where levels  $\log_2(m)$  or above correspond to our OPRAM's subtrees, and all smaller levels correspond to the pool. Our stochastic process is very similar to that of Circuit ORAM, but with the following difference. In Circuit ORAM, we always read and remove a block, and then perform exactly one eviction. Here, we perform m read and remove operations and then m evictions. We henceforth refer to the latter stochastic process Batched Circuit ORAM. Modulo the parallelism, the stochastic process of the warmup OPRAM scheme is identical to that of Batched Circuit ORAM. We then show that Circuit ORAM stochastically dominates Batched Circuit ORAM in terms of the number of blocks in the smaller  $\log_2(m)$  levels of the tree (see Section 5.6). We can then bound the pool size of the warmup scheme by bounding the total number of blocks in the smaller  $\log_2(m)$  levels of a Circuit ORAM tree. It is not hard to see that the pool occupancy does not exceed  $O(m) + \alpha \log N$  except with negligible probability.

**Remark 1.** We remark that when the block size is large enough, i.e.,  $B = N^{\epsilon}$ , the warmup scheme already achieves asymptotic optimality in terms of both total work and parallel runtime when  $m = N^{\epsilon}$ , where *m* denotes the number of PRAM CPUs and *N* denotes the total number of memory blocks. In the remainder, we consider a model where the OPRAM is allowed to consume more CPUs than the original PRAM. We show that in this case, the parallel runtime can be further reduced asymptotically.

### 2.5 Achieve Small Parallel Runtime: The Challenges

Previous works on OPRAM assume that the OPRAM must consume the same number of CPUs as the PRAM, and they aim to use a small number of OPRAM steps to simulate each PRAM step. In this case, the parallel runtime and total work are the same.

We consider a new OPRAM model where the OPRAM can consume more CPUs than the PRAM. We show that in this case, the parallel runtime blowup of the OPRAM can be further reduced. from  $O(\log^2 N)$  to  $O(\log N \log \log N)$  while preserving total work. Achieving this turns out to be highly non-trivial. We also remark that the  $\Omega(\log m)$  parallel runtime lower bound by Chan et al. is for this more permissive model, i.e., even when the OPRAM can consume more CPUs than the PRAM, there is still an  $\Omega(\log m)$  lower bound in parallel runtime. It turns out that reducing the parallel runtime incurs significant challenges.

To distinguish between different levels of recursion, we refer to the highest-level OPRAM holding the N original blocks as data-OPRAM. For each  $1 \le i < \log_2 N - 1$ , we refer to the level-*i* ORPAM as pos-OPRAM<sub>i</sub>, which holds  $2^i$  blocks.

In Section 2.4, we saw that each level of the recursion is a non-recursive OPRAM that has a fetch phase and a maintain phase. The fetch phase is inherently sequential across all recursion levels: one must look up the leaf identifier of the next level before proceeding to read the next recursion level. On the other hand, the maintain phase is trivially parallelizable across all recursion levels: after m blocks are fetched, the data-OPRAM and all pos-OPRAMs can perform the write-back process simultaneously. Therefore, over all recursion levels, the maintain phase's parallel runtime does not blow up due to recursion, but the fetch phase's parallel runtime must be multiplied by an  $O(\log N)$  factor that is the depth of the recursion.

**Goals.** Henceforth we will focus on how to reduce the parallel runtime of the fetch phase of each non-recursive OPRAM. Our goals include the following:

- 1. For each pos-OPRAM, we would like to achieve  $O(\log \log N)$  parallel runtime for the fetch phase.

- 2. However, we allow the (highest-level) data-OPRAM's fetch phase to have  $O(\log \log N + \log m)$  parallel runtime the data-OPRAM is special because requests must be routed to the request CPUs at the end, and this routing step will incur  $O(\log m)$  parallel runtime.

- 3. We would like to achieve the reduction in parallel runtime while maintaining the same asymptotic total work.

**Dissecting the challenges.** We now dissect our warmup scheme described in Section 2.4, particularly focusing on what it takes to reduce the parallel runtime of the fetch phase. The fetch phase of the warmup scheme involves three major steps (all other operations such as simultaneous removal of fetched blocks, routing from pool to subtrees, and evictions are non-blocking and are considered part of the maintain phase):

- Subtree lookup (easy): First, the warmup scheme involves reading m tree paths. This step can be quite trivially parallelized achieving  $O(\log \log N)$  parallel runtime and without blowing up total work. First, we we assign  $\log N$  CPUs per path to read each physical location on all paths simultaneously. Then we run an instance of the parallel oblivious select algorithm (see Section 3.3) per path to aggregate each path's fetch result to a designated CPU.

- Pool lookup (hard): In the warmup scheme, the fetch phase also involves looking for the m requested blocks in the pool. This may be achieved with oblivious routing, which unfortunately takes  $\Theta(\log m) = \Theta(\log N)$  parallel runtime (when  $m = \sqrt{N}$  for instance). At this moment, it is not straightforward how to reduce the parallel runtime incurred in this step in fact, as

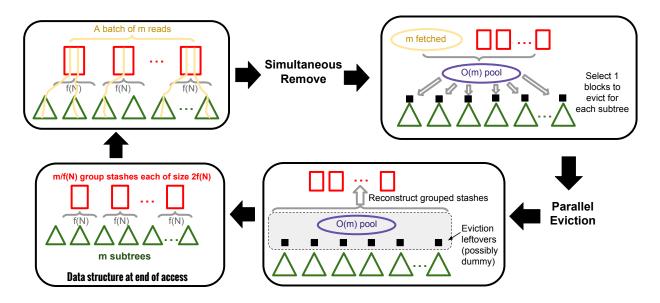

Figure 1: Circuit OPRAM data structure and operations.  $f(N) := \alpha \log N$  for some  $\alpha = \omega(1)$ .

we describe later, new techniques are required, involving replacing the (flat) pool with (semistructured) group stashes instead.

Route position identifiers fetched in one level to the next level's fetch CPUs (hard): Another notable difficulty is how to route the fetched position identifiers in one recursion level to the next level's fetch CPUs, who need to know which tree paths to look for the blocks. For simplicity, let us imagine that in the d-level of recursion, a pos-OPRAM<sub>d</sub> block with address addr ∈ {0,1}<sup>d</sup> stores two position identifiers for the (d + 1)-level addresses (addr||0) and (addr||1) ∈ {0,1}<sup>d+1</sup>. At the next level of recursion, there are 1 or 2 fetch CPUs waiting for the corresponding leaf identifiers. Routing fetched results to the next level's fetch CPUs must be done obliviously, e.g., without revealing whether both (addr||0) and (addr||1) are consumed by the next level of recursion, or only one of them is (and if so, which one).

Again, a naive approach is to rely on oblivius routing, but again this would incur  $\Theta(\log m)$  parallel runtime which is too expensive for our purpose.

In the next two subsections, we will describe how to address each of the above challenges identified. We will start by describing how to avoid using oblivious routing for the pool reads. Next, we will describe how to route fetched results to the next recursion level's fetch CPUs in small parallel runtime.

### 2.6 From Flat Pool to Semi-Structured Group Stashes

**Two extremes.** As mentioned earlier, reading the (structured) tree paths requires  $O(\log \log N)$  parallel runtime whereas fetching from the flat pool takes  $\Theta(\log m)$  parallel steps due to oblivious routing. Previously, we have described two approaches at two ends of the spectrum:

1. The OPRAM scheme by Chen et al. [6] routes all fetched blocks back to each subtree during the offline phase. Thus, for every access, their scheme requires routing  $O(\alpha \log N)$  blocks to each subtree and performing  $O(\alpha \log N)$  evictions per subtree. Each subtree has a stash of  $O(\alpha \log N)$

in size. Therefore, this approach is inefficient during the maintain phase but the fetch phase can be done in  $O(\log \log N)$  parallel time for each recursion level.

2. By contrast, our warmup scheme (Section 2.4) routes only 1 block back to each subtree and performs 1 eviction per subtree for each access. However, our warmup scheme requires an O(m) flat pool to store overflowing blocks. In comparison, our warmup scheme is more efficient than Chen et al. [6] in the maintain phase by a logarithmic factor, but unfortunately the introduction of the flat pool causes reads in the fetch phase to take  $\Theta(\log m)$  parallel time.

**Our approach: seek middle ground.** Our approach seeks a middle ground between these two extremes. At the end of the maintain phase, we convert the pool to  $\frac{2m}{\alpha \log N}$  group stashes where each group stash is the shared stash of  $\alpha \log N$  subtrees. Each group stash obtains  $\alpha \log N$  blocks in expectation, and  $2\alpha \log N$  blocks with all but  $\operatorname{negl}(N)$  probability, because  $\alpha = \omega(1)$ . Notably, except with negligible probability, the group stash's occupancy is only a constant factor larger than is mean. Therefore, constructing the group stashes from the flat pool could be achieved by obliviously routing  $2\alpha \log N$  possibly dummy blocks to each group stash — and this incurs  $O(m \log m)$  total work and  $O(\log m)$  parallel time. The advantage to incur  $O(\log m)$  parallel time in the maintain phase (as opposed to the fetch phase) is that the maintain phases across different levels of recursion can be performed in parallel, whereas the fetch phases of different levels have to be performed sequentially.

Observe that in the fetch phase of the next step, the group stashes are ready to be used. At the beginning of the maintain phase, we just take the union of the group stashes and the fetched blocks and treat it as a flat pool again.

Another way to view our scheme is the following: at the end of the maintain phase, we perform some preparation work to restore some structure on the O(m) flat pool containing overflowing blocks. With such preparation, during the batch of reads in the next fetch phase, each subtree can view the corresponding group stash as part of its root bucket — we can therefore leverage the aforementioned oblivious aggregation algorithm to perform reads in  $O(\log \log N)$  parallel steps.

At this moment, the most significant missing piece is how one can efficiently route the fetched position identifiers to the next recursion level, which we shall explain in the next subsection.

#### 2.7 Routing Fetched Position Identifiers to the Next Recursion Level

Recall that the problem is the following: m fetch CPUs at recursion level d have fetched position identifiers to be sent to recursion level d + 1. We would like to route these position identifiers to the corresponding fetch CPUs at level d + 1. A naive approach is to rely on oblivious routing — but this would incur  $\Theta(\log m)$  parallel steps. Improving this in small parallel runtime turns out to be rather challenging.

**Notations.** To understand our solution, it helps to introduce a few notations. We will henceforth assume a fan-out of 2, i.e., each block holds exactly two position identifiers.

Let  $D := \log_2 N$  denote the total number of recursion levels. Let  $\operatorname{addr}^{\langle D \rangle} \in \{0, 1\}^D$  denote a virtual address. We will use the notation  $\operatorname{addr}^{\langle d \rangle}$  to denote a truncated *d*-bit address at recursion level *d*. If we access a block with virtual address  $\operatorname{addr}^{\langle d \rangle}$  in recursion level *d*, we can obtain the position identifiers of the next-level addresses  $(\operatorname{addr}||0)^{\langle d \rangle}$  and  $(\operatorname{addr}||1)^{\langle d \rangle}$ .

Suppose that at the beginning of each PRAM step, a preparation procedure is performed in parallel across all recursion levels. This preparation procedure examines the batch of m virtual addresses requested (again, without loss of generality, we assume that conflict resolution has already been done and that the m virtual addresses are distinct). Then, at each recursion level d, the preparation procedure writes down the following *instruction array* (at this moment we simply claim

that such preparation can be done efficiently and we defer the detailed algorithm to Section 6.3):

$$\underline{\text{Incomplete instruction array:}} \ \mathsf{Instr}^{\langle d \rangle} := \Big\{ (\mathsf{addr}^{\langle d \rangle}, \mathsf{flag}, \_) \mid \mathsf{dummy} \Big\}_{2m}$$

Specifically, each entry of the instruction array is either a dummy element (denoted dummy) or is a real instruction of the form  $(\operatorname{addr}^{\langle d \rangle}, \operatorname{flag}, \_)$  where  $\operatorname{addr}^{\langle d \rangle}$  is a virtual address at level d, and flag is a 2-bit indicator that indicates whether each child of the address  $\operatorname{addr}^{\langle d \rangle}$  (i.e., the level-(d + 1)addresses  $(\operatorname{addr}||0)^{\langle d+1 \rangle}$  and  $(\operatorname{addr}||1)^{\langle d+1 \rangle}$ ) is requested at the next level. At this moment, each instruction is *incomplete*, and the wildcard \_ is an empty space left to later receive the position identifier for  $\operatorname{addr}^{\langle d \rangle}$  — only when the position identifier is received, can a fetch CPU actually execute the instruction. Finally, the subscript 2m denotes the length of the array. Even though there are at most m requests per recursion level, for reasons explained later, we need to pad the instruction array with dummy elements to size 2m. To ensure obliviousness, the entries of the array are randomly permuted obliviously.

Now, each of the 2m fetch CPU at recursion level d reads a block that contains two next-level position identifiers. We call the result of the read a *fetched array* whose size is 4m (note the factor-2 blowup in size)<sup>5</sup>:

$$\underline{\text{Fetched position identifiers:}} \hspace{0.1 cm} \text{Fetched}^{\langle d \rangle} := \left\{ (\mathsf{addr}^{\langle d+1 \rangle}, \mathsf{pos}) \mid \mathsf{dummy} \right\}_{4m},$$

where **pos** denotes the current position identifier for the virtual address  $\operatorname{addr}^{\langle d+1 \rangle}$  at recursion level d+1. Since a complete instruction contains a flag that indicates whether each of the next-level child address is needed, we assume that the Fetched<sup> $\langle d \rangle$ </sup> array has suppressed all level-(d+1) addresses not requested and replaced them with dummy.

Problem statement. We now have to solve the following challenge: given the following arrays

$$\mathsf{Fetched}^{\langle d \rangle} := \Big\{ (\mathsf{addr}^{\langle d+1 \rangle}, \mathsf{pos}) \mid \mathsf{dummy} \Big\}_{4m} \quad \mathrm{and} \quad \mathsf{Instr}^{\langle d+1 \rangle} := \Big\{ (\mathsf{addr}^{\langle d+1 \rangle}, \mathsf{flag}, \_) \mid \mathsf{dummy} \Big\}_{2m}$$

perform routing to "complete" the instructions at recursion level d + 1 where each incomplete instruction at recursion level d+1 receives the correct position identifier, thus forming a *completed* instruction array denoted  $\mathsf{CInstr}^{\langle d+1 \rangle}$ :

$$\underline{\text{Completed instruction array:}} \quad \mathsf{CInstr}^{\langle d+1\rangle} := \Big\{ (\mathsf{addr}^{\langle d+1\rangle},\mathsf{flag}, \ \mathsf{pos}) \mid \mathsf{dummy} \Big\}_{2m}$$

As mentioned earlier, we would like to achieve this in a small number of (online) parallel steps.

Overview of our approach. Our approach involves two steps:

1. Localized compression. Compress the 4*m*-sized Fetched<sup> $\langle d \rangle$ </sup> array back to size 2*m*, suppressing dummy elements. We will henceforth refer to this compressed array as Send<sup> $\langle d \rangle$ </sup> (whose type declaration is below):

$$\underline{\text{Compressed fetched position identifiers:}} \quad \mathsf{Send}^{\langle d \rangle} := \left\{ (\mathsf{addr}^{\langle d+1 \rangle}, \mathsf{pos}) \mid \mathsf{dummy} \right\}_{2m}$$

The challenge here is that we cannot resort to a global oblivious sort for compression. Instead, we propose an algorithm that localizes the compression work to each smaller group of elements.

$<sup>{}^{5}</sup>$ In the real construction detailed in Section 6, each entry of the fetched array actually carries the current position identifier **pos**, as well as the new (random) position identifier **pos'** of the corresponding block. We omit this here for clarity of exposition.

2. Use an offline/online paradigm for routing. Observe that at each recursion level, a read cannot be executed until the required position identifiers are received from the previous level.

Instead of performing all the work associated with one level before starting the next level, we observe that in each level, part of the work can be performed without the knowledge of the position identifiers from the previous level. We refer to this part of the work as the *offline* phase, which can be performed in parallel across all levels. We shall see that in the offline phase, for each level d, we pre-compute a permutation that will align the arrays  $\text{Send}^{\langle d \rangle}$  and  $\text{Instr}^{\langle d+1 \rangle}$  with respect to the level-(d+1) addresses.

In contrast, the *online* phase refers to work that can be performed only when the position identifiers are known, and hence is performed sequentially level by level. After the reads are performed in level d to form the Send<sup> $\langle d \rangle$ </sup> array, we can make use of the pre-computed permutation in the offline phase to "send" the required position identifiers to the correct entries in  $Instr^{\langle d+1 \rangle}$  using only O(1) parallel runtime.

To accomplish either of the above would require non-trivial techniques as we explain below.

**Localized oblivious compression.** Suppose we have an array of 4m elements of which at most m are real. How can we obliviously compress the array down to 2m elements such that all real elements are preserved (i.e., 2m dummy elements are removed)? A naive idea is to rely on oblivious sorting over these 4m elements, but this would incur  $\Theta(\log m)$  parallel runtime and would be too expensive.

Our key idea is to "localize" the compression. Suppose that these 4m elements have been randomly permuted. Then, every consecutive  $2\alpha \log N$  group of elements can only have  $\alpha \log N$ real elements with all but negligible probability<sup>6</sup>, where  $\alpha = \omega(1)$  is any super-constant function. Since this is true, we can perform *localized* oblivious compression, by performing oblivious sorting (where real elements have higher priority) on each non-overlapping group of  $2\alpha \log N$  consecutive elements and discarding half of the elements in each group with the lowest priorities. This incurs only  $O(\log \log N)$  parallel runtime instead of  $O(\log N)$ .

**Offline/online routing.** After the oblivious compression phase, we obtain a send array of the form  $\mathsf{Send}^{\langle d \rangle} := \{(\mathsf{addr}^{\langle d+1 \rangle}, \mathsf{pos}) \mid \mathsf{dummy}\}_{2m}$ . This send array contains the fetched position identifiers of the next recursion level. The next level's instruction array  $\mathsf{Instr}^{\langle d \rangle} := \{(\mathsf{addr}^{\langle d \rangle}, \mathsf{flag}, \_) \mid \mathsf{dummy}\}_{2m}$  must now receive these position identifiers such that the instructions can be completed. Again, we would like to achive this without performing oblivious routing in the online phase.

Our idea is the following: what if, in the offline phase, it is possible to figure out the permutation to align the arrays  $\text{Send}^{\langle d \rangle}$  and  $\text{Instr}^{\langle d+1 \rangle}$  with respect the level-(d+1) addresses? In this way, the online phase can simply apply the permutation in a single parallel step to align the two arrays, after which "receiving" the position identifiers becomes a simple coordinate-wise copy. Below we describe how to carry out this idea in a way that guarantees obliviousness. The offline phase performs the following:

- 1. Oblivious random permutation of incomplete instruction arrays. First, in the offline preparation phase, after generating the incomplete instruction array  $\mathsf{Instr}^{(d+1)}$  at each recursion level d, we permute this array at random obliviously, i.e., without revealing the random permutation.

- 2. Offline emulation of the online phase. Next, the offline preparation phase will emulate the online execution but without filling in the actually fetched contents. Specifically, it will emulate the

<sup>&</sup>lt;sup>6</sup>Recall that we need to pad each recursion level to 2m instructions. The reason is the following: for the oblivious compression to cut half of the elements, the fraction of real elements in the array must be a constant smaller than  $\frac{1}{2}$ . Here we set this fraction to be  $\frac{1}{4}$ .

$\overline{\mathsf{Fetched}}^{\langle d \rangle}$  array (while leaving the fetched position identifiers blank). Then, it will emulate the oblivious compression which results in the send array  $\overline{\mathsf{Send}}^{\langle d \rangle}$ . We use the notational convention  $\overline{\mathsf{arr}}$  to denote the offline, emulated version of  $\mathsf{arr}$  — specifically,  $\overline{\mathsf{arr}}$  is the same as  $\mathsf{arr}$  except that it leaves the fetched position identifiers and contents blank.

3. Construction of the routing permutation. Finally, the offline phase will figure out the permutation to apply to  $\overline{\mathsf{Send}}^{\langle d \rangle}$  such that it is aligned with  $\mathsf{Instr}^{\langle d+1 \rangle}$ . This step can be achieved through a sequence of oblivious sorts as we describe in detail in Section 6.3.

It is not hard to see that the above offline operations can be parallelized across multiple recursion levels. As a result, the offline phase can be completed in  $O(\log m)$  parallel runtime, and  $O(\alpha m \log m \log N)$  total work — we defer a more detailed explanation to Section 6.3.

Given the above offline preparation, we quickly recap the online phase for clarity:

1. Let d denote the current recursion level. Assign 2m fetch CPUs, each of which read one completed instruction in  $\mathsf{CInstr}^{\langle d \rangle}$ . The completed instruction specifies which path to read and what address to look for. Each fetch CPU recruits log N auxiliary CPUs to read its path and aggregate the result, which contains 2 position identifiers for the next level.

The result of this step is the fetched array  $\mathsf{Fetch}^{\langle d \rangle}$  of size 4m.

- 2. Apply the oblivious compression algorithm to compress  $\mathsf{Fetch}^{\langle d \rangle}$  down to size-2*m* array  $\mathsf{Send}^{\langle d \rangle}$ .

- 3. In a single parallel step, apply the routing permutation that the offline phase has pre-computed to align the arrays  $\text{Send}^{\langle d \rangle}$  and  $\text{Instr}^{\langle d+1 \rangle}$  in order to construct the completed instruction array  $\text{CInstr}^{\langle d+1 \rangle}$  in the next level.

It is not hard to see that the online phase incurs only  $O(\log \log N)$  parallel steps, since both the parallel path read and the localized oblivious compression requires only  $O(\log \log N)$  parallel steps.

**Obliviousness.** It is important to note why the above approach preserves obliviousness. The key observation is that each  $\mathsf{Instr}^{\langle d+1 \rangle}$  array is independently and randomly permuted in the offline phase (without revealing the permutation). Therefore, every permutation from  $\mathsf{Send}^{\langle d \rangle}$  to  $\mathsf{Instr}^{\langle d+1 \rangle}$  that is revealed to the adversary is an independent, random permutation. Therefore, the adversary could have simulated these permutations itself without knowing the data contents.

### 2.8 Putting it Altogether

It is now a good time to give an overview of the resulting scheme (see Figure 1). Below we describe what happens in a pos-OPRAM level. For the (highest-level) data-OPRAM, the operations are almost the same, except that instead of routing position identifiers to the next level's fetch CPUs, the data-OPRAM would instead route fetched blocks to the requesting CPUs. For each of the following steps, we indicate whether it is performed level-by-level sequentially or in parallel across different recursion levels of pos-OPRAM.

• All levels in parallel: offline preparation. Given a batch of memory requests (assume distinct addresses), perform offline preparation at all recursion levels. As mentioned in Section 2.7, the offline preparation is necessary to allow the online fetch phase to have small parallel runtime.

- Level-by-level: fetch. Given 2m fetch instructions at a recursion level among which at most m are real<sup>7</sup>, in parallel perform 2m reads, each of which involves reading blocks from 1) a path in the corresponding subtree; and 2) the subtree's corresponding group stash. The parallel reads can be accomplished in  $O(\log \log N)$  time for an appropriately small  $\alpha = \omega(1)$ .

- Level-by-level: route position identifiers to next level (Section 2.7). Each of the 2m fetches returns a block. Without loss of generality, suppose that each block contains 2 position identifiers (for the next level). Among these resulting 4m position identifiers, at most m of them are needed by the next recursion level (recall that the next recursion level will also have 2m fetch instructions, of which at most m are real). Now, we leverage a special procedure to route position identifiers to the next level's fetch CPUs in O(1) parallel steps see Section 2.7.

- All levels in parallel: simultaneous removal. Perform a parallel remove procedure to remove all fetched blocks from their respective paths.

- All levels in parallel: eviction. Now, the fetched m blocks and the original group stashes are merged into a flat pool. From this pool, obliviously route exactly one (possibly dummy) block to each subtree for eviction, where the block is selected using Circuit ORAM's "deepest" criterion, where deepest is defined with respect to the current eviction path. Now, perform exactly one eviction per subtree on a path chosen according to the Circuit ORAM algorithm.

- All levels in parallel: reconstruct group stashes and compress. After eviction, each subtree has one (possibly dummy) block leftover. All eviction leftovers are merged into the pool. Now, we leverage oblivious sorting to reconstruct group stashes from the pool. Although not made explicit, we in fact also perform a compression operation along with the reconstruction of the group stashes: notice that the pool has grown due to the addition of the *m* fetched blocks. However, the subtree evictions should in expectation have evicted O(m) blocks back into the subtrees. Therefore, the total occupancy of the pool (or the group stashes) will not keep increasing.

### 2.9 Extensions

Varying number of CPUs. Our overview earlier assumes that the original PRAM always has the same number of CPUs in every time step, i.e., all batches of memory requests have the same size. We can further extend our scheme for the case when the number of PRAM CPUs varies over time. Below we briefly describe the idea while leaving details to Sections 5 and 6. Without loss of generality, henceforth we assume that in every time step, the number of requests in a batch m is always a power of 2 — if not, we can simply round it up to the nearest power of 2 incurring only O(1) penalty in performance.

Suppose that the OPRAM scheme currently maintains  $\hat{m}$  subtrees, but the incoming batch has  $m > \frac{\hat{m}}{2}$  number of requests. In this case, we will immediately adjust the number of subtrees to  $\hat{m} := 2m$ . This can be done simply by merging more heights of the tree into the flat pool (and at the end of the maintain phase, the flat pool will be converted to the group stashes).

The more difficult case is when the incoming batch contains less than  $m < \frac{\hat{m}}{2}$  requests. In this case, we need to decrease the number of subtrees  $\hat{m}$ . However, instead of decreasing  $\hat{m}$  immediately to 2m, we use a *lazy* strategy: every time we halve the value of  $\hat{m}$  — and to achieve this we only need to reconstruct one extra height of the big ORAM tree, which can be achieved through oblivious sorting in  $O(\hat{m} \log \hat{m})$  total work and  $O(\log \hat{m})$  parallel time. In comparison, had we immediately

<sup>&</sup>lt;sup>7</sup>Although at most m fetch instructions are real, we pad the instruction array to 2m with dummy instructions — the need arises due to the algorithms in Section 2.7 for routing fetched position identifiers to the next recursion level.

changed  $\hat{m}$  to 2m, it would have been too expensive to reconstruct up to  $\log N$  heights of the ORAM tree (e.g., when m suddenly drops to 1).

**Results for large block sizes.** When the block size is sufficiently large, we show the following results:

- Circuit OPRAM achieves  $O(\alpha \log N)$  total work blowup, and  $O(\log N)$  parallel runtime. In light of Goldreich and Ostrovsky's  $\Omega(\log N)$  lower bound [16,17], Circuit OPRAM is therefore asymptotically optimal in terms of total work

- We introduce a variant of the scheme called Circuit OPRAM<sup>\*</sup> that achieves  $O(\log N \log \log N)$  total work blowup, and  $O(\log m + \log \log N)$  parallel runtime. In light of the  $\Omega(\log m)$  parallel runtime lower bound by Chan et al. [5], Circuit OPRAM<sup>\*</sup> is asymptotically optimal in terms of parallel runtime when  $m = \Omega(\log N)$ . We stress that to construct this variant requires non-trivial techniques for constructing a parallelized counterpart of Circuit ORAM's eviction algorithm [34].

We defer the technical details and additional extensions and parametrization tricks to Section 8.

### 2.10 Related Work

In the introduction, we compared with some of the closely related works earlier. In this section, we describe additional related work.

**Oblivious RAM (ORAM).** Oblivious RAM (ORAM) was initially proposed by Goldreich and Ostrovsky [16,17] who showed that any RAM program can be simulated obliviously incurring only  $O(\alpha \log^3 N)$  runtime blowup, while achieving a security failure probability that is negligible in N. Numerous subsequent works [9, 18, 22, 26, 27, 30, 33, 34, 34–38] improved Goldreich and Ostrovsky's seminal result in different application settings including cloud outsourcing, secure processor, and secure multi-party computation.

Most of these schemes follow one of two frameworks: the hierarchical framework, originally proposed by Goldreich and Ostrovsky [16, 17], or the tree-based framework proposed by Shi et al. [30]. To date, some of the (asymptotically) best schemes include the following: 1) Kushilevitz et al. [22] showed a *computationally secure* ORAM scheme with  $O(\log^2 N/\log \log N)$  runtime blowup for general block sizes; and 2) Wang et al. construct Circuit ORAM [34], a *statistically secure* ORAM that achieves  $O(\alpha \log^2 N)$  runtime blowup for general block sizes and  $O(\alpha \log N)$  runtime blowup for large enough blocks. Further, using a standard trick initially proposed by Fletcher et al. [11] and later improved in the Circuit ORAM paper [34], we can modify Circuit ORAM into a computationally secure variant by relying on a PRF, and achieve  $O(\alpha \log^2 N/\log \log N)$  runtime blowup where  $\alpha$  can be any super-constant function — this makes Circuit ORAM (almost) competitive to Kushilevitz et al. [22] even for small block sizes. Unfortunately there does not seem to be a straightforward way to adapt this trick to the parallel setting and make it compatible with Circuit OPRAM's level-by-level position map routing algorithm. Therefore we leave it as an open question whether there is an OPRAM scheme that achieves  $O(\log^2 N/\log \log N)$  total work blowup and parallel runtime blowup competitive to Circuit OPRAM.