# Constant-Round Maliciously Secure Two-Party Computation in the RAM Model

Carmit Hazay\* Avishay Yanai\*

#### **Abstract**

The *random-access memory (RAM)* model of computation allows program constant-time memory lookup and is more applicable in practice today, covering many important algorithms. This is in contrast to the classic setting of secure 2-party computation (2PC) that mostly follows the approach for which the desired functionality must be represented as a boolean circuit. In this work we design the first *constant round* maliciously secure two-party protocol in the RAM model. Our starting point is the garbled RAM construction of Gentry et al. [GHL<sup>+</sup>14] that readily induces a constant round semi-honest two-party protocol for any RAM program assuming identity-based encryption schemes. We show how to enhance the security of their construction into the malicious setting while facing several challenges that stem due to handling the data memory. Next, we show how to apply our techniques to a more recent garbled RAM construction by Garg et al. [GLOS15] that is based on one-way functions.

<sup>\*</sup>Bar-Ilan University, Israel. Emails: carmit.hazay@biu.ac.il, ay.yanay@gmail.com. Supported by the European Research Council under the ERC consolidators grant agreement n. 615172 (HIPS) and by the BIU Center for Research in Applied Cryptography and Cyber Security in conjunction with the Israel National Cyber Bureau in the Prime Ministers Office. First author's research partially supported by a grant from the Israel Ministry of Science and Technology (grant No. 3-10883).

# **Contents**

| 1 | Introduction                                                               | 3  |

|---|----------------------------------------------------------------------------|----|

|   | 1.1 Our Results                                                            | 4  |

| 2 | Preliminaries                                                              | 7  |

|   | 2.1 The RAM Model of Computation                                           | 7  |

|   | 2.1.1 Predictably Time Writes                                              | 8  |

|   | 2.2 Oblivious RAM (ORAM)                                                   | 8  |

|   | 2.2.1 Realization of the Modified Definition                               | 9  |

|   | 2.3 Secure Computation in the RAM Model                                    | 10 |

|   | 2.3.1 Full Security                                                        | 10 |

|   | 2.3.2 The UMA Model                                                        | 11 |

|   | 2.3.3 A Transforation From UMA to Full Security                            | 12 |

|   | 2.3.4 On the Capabilities of Semi-Honest in a Garbled RAM and ORAM Schemes | 13 |

|   | 2.4 Timed IBE [GHL <sup>+</sup> 14]                                        | 14 |

|   | 2.5 Garbled RAM Based on IBE [GHL <sup>+</sup> 14]                         | 15 |

|   | 2.6 Garbled Circuits                                                       | 16 |

|   |                                                                            |    |

| 3 | Building Blocks                                                            | 18 |

|   | 3.1 Enhanced CPU-Step Function                                             |    |

|   | 3.2 Initialization Circuit                                                 |    |

|   | 3.3 Batch Single-Choice Cut-And-Choose OT                                  | 20 |

| 4 | The Complete Protocol                                                      | 22 |

|   | 4.1 2PC in the UMA Model                                                   | 23 |

| 5 | Proof of Theorem 4.1                                                       | 26 |

|   | 5.1 The Case S is Corrupted                                                | 26 |

|   | 5.2 The Case R is Corrupted                                                |    |

| _ |                                                                            | 22 |

| 6 | Removing the IBE Assumption                                                | 32 |

|   | 6.1 GRAM Based on OWF [GLOS15]                                             |    |

|   | 6.1.1 Garbling Data                                                        |    |

|   | 6.1.2 Garbling Program                                                     |    |

|   | 6.1.3 Program Execution Demonstration                                      |    |

|   | 6.2 2PC in the Presence of Malicious Adversaries Relying on OWF            | 36 |

| A | Building Blocks                                                            | 40 |

|   | A.1 Garbled Circuits                                                       | 40 |

|   | A.2 The Hybrid Model                                                       | 40 |

|   | A.3 Batch Single-Choice Cut-and-Choose OT                                  |    |

|   | A.4 Commitment Schemes                                                     |    |

|   |                                                                            |    |

# 1 Introduction

Background on secure computation. Secure multi-party computation enables a set of parties to mutually run a protocol that computes some function f on their private inputs, while preserving a number of security properties. Two of the most important properties are privacy and correctness. The former implies data confidentiality, namely, nothing leaks by the protocol execution but the computed output. The latter requirement implies that the protocol enforces the integrity of the computations made by the parties, namely, honest parties learn the correct output. More generally, a rigorous security definition requires that distrusting parties with secret inputs will be able to compute a function of their inputs as if the computation is executed in an ideal setting, where the parties send their inputs to a incorruptible trusted party that performs the computation and returns its result (also known by the ideal/real paradigm). The feasibility of secure computation has been established by a sequence of works [Yao86, GMW87, Bea91, MR91, Can00], proving security under this rigorous definition with respect to two adversarial models: the semi-honest model (where the adversary follows the instructions of the protocol but tries to learn more than it should from the protocol transcript), and the malicious model (where the adversary follows an arbitrary polynomial-time strategy).

Following these works much effort was put in order to improve the efficiency of computation with the aim of minimizing the workload of the parties [JS07, LP07, IPS08] [IPS09, PSSW09, NO09, LP11, IKO<sup>+</sup>11, Lin13]. These general-purpose protocols are restricted to functions represented by Boolean/arithmetic circuits. Namely, the function is first translated into a (typically Boolean) circuit and then the protocol securely evaluates it gate-by-gate on the parties' private inputs. This approach, however, falls short when the computation involves access to a large memory since in the circuits-based approach, dynamic memory accesses, which depend on the secret inputs, are translated into a linear scan of the memory. This translation is required for every memory access and causes a huge blowup in the description of the circuit.

The RAM model of computation. We further note that the majority of applications encountered in practice today are more efficiently captured using random-access memory (RAM) programs that allow constant-time memory lookup. This covers graph algorithms, such as the known Dijkstra's shortest path algorithm, binary search on sorted data, finding the kth-ranked element, the Gale-Shapely stable matching algorithm and many more. This is in contrast to the sequential memory access that is supported by the architecture of Turing machines. Generic transformations from RAM programs that run in time T generate circuits of size ( $T^3 \log T$ ) which are non-scalable even for cases where the memory size is relatively small [CR72, PF79].

To address these limitations, researchers have recently started to design secure protocols directly in the RAM model [DMN11, GKK<sup>+</sup>12, AHMR15]. The main underlying idea is to rely on Oblivious RAM (ORAM) [Gol87, Ost90, GO96], a fundamental tool that supports dynamic memory access with polylogarithmic cost while preventing any leakage from the memory. To be concrete, ORAM is a technique for hiding all the information about the memory of a RAM program. This includes both the content of the memory as well as the access pattern to it.

In more details, a RAM program P is defined by a function that is executed in the presence of memory D via a sequence of read and write operations, where the memory is viewed as an array of n entries (or blocks) that are initially set to zero. More formally, a RAM program is defined by a "next instruction" function that is executed on an input x, a current state state and data element  $b^{\text{read}}$  (that will always be equal to the last read element from memory D) and outputs the next instruction and an updated state. We use the notation  $P^D(x)$  to denote the execution of such a program. To avoid trivial solutions, such as fetching the entire memory, it is required that the space used by the evaluator grows linearly with  $\log n$ , |x| and the block length. The space complexity of a RAM program on inputs x, D is the maximum number of entries used

by P during the course of the execution. The time complexity of a RAM program on the same inputs is the number of instructions issued in the execution as described above.

Secure computation for RAM programs. An important application of ORAM is in gaining more efficient protocols for secure computation [GKK+12, GGH+13, LO13, GHJR14] [GHL+14, KS14, LHS+14, WHC+14, WCS15, AHMR15, GLOS15, HMR15, GLO15]. This approach is used to securely evaluate RAM programs where the overall input sizes of the parties are large (for instance, when one of the inputs is a database). Amongst these works, only [AHMR15] addresses general secure computation for arbitrary RAM programs with security in the presence of malicious adversaries. The advantage of using secure protocols directly for RAM programs is that such protocols imply (amortized) complexity that can be sublinear in the total size of the input. In particular, the overhead of these protocols grows linearly with the time-complexity of the underlying computation on the RAM program (which may be sublinear in the input size). This is in contrast to the overhead induced by evaluating the corresponding Boolean/arithmetic circuit of the underlying computation (for which its size is linear in the input size).

One significant challenge in handling dynamic memory accesses is to hide the actual memory locations being read/written from all parties. The general approach in most of these protocols is of designing protocols that work via a sequence of ORAM instructions using traditional circuit-based secure computation phases. More precisely, these protocols are defined using two phases: (1) initialize and setup the ORAM, a one-time computation with cost depending on the memory size, (2) evaluate the next-instruction circuit which outputs shares of the RAM program's internal state, the next memory operations (read/write), the location to access, and the data value in case of a write. This approach leads to protocols with semi-honest security whom their round complexity depends on the ORAM running time. In [GKK+12] Gordon et al. designed the first rigorous semi-honest secure protocols based on this approach, that achieves sublinear amortized overhead that is asymptotically close to the running time of the underlying RAM program in an insecure environment.

As observed later by Afshar et al. [AHMR15], adapting this approach in the malicious setting is quite challenging. Specifically, the protocol must ensure that the parties use state and memory shares that are consistent with prior iterations, while ensuring that the running time only depends on the ORAM running time rather than on the entire memory. They therefore consider a different approach of garbling the memory first and then propagate the output labels of these garbling within the CPU-step circuits.

The main question left open by their work is the *feasibility of constant round malicious secure computation in the RAM model*. In this work we address this question in the two-party setting.

#### 1.1 Our Results

We design the first constant round maliciously secure protocol for arbitrary RAM programs. Our starting point is the garbled RAM construction of Gentry et al. [GHL<sup>+</sup>14], which is the analogue object of garbled circuits [Yao82, BHR12] with respect to RAM programs. Namely, a user can garble an arbitrary RAM program directly without converting it into a circuit first. A garbled RAM scheme can be used to garble the data, the program and the input in a way that reveals only the evaluation outcome and nothing else. In their work, Gentry et al. proposed two ways to fix a subtle point emerged in an earlier construction by Lu and Ostrovsky [LO13] that requires a complex "circular" use of Yao garbled circuits and PRFs. For simplicity, we chose to focus on their garbled RAM based on identity based encryption (IBE) schemes. We show how to transform their IBE based protocol into a maliciously secure 2PC protocol at the cost of involving the cut-and-choose technique. Following that, we show how to achieve the same result using the more involved

garbled RAM construction of Garg et al. [GLOS15] assuming only the existence of one-way-functions. We state our main theorem below,

**Theorem 1.1** (Informal). Under the standard assumptions for achieving static malicious 2PC security, there exists a constant round protocol securely realizes any RAM program in the presence of malicious adversaries, making only black-box use of an Oblivious RAM construction, where the size of the garbled database is  $|D| \cdot \operatorname{poly}(\kappa)^1$ , the size of the garbled input is  $|x| \cdot O(\kappa) + T \cdot \operatorname{poly}(\kappa)$  and the size of the garbled program and its evaluation time is  $|C_{\text{CPU}}^P| \times T \times \operatorname{poly}(\kappa) \times \operatorname{polylog}(|D|) \times s$ .

Where  $C_{CPU}^P$  is a circuit that computes a CPU-step that involves reading/writing to the memory, T is the running time of program P on input x,  $\kappa$  is the security parameter and s is a statistical cut-and-choose parameter.

# Challenges faced in the malicious setting and RAM programs.

- 1. MEMORY MANAGEMENT. Intuitively speaking, garbled RAM readily induces a two-party protocol with semi-honest security by exchanging the garbled input using oblivious transfer (OT). The natural approach for enhancing the security of a garbled RAM scheme into a maliciously 2PC protocol is by using the cut-and-choose approach [LP07] where the basic underlying semi-honest protocol is repeated *s* times (for some statistical parameter *s*), such that a subset of these instances are "opened" in order to demonstrate correct behaviour whereas the rest of "unopened" instances are used to obtaining the final outcome (typically by taking the majority of results). The main challenge in boosting the security of a semi-honest secure protocol into the malicious setting, using this technique in the RAM model, is with handling multiple instances of memory data. That is, since each semi-honest protocol instance is executed independently, the RAM program implemented within this instance is associated with its own instance of memory. Recalling that the size of the memory might be huge compared to the other components in the RAM system, it is undesirable to store multiple copies of the data in the local memory of the parties. Therefore, the first challenge we had to handle is how to work with multiple copies of the same protocol while having access to a single memory data.

- 2. Handling check/evaluation circuits. The second challenge concerns the cut-and-choose proof technique as well. The original approach to garble the memory is by using encryptions computed based on PRF keys that are embedded inside the garbled circuits. These keys are used to generate a translation mapping which allows the receiver to translate between the secret keys and the labels of the read bit in the next circuit. When employing the cut-and-choose technique, all the secret information embedded within the circuits is exposed during the check process of that procedure which might violate the privacy of the sender. The same difficulty arises when hardwiring the randomness used for the encryption algorithm. A naive solution would be to let the sender choose *s* sets of keys, such that each set is used within the appropriate copy of the circuit. While this solution works, it prevents the evaluator from determining the majority of the (intermediate) results of all copies.

- 3. INTEGRITY AND CONSISTENCY OF MEMORY OPERATIONS. During the evaluation of program *P*, the receiver reads and writes back to the memory. In the malicious setting these operations must be backed up with a mechanism that enforces correctness. Moreover, a corrupted evaluator should not be able to roll back the stored memory to an earlier version. This task is very challenging in a scenario

<sup>&</sup>lt;sup>1</sup>The size mentioned is correct when relying on the IBE assumption, while relying on the OWF assumption would incur database size of  $|D| \cdot \log |D| \cdot \operatorname{poly}(\kappa)$ .

where the evaluator locally stores the memory and fully controls its accesses without the sender being able to verify whether the receiver has indeed carried out the required instructions (as that would imply that the round complexity grows linearly with the running time of the RAM program).

Constant round 2PC in the RAM model. Towards achieving malicious security, we demonstrate how to adapt the garbled RAM construction from [GHL<sup>+</sup>14] into the two-party setting while achieving malicious security. Our protocol is combined of two main components. First, an initialization circuit is evaluated in order to create all the IBE keys (or the PRF keys) that are incorporated in the latter RAM computation, based on the joint randomness of the parties (this phase is not computed locally since we cannot rely on the sender properly creating these keys). Next, the program *P* is computed via a sequence of small CPU-steps that are implemented using a circuit that takes as input the current CPU state and a bit that was read from the last read memory location, and outputs an updated state, the next location to read, a location to write to and a bit to write into that location. In order to cope with the challenges regarding the cut-and-choose approach, we must ensure that none of the secret keys nor randomness are incorporated into the circuits, but instead given as inputs. Moreover, to avoid memory duplication, all the circuits are given the same sequence of random strings. This ensures that the same set of secret keys/ciphertexts are created within all CPU circuits.

We note that our protocol is applicable to any garbled scheme that supports wire labels and can be optimized using all prior optimizations. Moreover, in a variant of our construction the initialization phase can be treated as a preprocessing phase that does not depend on the input. We further note that our abstraction of garbled circuits takes into account authenticity [BHR12]. Meaning that, a malicious evaluator should not be able to conclude the encoding of a string that is different than the actual output. This requirement is crucial for the security of garbled circuits with reusable labels (namely, where the output labels are used as input labels in another circuit), and must be addressed even in the semi-honest setting (and specifically for garbled RAM protocols). This is because authenticity is not handled by the standard privacy requirement. Yet, all prior garbled RAM constructions do not consider it. We stress that we do not claim that prior proofs are incorrect, rather that the underlying garbled circuits must adhere this security requirement in addition to privacy.

As final remark, we note that our construction employs the underlying ORAM in a black-box manner as the parties invoke it locally. This is in contrast to alternative approaches that compute the ORAM using a two (or multi)-party secure protocol such as in [GKK<sup>+</sup>12].

**Complexity.** The overhead of our protocol is dominated by the complexity induced by the garbled RAM construction of [GHL<sup>+</sup>14] times s, where s is the cut-and-choose statistical parameter. The [GHL<sup>+</sup>14] construction guarantees that the size/evaluation time of the garbled program is  $|C_{CPU}^P| \times T \times poly(\kappa) \times polylog(n)$ . Therefore the multiplicative overhead of our protocol is  $poly(\kappa) \times polylog(n) \times s$ .

**Reusable/persistent data.** Reusable/persistent data means that the garbled memory data can be reused across multiple program executions. That is, all memory updates are persist for future program executions and cannot be rolled back by the malicious evaluator. This feature is very important as it allows to execute a sequence of programs without requiring to initialize the data for every execution, implying that the running time is only proportional to the program running time (in a non-secured environment). The [GHL<sup>+</sup>14] garbled RAM allows to garble any sequence of programs (nevertheless, this set must be given to the garbler in advance and cannot be adaptively chosen). We show that our scheme preserves this property in the presence of malicious attacks as well.

**Concurrent work.** In a concurrent and independent work by Garg, Gupta, Miao and Pandey [GGMP16], the authors demonstrate constant-round multi-party computation with the advantage of achieving a construction that is *black-box* in the one-way function. Their work is based on the black-box GRAM construction of [GLO15] and the actively secure constant-round MPC construction of [BMR90]. The core technique of pulling secrets out of the programs and into the inputs is common to both our and their work. In another paper [Mia], Miao demonstrates how to achieve persistent data in the two-party setting, assuming a random oracle and using techniques from [NO09] and [BHR12].

# 2 Preliminaries

**Basic Notations.** We denote the security parameter by  $\kappa$ . We say that a function  $\mu: \mathbb{N} \to \mathbb{N}$  is negligible if for every positive polynomial  $p(\cdot)$  and all sufficiently large  $\kappa$  it holds that  $\mu(\kappa) < \frac{1}{p(\kappa)}$ . We use the abbreviation PPT to denote probabilistic polynomial-time. We further denote by  $a \leftarrow A$  the random sampling of a from a distribution A, by [d] the set of elements  $(1, \ldots, d)$  and by [0, d] the set of elements  $(0, \ldots, d)$ .

We now specify the definition of  $(\kappa, s)$ -computational indistinguishability (denoted  $\stackrel{\kappa, s}{\approx}$ ), while the usual (computational indistinguishability) definition (denoted  $\stackrel{c}{\approx}$ ) can be inferred.

**Definition 2.1.** Let  $X = \{X(a,\kappa,s)\}_{a\in\{0,1\}^*,\kappa,s\in\mathbb{N}}$  and  $Y = \{Y(a,\kappa,s)\}_{a\in\{0,1\}^*,\kappa,s\in\mathbb{N}}$  be two distribution ensembles. We say that X and Y are  $(\kappa,s)$ -computationally indistinguishable, denoted  $X \overset{\kappa,s}{\approx} Y$ , if there exist a constant  $0 < c \le 1$  such that for every PPT machine D, every  $s \in \mathbb{N}$  every positive polynomial  $p(\cdot)$  and all sufficiently large  $\kappa$  it holds that for every  $a \in \{0,1\}^*$ :

$$\left| \Pr \left[ D(X(a,\kappa), 1^{\kappa}) = 1 \right] - \Pr \left[ D(Y(a,\kappa), 1^{\kappa}) = 1 \right] \right| < \frac{1}{p(\kappa)} + \frac{1}{2^{c \cdot s}}.$$

#### 2.1 The RAM Model of Computation

We follow the notation from [GHL<sup>+</sup>14] verbatim. We consider a program P that has random-access to a memory of size n, which is initially empty. In addition, the program gets a "short" input x, which we can alternatively think of as the initial state of the program. We use the notation  $P^D(x)$  to denote the execution of such program. The program can read/write to various locations in memory throughout the execution. [GHL<sup>+</sup>14] also considered the case where several different programs are executed sequentially and the memory persists between executions. Our protocol follows this extension as well. Specifically, this process is denoted as  $(y_1, \ldots, y_c) = (P_1(x_1), \ldots, P_\ell(x_c))^D$  to indicate that first  $P_1^D(x_1)$  is executed, resulting in some memory contents  $D_1$  and output  $y_1$ , then  $P_2^{D_1}(x_2)$  is executed resulting in some memory contents  $D_2$  and output  $y_2$  etc.

**CPU-step circuit.** We view a RAM program as a sequence of at most T small CPU-steps, such that step  $1 \le t \le T$  is represented by a circuit that computes the following functionality:

$$\mathbf{C}^P_{\text{CPU}}(\mathsf{state}_t, b_t^{\mathsf{read}}) = (\mathsf{state}_{t+1}, i_t^{\mathsf{read}}, i_t^{\mathsf{write}}, b_t^{\mathsf{write}}).$$

Namely, this circuit takes as input the CPU state  $\mathsf{state}_t$  and a bit  $b_t^\mathsf{read}$  that was read from the last read memory location, and outputs an updated state  $\mathsf{state}_{t+1}$ , the next location to read  $i_t^\mathsf{read} \in [n]$ , a location to write to  $i_t^\mathsf{write} \in [n] \cap \bot$  (where  $\bot$  means "write nothing") and a bit  $b_t^\mathsf{write}$  to write into that location. The computation  $P^D(x)$  starts in the initial state  $\mathsf{state}_1 = (x_1, x_2)$ , corresponding to the parties "short input"

and by convention we will set the initial read bit to  $b_1^{\text{read}} := 0$ . In each step t, the computation proceeds by running  $\mathbf{C}_{\text{CPU}}^P(\mathsf{state}_t, b_t^{\text{read}}) = (\mathsf{state}_{t+1}, i_t^{\text{read}}, i_t^{\text{write}}, b_t^{\text{write}})$ . We first read the requested location  $i_t^{\text{read}}$  by stetting  $b_{t+1}^{\text{read}} := D[i_t^{\text{read}}]$  and, if  $i_t^{\text{write}} \neq \bot$  we write to the location by setting  $D[i_t^{\text{write}}] := b_t^{\text{write}}$ . The value  $y = \mathsf{state}_{T+1}$  output by the last CPU-step serves as the output of the computation.

A program P has a *read-only* memory access, if it never overwrites any values in memory. In particular, using the above notation, the outputs of  $C_{CPU}^P$  always set  $i_t^{\text{write}} = \bot$ .

#### 2.1.1 Predictably Time Writes

Predictably Time Writes (ptWrites) means that whenever we want to read some location i in memory, it is easy to figure out the time (i.e., CPU step) t' in which that location was last written to, given only the current state of the computation and without reading any other values in memory. In [GHL<sup>+</sup>14] the authors describe how to upgrade a solution for ptWrites to one that allows arbitrary writes. More formally,

**Definition 2.2** (Predictably timed writes [GHL<sup>+</sup>14]). A program execution  $P^D(x_1, x_2)$  has predictably timed writes if there, denoted WriteTime, such that the following holds for every CPU step  $t=1,\ldots,T$ . Let the inputs/outputs of the t-th CPU step be cpu-step(state<sub>t</sub>,  $b_t^{\text{read}}$ ) = (state<sub>t+1</sub>,  $i_t^{\text{read}}$ ,  $i_t^{\text{write}}$ ,  $b_t^{\text{write}}$ ), then t' = WriteTime(t, state<sub>t</sub>,  $i_t^{\text{read}}$ ) is the largest value of t' < t such that the CPU step t' wrote to memory location  $i_t^{\text{read}}$ ; i.e.  $i_t^{\text{write}} = i_t^{\text{read}}$ .

As in [GHL<sup>+</sup>14], we also describe a solution for RAM programs that support ptWrites and then show how to extend it to the general case.

# 2.2 Oblivious RAM (ORAM)

ORAM, initially proposed by Goldreich and Ostrovsky [Gol87, Ost90, GO96], is an approach for making a read/write memory access pattern of a RAM program input-oblivious. More precisely, it allows a client to store private data on an untrusted server and maintain obliviousness while accessing that data, by only storing a short local state. A secure ORAM scheme not only hides the content of the memory from the server, but also the access pattern of which locations in the memory the client is reading or writing in each protocol execution.<sup>2</sup> The work of the client and server in each such access should be small and bounded by a poly-logarithmic factor in the memory size, where the goal is to access the data without downloading it from the server in its entirely. In stronger attack scenarios, the ORAM is also authenticated which means that the server cannot modify the content of the memory. In particular, the server cannot even "roll-back" to an older version of the data. The efficiency of ORAM constructions is evaluated by their bandwidth blowup, client storage and server storage. Bandwidth blowup is the number of data blocks that are needed to be sent between the parties per request. Client storage is the amount of trusted local memory required for the client to manage the ORAM and server storage is the amount of storage needed at the server to store all data blocks. Since the seminal sequence of works by Goldreich and Ostrovsky, ORAM has been extensively studied [SCSL11, GMOT12, KLO12, WS12, SvDS<sup>+</sup>13, RFK<sup>+</sup>15], optimizing different metrics and parameters.

Before giving the formal definition let us put down the settings and notations: A Random Access Machine (RAM) with memory size n consists of a CPU with a small number of registers (e.g.  $poly(\kappa)$ , where  $\kappa$  is the security parameter), that each can store a string of length  $\kappa$  (called a "word") and external memory of size n. A word is either  $\perp$  or a  $\kappa$  bit string. Given n and x, the CPU executes the program P by

<sup>&</sup>lt;sup>2</sup>This can always be done by encrypting the memory.

sequentially evaluating the CPU-step function  $C^P_{\text{CPU}}(n, \mathsf{state}_t, b_t^{\mathsf{read}}) = (\mathsf{state}_{t+1}, i_t^{\mathsf{read}}, i_t^{\mathsf{write}}, b_t^{\mathsf{write}})$  where  $t = 0, 1, 2, \dots, T-1$  such that T is the upper bound on the program run time and  $\mathsf{state}_0 = x$ . The sequence of memory cells and data written in the course of the execution of the program is defined by  $\mathsf{MemAccess}(P, n, x) = \{(i_t^{\mathsf{read}}, i_t^{\mathsf{write}}, b_t^{\mathsf{write}})\}_{t \in [T]}$  and the number of memory accesses that were performed during a program execution is denoted by T(P, n, x) (that is, the running time of the program P with memory of size p0 on input p2).

In this work we follow a slightly modified version of the standard definition (of [Gol87, Ost90, GO96]), in which the compiled program  $P^*$  is not hardcoded with any secret values, namely, neither secret keys for encryption/authentication algorithms nor the randomness that specifies future memory locations to be accessed by the program, rather, the compiled program obtains these secret values as input. More concretely,  $P^*$  is given two inputs: (1) a secret value k that is used to derive the keys for encrypting and authenticating the data, (2) a uniformly random string k which corresponds to the random indices that are accessed during the computation. The formal definition follows:

**Definition 2.3.** A polynomial time algorithm C is an Oblivious RAM (ORAM) compiler with computational overhead  $c(\cdot)$  and memory overhead  $m(\cdot)$ , if C, when given  $n \in \mathbb{N}$  and a deterministic RAM program P with memory size n, outputs a program  $P^*$  with memory size  $m(n) \cdot n$ , such that for any input  $x \in \{0,1\}^*$ , uniformly random key  $k \in \{0,1\}^{\kappa}$  and uniformly random string  $r \in \{0,1\}^{\kappa}$ , it follows that  $T(P^*(n,x,k,r)) = c(n) \cdot T(P,n,x)$  and there exists a negligible function  $\mu$  such that the following properties hold:

- Correctness. For any  $n \in \mathbb{N}$ , any input  $x \in \{0,1\}^*$ , any key and uniformly random string  $k,r \in \{0,1\}^{\kappa}$ , with probability at least  $1 \mu(\kappa)$ ,  $P^*(n,x,k,r) = P(n,x)$ .

- Obliviousness. For any two programs  $P_1, P_2$ , any  $n \in \mathbb{N}$ , any two inputs, uniformly random keys and uniformly random strings:  $x_1, x_2 \in \{0, 1\}^*, k_1, k_2, r_1, r_2 \in \{0, 1\}^\kappa$  respectively, if  $T(P_1(n, x_1)) = T(P_2(n, x_2))$  and  $P_1^* \leftarrow C(n, P_1, \rho_1)$ ,  $P_2^* \leftarrow C(n, P_2, \rho_2)$  then MemAccess $(P_1^*(n, x_1, k_1, r_1))$  and MemAccess $(P_2^*(n, x_2, k_2, r_2))$  are computationally indistinguishable, where the random tapes  $\rho_1, \rho_2$  that were used by the compiler to generate the compiled programs are given to the distinguisher.

Note that the above definition (just as the definition of [GO96]) only requires an oblivious compilation of deterministic programs P. This is without loss of generality: We can always view a randomized program as a deterministic one that receives random coins as part of its input.

#### 2.2.1 Realization of the Modified Definition

We present here a sketch of an ORAM compiler that meets the above requirements, which is a slightly modified construction of the Simple ORAM that was presented in [CP13]. The modified compiler is a deterministic algorithm C, that is, its random tape  $\rho$  is an empty string  $\varepsilon$ . When given a program P, the compiler outputs a program  $P^*$  that takes the inputs x, k, r where x is the input to the original program P, k is a uniformly random string from which the encryption/authentication keys are derived and r is a uniformly random strings of the following form:  $r = \{Pos, r_1, r_2, \ldots, r_T\}$  such that Pos is the initial position map of the oblivious program and  $r_1, \ldots, r_T$  are the additional random locations that are used for each iteration

<sup>&</sup>lt;sup>3</sup>The following definition is derived from the definition given in[CP13].

<sup>&</sup>lt;sup>4</sup>The use of  $\rho_1$ ,  $\rho_2$  does not reveal any information about the access pattern nor about the encryption key of the data, these are determined only by the keys  $k_1$ ,  $k_2$  and the random strings  $r_1$ ,  $r_2$ .

during the execution of the program  $P^*$ . The program  $P^*$  that C outputs is specified exactly as the the oblivious program presented in [CP13], except that the position map Pos and random paths  $r_1, \ldots, r_T$  are not hardcoded within the program, rather, they are given as inputs to the program.

## 2.3 Secure Computation in the RAM Model

We adapt the standard definition for secure two-party computation of [Gol04, Chapter 7] for the RAM model of computation. In this model of computation, the initial input is split between two parties and the parties run a protocol that securely realizes a program P on a pair of "short" inputs  $x_1, x_2$ , which are viewed as the initial state of the program. In addition, the program P has random-access to a memory of size n which is initially empty. Using the notations from Section 2.1, we refer to this (potentially random) process by  $P^D(x_1, x_2)$ . In this work we prove the security of our protocols in the presence of malicious computationally bounded adversaries.

We next formalize the ideal and real executions, considering D as a common resource.<sup>5</sup> Our formalization induces two flavours of security definitions. In the first (and stronger) definition, the memory accesses to D are hidden, that is, the ideal adversary that corrupts the receiver only obtains (from the trusted party) the running time T of the program P and the output of computation y. Given only these inputs, the simulator must be able to produce an indistinguishable memory access pattern. In the weaker, unprotected memory access model described below, the simulator is further given the content of the memory, as well as the memory access pattern produced by the trusted party throughout the computation of  $P^D$ . We present here both definitions, starting with the definition of full security.

# 2.3.1 Full Security

Execution in the ideal model. In an ideal execution, the parties submit their inputs to a trusted party that computes the output; see Figure 1 for the description of the functionality computed by the trusted party in the ideal execution. Let P be a two-party program, let  $\mathcal{A}$  be a non-uniform PPT machine and let  $i \in \{S, R\}$  be the corrupted party. Then, denote the *ideal execution of* P on inputs  $(x_1, x_2)$ , auxiliary input z to  $\mathcal{A}$  and security parameters s,  $\kappa$ , by the random variable  $\mathbf{IDEAL}_{\mathcal{A}(z),i}^{\mathcal{F}_{RAM}}(s,\kappa,x_1,x_2)$ , as the output pair of the honest party and the adversary  $\mathcal{A}$  in the above ideal execution.

#### Functionality $\mathcal{F}_{\scriptscriptstyle \mathrm{RAM}}$

The functionality  $\mathcal{F}_{RAM}$  interacts with a sender S and a receiver R. The program P is known and agreed by both parties.

**Input:** Upon receiving input value (INPUT<sub>S</sub>,  $x_1$ ) from S and input value (INPUT<sub>R</sub>,  $x_2$ ) from R store  $x_1, x_2$  and initialize the memory data D with  $0^n$ .

**Output:** If both inputs are recorded execute  $y \leftarrow P^D(x_1, x_2)$  and send (OUTPUT<sub>R</sub>, T, y) to R.

Figure 1: A 2PC secure evaluation functionality in the RAM model for program P.

<sup>&</sup>lt;sup>5</sup>Nevertheless, we note that the memory data D will be kept in the receiver's local memory.

Execution in the real model. In the real model there is no trusted third party and the parties interact directly. The adversary  $\mathcal{A}$  sends all messages in place of the corrupted party, and may follow an arbitrary PPT strategy. The honest party follows the instructions of the specified protocol  $\pi$ . Let  $P^D$  be as above and let  $\pi$  be a two-party protocol for computing  $P^D$ . Furthermore, let  $\mathcal{A}$  be a non-uniform PPT machine and let  $i \in \{S,R\}$  be the corrupted party. Then, the *real execution of*  $\pi$  on inputs  $(x_1,x_2)$ , auxiliary input z to  $\mathcal{A}$  and security parameters  $s, \kappa$ , denoted by the random variable  $\text{REAL}_{\mathcal{A}(z),i}^{\pi}(s,\kappa,x_1,x_2)$ , is defined as the output pair of the honest party and the adversary  $\mathcal{A}$  from the real execution of  $\pi$ .

**Security as emulation of a real execution in the ideal model.** Having defined the ideal and real models, we can now define security of protocols. Loosely speaking, the definition asserts that a secure party protocol (in the real model) emulates the ideal model (in which a trusted party exists). This is formulated by saying that adversaries in the ideal model are able to simulate executions of the real-model protocol.

**Definition 2.4** (Secure computation). Let  $\mathcal{F}_{RAM}$  and  $\pi$  be as above. Protocol  $\pi$  is said to securely compute  $P^D$  with abort in the presence of malicious adversary if for every non-uniform PPT adversary  $\mathcal{A}$  for the real model, there exists a non-uniform PPT adversary  $\mathcal{S}$  for the ideal model, such that for every  $i \in \{S, R\}$ ,

$$\left\{\mathbf{IDEAL}_{\mathcal{S}(z),i}^{\mathcal{F}_{\mathrm{RAM}}}(s,\kappa,x_1,x_2)\right\}_{s,\kappa\in\mathbb{N},x_1,x_2,z\in\{0,1\}^*} \overset{\mathrm{c}}{\approx} \left\{\mathbf{REAL}_{\mathcal{A}(z),i}^{\pi}(s,\kappa,x_1,x_2)\right\}_{s,\kappa\in\mathbb{N},x_1,x_2,z\in\{0,1\}^*}$$

where s and  $\kappa$  are the security parameters.

We next turn to a weaker definition of secure computation in the unprotected memory access model, and then discuss a general transformation from a protocol that is secure in the UMA model to a protocol that is fully secure.

#### 2.3.2 The UMA Model

In [GHL<sup>+</sup>14], Gentry et al. considered a weaker notion of security, denoted by *Unprotected Memory Access* (UMA), in which the receiver may additionally learn the content of the memory D, as well as the memory access pattern throughout the computation including the locations being read/written and their contents.<sup>6</sup> In the context of two-party computation, when considering the ideal execution, the trusted party further forwards the adversary the values  $\text{MemAccess} = \{(i_t^{\text{read}}, i_t^{\text{write}}, b_t^{\text{write}})\}_{t \in [T]}$  where  $i_t^{\text{read}}$  is the address to read from,  $i_t^{\text{write}}$  is the address to write to and  $b_t^{\text{write}}$  is the bit value to be written to location  $i_t^{\text{write}}$  in time step t. We denote this functionality, described in Figure 2, by  $\mathcal{F}_{\text{UMA}}$ . We define security in the UMA model and then discuss our general transformation from UMA to full security.

**Definition 2.5** (Secure computation in the UMA model). Let  $\mathcal{F}_{\text{UMA}}$  be as above. Protocol  $\pi$  is said to securely compute  $P^D$  with UMA and abort in the presence of malicious adversaries if for every non-uniform PPT adversary  $\mathcal{A}$  for the real model, there exists a non-uniform PPT adversary  $\mathcal{S}$  for the ideal model, such that for every  $i \in \{S, R\}$ , for every  $s \in \mathbb{N}$ ,  $x_1, x_2, z \in \{0, 1\}^*$  and for large enough  $\kappa$

$$\left\{\mathbf{IDEAL}_{\mathcal{S}(z),i}^{\mathcal{F}_{\mathrm{UMA}}}(s,\kappa,x_1,x_2)\right\}_{s,\kappa,x_1,x_2,z} \overset{\kappa,s}{\approx} \left\{\mathbf{REAL}_{\mathcal{A}(z),i}^{\pi}(s,\kappa,x_1,x_2)\right\}_{s,\kappa,x_1,x_2,z}$$

where s and  $\kappa$  are the security parameters.

<sup>&</sup>lt;sup>6</sup>Gentry et al. further demonstrated that this weaker notion of security is useful by providing a transformation from this setting into the stronger setting for which the simulator does not receive this extra information. Their proof holds against semi-honest adversaries. A simple observation shows that their proof can be extended for the malicious 2PC setting by considering secure protocols that run the oblivious RAM and the garbling computations; see below our transformation.

#### Functionality $\mathcal{F}_{\scriptscriptstyle \mathrm{UMA}}$

The functionality  $\mathcal{F}_{\text{UMA}}$  interacts with a sender S and a receiver R. The program P is known and agreed by both parties.

**Input:** Upon receiving input value (INPUT<sub>S</sub>,  $x_1$ ) from S and input value (INPUT<sub>R</sub>,  $x_2$ ) from R, store  $x_1, x_2$  and initialize the memory data D with  $0^n$ .

**Output:** If both inputs are recorded, execute  $y \leftarrow P^D(x_1, x_2)$  and send (OUTPUT<sub>R</sub>, T, y, MemAccess) to R, where T is the number of memory accesses that were performed during the execution, and MemAccess is the access pattern of the execution.

Figure 2: A 2PC secure evaluation functionality in the UMA model for program P.

# 2.3.3 A Transforation From UMA to Full Security

Below, we present a transformation  $\Theta$ , that is given (1) a protocol  $\pi$  with UMA security for RAM programs that support ptWrites and (2) a secure ORAM compiler C that satisfies ptWrites,<sup>7</sup> and outputs a two-party protocol for arbitrary RAM programs with full security; see Figure 3 for the description of  $\Theta$ . The formal theorem follows:

**Theorem 2.6.** Let  $\pi$  be a secure two-party protocol that provides UMA security for RAM programs that support ptWrites in the presence of malicious adversaries and C an ORAM compiler that satisfies ptWrites, then  $\Theta$  is a two-party protocol that provides full security for arbitrary RAM programs in the presence of malicious adversaries.

Note that the transformation uses the ORAM compiler C and the UMA-secure protocol  $\pi$  in a blackbox manner. In addition, the transformation preserves all the properties that are related to the memory management, i.e., the party who handles the memory in  $\pi$  is the same one who handles the memory in  $\pi' \leftarrow \Theta(P,\pi)$ . Note that the efficiency of the resulted protocol  $\pi' \leftarrow \Theta(P,\pi)$  is dominated by the efficiency of the UMA-secure protocol  $\pi$  and the ORAM compiler C. Specifically, the recent ORAM constructions set an additional polylog overhead with respect to all relevant parameters.

**Security.** We next present a proof sketch to the transformation presented in Figure 3. We consider first a corrupted receiver, which is the more complicated case, and then a corrupted sender.

R is corrupted. Let  $S_{\text{UMA}}$  be the simulator for protocol  $\pi$  in the UMA model. The simulator for the general model,  $S_{\text{RAM}}$ , works as follows:

1. Let T be the run time of the program P, and let  $\tilde{P}$  be the program of the form:

```

For i=0 To T:

Read(k);

```

for some constant  $k \in [n]$  (i.e. k is in the range of D's size). Let  $\tilde{P}^* \leftarrow C(n, \tilde{P})$  and its memory access pattern MemAccess $(\tilde{P}^*, n, \varepsilon)$  resulted by its execution (where  $\varepsilon$  is an empty string, since  $\tilde{P}$  gets no input).

<sup>&</sup>lt;sup>7</sup>As for RAM programs, ORAM schemes can also support this property. Moreover, the [GHL<sup>+</sup>14] transformation discussed in Section 2.1.1 can be applied to ORAM schemes as well.

#### Transformation $\Theta$ from UMA to Fully Secure Protocol

**Inputs:** The program P that the parties wish to compute. The protocol  $\pi$  to compute a two-party protocol with a UMA security. A secure ORAM compiler C. The sender S has  $x_1$  and the receiver R has  $x_2$ .

#### **Protocol:**

- 1. The parties generate the randomness  $\rho$  using a coin-tossing protocol.

- 2. The parties agree on the oblivious program  $P^* \leftarrow C(P, n, \rho)$  where  $\rho$  is C's random tape.

- 3. The parties run  $\pi(P^*)$  where R's inputs are  $x_1, k_1, r_1$ , S's inputs are  $x_2, k_2, r_2$  and the program  $P^*$  is given n (the memory size), the parties' input  $x = x_1 \| x_2$ , the key and the random tape of the compiled program, i.e.  $k_1 \oplus k_2$  and  $r_1 \oplus r_2$ , respectively. That is, the parties run  $\pi(P^*(n, x_1 \| x_2, k_1 \oplus k_2, r_1 \oplus r_2))$ .

Figure 3: A transformation from UMA to full security.

2. Given the output of the program y = P(x, y), the simulator  $\mathcal{S}_{RAM}$  outputs the view that is the result of  $\mathcal{S}_{UMA}(y, \mathsf{MemAccess}(\tilde{P}^*, n, \varepsilon))$ .

We claim that the view that  $\mathcal{S}_{\text{RAM}}$  outputs is indistinguishable from the real view of the receiver in the real execution of the protocol. Assume, by contradiction, that there exist inputs  $x_1, x_2$  for which there exists a distinguisher  $\mathcal{D}$  who can distinguish between the two views with more than negligible probability. Consider the following hybrid view  $\mathbf{Hyb}$  which is constructed as follows: Given  $P, x_1, x_2, n$ , compute  $P^* \leftarrow C(n, P)$ , choose random strings k and r and run  $P^*(n, x_1 || x_2, k, r)$ . Let  $\mathsf{MemAccess}(P^*, n, (x_1 || x_2, k, r))$  be the access pattern induced by this execution, then, outputs  $\mathsf{Hyb} = \mathcal{S}_{\text{UMA}}(y, \mathsf{MemAccess}(P^*, n, (x_1 || x_2, k, r)))$ . The indistinguishability between  $\mathcal{S}_{\text{RAM}}(y)$  and  $\mathsf{Hyb}(P, x_1, x_2, n)$  is reduced to the obliviousness of the ORAM compiler and the indistinguishability between  $\mathsf{Hyb}(P, x_1, x_2, n)$  and the real view is reduced to the indistinguishability of the simulation of  $\mathcal{S}_{\text{UMA}}$  and the real view of the execution of protocol  $\pi$ .

S is corrupted. This case is simpler since, by the definitions of functionalities  $\mathcal{F}_{\text{UMA}}$  and  $\mathcal{F}_{\text{RAM}}$  the sender receives no output from the computation, thus, the same simulator used in the UMA model works in the general RAM model, that is  $\mathcal{S}_{\text{RAM}} = \mathcal{S}_{\text{UMA}}$ . Specifically, indistinguishability between the output of  $\mathcal{S}_{\text{RAM}}$  and the sender's view in the real execution in the RAM model is immediately reduced to the indistinguishability between the output of  $\mathcal{S}_{\text{RAM}}$  and the view in the real execution in the UMA model.

Note that our ORAM compiler definition simplifies the transformation to full security as now the result oblivious program  $P^*$  gets its randomness r as part of its input, rather than being hardcoded with it. Furthermore, recalling that this randomness is used to determine the future locations in memory for which the oblivious program is going to access, we note that r is not revealed as part of the "check circuits" when using the cut-and-choose technique.

# 2.3.4 On the Capabilities of Semi-Honest in a Garbled RAM and ORAM Schemes

When considering ORAM schemes in the context of two-party computation, it must be ensured that a read operation is carried out correctly. Namely, that the correct element from the memory is indeed fetched,

and that the adversary did not "roll back" to an earlier version of that memory cell. Importantly, this is not just a concern in the presence of malicious adversaries, as a semi-honest adversary may try to execute its (partial) view on inconsistent memory values. Therefore, the scheme must withhold such attacks. Handling the first attack scenario is relatively simply using message authentications codes (MACs), so that a MAC tag is stored in addition to the encrypted data. Handling roll backs is slightly more challenging and is typically done using Merkle trees. In [GHL<sup>+</sup>14] roll backs are prevented by creating a new secret key for each time period. This secret key is used to decrypt a corresponding ciphertext in order to extract the label for the next garbled circuit. By replacing the secret key each time period, the adversary is not able decrypt a ciphertext created in some time period with a secret key that was previously generated.

## 2.4 Timed IBE [GHL<sup>+</sup>14]

TIBE was introduced by Gentry et al. in [GHL<sup>+</sup>14] in order to handle memory data writings in their garbled RAM construction. This primitive allows to create "time-period keys" TSK<sub>t</sub> for arbitrary time periods  $t \geq 0$  such that TSK<sub>t</sub> can be used to create identity-secret-keys  $\mathsf{SK}_{(t,v)}$  for identities of the form (t,v) for arbitrary v but cannot break the security of any other identities with  $t' \neq t$ . Gentry et al. demonstrated how to realize this primitive based on IBE [BF03, BB11]. Informally speaking, the security of TIBE is as follows: Let  $t^*$  be the "current" time period. Given a single secret key  $\mathsf{SK}_{(t,v)}$  for every identity (t,v) of the "past" periods  $t < t^*$  and a single period key  $\mathsf{TSK}_t$  for every "future" periods  $t^* < t \leq T$ , semantic security should hold for any identity of the form  $\mathsf{id}^* = (t^*, v^*)$  (for which neither a period nor secret key were not given). The formal definition of Timed IBE which is used across our protocol is as follows:<sup>8</sup>

**Definition 2.7** (Timed IBE (TIBE)). A TIBE scheme Consists of 5 PPT algorithms MasterGen, TimeGen, KeyGen, Enc, Dec with the syntax:

- $(MPK, MSK) \leftarrow MasterGen(1^{\kappa})$ : generates master public/secret key pair MPK, MSK.

- $\mathsf{TSK}_t \leftarrow \mathsf{TimeGen}(\mathsf{MSK},t)$ : Generates a time-period key for time-period  $t \in \mathbb{N}$ .

- $\mathsf{sk}_{(t,v)} \leftarrow \mathsf{KeyGen}(\mathsf{TSK}_t,(t,v))$ : creates a secret key for the identity (t,v).

- ct  $\leftarrow$  Enc<sub>MPK</sub>((t, v), msg): creates an encryption of msg under the identity (t, v).

- $msg = Dec_{sk_{(t,v)}}(ct)$ : decrypts a ciphertexts ct for the identity (t,v) using a secret key  $sk_{(t,v)}$ .

The scheme should satisfy the following properties:

**Correctness:** For any id = (t, v), and any msg  $\in \{0, 1\}^*$  it holds that:

$$\Pr\bigg[\mathsf{Dec}_{\mathsf{sk}}(\mathsf{ct}) = \mathsf{msg}\bigg| \begin{array}{c} (\mathsf{MPK},\mathsf{MSK}) \leftarrow \mathsf{MasterGen}(1^\kappa), \mathsf{TSK}_t \leftarrow \mathsf{TimeGen}(\mathsf{MSK},t), \\ \mathsf{sk} \leftarrow \mathsf{KeyGen}(\mathsf{TSK}_t,(t,v)), \mathsf{ct} \leftarrow \mathsf{Enc}_{\mathsf{MPK}}((t,v),\mathsf{msg}) \end{array} \bigg] = 1.$$

**Security:** We consider the following game between an attacker A and a challenger.

• The attacker  $\mathcal{A}(1^\kappa)$  chooses some identity  $\mathrm{id}^* = (t^*, v^*)$  with  $t^* \in \mathbb{N}$  and some bound  $T \geq t^*$  (given in unary). The attacker also chooses a set of identities I such that I contains exactly one identity (t, v) for each period  $t \in 1, \ldots t^* - 1$ . Lastly, the adversary chooses  $\mathrm{messages} \; \mathrm{msg}_0, \mathrm{msg}_1 \in \{0, 1\}^*$  of equal size  $|\mathrm{msg}_0| = |\mathrm{msg}_1|$ .

$<sup>^{8}</sup>$ We omit from the following definition the multiple secret keys that the adversary receives for identities of the form (0, v) since in our scheme, data initialization is done as part of the computation if required.

• The challenger chooses (MPK, MSK)  $\leftarrow$  MasterGen( $1^{\kappa}$ ), and TSK $_t \leftarrow$  TimeGen(MSK, t) for  $t \in [T]$ . For each id  $= (t, v) \in I$  it chooses  $\mathsf{sk}_{\mathsf{id}} \leftarrow \mathsf{KeyGen}(\mathsf{TSK}_t, \mathsf{id})$ . Lastly, the challenger chooses a challenge bit  $b \leftarrow \{0, 1\}$  and sets ct  $\leftarrow \mathsf{Enc}_{\mathsf{MPK}}(\mathsf{id}^*, \mathsf{msg}_b)$ . The challenger gives the attacker:

$$\mathsf{MSK}, \ \overline{\mathsf{TSK}} = \{\mathsf{TSK}_t\}_{t^* < t < T}, \ \overline{\mathsf{sk}} = \{(\mathsf{id}, \mathsf{sk}_{\mathsf{id}})\}_{\mathsf{id} \in S}, \ \mathsf{ct}.$$

• The attacker outputs a bit  $\hat{b} \in \{0, 1\}$ .

The scheme is secure if, for all PPT  $\mathcal{A}$ , we have  $|Pr[b=\widehat{b}]-\frac{1}{2}|\leq \mu(\kappa)$  in the above game.

# 2.5 Garbled RAM Based on IBE [GHL<sup>+</sup>14]

Our starting point is the garbled RAM construction of [GHL<sup>+</sup>14]. Intuitively speaking, garbled RAM [LO13] is an analogue object of garbled circuits [Yao82, BHR12] with respect to RAM programs. The main difference when switching to RAM programs is the requirement of maintaining a memory data D. In this scenario, the data is garbled once, while many different programs are executed sequentially on this data. As pointed out in the modeling of [GHL<sup>+</sup>14], the programs can only be executed in the specified order, where each program obtains a state that depends on prior executions. The [GHL<sup>+</sup>14] garbled RAM proposes a fix to the aforementioned circularity issue raised in [LO13] by using an Identity Based Encryption (IBE) scheme [BF03, BB11] instead of a symmetric-key encryption scheme.

In more details, the inputs D, P, x to the garbled RAM are garbled into  $\tilde{D}, \tilde{P}, \tilde{x}$  such that the evaluator reveals the output  $\tilde{P}(\tilde{D}, \tilde{x}) = P(D, x)$  and nothing else. A RAM program P with running time T can be evaluated using T copies of a Boolean circuit  $C_{\text{CPU}}^P$  where  $C_{\text{CPU}}^t$  computes the function  $C_{\text{CPU}}^P$  (state,  $b_t^{\text{read}}) = (\text{state}_{t+1}, i_t^{\text{read}}, i_t^{\text{write}}, b_t^{\text{write}})$ . Then secure evaluation of P is possible by having the sender S garble the circuits  $\{C_{\text{CPU}}^t\}_{t\in[T]}$  (these are called the garbled program  $\tilde{P}$ ), whereas the receiver R sequentially evaluates these circuits. In order for the evaluation to be secure the state of the program should remain secret when moving from one circuit to another. To this end, the garbling is done in a way that assigns the output wires of one circuit with the same labels as the input wires of the next circuit. The main challenge here is to preserve the ability to read and write from the memory while preventing the evaluator from learning anything beyond the program's output, including any intermediate value.

The original idea from [LO13] employed a clever usage of a PRF for which the secret key is embedded inside all the CPU-steps circuits, where the PRF's role is twofold. For reading from the memory it is used to produce ciphertexts encrypting the labels of the input wire of the input bit of the next circuit, whereas for writing it is used to generate secret keys for particular "identities". As explained in [GHL $^+$ 14], the proof of [LO13] does not follow without assuming an extra circularity assumption. In order to avoid circularity, Gentry et al. proposed to replace the PRF with a public-key primitive. As it is insufficient to use a standard public-key cryptosystem (since the circuit must still produce secret keys for each memory location i, storing the keys  $\mathsf{sk}_{i,0}, \mathsf{sk}_{i,1}$ ), the alternative is to use IBE. Below, we briefly describe their scheme.

The read-only solution. The initialized garbled data  $\tilde{D}$  contains a secret key  $\mathsf{sk}_{i,b}$  in each memory location  $i \in [n]$  where D[i] = b, such that i, b serves as an identity secret key for the "identity" (i, b). Moreover, each garbled circuit  $\mathrm{GC}^t_{\mathrm{CPU}}$  is hardwired with the master public key MPK of an IBE scheme. This way, the garbled circuit can encrypt the input labels for the next circuit, that are associated with the bit that has just been read from the memory. More specifically, the circuit generates two ciphertexts  $\mathsf{ct}_0$ ,  $\mathsf{ct}_1$  that are viewed

<sup>&</sup>lt;sup>9</sup>For ease of presentation, Gentry et al. abstract the security properties of the IBE scheme using a new primitive denoted by Timed IBE (TIBE); see Section 2.4 for more details.

as a translation map. Namely,  $\mathsf{ct}_b = \mathsf{Enc}_{\mathsf{MPK}}(\mathsf{id} = (i, b); \mathsf{msg} = \mathsf{lbl}_b^{t+1})$  and the correct label is extracted by decrypting the right ciphertext using  $\mathsf{sk}_{i,b}$ , such that  $\mathsf{lbl}_0^{t+1}, \mathsf{lbl}_1^{t+1}$  are the input labels in the next garbled circuit that are associated with the last input bit read from the memory.

**The read-write solution.** A complete solution that allows both reading and writing is slightly more involved. We describe how to garble the data and the program next.

GARBLING THE DATA. The garbled data consists of secret keys  $\mathsf{sk}_{(t,i,b)}$  for identities of the form  $\mathsf{id} = (t,i,b)$  where i is the location in the memory D', t is the last time step for which that location was written to and  $b \in \{0,1\}$  is the bit that was written to location i at time step t. The honest evaluator only needs to keep the most recent secret key for each location i.

Garbling the program. Next, each CPU garbled circuit computes the last time step in which memory location i was written to by computing  $t' = \mathsf{WriteTime}(t,\mathsf{state}_t,i_t^\mathsf{read})$ . Namely, if at time step t the garbled circuit  $\mathsf{GC}^t_{\mathsf{CPU}}$  instructs to read from location  $i_t^\mathsf{read}$ , then the circuit further computes the last time step, u, in which that  $i_t^\mathsf{read}$  was written to, it then computes the translation map  $\mathsf{translate}_t = (\mathsf{ct}_0, \mathsf{ct}_1)$  by  $\mathsf{ct}_b = \mathsf{Enc}_{\mathsf{MPK}}(\mathsf{id} = (u, i_t^\mathsf{read}, b); \mathsf{msg} = \mathsf{lbl}_b^{t+1}))$ , and outputs it in the clear.

In order to write at time step t to memory location  $i=i_t^{\text{write}}$  the value  $b=b_t^{\text{write}}$ , a naive solution would hardwire MSK within each garbled circuit and then generate the key  $\mathsf{sk}_{(t,i,b)} = \mathsf{KeyGen}_{\mathsf{MSK}}(\mathsf{id} = (t,i,b));$  but this idea re-introduces the circularity problem. Instead, Gentry et al. [GHL+14] solve this problem by introducing a new primitive called Timed IBE (TIBE). Informally, this is a two-level IBE scheme in which the first level includes the master public/secret keys (MPK, MSK) whereas the second level has T timed secret keys  $\mathsf{TSK}_1, \ldots, \mathsf{TSK}_T$ . The keys  $\mathsf{MPK}$ ,  $\mathsf{MSK}$  are generated by  $\mathsf{MasterGen}(1^\kappa)$  and the timed keys are generated by  $\mathsf{TSK}_t = \mathsf{TimeGen}(\mathsf{MSK}, t)$ .

Then in the garbling phase, the key  $\mathsf{TSK}_t$  is hardwired within the tth garbled circuit  $\mathsf{GC}^t_{\mathsf{CPU}}$  and is used to write the bit  $b^{\mathsf{write}}_t$  to memory location  $i^{\mathsf{write}}_t$ . To do that  $\mathsf{GC}^t_{\mathsf{CPU}}$  computes the secret key for identity (t,i,b) by  $\mathsf{sk}_{(t,i,b)} \leftarrow \mathsf{KeyGen}(\mathsf{TSK}_t,(t,i,b))$  which is then stored in memory location i by the evaluator. Note that  $\mathsf{GC}^t_{\mathsf{CPU}}$  outputs a secret key for only one identity in every time step (for (t,i,b) but not (t,i,1-b)). This solution bypasses the circularity problem since the timed secret keys  $\mathsf{TSK}_t$  are hardwired only within the garbled circuit computing  $\mathsf{C}^t_{\mathsf{CPU}}$ , and cannot be determined from either  $\mathsf{sk}_{(t,i,b)}$  or the garbled circuit, provided that the TIBE scheme and the garbling schemes are secure.

#### 2.6 Garbled Circuits

The idea of garbled circuit is originated in [Yao82]. Here, a sender can encode a Boolean circuit that computes some PPT function f, in a way that (computationally) hides from the receiver any information but the function's output. In this work we consider a variant of the definition from [GHL<sup>+</sup>14] that abstracts out the security properties of garbled circuits that are needed via the notion of a garbled circuit with wire labels. The definition that we propose below stems from the cut-and-choose technique chosen to deal with a malicious sender. Specifically, the sender uses the algorithm Garb to generate s garbled versions of the circuit s, namely s for some statistical parameter s. Then, in order to evaluate these circuits the sender sends s for some statistical parameter s. Then, in order to evaluate these circuits the sender sends s for some statistical parameter s. Then, in order to evaluate these circuits the garbled circuit s for some statistical parameter s. Then, in order to evaluate these circuits the sender sends s for some statistical parameter s. Then, in order to evaluate these circuits the garbled circuit s for the garbled circuit s for some statistical parameter s. Then, in order to evaluate these circuits the sender sends s for some statistical parameter s. Then, in order to evaluate these circuits the sender sends s for some statistical parameter s. Then, in order to evaluate these circuits the sender sends s for some statistical parameter s. Then, in order to evaluate these circuits the sender sends s for some statistical parameter s. Then, in order to evaluate these circuits the sender sends s for some statistical parameter s. Then, in order to evaluate these circuits the sender sends s for some statistical parameter s. Then, in order to evaluate these circuits the sender sends s for some statistical parameter s. Then, in order to evaluate these circuits s for some statistical parameter s. Then, in order to evaluate s for some

the input to the circuit). The evaluator learns s sets $^{10}$  of output-wire labels  $\{\tilde{y}_i\}_{i\in[s]}$  corresponding to the output  $y=\mathrm{C}(x)^{11}$ , where  $\tilde{y}_i=(\mathsf{lbl}_{\mathrm{out},y[1]}^{1,i},\ldots,\mathsf{lbl}_{\mathrm{in},y[v_{\mathrm{out}}]}^{v_{\mathrm{out}},i})$ , but nothing else (for example, it does not learn  $\mathsf{lbl}_{\mathrm{out},1-y[1]}^{1,i}$ ). For clarity, in the following exposition the label  $\mathsf{lbl}_{\mathrm{in},b}^{j,i}$  is the label that represents the bit-value  $b\in\{0,1\}$  for the jth input wire  $(j\in v_{\mathrm{in}})$  in the ith garbled version of the circuit (for  $i\in s$ ), namely  $\tilde{\mathrm{C}}_i$ . Analogously,  $\mathsf{lbl}_{\mathrm{out},b}^{j,i}$  represents the same, except that it is associated with an output wire (where  $j\in v_{\mathrm{out}}$ ).

We further abstract two important properties of *authenticity* and *input consistency*. Loosely speaking, the authenticity property ensures that a malicious evaluator will not be able to produce a valid encoding of an incorrect output given the encoding of some input and the garbled circuit. This property is required due to the reusability nature of our construction. Namely, given the output labels of some iteration, the evaluator uses these as the input labels for the next circuit. Therefore, it is important to ensure that it cannot enter an encoding of a different input (obtained as the output from the prior iteration). In the abstraction used in our work, violating authenticity boils down to the ability to generate a set of output labels that correspond to an incorrect output. Next, a natural property that a maliciously secure garbling scheme has to provide is *input consistency*. We formalize this property via a functionality, denoted by  $\mathcal{F}_{\text{IC}}$ . That is, given a set of garbled circuits  $\{\tilde{C}_i\}_i$  and a set of garbled inputs  $\{\tilde{x}_i\}_{i=1}^s$  (where  $|\tilde{x}_i|=j$ ) represent the same input value, and 0 otherwise. This functionality is described in Figure 7. We now proceed to the formal definition.

**Definition 2.8** (Garbled circuits.). A circuit garbling scheme with wire labels consists of the following two polynomial-time algorithms:

- The garbling algorithm Garb:

$$\left(\{\tilde{\mathbf{C}}_i\}_i, \{u, b, \mathsf{Ibl}_{\mathrm{in}, b}^{u, i}\}_{u, i, b}\right) \leftarrow \mathsf{Garb}\bigg(1^\kappa, s, \mathbf{C}, \{v, b, \mathsf{Ibl}_{\mathrm{out}, b}^{v, i}\}_{v, i, b}\bigg)$$

for every  $u \in [v_{\rm in}], v \in [v_{\rm out}], i \in [s]$  and  $b \in \{0,1\}$ . That is, given a circuit C with input size  $v_{\rm in}$ , output size  $v_{\rm out}$  and s sets of output labels  $\{v,b,\mathsf{lbl}^{v,i}_{\mathrm{out},b}\}_{v,i,b}$ , outputs s garbled circuits  $\{\tilde{C}_i\}_{i \in [s]}$  and s sets of input labels  $\{u,b,\mathsf{lbl}^{u,i}_{\mathrm{in},b}\}_{u,i,b}$ .

- The evaluation algorithm Eval:

$$\left\{ \mathsf{Ibl}_{\mathrm{out}}^{1,i}, \dots, \mathsf{Ibl}_{\mathrm{out}}^{v_{\mathrm{out}},i} \right\}_{i \in [s]} = \mathsf{Eval} \bigg( \left\{ \tilde{\mathbf{C}}_i, \; (\mathsf{Ibl}_{\mathrm{in}}^{1,i}, \dots, \mathsf{Ibl}_{\mathrm{in}}^{v_{\mathrm{in}},i}) \right\}_{i \in [s]} \bigg).$$

That is, given s garbled circuits  $\{\tilde{C}_i\}_i$  and s sets of input labels  $\{\mathsf{lbl}_{\mathrm{in}}^{1,i},\ldots,\mathsf{lbl}_{\mathrm{in}}^{v_{\mathrm{in}},i}\}_i$ , outputs s sets of output labels  $\{\mathsf{lbl}_{\mathrm{out}}^{1,i},\ldots,\mathsf{lbl}_{\mathrm{out}}^{v_{\mathrm{in}},i}\}_i$ . Intuitively, if the input labels  $(\mathsf{lbl}_{\mathrm{in}}^{1,i},\ldots,\mathsf{lbl}_{\mathrm{in}}^{v_{\mathrm{in}},i})$  correspond to some input  $x \in \{0,1\}^{v_{\mathrm{in}}}$  then the output labels  $(\mathsf{lbl}_{\mathrm{out}}^{1,i},\ldots,\mathsf{lbl}_{\mathrm{out}}^{v_{\mathrm{out}},i})$  should correspond to y = C(x).

Furthermore, the following properties hold.

**Correctness.** For correctness, we require that for any circuit C and any input  $x \in \{0,1\}^{v_{\text{in}}}$ ,  $x = (x[1], \ldots, x[v_{\text{in}}])$  such that  $y = (y[1], \ldots, y[v_{\text{out}}]) = C(x)$  and any s sets of output labels  $\{v, b, \mathsf{lbl}_{b, \text{out}}^{v, i}\}_{v, i, b}$  (for  $u \in v_{\text{in}}, v \in v_{\text{out}}, i \in [s]$  and  $b \in \{0,1\}$ ) we have

$$\Pr\left[\mathsf{Eval}\big(\big\{\tilde{\mathbf{C}}_i,\; (\mathsf{Ibl}_{\mathrm{in},x[1]}^{1,i},\ldots,\mathsf{Ibl}_{\mathrm{in},x[v_{\mathrm{in}}]}^{v_{\mathrm{in}},i})\big\}_i\right) = \big\{\mathsf{Ibl}_{\mathrm{out},y[1]}^{1,i},\ldots,\mathsf{Ibl}_{\mathrm{out},y[v_{\mathrm{out}}]}^{v_{\mathrm{out}},i}\big\}_i\right] = 1$$

<sup>10</sup> This s might be different from the s used in the garbling algorithm, still we used the same letter for simplification.

<sup>&</sup>lt;sup>11</sup>Note that this holds with overwhelming probability since some of the garbled circuits might be malformed.

$$\text{ where } \left( \{ \tilde{\mathbf{C}}_i \}_i, \{ u, b, \mathsf{Ibl}_{\mathrm{in},b}^{u,i} \}_{u,i,b} \right) \leftarrow \mathsf{Garb} \left( 1^\kappa, s, \mathbf{C}, \{ v, b, \mathsf{Ibl}_{\mathrm{out},b}^{v,i} \}_{v,i,b} \right) \text{ as described above.}$$

Verifying the correctness of a circuit. Note that in a cut-and-choose based protocols, the receiver is instructed to check the correctness of a subset of the garbled circuits. This check can be accomplished by the sender sending the receiver the randomness used in Garb. In our protocol this is accomplished by giving the receiver both input labels for each input wire of the check circuits, for which it can verify that the circuit computes the agreed functionality. We note that this check is compatible with all prior known garbling schemes.

**Privacy.** For privacy, we require that there is a PPT simulator SimGC such that for any C, x, Z and  $\left\{ |\mathsf{bl}_{\mathsf{out}}^{1,z}, \dots, |\mathsf{bl}_{\mathsf{out}}^{v_{\mathsf{out}},z} \right\}_{z \in [Z]}, \{v, b, |\mathsf{bl}_{\mathsf{out},b}^{v,z} \}_{v,z \notin [Z],b}$  (i.e. one output label for wires in circuits indexed by  $z \notin Z$  and a pair of output labels for wires in circuits indexed by  $z \in Z$ ), we have

$$\left(\{\tilde{\mathbf{C}}_z\;(\mathsf{Ibl}_{\mathrm{in},x[1]}^{1,z},\ldots,\mathsf{Ibl}_{\mathrm{in},x[v_{\mathrm{in}}]}^{v_{\mathrm{in}},z})\}_z\right)\overset{\mathbf{c}}{\approx}\mathsf{SimGC}\left(1^\kappa,\left\{\mathsf{Ibl}_{\mathrm{out}}^{1,z},\ldots,\mathsf{Ibl}_{\mathrm{out}}^{v_{\mathrm{out}},z}\right\}_{z\in[Z]},\{v,b,\mathsf{Ibl}_{\mathrm{out},b}^{v,z}\}_{v,i\notin[Z],b}\right)$$

$$\text{ where } \left( \{ \tilde{\mathbf{C}}_z \}_z, \{u,b,\mathsf{Ibl}_{\mathrm{in},b}^{u,z} \}_{u,z,b} \right) \leftarrow \mathsf{Garb} \left( 1^\kappa, s, \mathbf{C}, \{v,b,\mathsf{Ibl}_{\mathrm{out},b}^{v,z} \}_{v,z,b} \right) \text{ and } y = \mathbf{C}(x).$$

**Authenticity.** We describe the authenticity game in Figure 8 (Appendix A.1) where the adversary is obtained a set of garbled circuits and garbled inputs for which the adversary needs to output a valid garbling of an invalid output. Namely, a garbled scheme is said to have *authenticity* if for every circuit C, for every PPT adversary  $\mathcal{A}$ , every s and for all large enough  $\kappa$  the probability  $\Pr[\operatorname{Auth}_{\mathcal{A}}(1^{\kappa}, s, C) = 1]$  is negligible. Our definition is inspired by the definition from [BHR12] and also adapted for the cut-and-choose approach.

**Input Consistency.** We abstract out the functionality that checks the validity of the sender's input across all garbled circuits. We say that, a garbling scheme has *input consistency* (in the context of cut-and-choose based protocols) if there exists a protocol that realize the  $\mathcal{F}_{IC}$  functionality described in Figure 7 (Appendix A.1).

Realizations of our garbled circuits notion. We require the existence of a protocol  $\Pi_{\rm IC}$  that securely realizes the functionality  $\mathcal{F}_{\rm IC}$  described in Figure 7, in the presence of malicious adversaries. In Appendix B we exemplify this realization with [LP11].

# 3 Building Blocks

In this section we show how to overcome the challenges discussed in the introduction and design the first maliciously secure 2PC protocol that does not require duplication of the data and works for every garbling scheme that supports our definition based on wire labels. Recall first that in [GHL<sup>+</sup>14] Gentry et al. have used a primitive called Timed IBE, where the secret-key for every memory location and stored bit (i, b) is enhanced with another parameter: the last time step t in which it has been written to the memory. The secret-key  $\mathsf{sk}_{(t,i,b)}$  for identity  $\mathsf{id} = (t,i,b)$  is then generated using the hard-coded time secret-key  $\mathsf{TSK}_t$ . Now, since algorithm KeyGen is randomized, running this algorithm t times will yield t independent secret timed keys. This results in t different values to be written to memory at the same location, which implies duplication of memory data t in order to avoid this, our solution forces the t duplicated garbled circuits for time step t to use the same random string t, yielding that all garbled circuits output the same key for the identity t, t, t, t, t. Importantly, this does not mean that we can hard-code t in all those t circuits, since doing

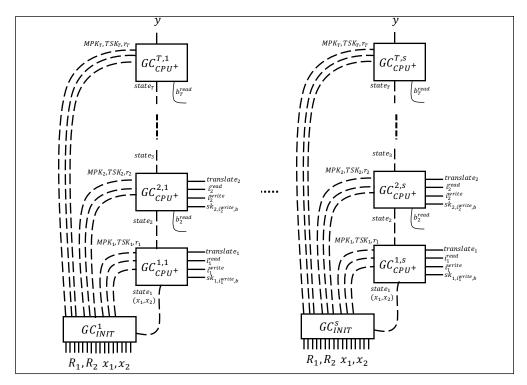

this would reveal r when applying the cut-and-choose technique on these garbled circuits as half of the circuits are opened. Clearly, we cannot reveal the randomness to the evaluator since the security definition of IBE (and Timed IBE) does not follow in such a scenario. Instead, we instruct the sender to input the *same randomness* in all s copies of the circuits and then run an input consistency check to these inputs in order to ensure that this is indeed the case. We continue with describing the components we embed in our protocol. An overview of the circuits involved in our protocol can be found in Figure 4 and a high-level overview of our protocol can be found in Section 4.

Figure 4: Garbled chains  $GC_{INIT}$ ,  $GC_{CPU^+}^{1,i}$ , ...  $GC_{CPU^+}^{T,i}$  for  $i \in [s]$ . Dashed lines refer to values that are passed privately (as one label per wire) whereas solid lines refer to values that are given in the clear.

# 3.1 Enhanced CPU-Step Function

The enhanced cpustep<sup>+</sup> function is essentially the CPU-step functionality specified in Section 2.1 enhanced with more additional inputs and output, and defined as follows

$$\mathsf{cpustep}^+(\mathsf{state}_t, b_t^\mathsf{read}, \mathsf{MPK}, \mathsf{TSK}_t, r_t) = (\mathsf{state}_{t+1}, i_t^\mathsf{read}, i_t^\mathsf{write}, b_t^\mathsf{write}, \mathsf{translate}_t)$$

where the additional inputs MSK, TSK $_t$  and  $r_t$  are the master public-key, a timed secret-key for time t and the randomness r used by the KeyGen algorithm. The output translate $_t$  is a pair of ciphertexts  $\operatorname{ct}_1,\operatorname{ct}_2,$  encrypted under MPK, that allows the evaluator to obtain the appropriate label of the wire that corresponds to the input bit in the next circuit. We denote the circuit that computes that function by  $\operatorname{C}^t_{\operatorname{CPU}^+}$ . The functionality of  $\operatorname{C}^t_{\operatorname{CPU}^+}$  is described in Figure 5. We later describe how to securely realize this function and, in particular, how these new additional inputs are generated and given to the T CPU-circuits. The enhanced CPU-step circuit wraps the WriteTime algorithm defined in Definition 2.2.

# Enhanced CPU-Step Circuit $C_{CPU}^t$

This circuit computes the enhanced CPU-step function cpustep<sup>+</sup>. This circuit wraps the following algorithms: (1) the usual cpu-step for computing the next CPU-step of program P, (2) WriteTime which computes the last time t' that the program wrote to location  $i_t^{\text{read}}$  and (3) the TIBE related functionalities KeyGen and Enc. Furthermore, the labels  $|\mathbf{b}|_1^{t+1}$  and  $|\mathbf{b}|_1^{t+1}$  are hard coded in the circuit.

#### Inputs.

- state<sub>t</sub> the last state that was output by the previous circuit. We define state<sub>1</sub> to be the parties' inputs  $x_1, x_2$  and set  $b_0^{\text{read}}$  to be zero.

- $b_t^{\text{read}}$  the last bit that was read from the memory data (i.e.  $b_t^{\text{read}}$  was read from location  $i_t^{\text{read}}$ ).

- MPK the master public key of the TIBE scheme.

- $\mathsf{TSK}_t$  a timed secret-key.

- $r_t$  randomness to be used by algorithms KeyGen and Enc<sub>MPK</sub>.

**Outputs.**  $C_{CPU}^t$  invokes  $C_{CPU}^t$  (the usual CPU-step circuit) that computes:

$$\mathsf{cpu\text{-}step}(\mathsf{state}_t, b_t^\mathsf{read}) = (\mathsf{state}_{t+1}, i_t^\mathsf{read}, i_t^\mathsf{write}, b_t^\mathsf{write})$$

where  $\mathsf{state}_{t+1}$  is the next state of the program;  $i^{\mathsf{read}}_{t+1}$  is the next location to read from;  $i^{\mathsf{write}}_{t+1}$  is the next location to write to and  $b^{\mathsf{read}}_{t+1}$  is the bit to write to location  $i^{\mathsf{write}}_{t+1}$ .

The circuit outputs the translation translate<sub>t</sub> =  $(\mathsf{ct}_t^0, \mathsf{ct}_t^1)$  defined by:

```

\begin{array}{lcl} t' & = & \mathsf{WriteTime}(i_{t+1}^\mathsf{read}) \\ \mathsf{ct}_t^0 & = & \mathsf{Enc}_\mathsf{MPK}(\mathsf{id} = (t, t', 0), \mathsf{msg} = \mathsf{lbl}_{t+1}^0) \\ \mathsf{ct}_t^1 & = & \mathsf{Enc}_\mathsf{MPK}(\mathsf{id} = (t, t', 1), \mathsf{msg} = \mathsf{lbl}_{t+1}^1) \end{array}

```

Finally, the circuit computes  $\mathsf{sk}_{(t,i,b)} = \mathsf{KeyGen}(\mathsf{TSK}_t, \mathsf{id} = (t, i_{t+1}^{\mathsf{write}}, b_{t+1}^{\mathsf{write}}))$  and outputs

$$(\mathsf{state}_{t+1}, i_{t+1}^{\mathsf{read}}, i_{t+1}^{\mathsf{write}}, \mathsf{sk}_{(t,i,b)}, \mathsf{translate}_t).$$

Figure 5: The CPU-step circuit.

# 3.2 Initialization Circuit

The initialization circuit generates all required keys and randomness to our solution and securely transfer them to the CPU-step circuits. As explained before, our solution requires the parties to input not only their input to the program but also a share to a randomness that the embedded algorithms would be given (that is, the randomness is not fixed by one of the parties). The circuit is described in figure 6.

# 3.3 Batch Single-Choice Cut-And-Choose OT

As a natural task in a cut-and-choose based protocol, we need to carry out cut-and-choose oblivious transfers for all wires in the circuit, for which the receiver picks a subset  $Z \subset [s]$  and then obtains either both input

#### Initialization Circuit $C_{INIT}$

The circuit generates all keys and randomness for the T CPU step circuits  $C^1_{CPU^+}, \dots, C^T_{CPU^+}$ .

#### Inputs.

- The parties input  $x_1, x_2$ , and

- $(2 \cdot (1 + T + T + 2T)) \cdot m = (8T + 2) \cdot m$  random values where m an upper bound on the length of the randomness required to run the TIBE algorithms: MasterGen, TimeGen, KeyGen and Enc. This particular number of random values is explained below.