# Rhythmic Keccak: SCA Security and Low Latency in HW

Victor Arribas<sup>1</sup>, Begül Bilgin<sup>1</sup>, George Petrides<sup>2</sup>, Svetla Nikova<sup>1</sup> and Vincent Rijmen<sup>1</sup>

<sup>1</sup> KU Leuven, imec-COSIC, Belgium, name.surname@esat.kuleuven.be

<sup>2</sup> Vrije Universiteit Brussel, Belgium, george.petrides@vub.be

**Abstract.** Glitches entail a great issue when securing a cryptographic implementation in hardware. Several masking schemes have been proposed in the literature that provide security even in the presence of glitches. The key property that allows this protection was introduced in threshold implementations as *non-completeness*. We address crucial points to ensure the right compliance of this property especially for low-latency implementations. Specifically, we first discuss the existence of a flaw in DSD 2017 implementation of KECCAK by Gross *et al.* in violation of the noncompleteness property and propose a solution. We perform a side-channel evaluation on the first-order and second-order implementations of the proposed design where no leakage is detected with up to 55 million traces. Then, we present a method to ensure a non-complete scheme of an unrolled implementation applicable to any order of security or algebraic degree of the shared function. By using this method we design a two-rounds unrolled first-order KECCAK-f[200] implementation that completes an encryption in 20.61ns, the fastest implementation in the literature to this date.

Keywords: Glitch  $\cdot$  non-completeness  $\cdot$  threshold implementation  $\cdot$  consolidated masking scheme  $\cdot$  domain-oriented masking

# 1 Introduction

Physical attacks are a serious threat to cryptographic implementations, capable of retrieving important information such as the secret key. In particular, Side-Channel Attacks (SCA), which are based on observing the behavior of the device without making any changes on it or its working conditions, are used frequently due to their relatively low cost and difficulty to be detected. In this paper, we use Differential Power Analysis (DPA) in particular, which exploits the relation between the intermediate values produced internally during the calculations and the instantaneous power consumption of the cryptographic device [KJJ99]. However, our observations can be generalized to other forms of SCA, such as the ones exploiting the electromagnetic emanation of the device [GMO01].

Different countermeasures have been proposed that aim to make the power consumption of a cryptographic device independent of the intermediate values. Here, we focus on Threshold Implementation (TI) [NRR06, NRS08, NRS11] and Domain Oriented Masking (DOM) [GMK16], which are based on secret sharing schemes and techniques from Multi-Party Computation (MPC). Moreover, they have the advantage of providing theoretical security on hardware if implemented according to the non-completeness property defined in [NRR06, BGN<sup>+</sup>14a], if fed with enough entropy and if the device works under the independent leakage assumption as described in [DFS15]. There are several papers in the literature applying these countermeasures on the KECCAK permutations: Bertoni *et al.* [BDPA10a] and Bilgin *et al.* [BDN<sup>+</sup>14] with first-order resistant implementations and more recent work by Gross *et al.* [GSM17] that proposes higher-order countermeasures. **Our contribution** In this paper, we first briefly summarize KECCAK sponge function, and TI and DOM schemes (Sect. 2). Then, we analyze the recently published higher-order DOM KECCAK implementations [GSM17] and point out a flaw that can possibly lead to successful attacks. We describe how careful tracing of the non-completeness property can be done to fix this flaw for any order. We show the different behavior between the original design and our proposal for first- and second-order implementations using TVLA with 55 million of traces (Sect. 3). Finally, we discuss how TI can be used for unrolled implementations without breaking the non-completeness property for the first time in literature. We present a low latency KECCAK implementation that performs an encryption in 20.61ns making it the fastest implementation published to this date (Sect. 4).

# 2 Preliminaries

### 2.1 Keccak Permutations

KECCAK is a family of sponge functions using the permutations KECCAK-f[b] where  $b \in \{25, 50, 100, 200, 400, 800, 1600\}$  defines different state sizes [BDPA10b]. KECCAK [BDPA10b] is the NIST SHA-3 standard [Rom14]. Among other properties, KECCAK stands out due to its high performance when implemented in hardware and its great area/speed trade-offs. The security claims of these variants follow the *Matryoshka principle*, i.e. analysis on of small sizes can easily be linked to bigger sizes. Benefiting from this property, we work on KECCAK-f[200], which is suitable for lightweight architectures and note that the concepts presented in this paper can naturally be extended to other choices of b. Moreover, since we simply work on KECCAK-f this work also covers KETJE [BDP+16a] and KEYAK [BDP+16b] authenticated encryptions.

KECCAK-f operates on a three-dimensional state S, where the bit in the coordinate (x, y, z) is denoted by S[x, y, z]. A round consists of five steps:

$$R = \iota \circ \chi \circ \pi \circ \rho \circ \theta, \text{ with}$$

$$\tag{1}$$

$$\theta: \quad S[x,y,z] \quad \leftarrow S[x,y,z] \oplus \bigoplus_{y'=0}^{4} S\left[x-1,y',z\right] \oplus \bigoplus_{y'=0}^{4} S\left[x+1,y',z-1\right],$$

$$\begin{split} \rho : \quad S\left[x, y, z\right] & \leftarrow S\left[x, y, z - (t+1)(t+2)/2\right], \\ & \text{with } t \text{ satisfying } 0 \le t < 24 \text{ and } \begin{pmatrix} 0 & 1 \\ 2 & 3 \end{pmatrix}^t \begin{pmatrix} 1 \\ 0 \end{pmatrix} = \begin{pmatrix} x \\ y \end{pmatrix} \text{ in } \mathrm{GF}(5)^{2 \times 2}, \\ & \text{or } t = -1 \text{ if } x = y = 0, \end{split}$$

$$\pi: \quad S[x,y] \quad \leftarrow S\left[x',y'\right], \text{ with } \left(\begin{array}{c} x\\ y\end{array}\right) = \left(\begin{array}{c} 0 & 1\\ 2 & 3\end{array}\right) \left(\begin{array}{c} x'\\ y'\end{array}\right),$$

$$\chi:$$

$S[x] \leftarrow S[x] \oplus (S[x+1] \oplus 1)S[x+2]$

ι

:

$$S \leftarrow S \oplus \operatorname{RC}[i_r]$$

, where  $\operatorname{RC}[i_r]$  is the round counter in cycle  $i_r$

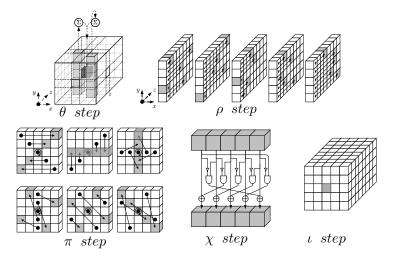

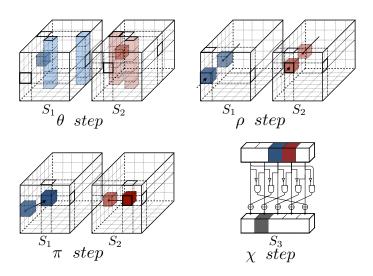

KECCAK-f[200] computes 18 rounds. Notice that we abuse the notation to focus on specific coordinates. Moreover, addition and subtraction in the coordinates are modular. For convenience, we provide visualizations of these steps in App. A.1 (Fig. 8) for KECCAK-f[200].

### 2.2 Masking Schemes

Different forms of masking schemes have been shown to provide provable security against side-channel analysis attacks given independent leakage and uniform input assumption. They are based on secret sharing where each sensitive, i.e. key dependent, data x is divided into s pieces ( $\mathbf{x} = (x_1, \ldots, x_s)$ ) such that  $x = x_1 \perp \ldots \perp x_s$ . Throughout this paper, we consider Boolean masking where  $\perp$  is field addition denoted by  $\oplus$  and full threshold sharing where all s shares need to be combined to derive x. The exact value of s is chosen depending on the desired security level which is specified further for different flavors of masking below.

Each function f(x) = y of the cryptographic algorithm is calculated in a shared manner where  $f_i(\mathbf{x}) = y_i$ . Masking is *correct* if  $\bigoplus y_i = y$ .

*d*-Probing Model. It has been shown in [DFS15] that if a masked circuit achieves security under the *d*-probing model [ISW03] where each calculation is treated separately, independent of the timing of the circuit, then it also provides security against  $d^{\text{th}}$ -order side-channel analysis attacks under independent leakage assumption. Similar to [RBN<sup>+</sup>15, FGP<sup>+</sup>17], we assume that an adversary probing a wire has information about all the intermediate values starting from the registers to the probed point of calculation. Note that this probing model is used specifically on hardware where glitches might occur in the circuit. As a result a *d*-probing adversary would acquire the knowledge of all the intermediate values used in all *d* probed wires.

#### 2.2.1 Threshold Implementation (TI)

This masking method, which is introduced by Nikova *et al.* [NRR06] for first-order security and extended by Bilgin *et al.* [BGN<sup>+</sup>14a] for higher-order security, is used widely on hardware since, unlike many masking schemes, it provides security under the non-ideal gate assumption. That is, the gates can glitch depending on prior inputs of that cycle before stabilizing without giving an advantage to an attacker. Below we repeat the non-completeness definition for completeness.

**Definition 1** (Non-completeness [BGN<sup>+</sup>14a]). The shared circuit  $\mathbf{f}$  of f is  $d^{\text{th}}$ -order non-complete if any combination of up to d component functions  $f_i$  is independent of at least one input share.

The lower bounds of number of input and output shares required to calculate a function of algebraic degree t such that it satisfies the above non-completeness property are given in [BGN<sup>+</sup>14a] as follows:

$$\begin{array}{rcl}

s_{in} &\geq & td+1, \\

s_{out} &\geq & \left(\begin{array}{c} s_{in_{min}} \\ t \end{array}\right).

\end{array}$$

(2)

This bound has then been used for a variety of algorithms and security orders [BNN<sup>+</sup>12, BGN<sup>+</sup>14b, BNN<sup>+</sup>14, BGN<sup>+</sup>15, BDN<sup>+</sup>14, CBR<sup>+</sup>15].

We provide the sharings of an AND/XOR gate  $(z = a \oplus bc)$  where  $(d, s_{in}, s_{out}) = (1, 3, 3)$ and  $(d, s_{in}, s_{out}) = (2, 5, 10)$  in Eqns (3) and (9) (in App. A.2) respectively together with a graphical representation in Fig. 9 (in App. A.2). We refer to a sharing with  $s_{in} = s_{out} = s$ as an s-sharing.

$$z_1 = a_1 \oplus b_1 c_1 \oplus b_1 c_2 \oplus b_2 c_1,$$

$$z_2 = a_2 \oplus b_2 c_2 \oplus b_2 c_3 \oplus b_3 c_2,$$

$$z_3 = a_3 \oplus b_3 c_3 \oplus b_1 c_3 \oplus b_3 c_1.$$

(3)

In order to satisfy the non-completeness property, the *compression* from  $s_{out}$  to  $s_{in}$  shares must follow a synchronization layer such as registers. The first-order case becomes advantageous since  $s_{out} = s_{in}$  and this intermediate synchronization layer is not necessary enabling a one cycle implementation. If a sharing dissatisfies the non-completeness property, we call it a *complete* sharing.

Another property introduced by TI is a uniform sharing. Since we only use permutations in this paper, we provide a simplified definition below.

**Definition 2** (Uniform Sharing [BGN<sup>+</sup>14a]). The s-sharing of an n-bit permutation f(x) = y is uniform if its sharing  $\mathbf{f}(\mathbf{x}) = \mathbf{y}$  (after compression) is an *ns*-bit permutation.

If this property is satisfied for each step of a cryptographic algorithm, the algorithm provides univariate security without the need of additional randomness. It has been shown in [RBN<sup>+</sup>15] that uniformity condition is not enough for multi-variate security in the higher-order case. The authors show that it is possible to achieve higher-order multi-variate security for TI by inserting fresh randomness to each  $s_{out}$  output shares just before the compression. This *refreshing* naturally provides a uniform sharing.

#### 2.2.2 Domain Oriented Masking (DOM)

In [GMK16], Gross *et al.* introduced  $d^{\text{th}}$ -order secure DOM-indep multiplier which uses  $s_{in} = d + 1$  input shares and d(d+1)/2 units of randomness. DOM multiplier assumes  $s_{in}$  domains.

The sharing structure of DOM-indep multiplier uses d + 1 input shares for hardware and is a follow up of Reparaz et al. [RBN<sup>+</sup>15] which provides security given only the independence of the shared input variables. The difference between DOM-indep as opposed to [RBN<sup>+</sup>15] multiplier is the significant randomness optimization, from  $(d + 1)^2$  to d(d + 1)/2. This optimized shared multiplier has been used in [GSM17] to provide very small implementations of KECCAK with higher-order security claim. We provide a DOMindep AND gate (z = ab) where  $(d, s_{in}, s_{out}) = (1, 2, 4)$  and  $(d, s_{in}, s_{out}) = (2, 3, 9)$  in Eqn. 4 below and in Eqn. 10 in appendix. The parenthesis [.] and (.) represent the mandatory and optional synchronizations respectively and r refers to the randomness used for refreshing.

$$z_{1} = (a_{1}b_{1}) \oplus [a_{1}b_{2} \oplus r],$$

$$z_{2} = [a_{2}b_{1} \oplus r] \oplus (a_{2}b_{2}).$$

(4)

In [GMK16] a second multiplier called DOM-dep multiplier is also introduced. DOMdep has the advantage of not relying on the independently shared inputs assumption of other d + 1 share schemes DOM-indep and [RBN<sup>+</sup>15] while using less randomness. For details of DOM-dep multiplier and randomness reductions of DOM, we refer to the original paper. Here, we only focus on DOM-indep multiplier which was used in [GSM17] and the non-completeness property. Therefore, we refer to DOM-indep as DOM for brevity.

# 3 Round-Based Implementations

KECCAK is implemented for a variety of platforms and constraints. The smallest roundbased implementation claiming security against side-channel analysis attacks is the work from Gross *et al.* [GSM17] which uses DOM. In this section, we first show an exploitable weakness of that round based implementation based on the failure of non-completeness property. We then verify the observability of our claims on an FPGA using t-test based leakage detection. Finally, we discuss how a sharing using  $s_{in} \ge d + 1$  shares should be implemented such that it satisfies the non-completeness property and the restrictions of such an implementation. Note that our analysis covers round-based implementations of any order but does not cover the serialized architectures presented in [GSM17].

### 3.1 Analysis of DOM-Keccak

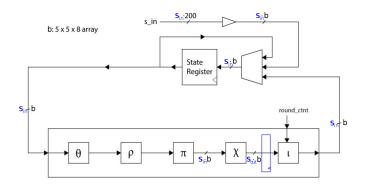

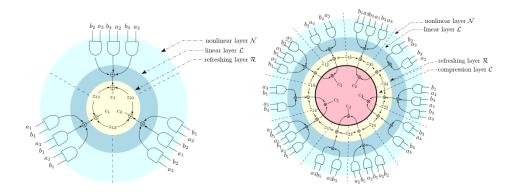

A traditional round-based implementation of KECCAK receives the input of  $\theta$  from a register;  $\theta$ ,  $\rho$ ,  $\pi$ ,  $\chi$  and  $\iota$  operations are calculated within the same clock cycle and the output of  $\iota$ is written to a register. When we consider a shared implementation the  $\chi$ -refreshing needs to be separated from  $\chi$ -compression by registers to achieve non-completeness marking the end of the cycle. The difference between these two architectures are depicted in Figure 1 where the blue marks correspond to the masked version. The  $\chi$ -compression is included in the  $\iota$  block.

Figure 1: Plain and secure(blue) KECCAK round-based implementation

The implementation in [GSM17] uses the sharing in Eqn. (5) of  $\chi$  up to the synchronization register for first order. The randomness r is taken from another (independent) part of the state. The synchronization is performed only on the *cross-domain* shares  $S'_2[x]$ and  $S'_3[x]$  by using a register triggered on the negative edge of the clock while triggering the state register in the positive edge (double clocking). Analyzing each linear and nonlinear step individually as is done in [GSM17], shows that the non-completeness property is satisfied in each separate step. However, the non-completeness of any implementation should be verified from register to register since the glitchy behavior can accumulate.

$$\begin{aligned}

S'_{1}[x] &\leftarrow S_{1}[x] \oplus (S_{1}[x+1] \oplus 1)S_{1}[x+2], \\

S'_{2}[x] &\leftarrow S_{1}[x+1]S_{2}[x+2] \oplus r, \\

S'_{3}[x] &\leftarrow S_{2}[x+1]S_{1}[x+2] \oplus r, \\

S'_{4}[x] &\leftarrow S_{2}[x] \oplus (S_{2}[x+1] \oplus 1)S_{2}[x+2].

\end{aligned}$$

(5)

When we analyzed one round of the aforementioned implementation, we noticed that the non-completeness property from register to register is not satisfied for 112 output bits of the round output invalidating a condition for security. Below we trace back the input shares used to calculate a specific bit of the state particularizing Eqn. (1) for first-order secure implementation. A graphical representation is also provided in Fig. 10 in App. A.3.1. We use  $S_i^f$  to refer to the output of f for share  $S_i$ : Tracing back output bit  $S^{\chi}[4,1,0]$  of the  $\chi$  permutation:

$$\begin{split} \chi^{-1} : & S_3^{\chi} \left[ 4, 1, 0 \right] & \leftarrow S_2^{\pi} \left[ 0, 1, 0 \right] S_1^{\pi} \left[ 1, 1, 0 \right] \oplus r \\ \pi^{-1} : & S_2^{\pi} \left[ 0, 1, 0 \right] & \leftarrow S_2^{\rho} \left[ 3, 0, 0 \right] \\ & S_1^{\pi} \left[ 1, 1, 0 \right] & \leftarrow S_1^{\rho} \left[ 4, 1, 0 \right] \\ \rho^{-1} : & S_2^{\rho} \left[ 3, 0, 0 \right] & \leftarrow S_2^{\theta} \left[ 3, 0, 4 \right] \\ & S_1^{\rho} \left[ 4, 1, 0 \right] & \leftarrow S_1^{\theta} \left[ 4, 1, 4 \right] \\ \theta_1^{-1} : & S_2^{\theta} \left[ 3, 0, 4 \right] & \leftarrow S_2 \left[ 3, 0, 4 \right] \oplus \bigoplus_{y'=0}^{4} S_2 \left[ 2, y', 4 \right] \oplus \bigoplus_{y'=0}^{4} S_2 \left[ 4, y', 3 \right] \\ & S_1^{\theta} \left[ 4, 1, 4 \right] & \leftarrow S_1 \left[ 4, 1, 4 \right] \oplus \bigoplus_{y'=0}^{4} S_1 \left[ 3, y', 4 \right] \oplus \sum_{y'=0}^{4} S_1 \left[ 0, y', 3 \right] \end{split}$$

From these expressions it can be derived that the output bit  $S_3^{\chi}[4, 1, 0]$  of the non-linear layer depends, among others, on the input bits  $S_1[3, 0, 4]$  and  $S_2[3, 0, 4]$ . This means that all shares of [3, 0, 4] are used and hence, non-completeness fails. Note that similar complete output bits can also be found for higher-order implementations. We provide a second-order example in App. A.3.1.

#### 3.1.1 Evaluation

To illustrate the problem presented above we implement a first-order DOM-KECCAK and test on FPGA. Our masked round-based implementation follows the structure depicted in Fig. 1. Note that we do not use negative-edge triggering for the cross-domain shares for ease of analysis leading to a two cycle per round implementation. Moreover, we always use fresh randomness to ensure that a possible problem in the second order is not caused by the degradation on the uniformity.

**Platform.** To evaluate our design, we deploy it into a Spartan-6 Xilinx FPGA on a Sakura-G board, which is specifically designed for side-channel evaluation. To reduce the noise during the evaluation we split the implementation into two different FPGAs: a control FPGA handles I/O with the host computer and supplies data in masked representation to the crypto FPGA. Crypto FPGA holds a PRNG, which generates the randomness for refreshing, and our masked KECCAK designs. In order to get the cleanest possible traces, we clock the PRNG in the negative edge to avoid extra noise and use a very slow 3 MHz clock so that we are sure there is no overlap in the power consumption. The design is synthesized using the Xilinx tools with the property KEEP HIERARCHY set to *yes*, in order to avoid optimizations among the different blocks what would compromise the security of the design. We sample at 1.0GS/s with 2000 points per frame over two rounds and a half.

**TVLA.** We use non-specific test vector leakage assessment (TVLA) method described in  $[CMG^+13]$  to detect leakage. Note that this t-test based leakage detection method is not used to mount an attack and retrieve the key. From a theoretical point of view, the presence of leakage is a necessary, but not sufficient condition for an attack to succeed. However, not observing leakage gives confidence to designer. We choose our confidence level to be 99.9995% which corresponds to absolute t-values being greater than 4.5 for failure.

Two different tests are performed, namely, Fix vs. Random with masks off and with masks on. In both cases the idea is to compare the power consumption of the

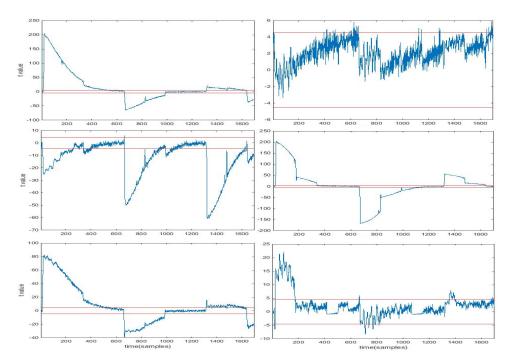

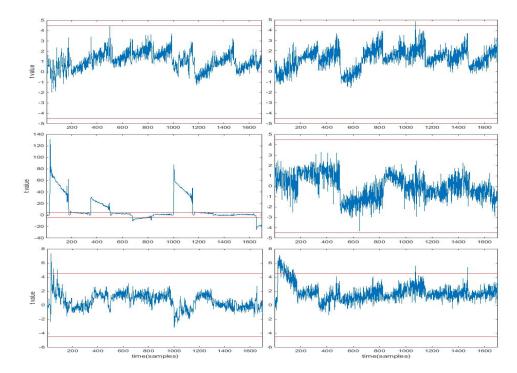

Figure 2: TVLA on first-order DOM-KECCAK implementation. Left: Masks off. Right: masks on

KECCAK-*f* given to different states, the first one, chosen at random and fixed through all the encryptions and the second one, randomly chosen as well, that changes for every encryption. The test determines whether it is possible to distinguish between one another and hence, find potentially exploitable leakage depending on the state. When masks are off leakage is expected, since the countermeasures are switched off. On the other hand, when masks are on we expect no first-order leakage for a first-order implementation. We ensure that the initial sharing is done properly and focus our analysis only on the first two rounds of the cipher to validate our claims. All designs analyzed in this work are done under this same conditions.

Figure 2 shows results of TVLA for 20 thousand traces when masks are off and 55 million traces when masks are on for a DOM-KECCAK implementation. In this case, although the leakage is reduced greatly, we see that the t-score goes over 4.5 for a significant number of sample points during both first and second rounds. We emphesize that we make no claims on this observation leading to a successful attack. Our goal is to make leakage assessment comparison between this implementation and our proposal which is presented in the next section.

### 3.2 Non-Complete Round-Based Architecture

The question that naturally arises after this analysis is the root of the non-completeness failure. Clearly, it is important to take into account the effect of the linear layers in combination with the non-linear layer within a cycle, since  $\chi$  and the linear operations including  $\theta$  are secure individually. A detailed observation shows the following.

**Order of operations.** The order of linear and non-linear operations within a round is important. If the round structure of a cryptographic algorithm follows the traditional SPN approach where the linear operation follows the non-linear operation within a round,

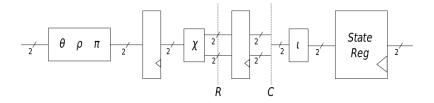

Figure 3: One round structure of the naive fix

Figure 4: One round structure of our design

we would not observe this failure of non-completeness if the non-linear operation is noncomplete. For higher orders, one still needs to ensure composibility, which is not the objective of this paper's discussion.

**Linear transformations.** The structure of KECCAK linear operations, in particular  $\theta$  which shuffles and *combines* several state bits, causes the non-completeness to fail when  $\chi$  is applied later. Operations  $\rho$  and  $\pi$  being simple wirings do not combine several bits and hence do not cause any problem.

**Naive fix.** Following above observations, one can clearly see that it suffices to introduce a register between the linear operations and  $\chi$  to secure the design. However, this new layer of registers increases the number of cycles required per round. When combined with the register needed just right after the refreshing layer, the cycle count becomes three times bigger than the plain implementation of KECCAK-f[200] without a significant increase in maximum frequency. Fig. 3 illustrates this architecture. However, the main goal tried to achieve with a parallel implementation is a low-latency design, compared to a serial implementation that would have a higher latency but smaller area.

**Our design.** In order to reduce the latency, we remove the registers that come after step  $\chi$  and use the state registers instead to keep the security conditions. This way the compression layer comes right after the state registers and before starting the next round computations. In this case we need two clock cycles to perform one round and hence 36 cycles for KECCAK-f[200]. Figure 4 presents this structure, with which the implementation is fulfilling non-completeness. Note that it is possible to re-use some part of the state register for synchronization after the linear layer with a careful selection of reused registers. This would reduce the area by approximately 2800GE. Here, we use two separate registers for clear analysis of the target difference.

#### 3.2.1 Evaluation

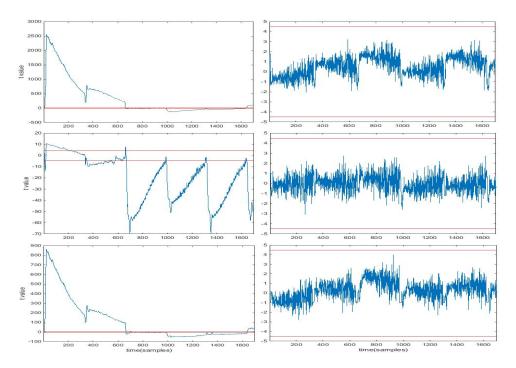

Here we present the results for our non-complete KECCAK (NC-KECCAK) for both firstand second-order implementations, which follow the structure defined in Fig. 4. We kept exactly the same setup as in Section 3.1.1 for comparability. In the case of the first-order secure implementation no first-order leakage appears, while in the second-order neither first- nor second-order leakage appear up to 55 million traces. Fig. 5 presents these results.

Figure 5: T-test on first (left) and second-order (right) NC-KECCAK implementations over 55M traces.

### 3.3 Performance Analysis

To synthesize our designs we use Synopsys Design Compiler Version I-2013.12 with NanGate 45nm Open Cell Library. The synthesis is done by using the -compile command and setting the flag -exact\_map to avoid any optimization that could affect the security. The option -no\_autoungroup is set by default when using -compile. This way it keeps the hierarchy of the design so that no optimizations in between modules can happen. Table 1 shows the results for this section's implementations. Note that the number of random bits presented is for each round, i.e., for every two clock cycles, and can be reduced significantly using the ideas from [BDN<sup>+</sup>14, GSM17, Dae17] which is not the goal of this paper.

Table 1: Synthesis results for the different designs

|                |            | ARE   | A(kGE)   |       |       |        | Max.Freq. |

|----------------|------------|-------|----------|-------|-------|--------|-----------|

| DESIGN         | $\chi$     | θ     | State    | Total | Rand. | Cycles | (MHz)     |

| Plain          | 542.63     | 638.4 | 1333     | 2759  | -     | 18     | 1 1 3 6   |

| DOM-Keccak 1st | $9881^{*}$ | 1600  | 2667     | 17105 | 200   | 36     | 1087      |

| NC-Keccak 1st  | 2613       | 1600  | $5334^*$ | 17493 | 200   | 36     | 1300      |

| NC-Keccak 2nd  | 6200       | 2400  | 12001*   | 35223 | 600   | 36     | 1205      |

\* This number includes the registers layer needed before the compression

# 4 Speeding Up Keccak Implementations

Our goal in this section is to push the limits of low-latency masked KECCAK implementation using standard CMOS-like cells. Clearly, it is very challenging to provide a secure unrolled implementation of KECCAK that calculates more than one round in one clock cycle using a  $s_{in} = d + 1$  share masking scheme. However, due to increased number of shares TI can become advantageous in this setting. In what follows, we first discuss how to implement multiple layers of nonlinear functions generically. Then, we propose a method to halve the latency of a KECCAK implementation using TI and analyze the difficulties found in the process. We conclude this section with our security analysis and synthesis results which shows the fastest secure hardware implementation published to this date.

### 4.1 Unrolling Quadratic Round Functions

Let  $\mathcal{R}_i$  be a quadratic round function, similar to that of KECCAK permutations. And let us initially target two rounds,  $\mathcal{F} = \mathcal{R}_i \circ \mathcal{R}_{i+1}$ . That is, we need to share and calculate not a quadratic, but a quartic function. According to Eqn. (2), a first-order resistant implementation of a quartic function requires  $s_{in} \geq 5$  shares given the algebraic normal form (ANF) of this function. However, for KECCAK and many other schemes alike gathering and using the ANF of two rounds  $\mathcal{F}$  is not trivial due to the high diffusion of state bits. Specifically for KECCAK-f[200], it can be seen that a single output bit of  $\mathcal{F}$  depends on almost all input bits. Due to this difficulty and to avoid a case by case analysis for each target algorithm, we opt to develop a generic method.

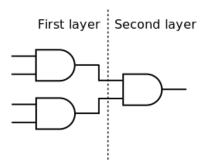

For additional simplicity, let's assume  $\mathcal{R}_i$  is composed of a series of AND gates. The dependency for a particular output is provided in Fig. 6. It is clear that if we implement the first layer using 3 shares which is the minimum number of shares proposed for first-order security in Eqn. (2), the first layer would indeed be secure. However the second layer which uses the first layer's output can not satisfy non-completeness, i.e. every output share of  $\mathcal{F}$  would depend on all input shares of  $\mathcal{F}$ .

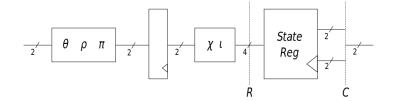

Figure 6: Quartic operation composed of two quadratic operations

We would like to achieve first-order security even at the last round of unrolled implementation. With our method, we suggest to crawl backward until the first round of  $\mathcal{F}$  and decide how-many shares we need. That is, we observe that first-order non-completeness of a quadratic function in the second layer implies combination of any two shares being independent of the secret in the input of the second layer. This implies any two share of the output of the first layer being independent of the input which is the definition of second-order non-completeness. Hence, if we implement the first and second layers such that they satisfy second- and first-order non-completeness respectively,  $\mathcal{F}$  would satisfy first-order non-completeness. This observation is naturally applicable to higher degree functions and easily extendable to more rounds. There is still one challenge remaining: the second-order non-complete layer will increase the number of shares, hence the first order non-complete layer should be compatible to work with increased number of shares with embedded compression layer to keep the number of shares at the output of  $\mathcal{F}$  as low as possible. We call a sharing where  $s_{in} > s_{out}$  a compression sharing.

### 4.2 First Attempt for Keccak

We build the second order secure sharing for  $\mathcal{R}_i$  with  $s_{in} = 5$  and  $s_{out} = 10$ . Eqn. (6) shows the output dependencies on the input shares for an AND gate. Every combination of two outputs is independent of at least one input share.

$$S'_{1} = f_{1}(S_{1}, S_{2}) \qquad S'_{6} = f_{6}(S_{1}, S_{3})$$

$$S'_{2} = f_{2}(S_{2}, S_{3}) \qquad S'_{7} = f_{7}(S_{3}, S_{5})$$

$$S'_{3} = f_{3}(S_{3}, S_{4}) \qquad S'_{8} = f_{8}(S_{5}, S_{2}) \qquad (6)$$

$$S'_{4} = f_{4}(S_{4}, S_{5}) \qquad S'_{9} = f_{9}(S_{2}, S_{4})$$

$$S'_{5} = f_{5}(S_{5}, S_{1}) \qquad S'_{10} = f_{10}(S_{4}, S_{1})$$

Note that due to the linear layer of KECCAK-f, the AND gates in  $\mathcal{R}_{i+1}$  depends more than the output of two AND gates. Hence, not every first-order non-complete sharing of  $\mathcal{R}_{i+1}$  leads to a non-complete  $\mathcal{F}$ . Moreover, even though many direct  $10 \rightarrow 10$  sharings of  $\mathcal{R}_{i+1}$  satisfying the above restriction can be derived following a simple procedure (every output share will combine three of the previous pairs where at most two of the initial input shares can be repeated), we would like to have a compression sharing to avoid increase of number of shares.

For a target of  $10 \rightarrow 5$  compression sharing, we need to be more careful since more pairs are combined. Eqn. (7) illustrates the input-output dependency of a possible sharing for  $\mathcal{R}_{i+1}$ .

$$\begin{aligned}

S_1'' &= f_1(S_1', S_2', S_3', S_6', S_9', S_{10}') & (\text{Missing input } S_5) \\

S_2'' &= f_2(S_1', S_2', S_5', S_6', S_7', S_8') & (\text{Missing input } S_4) \\

S_3'' &= f_3(S_1', S_4', S_5', S_8', S_9', S_{10}') & (\text{Missing input } S_3) \\

S_4'' &= f_4(S_3', S_4', S_5', S_6', S_7', S_{10}') & (\text{Missing input } S_2) \\

S_5'' &= f_5(S_2', S_3', S_4', S_7', S_8', S_9') & (\text{Missing input } S_1)

\end{aligned}$$

(7)

### 4.3 Our Design

The greatest area contributor of a KECCAK parallel implementation, is the  $\chi$  step. The number of gates in the non-linear operation scales with the number of input shares as follows:

- Number of AND gates =  $\begin{pmatrix} s_{in} \\ 2 \end{pmatrix} + s_{in}$

- Number of XOR gates =  $\begin{pmatrix} s_{in} \\ 2 \end{pmatrix} + s_{in}$

- Number of NOT gates  $= s_{in}$

The area overhead of increasing the number of shares to 10 is significant, so we decided to look for another sharing for the first layer that produces less outputs. One possible option is the  $6 \rightarrow 7$  sharing proposed in [BGN<sup>+</sup>14a]. Our further investigations lead to  $6 \rightarrow 6$  sharing schemes that we can use for both layers, which are shown in Eqn. (8).

| $S_1' = f_1(S_1, S_2, S_3)$ | $S_1'' = f_1(S_4', S_5', S_6')$ | (Missing input $S_1$ ) |     |

|-----------------------------|---------------------------------|------------------------|-----|

| $S_2' = f_2(S_1, S_4, S_5)$ | $S_2'' = f_2(S_2', S_3', S_5')$ | (Missing input $S_2$ ) |     |

| $S_3' = f_3(S_1, S_4, S_6)$ | $S_3'' = f_3(S_2', S_3', S_4')$ | (Missing input $S_3$ ) | (8) |

| $S'_4 = f_4(S_2, S_5, S_6)$ | $S_4'' = f_4(S_1', S_4', S_5')$ | (Missing input $S_4$ ) |     |

| $S_5' = f_5(S_3, S_5, S_6)$ | $S_5'' = f_5(S_1', S_3', S_6')$ | (Missing input $S_5$ ) |     |

| $S_6' = f_6(S_2, S_3, S_4)$ | $S_6'' = f_6(S_1', S_2', S_6')$ | (Missing input $S_6$ ) |     |

With this sharing we are able to reduce the area considerably without failing noncompleteness.

#### 4.3.1 Performance Analysis

The implementation is done in parallel by concatenating two rounds, i.e. the round which is depicted with a box in Fig. 1 is repeated twice before synchronization. We present the results for the two sharing schemes mentioned above in Table 2 for comparison.

Table 2: Results for the different double round sharings which require 9 cycles and no extra randomness for refreshing

|                                                                                                | AREA(kGE)             |                  |              |             |                  | Max.Freq.                                     |                   |

|------------------------------------------------------------------------------------------------|-----------------------|------------------|--------------|-------------|------------------|-----------------------------------------------|-------------------|

| DESIGN                                                                                         | $\chi_1$              | $\chi_2$         | $	heta_1$    | $	heta_2$   | State            | Total                                         | (MHz)             |

| $\begin{array}{c} 5 \rightarrow 10 \rightarrow 5 \\ 6 \rightarrow 6 \rightarrow 6 \end{array}$ | $\frac{13533}{22400}$ | $59893 \\ 22160$ | $4280\ 5662$ | $9747\5662$ | $6\ 700\ 8\ 033$ | $\begin{array}{c} 99347 \\ 70120 \end{array}$ | $395.25 \\ 436.7$ |

The first non-linear operation in  $5 \rightarrow 10 \rightarrow 5$  sharing is a bit cheaper than the one using  $6 \rightarrow 6 \rightarrow 6$ . However, the second non-linear operation of  $5 \rightarrow 10 \rightarrow 5$  is significantly more expensive due to the greater number of inputs as expected. In the  $6 \rightarrow 6 \rightarrow 6$  scheme the state register is a bit bigger since there is one more share to store. All things considered, the area reduction of our design compared to a first attempt is clear.

Given the results, is possible to see that the time needed for a single encryption is 20.61ns. Therefore we can affirm this is the fastest round based KECCAK implementation published to this date.

### 4.3.2 Evaluation

We evaluate the optimized design using the  $6 \rightarrow 6 \rightarrow 6$  sharing. The test is done under the conditions already presented in Section 3.1.1. Since this implementation is much faster than the previous ones, the analysis covers 10 rounds of the cipher.

The results are presented in Fig. 7 for masks off and masks on. It is possible to appreciate that the countermeasures indeed prevent leakage from appearing in the first-order. Moreover, we observe no leakage in the second or in the third order t-test using 55 million measurements. We attribute this to the noise introduced by the large number of shares used.

# 5 Conclusions

In this work we presented, on the one hand, a flaw in previous round based KECCAK secure implementations on hardware and how to address this issue. We propose this solution

Figure 7: T-test on first order d+1 KECCAK implementation. Left: Masks off. Right: DOM-KECCAK masks on

for KECCAK permutations, but it is also applicable to other algorithms that concatenate several linear and non-linear operations. On the other hand, we introduced a method to speed up masked hardware implementations. Thus, by applying this method, the fastest KECCAK implementation is presented.

# References

- [BDN<sup>+</sup>14] B. Bilgin, J. Daemen, V. Nikov, S. Nikova, V. Rijmen, and G. Van Assche. Efficient and first-order DPA resistant implementations of keccak. in CARDIS, volume 8419 of LNCS pp 187-199, June 2014.

- [BDP<sup>+</sup>16a] G. Bertoni, J. Daemen, M. Peeters, G. Van Assche, and R. Van Keer. Caesar submission: Ketje v2, September 2016.

- [BDP<sup>+</sup>16b] G. Bertoni, J. Daemen, M. Peeters, G. Van Assche, and R. Van Keer. Caesar submission: Keyak v2, September 2016.

- [BDPA10a] G. Bertoni, J. Daemen, M. Peeters, and G. Van Assche. Building power analysis resistant implementations of keccak. Second SHA-3 candidate conference, August 2010.

- [BDPA10b] G. Bertoni, J. Daemen, M. Peeters, and G. Van Assche. The keccak reference. http://http://keccak.noekeon.org/, January 2010.

- [BGN<sup>+</sup>14a] B. Bilgin, B. Gierlichs, S. Nikova, V. Nikov, and V. Rijmen. Higher-order threshold implementations. In ASIACRYPT, volume 8874 of LNCS, pages 326-343. Springer, 2014.

- [BGN<sup>+</sup>14b] B. Bilgin, B. Gierlichs, S. Nikova, V. Nikov, and V. Rijmen. A more efficient aes threshold implementation. In D. Pointcheval and Damien Vergnaud, editors, *Progress in Cryptology-AFRICACRYPT 2014*, volume 8469 of *Lecture Notes in Computer Science*, pages 267–284. Springer International Publishing, 2014.

- [BGN<sup>+</sup>15] B. Bilgin, B. Gierlichs, S. Nikova, V. Nikov, and V. Rijmen. Trade-offs for threshold implementations illustrated on AES. Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on, 34(7):1188–1200, July 2015.

- [BNN<sup>+</sup>12] B. Bilgin, S. Nikova, V. Nikov, V. Rijmen, and G. StÃijtz. Threshold implementations of all 3 × 3 and 4 × 4 s-boxes. In Emmanuel Prouff and Patrick Schaumont, editors, Cryptographic Hardware and Embedded Systems-CHES 2012, volume 7428 of Lecture Notes in Computer Science, pages 76–91. Springer Berlin Heidelberg, 2012.

- [BNN<sup>+</sup>14] B. Bilgin, S. Nikova, V. Nikov, V. Rijmen, N. Tokareva, and V. Vitkup. Threshold implementations of small s-boxes. *Cryptography and Communications*, pages 1–31, 2014.

- [CBR<sup>+</sup>15] T. De Cnudde, B. Bilgin, O. Reparaz, V. Nikov, and S. Nikova. Higher-order threshold implementation of the AES s-box. In Naofumi Homma and Marcel Medwed, editors, Smart Card Research and Advanced Applications - 14th International Conference, CARDIS 2015, Bochum, Germany, November 4-6, 2015. Revised Selected Papers, volume 9514 of Lecture Notes in Computer Science, pages 259–272. Springer, 2015.

- [CMG<sup>+</sup>13] J. Cooper, E. De Mulder, G. Goodwill, J. Jaffe, G. Kenworthy, and P. Rohatgi. Test vector leakage assessment (TVLA) methodology in practice. International Cryptographic Module Conference, 2013. http://icmc-2013.org/wp/ wp-content/uploads/2013/09/goodwillkenworthtestvector.pdf.

- [Dae17] J. Daemen. Changing of the guards: A simple and efficient method for achieving uniformity in threshold sharing. In Wieland Fischer and Naofumi Homma, editors, Cryptographic Hardware and Embedded Systems - CHES 2017 - 19th International Conference, Taipei, Taiwan, September 25-28, 2017, Proceedings, volume 10529 of Lecture Notes in Computer Science, pages 137-153. Springer, 2017.

- [DFS15] A. Duc, S. Faust, and F.-X. Standaert. Making Masking Security Proofs Concrete, pages 401–429. Springer Berlin Heidelberg, Berlin, Heidelberg, 2015.

- [FGP<sup>+</sup>17] S. Faust, V. Grosso, S. Merino Del Pozo, C. Paglialonga, and F.-X. Standaert. Composable masking schemes in the presence of physical defaults and the robust probing model. Cryptology ePrint Archive, Report 2017/711, 2017. http://eprint.iacr.org/2017/711.

- [GMK16] H. Gross, S. Mangard, and T. Korak. Domain-oriented masking: Compact masked hardware implementations with arbitrary protection order. Cryptology ePrint Archive, Report 2016/486, 2016. http://eprint.iacr.org/2016/ 486.

- [GMO01] Karine Gandolfi, Christophe Mourtel, and Francis Olivier. Electromagnetic analysis: Concrete results. In Çetin K. Koç, David Naccache, and Christof

Paar, editors, Cryptographic Hardware and Embedded Systems-CHES 2001, volume 2162 of LNCS, pages 251–261. Springer Berlin Heidelberg, 2001.

- [GSM17] H. Gross, D. Schaffenrath, and S. Mangard. Higher-order side-channel protected implementations of keccak. In 2017 Euromicro Conference on Digital System Design (DSD), pages 205–212, Aug 2017.

- [ISW03] Y. Ishai, A. Sahai, and D. Wagner. Private Circuits: Securing Hardware against Probing Attacks, pages 463–481. Springer Berlin Heidelberg, Berlin, Heidelberg, 2003.

- [KJJ99] P. C. Kocher, J. Jaffe, and B. Jun. Differential power analysis. In Advances in Cryptology - CRYPTO '99, 19th Annual International Cryptology Conference, Santa Barbara, California, USA, August 15-19, 1999, Proceedings, pages 388–397, 1999.

- [NRR06] S. Nikova, C. Rechberger, and V. Rijmen. Threshold implementations against side-channel attacks and glitches. In ICICS, volume 4307 of LNCS, pages 529-545. Springer, 2006.

- [NRS08] S. Nikova, V. Rijmen, and M. Schlaffer. Secure hardware implementation of non-linear functions in the presence of glitches. In ICISC, volume 5461 of LNCS, pages 218-234. Springer, 2008.

- [NRS11] S. Nikova, V. Rijmen, and M. Schlaffer. Secure hardware implementation of non-linear functions in the presence of glitches. J. Cryptology, 24(2):292-321, 2011.

- [RBN<sup>+</sup>15] O. Reparaz, B. Bilgin, S. Nikova, B. Gierlichs, and I. Verbauwhede. Consolidating Masking Schemes, pages 764–783. Springer Berlin Heidelberg, Berlin, Heidelberg, 2015.

- [Rom14] C. H. Romine. SHA-3 standard: Permutation-based hash and extendable output functions. 2014.

# **A** Appendix

# A.1 Keccak Round Steps

Figure 8: KECCAK-f[200] state and steps [BDPA10b].

# A.2 Second-order Masking

### A.2.1 Threshold Implementation (TI)

| $z_1=a_1\oplus b_1c_1\oplus b_1c_5\oplus b_5c_1$         | $z_2 = a_2 \oplus b_2 c_2 \oplus b_1 c_2 \oplus b_2 c_1$ |     |

|----------------------------------------------------------|----------------------------------------------------------|-----|

| $z_3 = a_3 \oplus b_3 c_3 \oplus b_1 c_3 \oplus b_3 c_1$ | $z_4=a_4\oplus b_4c_4\oplus b_1c_4\oplus b_4c_1$         |     |

| $z_5=a_5\oplus b_5c_5\oplus b_2c_5\oplus b_5c_2$         | $z_6 = b_2 c_3 \oplus b_3 c_2$                           | (9) |

| $z_7 = b_2 c_4 \oplus b_4 c_2$                           | $z_8 = b_3 c_4 \oplus b_4 c_3$                           |     |

| $z_9 = b_3 c_5 \oplus b_5 c_3$                           | $z_{10}=b_4c_5\oplus b_5c_4$                             |     |

### A.2.2 Domain Oriented Masking (DOM)

$$z_{1} = (a_{1}b_{1}) \oplus [a_{1}b_{2} \oplus r_{1}] \oplus [a_{1}b_{3} \oplus r_{2}],$$

$$z_{2} = [a_{2}b_{1} \oplus r_{1}] \oplus (a_{2}b_{2}) \oplus [a_{2}b_{3} \oplus r_{3}],$$

$$z_{3} = [a_{3}b_{1} \oplus r_{2}] \oplus [a_{3}b_{2} \oplus r_{3}] \oplus (a_{3}b_{3}).$$

(10)

# A.3 Non-completeness Failure in Round-Based DOM Implementation

## A.3.1 First Order.

Fig. 10 presents graphically what is demonstrated in Eqn.6 numerically:

Figure 9: First- and second-order threshold implementation with randomness.

## A.3.2 Second Order.

# First bit

$$\begin{split} \chi^{-1} : & S_2^{\chi} \left[ 0, 0, 7 \right] & \to S_2^{\pi} \left[ 0, 0, 7 \right] \oplus S_2^{\pi} \left[ 1, 0, 7 \right] S_2^{\pi} \left[ 2, 0, 7 \right] \\ \pi^{-1} : & S_2^{\pi} \left[ 0, 0, 7 \right] & \to S_2^{\rho} \left[ 0, 0, 7 \right] \\ & S_2^{\pi} \left[ 1, 0, 7 \right] & \to S_2^{\rho} \left[ 1, 1, 7 \right] \\ & S_2^{\pi} \left[ 2, 0, 7 \right] & \to S_2^{\rho} \left[ 2, 2, 7 \right] \\ \rho^{-1} : & S_2^{\rho} \left[ 0, 0, 7 \right] & \to S_2^{\rho} \left[ 0, 0, 7 \right] \\ & S_2^{\rho} \left[ 1, 1, 7 \right] & \to S_2^{\rho} \left[ 1, 1, 3 \right] \\ & S_2^{\rho} \left[ 2, 2, 7 \right] & \to S_2^{\rho} \left[ 2, 2, 4 \right] \\ \theta_1^{-1} : & S_2^{\theta} \left[ 0, 0, 7 \right] & \to S_2 \left[ 0, 0, 7 \right] \oplus \bigoplus_{y'=0}^{4} S_2 \left[ 4, y', 7 \right] \oplus \bigoplus_{y'=0}^{4} S_2 \left[ 1, y', 6 \right] \\ & S_2^{\theta} \left[ 1, 1, 3 \right] & \to S_2 \left[ 1, 1, 3 \right] \oplus \bigoplus_{y'=0}^{4} S_2 \left[ 0, y', 3 \right] \oplus \sum_{y'=0}^{4} S_2 \left[ 2, y', 2 \right] \\ & S_2^{\theta} \left[ 2, 2, 4 \right] & \to S_2 \left[ 2, 2, 4 \right] \oplus \bigoplus_{y'=0}^{4} S_2 \left[ 1, y', 4 \right] \oplus \sum_{y'=0}^{4} S_2 \left[ 3, y', 3 \right] \end{split}$$

Figure 10: Tracing back output bit  $C^{\chi}[4, 1, 0]$ .

# Second bit

| $\chi^{-1}$ :     | $S_{6}^{\chi}[2,0,5]$              | $\rightarrow S_1^{\pi} [4, 0, 5] S_3^{\pi} [3, 0, 5]$                                                                                      |

|-------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| $\pi^{-1}$ :      | 1                                  | $ \to S_1^{\rho} [4, 4, 5] $<br>$ \to S_3^{\rho} [3, 3, 5] $                                                                               |

| $\rho^{-1}$ :     | -                                  | $ ightarrow S_1^{	heta} [4, 4, 7]  ightarrow S_3^{	heta} [3, 3, 0]$                                                                        |

| $\theta_1^{-1}$ : | $S_{1}^{\theta}\left[4,4,7\right]$ | $ ightarrow S_1\left[4,4,7 ight] \oplus igoplus_{y'=0}^4 S_1\left[3,y',7 ight] \oplus igoplus_{y'=0}^4 S_1\left[0,y',6 ight]$              |

|                   | $S_{3}^{\theta}\left[3,3,0\right]$ | $\rightarrow S_{3}\left[3,3,0\right] \oplus \bigoplus_{y'=0}^{4} S_{3}\left[2,y',0\right] \oplus \sum_{y'=0}^{4} S_{3}\left[4,y',7\right]$ |