# Sapphire: A Configurable Crypto-Processor for Post-Quantum Lattice-based Protocols (Extended Version)

Utsav Banerjee, Tenzin S. Ukyab and Anantha P. Chandrakasan

Massachusetts Institute of Technology, Cambridge, MA, USA

Abstract. Public key cryptography protocols, such as RSA and elliptic curve cryptography, will be rendered insecure by Shor's algorithm when large-scale quantum computers are built. Cryptographers are working on quantum-resistant algorithms, and lattice-based cryptography has emerged as a prime candidate. However, high computational complexity of these algorithms makes it challenging to implement lattice-based protocols on low-power embedded devices. To address this challenge, we present Sapphire - a lattice cryptography processor with configurable parameters. Efficient sampling, with a SHA-3-based PRNG, provides two orders of magnitude energy savings; a single-port RAM-based number theoretic transform memory architecture is proposed, which provides 124k-gate area savings; while a low-power modular arithmetic unit accelerates polynomial computations. Our test chip was fabricated in TSMC 40nm low-power CMOS process, with the Sapphire cryptographic core occupying 0.28 mm<sup>2</sup> area consisting of 106k logic gates and 40.25 KB SRAM. Sapphire can be programmed with custom instructions for polynomial arithmetic and sampling, and it is coupled with a low-power RISC-V micro-processor to demonstrate NIST Round 2 lattice-based CCA-secure key encapsulation and signature protocols Frodo, NewHope, qTESLA, CRYSTALS-Kyber and CRYSTALS-Dilithium, achieving up to an order of magnitude improvement in performance and energy-efficiency compared to state-of-the-art hardware implementations. All key building blocks of Sapphire are constant-time and secure against timing and simple power analysis side-channel attacks. We also discuss how masking-based DPA countermeasures can be implemented on the Sapphire core without any changes to the hardware.

$\label{eq:Keywords: Lattice-based Cryptography LWE · Ring-LWE · Module-LWE · post-quantum · NIST Round 2 · Number Theoretic Transform · Sampling · energy-efficient · low-power · constant-time · side-channel security · ASIC · hardware implementation$

## 1 Introduction

Modern public key cryptography relies on hard mathematical problems such as integer factorization, discrete logarithms over finite fields and discrete logarithms over elliptic curve groups. However, these problems can be solved by a large-scale quantum computer in polynomial time using Shor's algorithm [Sho97], thus making today's public key protocols like RSA and ECC vulnerable to quantum attacks. Given the rapid advancement in quantum computing technology over the past few years, cryptographers are developing quantum-secure public key algorithms to protect today's data from tomorrow's threats. Lattice-based cryptography is considered one of the most promising candidates for post-quantum cryptographic protocols because of its extensive security analysis as well as small public key and signature sizes.

The National Institute of Standards and Technology (NIST) formally initiated the process of standardizing post-quantum cryptography in 2016 [CJL<sup>+</sup>16]. The first round of candidates were announced in late 2017, with lattice-based cryptography accounting for 48% of the public-key encryption and key encapsulation (PKE/KEM) schemes and 25% of the signature schemes. In early 2019, the candidates moving on to the second round were announced [AAA<sup>+</sup>19], and lattice-based cryptography accounts for 53% (9 out of 17) and 33% (3 out of 9) of the candidates for PKE/KEM and signature schemes respectively. The theoretical foundation of several of these lattice-based protocols lies in the *learning with errors* (LWE) problem [Reg05] and its variants such as Ring-LWE [LPR13] and Module-LWE [LS15], and the hardness of LWE has been well-studied in the presence of both classical

and quantum adversaries [BLP<sup>+</sup>13, Reg04]. This has been accompanied by several software and hardware implementations [RVM<sup>+</sup>14, dRVV15, AJS16, KLC<sup>+</sup>17, OG17, NDBC18, BFM<sup>+</sup>18, HOKG18, STCZ18, AHH<sup>+</sup>18, LZL<sup>+</sup>19, BSNK19] of LWE and Ring-LWE-based public key encryption and key encapsulation protocols, each supporting specific lattice parameters chosen for increased performance and efficiency. Existing lattice-based cryptography implementations, both in software and hardware, have been thoroughly surveyed in [NDR<sup>+</sup>19]. Most of the hardware implementations focus on FPGA demonstration in order to support reconfigurability of lattice parameters, which is especially important for a fast evolving field like lattice-based cryptography, while existing ASIC implementations either lack configurability or have power and area overheads. Some of the key challenges of implementing lattice-based cryptography in ASICs have been discussed in [OGV<sup>+</sup>16], and this work presents a solution using a combination of architectural and algorithmic techniques.

Our contributions: In this work, we present Sapphire – a configurable lattice cryptography processor – which combines low-power modular arithmetic, area-efficient memory architecture and fast sampling techniques to achieve high energy-efficiency and low cycle count, ideal for securing low-power embedded systems. The key technical aspects of our work are as follows:

- 1. A low-power modular arithmetic core, with configurable prime modulus, is used to accelerate polynomial arithmetic operations; a pseudo-configurable modular multiplier is also implemented, which provides up to  $3\times$  improvement in energy-efficiency.

- 2. A single-port SRAM-based number theoretic transform (NTT) memory architecture provides 124k-gate area savings without any loss in performance or energy-efficiency.

- 3. An efficient Keccak core is combined with fast sampling techniques to speed up polynomial sampling, while supporting a wide variety of discrete distribution parameters.

- 4. These efficient hardware building blocks are integrated together with an instruction memory and decoder to build our crypto-processor, which can be programmed with custom instructions for polynomial sampling and arithmetic.

- 5. The Sapphire crypto-processor is coupled with an efficient RISC-V micro-processor to demonstrate several NIST Round 2 lattice-based key encapsulation and signature protocols such as Frodo [NAB+19], NewHope [PAA+19], qTESLA [BAA+19], CRYSTALS-Kyber [SAB+19] and CRYSTALS-Dilithium [LDK+19], achieving more than an order of magnitude improvement in performance and energy-efficiency compared to state-of-the-art assembly-optimized software and hardware implementations.

- 6. All the key building blocks, such as NTT, polynomial arithmetic and binomial sampling, are constant-time and secure against timing and simple power analysis attacks. While our baseline protocol implementations are not secure against differential power analysis attacks, we discuss how our crypto-processor can be programmed to implement masking-based countermeasures.

- 7. Our ASIC implementation was fabricated in the TSMC 40nm low-power CMOS process, and all protocol-level demonstrations and side-channel measurements were conducted on our test chip.

The rest of the paper is organized as follows: Section 2 provides a brief mathematical background on LWE and associated computations; in Section 3, we present our implementation of energy-efficient modular arithmetic along with an area-efficient NTT memory architecture; in Section 4, we describe our discrete distribution sampler accelerated by a low-power SHA-3 core; Section 5 describes the overall chip architecture; Section 6 presents detailed measurement results obtained from evaluating lattice-based protocols on our test chip, comparison with state-of-the-art software and hardware implementations as well as side-channel analysis; a summary of our key conclusions along with future research directions are discussed in Section 7.

This is an extended version of our CHES paper [BUC19] with additional design information, implementation of Frodo-1344 and preliminary side-channel leakage analysis. Also, several appendices have been added at the end of the paper to provide supplementary data.

# 2 Background

In this section, we provide a brief introduction to LWE, Ring-LWE and Module-LWE along with the associated computations. We use bold lower-case symbols to denote vectors and bold upper-case symbols to denote matrices. The symbol lg is used to denote all logarithms with base 2. The set of all integers is denoted as  $\mathbb{Z}$  and the quotient ring of integers modulo q is denoted as  $\mathbb{Z}_q$ . For two n-dimensional vectors  $\boldsymbol{a}$  and  $\boldsymbol{b}$ , their inner product is written as  $\langle \boldsymbol{a}, \boldsymbol{b} \rangle = \sum_{i=0}^{n-1} a_i \cdot b_i$ . The concatenation of two vectors  $\boldsymbol{a}$  and  $\boldsymbol{b}$  is written as  $\boldsymbol{a} \parallel \boldsymbol{b}$ .

#### 2.1 LWE and Related Lattice Problems

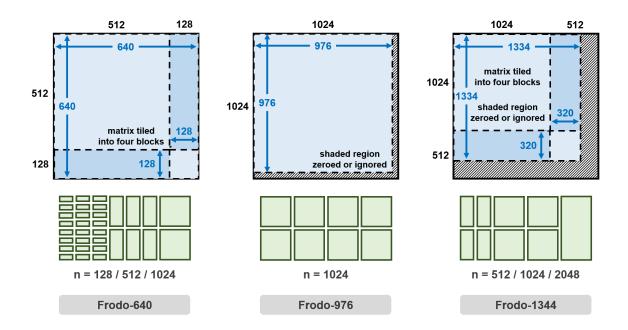

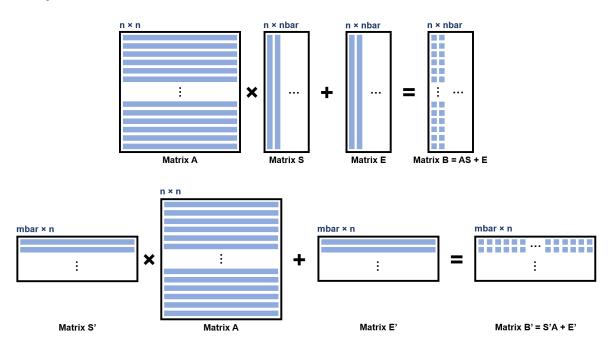

The Learning with Errors (LWE) problem [Reg05] acts as the foundation for several modern lattice-based cryptography schemes. The LWE problem states that given a polynomial number of samples of the form  $(\boldsymbol{a}, \langle \boldsymbol{a}, \boldsymbol{s} \rangle + e)$ , it is difficult to determine secret vector  $\boldsymbol{s} \in \mathbb{Z}_q^n$ , where vector  $\boldsymbol{a} \in \mathbb{Z}_q^n$  is sampled uniformly at random and error e is sampled from the appropriate error distribution  $\chi$ . Examples of secure LWE parameters are  $(n, q) = (640, 2^{15})$ ,  $(n, q) = (976, 2^{16})$  and  $(n, q) = (1344, 2^{16})$  for Frodo [NAB+19].

LWE-based cryptosystems involve large matrix operations which are computationally expensive and also result in large key sizes. To solve this problem, the Ring-LWE problem [LPR13] was proposed, which uses ideal lattices. Let  $\mathcal{R}_q = \mathbb{Z}_q[x]/(x^n+1)$  be the ring of polynomials where n is power of 2. The Ring-LWE problem states that given samples of the form  $(a, a \cdot s + e)$ , it is difficult to determine the secret polynomial  $s \in \mathcal{R}_q$ , where the polynomial  $a \in \mathcal{R}_q$  is sampled uniformly at random and the coefficients of the error polynomial e are small samples from the error distribution  $\chi$ . Examples of secure Ring-LWE parameters are (n,q) = (512,12289) and (n,q) = (1024,12289) for NewHope [PAA+19].

Module-LWE [LS15] provides a middle ground between LWE and Ring-LWE. By using module lattices, it reduces the algebraic structure present in Ring-LWE and increases security while not compromising too much on the computational efficiency. The Module-LWE problem states that given samples of the form  $(\boldsymbol{a}, \boldsymbol{a}^T \boldsymbol{s} + e)$ , it is difficult to determine the secret vector  $\boldsymbol{s} \in \mathcal{R}_q^k$ , where the vector  $\boldsymbol{a} \in \mathcal{R}_q^k$  is sampled uniformly at random and the coefficients of the error polynomial e are small samples from the error distribution  $\chi$ . Examples of secure Module-LWE parameters are (n, k, q) = (256, 2, 7681), (n, k, q) = (256, 3, 7681) and (n, k, q) = (256, 4, 7681) for CRYSTALS-Kyber [SAB+19].

## 2.2 Number Theoretic Transform

While the protocols based on standard lattices (LWE) involve matrix-vector operations modulo q, all the arithmetic is performed in the ring of polynomials  $\mathcal{R}_q = \mathbb{Z}_q[x]/(x^n+1)$  when working with ideal and module lattices. There are several efficient algorithms for polynomial multiplication [Ber08b], and the Number Theoretic Transform (NTT) is one such technique widely used in lattice-based cryptography.

The NTT is a generalization of the well-known Fast Fourier Transform (FFT) where all the arithmetic is performed in a finite field instead of complex numbers. Instead of working with powers of the n-th complex root of unity  $\exp(-2\pi j/n)$ , NTT uses the n-th primitive root of unity  $\omega_n$  in the ring  $\mathbb{Z}_q$ , that is,  $\omega_n$  is an element in  $\mathbb{Z}_q$  such that  $\omega_n^n = 1 \mod q$  and  $\omega_n^i \neq 1 \mod q$  for  $i \neq n$ . In order to have elements of order n, the modulus q is chosen to be a prime such that  $q \equiv 1 \mod n$ . A polynomial  $a(x) \in \mathcal{R}_q$  with coefficients  $a(x) = (a_0, a_1, \cdots, a_{n-1})$  has the NTT representation  $\hat{a}(x) = (\hat{a_0}, \hat{a_1}, \cdots, \hat{a_{n-1}})$ , where

$$\hat{a_i} = \sum_{j=0}^{n-1} a_j \omega_n^{ij} \bmod q \ \forall \ i \in [0, n-1]$$

The inverse NTT (INTT) operation converts  $\hat{a}(x) = (\hat{a_0}, \hat{a_1}, \dots, \hat{a_{n-1}})$  back to a(x) as

$$a_i = \frac{1}{n} \sum_{i=0}^{n-1} \hat{a_j} \omega_n^{-ij} \mod q \ \forall i \in [0, n-1]$$

Note that the INTT operation is similar to NTT, except that  $\omega_n$  is replaced by  $\omega_n^{-1} \mod q$  and the final results is divided by n. An iterative in-place version of the NTT algorithm is provided in Algorithm 1 [CLRS09, DB16]. The PolyBitRev function performs a permutation on the input polynomial a such that  $\hat{a}[i] = \text{PolyBitRev}(a)[i] = a[\text{BitRev}(i)]$ , where BitRev is formally defined as

#### Algorithm 1 Iterative In-Place NTT [CLRS09]

```

Require: Polynomial a(x) \in \mathcal{R}_q and n-th primitive root of unity \omega_n \in \mathbb{Z}_q

Ensure: Polynomial \hat{a}(x) \in \mathcal{R}_q such that \hat{a}(x) = \text{NTT}(a(x))

1: \hat{a} \leftarrow \text{PolyBitRev}(a)

2: for (s = 1; s \le \lg n; s = s + 1) do

m \leftarrow 2^s

\omega_m \leftarrow \omega_n^{n/m}

4:

for (k = 0; k < n; k = k + m) do

5:

6:

for (j = 0; j < m/2; j = j + 1) do

7:

8:

t \leftarrow \omega \cdot \hat{a}[k+j+m/2] \mod q

u \leftarrow \hat{a}[k+j]

9:

\hat{a}[k+j] \leftarrow u + t \mod q

10:

\hat{a}[k+j+m/2] \leftarrow u-t \bmod q

11:

\omega \leftarrow \omega \cdot \omega_m \bmod q

12:

end for

13:

14:

end for

15: end for

16: return \hat{a}

```

BitRev $(i) = \sum_{j=0}^{\lg n-1} (((i \gg j) \& 1) \ll (\lg n - 1 - i))$  (for positive integer i and power-of-two n), that is, bit-wise reversal of the binary representation of the index i. Since there are  $\lg n$  stages in the NTT outer loop, with O(n) operations in each stage, its time complexity is  $O(n \lg n)$ . The factors  $\omega$  are called the twiddle factors, similar to FFT.

The NTT provides a fast multiplication algorithm in  $\mathcal{R}_q$  with time complexity  $O(n \lg n)$  instead of  $O(n^2)$  for schoolbook multiplication. Given two polynomials  $a, b \in \mathcal{R}_q$ , their product  $c = a \cdot b \in \mathcal{R}_q$  can be computed as

```

c = INTT (NTT(a) \odot NTT(b))

```

where  $\odot$  denotes coefficient-wise multiplication of the polynomials. Since the product of a and b, before reduction modulo  $f(x) = x^n + 1$ , has 2n coefficients, using the above equation directly to compute  $a \cdot b$  will require padding both a and b with n zeros. To eliminate this overhead, the negative-wrapped convolution [How12] is used, with the additional requirement  $q \equiv 1 \mod 2n$  so that both the n-th and 2n-th primitive roots of unity modulo q exist, respectively denoted as  $\omega_n$  and  $\psi = \sqrt{\omega_n} \mod q$ . By multiplying a and b coefficient-wise by powers of  $\psi$  before the NTT computation, and by multiplying INTT(NTT(a)  $\odot$  NTT(b)) coefficient-wise by powers of  $\psi^{-1} \mod q$ , no zero padding is required and the n-point NTT can be used directly.

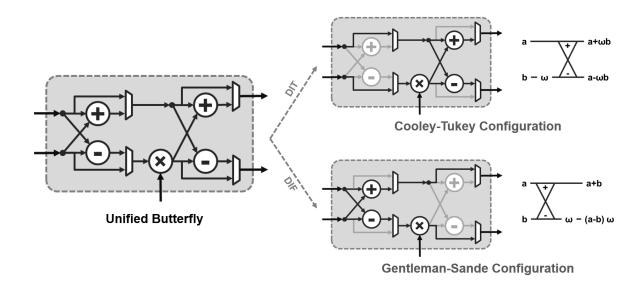

Similar to FFT, the NTT inner loop involves butterfly computations. There are two types of butterfly operations – Cooley-Tukey (CT) and Gentleman-Sande (GS) [LN16]. The CT butterfly-based NTT requires inputs in normal order and generates outputs in bit-reversed order, similar to the *decimation-in-time* FFT. The GS butterfly-based NTT requires inputs to be in bit-reversed order while the outputs are generated in normal order, similar to the *decimation-in-frequency* FFT. Using the same butterfly for both NTT and INTT requires a bit-reversal permutation. However, the bit-reversal can be avoided by using CT for NTT and GS for INTT [LN16].

#### 2.3 Sampling

In lattice-based protocols, the public vectors  $\boldsymbol{a}$  are generated from the uniform distribution over  $\mathbb{Z}_q$  through rejection sampling. The secret vectors  $\boldsymbol{s}$  and error terms e are sampled from the distribution  $\chi$  typically with zero mean and appropriate standard deviation  $\sigma$ . Accurate sampling of  $\boldsymbol{s}$  and e is critical to the security of these protocols, and the sampling must be constant-time to prevent side-channel leakage of the secret information. Although the original LWE proof used discrete Gaussian distributions for sampling the error terms, several lattice-based schemes use binomial, uniform and ternary distributions for efficiency. A detailed survey of different sampling techniques is available in [NDR+19].

# 3 Modular Arithmetic and NTT

The core arithmetic and logic unit (ALU) of Sapphire consists of a 24-bit data-path, with modular operations in  $\mathbb{F}_q$  for configurable q. In this section, we describe the details of our energy-efficient modular arithmetic implementation, the ALU design and our area-efficient NTT memory architecture.

#### 3.1 Modular Arithmetic Implementation

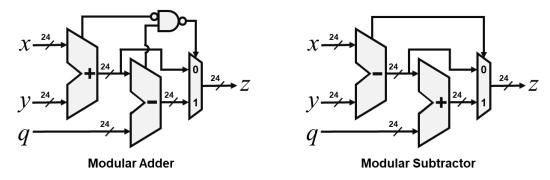

The modular arithmetic core consists of a 24-bit adder, a 24-bit subtractor and a 24-bit multiplier along with associated modular reduction logic. Our modular adder and subtractor designs are shown in Fig. 1, and the corresponding pseudo-codes are shown in Algorithms 2 and 3. Both designs use a pair of adder and subtractor, with the sum, carry bit, difference and borrow bit denoted as s, c, d and b respectively. Modular reduction is performed using conditional subtraction and addition, which are computed in the same cycle to avoid timing side-channels. The synthesized areas of the adder and the subtractor are around 550 GE (gate equivalent) each in area.

For modular multiplication, we use a 24-bit multiplier followed by Barrett reduction [Bar86] modulo a prime q of size up to 24 bits. Barrett reduction does not exploit any special property of the modulus q, thus making it ideal for supporting configurable moduli. Let z be the 48-bit product to be reduced to  $\mathbb{Z}_q$ , then Barrett reduction computes  $z \mod q$  by estimating the quotient  $\lfloor z/q \rfloor$  without performing any division, as shown in Algorithm 4. Barrett reduction involves two multiplications, one subtraction, one bit-shift and one conditional subtraction. The value of 1/q is approximated as  $m/2^k$ , with the error of approximation being  $e = 1/q - m/2^k$ , therefore the reduction is valid as long as ze < 1. Since  $z < q^2$ , k is set to be the smallest number such that  $e = 1/q - (\lfloor 2^k/q \rfloor/2^k) < 1/q^2$ . Typically, k is very close to  $2 \lceil \lg q \rceil$ , that is, the bit-size of  $q^2$ .

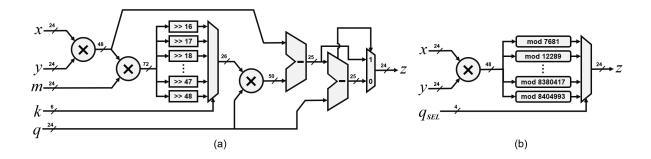

In order to understand the trade-offs between flexibility and efficiency in modular multiplication, we have implemented two different architectures of Barrett reduction logic: (1) with fully configurable modulus (q can be an arbitrary prime) and (2) with pseudo-configurable modulus (q belongs to a specific set of primes), as shown in Fig. 2.

Apart from the prime q (which can be up to 24 bits), the fully configurable version requires two

Figure 1: Design of our modular adder and subtractor with configurable modulus q.

```

Algorithm 2 Modular Addition

Algorithm 3 Modular Subtraction

\overline{\mathbf{Require:}}\ x,y\in\mathbb{Z}_q

\overline{\mathbf{Require:}} \ x, y \in \mathbb{Z}_q

Ensure: z = x + y \mod q

Ensure: z = x - y \mod q

1: (c,s) \leftarrow x + y

1: (b,d) \leftarrow x - y

2: (b,d) \leftarrow s - q

2: (c,s) \leftarrow d+q

3: if c = 1 or b = 0 then

3: if b = 1 then

4:

z \leftarrow d

z \leftarrow s

5: else

5: else

z \leftarrow s

z \leftarrow d

7: end if

7: end if

8: return z

8: return z

```

#### Algorithm 4 Modular Multiplication with Barrett Reduction [Bar86]

```

Require: x, y \in \mathbb{Z}_q, m and k such that m = \lfloor 2^k/q \rfloor

Ensure: z = x \cdot y \mod q

1: z \leftarrow x \cdot y

2: t \leftarrow (z \cdot m) \gg k

3: z \leftarrow z - (t \cdot q)

4: if z \geq q then

5: z \leftarrow z - q

6: end if

7: return z

```

**Figure 2:** Two different single-cycle modular multiplier architectures with (a) fully configurable and (b) pseudo-configurable modulus for Barrett reduction.

additional inputs m and k such that  $m = \lfloor 2^k/q \rfloor$  (m and k are allowed to be up to 24 bits and 6 bits respectively). It consists of total 3 multipliers, as shown in Fig. 2a, the first two being used to compute  $z = x \cdot y$  and  $z \cdot m$  respectively. For obtaining  $t = (z \cdot m) \gg k$ , the bit-wise shift is implemented purely using combinational logic (multiplexers) because shifting bits sequentially in registers can be extremely inefficient in terms of power consumption. We assume that  $16 \le k \le 48$  since q is not larger than 24 bits, q is typically not smaller than 8 bits and we know that  $k \approx 2 \lceil \lg q \rceil$ . The third multiplier is used to compute  $t \cdot q$ , and a pair of subtractors is used to calculate  $z - (t \cdot q)$  and perform the final reduction step. All the steps are computed in a single cycle to avoid any potential timing side-channels. The design was synthesized at 100 MHz (with near-zero slack) and occupies around 11k GE area, which includes the area (around 4k GE) of the 24-bit multiplier used to compute  $z = x \cdot y$ .

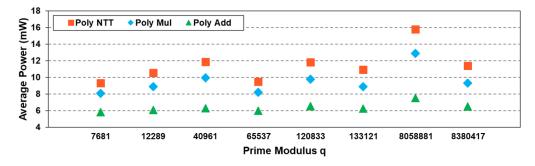

The pseudo-configurable modular multiplier implements Barrett reduction logic for the following primes used by NIST Round 1 lattice-based candidates: 7681 (CRYSTALS-Kyber) [SAB+19], 12289 (NewHope) [PAA+19], 40961 (R.EMBLEM) [SPL+17], 65537 (pqNTRUSign) [CHWZ17], 120833 (Ding Key Exchange) [DTGW17], 133121 / 184321 (LIMA) [ALO+17], 8380417 (CRYSTALS-Dilithium) [LDK+19], 8058881 (qTESLA v1.0) and 4205569 / 4206593 / 8404993 (qTESLA v2.0) [BAA+19]. As shown in Fig. 2b, there is dedicated reduction block for each of these primes, and the  $q_{SEL}$  input is

```

Algorithm 5 Reduction mod 7681

Require: q = 7681, x \in [0, q^2)

Ensure: z = x \mod q

1: t \leftarrow (x \ll 8) + (x \ll 4) + x

2: t \leftarrow t \gg 21

3: t \leftarrow (t \ll 13) - (t \ll 9) + t

4: z \leftarrow x - t

5: if z \ge q then

6: z \leftarrow z - q

7: end if

8: return z

```

```

Algorithm 6 Reduction mod 8380417

Require: q = 8380417, x \in [0, q^2)

Ensure: z = x \mod q

1: t \leftarrow (x \ll 23) + (x \ll 13) + (x \ll 3) - x

2: t \leftarrow t \gg 46

3: t \leftarrow (t \ll 23) - (t \ll 13) + t

4: z \leftarrow x - t

5: if z \ge q then

6: z \leftarrow z - q

7: end if

8: return z

```

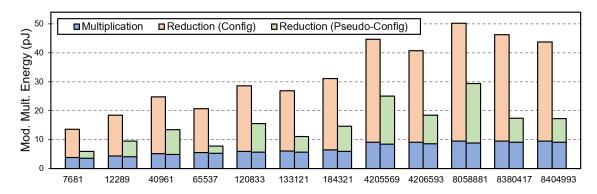

Figure 3: Comparison of modular multiplication energy for the two reduction architectures.

used to select the output of the appropriate block while the inputs to the other blocks are data-gated to save power. Since the reduction blocks have the parameters m, k and q coded in digital logic and do not require explicit multipliers, they involve lesser computation than the fully configurable reduction circuit from Fig. 2a, albeit at the cost of some additional area and decrease in flexibility. The reduction becomes particularly efficient when at least one of m and q or both can be written in the form  $2^{l_1} \pm 2^{l_2} \pm \cdots \pm 1$ , where  $l_1, l_2, \cdots$  are not more than four positive integers. For example, we consider the CRYSTALS primes: for  $q = 7681 = 2^{13} - 2^9 + 1$  we have k = 21 and  $m = 273 = 2^8 + 2^4 + 1$ , and for  $q = 8380417 = 2^{23} - 2^{13} + 1$  we have k = 46 and  $m = 8396807 = 2^{23} + 2^{13} + 2^3 - 1$ . Therefore, the multiplications by q and m can be converted to significantly cheaper bit-shifts and additions / subtractions, as shown in Algorithms 5 and 6. Implementation details and reduction parameters for each customized modular reduction block are provided in Appendix A. This design also performs modular multiplication in a single cycle. It was synthesized at 100 MHz (with near-zero slack) and occupies around 19k GE area, including the area of the 24-bit multiplier.

In Fig. 3, we compare the simulated energy consumption of the fully configurable and pseudo-configurable modular multiplier architectures for all the primes mentioned earlier. As expected, the multiplication itself consumes the same energy in both cases, but the modular reduction energy is up to  $6\times$  lower for the pseudo-configurable design. The overall decrease in modular multiplication energy, considering both multiplication and reduction together, is up to  $3\times$ , clearly highlighting the benefit of the dedicated modular reduction data-paths when working with prime moduli. For reduction modulo  $2^m$  (m < 24), e.g., in the case of Frodo, the output of the 24-bit multiplier is simply bit-wise AND-ed with  $2^m - 1$  implying that the modular reduction energy is negligible.

#### 3.2 Butterfly Unit and ALU

Next, we elaborate how the modular arithmetic units described earlier are integrated together to build the butterfly module. As discussed in Section 2, NTT computations involve butterfly operations similar to the Fast Fourier Transform, with the only difference being that all arithmetic is performed modulo q instead of complex numbers. There are two butterfly configurations – Cooley-Tukey (or DIT) and Gentleman-Sande (or DIF). In terms of arithmetic, the DIT butterfly computes  $(a + \omega b \mod q, a - \omega b \mod q)$  and the DIF butterfly computes  $(a + b \mod q, (a - b)\omega \mod q)$ , where a and b are the inputs to the butterfly and  $\omega$  is the twiddle factor. The DIT butterfly requires inputs to be in bit-reversed order and the DIF butterfly generates outputs in bit-reversed order, thus making DIF and DIT suitable for NTT and INTT respectively. While software implementations have the flexibility to program both configurations, hardware designs typically implement either DIT or DIF, thus requiring bit-reversals. To solve this problem, we have implemented a unified butterfly architecture [BPC19] which can be configured as both DIT and DIF, as shown in Fig. 4. It consists of two sets of modular adders and subtractors along with some multiplexing circuitry to select whether the multiplication with  $\omega$  is performed before or after the addition and subtraction. Since the critical path of the design is inside the modular multiplier, there is no impact on system performance. The associated area overhead is also negligible.

The modular arithmetic blocks inside the butterfly are re-used for coefficient-wise polynomial arithmetic operations as well as for multiplying polynomials with the appropriate powers of  $\psi$  and  $\psi^{-1}$

Figure 4: Unified butterfly in Cooley-Tukey and Gentleman-Sande configurations.

during negative-wrapped convolution. Apart from butterfly and arithmetic modulo q, the Sapphire ALU also supports the following bit-wise operations – AND, OR, XOR, left shift and right shift.

#### 3.3 NTT Memory Architecture

Hardware architectures for polynomial multiplication using NTT consist of memory banks for storing the polynomials along with the ALU which performs butterfly computations. Since each butterfly needs to read two inputs and write two outputs all in the same cycle, these memory banks are typically implemented using dual-port RAMs [RVM+14, CMV+15, DB16, LZL+19] or four-port RAMs [STCZ18]. Although true dual-port memory is easily available in state-of-the-art commercial FPGAs in the form of block RAMs (BRAMs), use of dual-port SRAMs in ASIC can pose large area overheads in resource-constrained devices. Compared to a simple single-port SRAM, a dual-port SRAM has double the number of row and column decoders, write drivers and read sense amplifiers. Also, the bit-cells in a low-power dual-port SRAM consist of ten transistors (10T) compared to the usual six transistor (6T) bit-cells in a single-port SRAM [NOI+08]. Therefore, the area of a dual-port SRAM can be as much as double the area of a single-port SRAM with the same number of bits and column muxing. To reduce this area overhead, we implement an area-efficient NTT memory architecture [BPC19] which uses the constant-geometry FFT data-flow [Pea68] and consists of single-port SRAMs only.

#### Algorithm 7 Constant Geometry Out-of-Place NTT [Pol71]

```

Require: Polynomial a(x) \in \mathcal{R}_q and n-th primitive root of unity \omega_n \in \mathbb{Z}_q

Ensure: Polynomial \hat{a}(x) \in \mathcal{R}_q such that \hat{a}(x) = \text{NTT}(a(x))

1: a \leftarrow \text{PolyBitRev}(a)

2: for (s = 1; s \le \lg n; s = s + 1) do

for (j = 0; j < n/2; j = j + 1) do

3:

k \leftarrow |j/2^{\lg{(n-s)}}| \cdot 2^{\lg{(n-s)}}

4:

\hat{a}[j] \leftarrow a[2j] + a[2j+1] \cdot \omega_n^k \bmod q

5:

\hat{a}[j+n/2] \leftarrow a[2j] - a[2j+1] \cdot \omega_n^k \bmod q

6:

end for

7:

if s \neq \lg n then

8:

a \leftarrow \hat{a}

9:

end if

11: end for

12: return \hat{a}

```

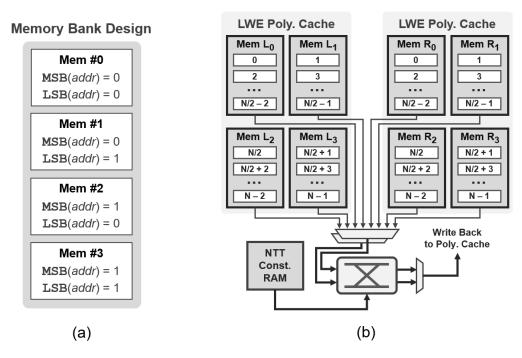

**Figure 5:** (a) Memory bank construction using single-port SRAMs and (b) proposed area-efficient NTT architecture using two such memory banks.

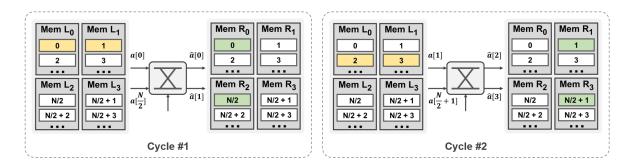

**Figure 6:** Data-flow of our NTT memory architecture in the first two cycles (butterfly inputs are in yellow and outputs are in green).

The constant geometry NTT is described in Algorithm 7 [Pol71, CMV<sup>+</sup>15]. Clearly, the coefficients of the polynomial are accessed in the same order for each stage, thus simplifying the read/write control circuitry. For constant geometry DIT NTT, the butterfly inputs are a[2j] and a[2j+1] and the outputs are  $\hat{a}[j]$  and  $\hat{a}[j+n/2]$ , while the inputs are a[j] and a[j+n/2] and the outputs are  $\hat{a}[2j]$  and  $\hat{a}[2j+1]$  for DIF NTT. However, the constant geometry NTT is inherently out-of-place, therefore requiring storage for both polynomials a and  $\hat{a}$ . For our hardware implementation, we create two memory banks – left and right – to store these two polynomials while allowing the butterfly inputs and outputs to ping-pong between them during each stage of the transform. Although out-of-place NTT requires storage for both the input and output polynomials, this does not affect the total memory requirements of the crypto-processor because the total number of polynomials required to be stored during the protocol execution is greater than two, e.g., four polynomials are involved in any computation of the form  $b=a\cdot s+e$ .

Next, we describe how these memory banks are constructed using single-port SRAMs so that each butterfly can be computed in a single cycle without causing read/write hazards. As shown in Fig. 5a, each polynomial is split among four single port SRAMs  $Mem\ 0-3$  on the basis of the least and most significant bits (LSB and MSB) of the coefficient index (or address addr). This allows simultaneously

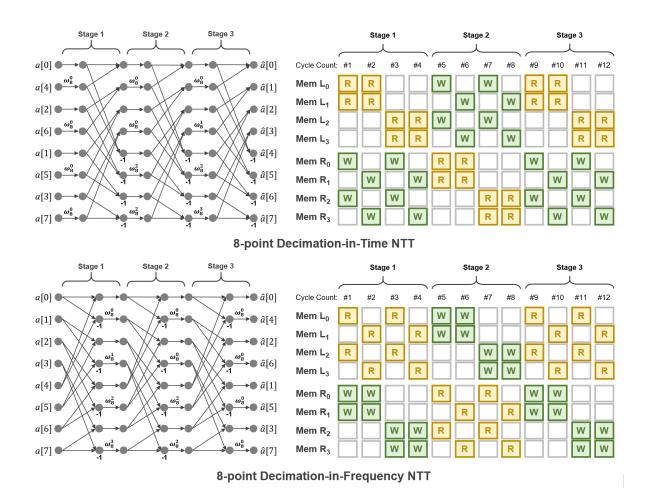

**Figure 7:** Memory access patterns for 8-point DIT and DIF NTT using our single-port SRAM-based memory architecture (R and W denote read and write respectively).

accessing coefficient index pairs of the form (2j, 2j + 1) and (j, j + n/2). Our NTT memory architecture is shown in Fig. 5b, which consists of two such memory banks labelled as  $LWE\ Poly\ Cache$ . In every cycle, the butterfly inputs are read from two different single-port SRAMs (out of four SRAMs in the input memory bank) and the outputs are also written to two different single-port SRAMs (out of four SRAMs in the output memory bank), thus avoiding hazards. The data flow in the first two cycles of NTT is shown in Fig. 6, where the input polynomial a is stored in the left bank and the output polynomial  $\hat{a}$  is stored in the right bank. As the input and output polynomials exchange their memory banks from one stage to the next, our NTT control circuitry ensures that the same data-flow is maintained. To illustrate this, the memory access patterns for all three stages of an 8-point NTT are shown in Fig. 7 for both decimation-in-time and decimation-in-frequency.

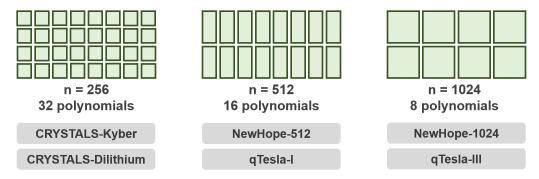

The two memory banks consist of four  $1024 \times 24$ -bit single-port SRAMs each (24 KB total). Together they store 8192 entries, which can be split into four 2048-dimension polynomials or eight 1024-dimension polynomials or sixteen 512-dimension polynomials or thirty-two 256-dimension polynomials or sixty-four 128-dimension polynomials or one-hundred-twenty-eight 64-dimension polynomials. By constructing this memory using single-port SRAMs (and some additional read-data multiplexing circuitry), we have achieved area savings equivalent to 124k GE compared to a dual-port SRAM-based implementation. This is particularly important since SRAMs account for a large portion of the total hardware area in ASIC implementations of lattice-based cryptography [STCZ18, FS19].

In order to allow configurable parameters, our NTT hardware also requires additional storage (labelled as NTT Constants RAM in Fig. 5) for the pre-computed twiddle factors:  $\omega_{2^i}^j$ ,  $\omega_{2^i}^{-j} \mod q$  for  $i \in [1, \lg n]$  and  $j \in [0, 2^{i-1})$  and  $\psi^i$ ,  $n^{-1}\psi^{-i} \mod q$  for  $i \in [0, n)$ . Since  $n \leq 2048$  and  $q < 2^{24}$ , this would require another 24 KB of memory. To reduce this overhead, we exploit the following properties of  $\omega$  and  $\psi$ :

| Design                         | Platform         | Tech<br>(nm) | VDD<br>(V) | Freq<br>(MHz) | Parameters                                                           | NTT<br>Cycles              | NTT<br>Energy                        |

|--------------------------------|------------------|--------------|------------|---------------|----------------------------------------------------------------------|----------------------------|--------------------------------------|

| This work                      | ASIC             | 40           | 1.1        | 72            | (n = 256, q = 7681)<br>(n = 512, q = 12289)<br>(n = 1024, q = 12289) | 1,289<br>2,826<br>6,155    | 165.98 nJ<br>410.52 nJ<br>894.28 nJ  |

| Software<br>[KRSS18]           | ARM<br>Cortex-M4 | -            | 3.0        | 100           | (n = 256, q = 7681)<br>(n = 512, q = 12289)<br>(n = 1024, q = 12289) | 22,031<br>34,262<br>75,006 | 13.55 μJ<br>21.07 μJ<br>46.13 μJ     |

| Song et al.<br>[STCZ18]        | ASIC             | 40           | 0.9        | 300           | (n = 256, q = 7681)<br>(n = 512, q = 12289)                          | 160<br>492                 | 31 nJ<br>96 nJ                       |

| Nejatollahi et al.<br>[NDBC18] | ASIC             | 45           | 1.0        | 100           | (n = 512, q = 12289)                                                 | 2,854<br>11,053            | 1016.02 nJ<br>596.86 nJ              |

| Fritzmann et al.<br>[FS19]     | ASIC             | 65           | 1.2        | 25            | (n = 256, q = 7681)<br>(n = 512, q = 12289)<br>(n = 1024, q = 12289) | 2,056<br>4,616<br>10,248   | 254.52 nJ<br>549.98 nJ<br>1205.03 nJ |

| Roy et al.<br>[RVM+14]         | FPGA             | -            | -          | 313<br>278    | (n = 256, q = 7681)<br>(n = 512, q = 12289)                          | 1,691<br>3,443             | -                                    |

| Du et al.<br>[DB16]            | FPGA             | -            | -          | 233           | (n = 256, q = 7681)<br>(n = 512, q = 12289)                          | 4,066<br>8,806             | -                                    |

**Table 1:** Comparison of our NTT performance with state-of-the-art

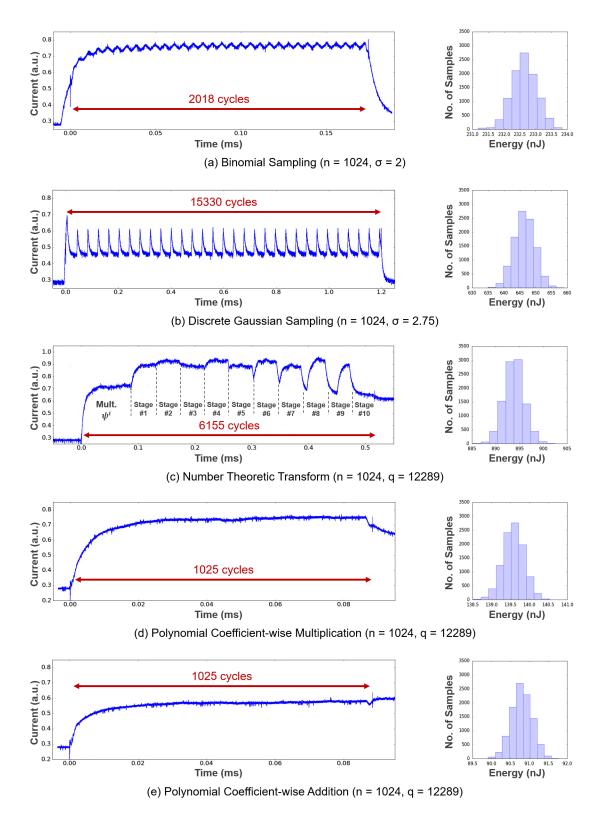

$\omega_{n/2} = \omega_n^2$ ,  $\omega_n^{-j} = \omega_n^{n-j}$  and  $\omega = \psi^2$  [DB16]. Then, it's sufficient to store only  $\omega_n^j$  for  $j \in [0, n/2)$  and  $\psi^i$ ,  $n^{-1}\psi^{-i} \mod q$  for  $i \in [0, n)$ , thus reducing the twiddle factor memory size by 37.5% down to 15 KB. Finally, we compare the energy-efficiency and performance of our NTT with state-of-the-art software and ASIC hardware implementations in Table 1. For the software implementation, we have used assemblyoptimized code for ARM Cortex-M4 from the PQM4 crypto library [KRSS18], and measurements were performed using the NUCLEO-F411RE development board [STM]. Total cycle count of our NTT is  $(\frac{n}{2}+1) \lg n + (n+1)$ , including the multiplication of polynomial coefficients with powers of  $\psi$ . All measurements for our NTT implementation were performed on our test chip operating at clock frequency 72 MHz and nominal supply voltage 1.1 V. Our hardware-accelerated NTT is up to 11× more energy-efficient than the software implementation, after accounting for voltage scaling. It is  $2.5\times$  more energy-efficient compared to the fast NTT design from [NDBC18] with similar cycle count, and  $1.5 \times$ more energy-efficient compared to the slow NTT design from [NDBC18] with 4× cycle count. Our NTT is almost twice as fast as [FS19], since our memory architecture allows computing one butterfly per cycle even with single-port SRAMs, while having similar energy consumption. The energy-efficiency of our NTT implementation is largely due to the careful design of low-power modular arithmetic, as discussed earlier, which decreases overall modular reduction complexity and simplifies the logic circuitry. However, our NTT is still about 4× less energy-efficient compared to [STCZ18], primarily due to the fact that [STCZ18] uses 16 parallel butterfly units along with dedicated four-port scratch-pad buffers to achieve

higher parallelism and lower energy consumption at the cost of significantly larger chip area (2.05 mm<sup>2</sup>) compared to our design (0.28 mm<sup>2</sup>). As will be discussed in Section 6, sampling accounts for majority of the computational cost in Ring-LWE and Module-LWE schemes, therefore justifying our choice of

area-efficient NTT architecture at the cost of some energy overhead.

# 4 Discrete Distribution Sampler

Hardness of the LWE problem is directly related to statistical properties of the error samples. Therefore, an accurate and efficient sampler is a critical component of any lattice cryptography implementation. Sampling accounts for a major portion of the computational overhead in software implementations of ideal and module lattice-based protocols [OSPG18]. A cryptographically secure pseudo-random number generator (CS-PRNG) is used to generate uniformly random numbers, which are then post-processed to convert them into samples from different discrete probability distributions. In this section, we describe our design of energy-efficient CS-PRNG along with fast sampling techniques for configurable distribution parameters.

#### 4.1 Energy-Efficient CS-PRNG

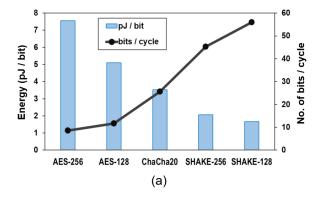

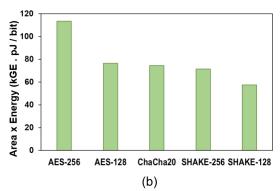

Some of the standard choices for CS-PRNG are SHA-3 in the SHAKE mode [NIS15], AES in counter mode [NIS01] and ChaCha20 [Ber08a]. In order to identify the most efficient among these, we have compared them in terms of area, pseudo-random bit generation performance and energy consumption, as shown in Table 2. Only place-and-route area and measured energy are considered for all analysis, and synthesis area is reported for reference. For fair comparison, all the three primitives – SHA-3, AES and ChaCha20 – were implemented as full data path architectures. From Fig. 8, we observe that although all three primitives have comparable area-energy product, SHA-3 is  $2\times$  more energy-efficient than ChaCha20 and  $3\times$  more energy-efficient than AES; and this is largely due to the fact that SHA-3 generates the highest number of pseudo-random bits per round.

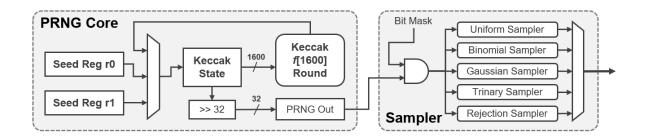

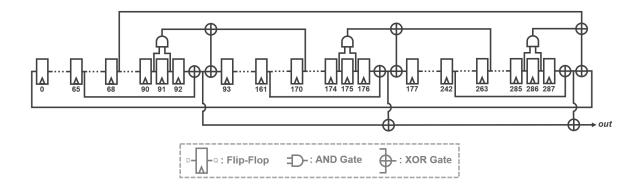

The basic building block of SHA-3 is the Keccak permutation function [BDPV09]. Therefore, our PRNG consists of a 24-cycle Keccak-f[1600] core [BPC19] which can be configured in different SHA-3 modes and consumes 2.33 nJ per round at nominal voltage of 1.1 V (and 0.89 nJ per round at 0.68 V). Its 1600-bit state is processed in parallel, thus avoiding expensive register shifts and multiplexing

| PRNG        | Area (kGE) <sup>a</sup> | Cycles / Round | No. of PRNG Bits | Energy (pJ / bit) b |

|-------------|-------------------------|----------------|------------------|---------------------|

| SHAKE-128   | 24.5 (22.5)             | 24             | 1344             | 1.67                |

| SHAKE-256   | 34.5 (23.5)             | 24             | 1088             | 2.07                |

| ChaCha20    | 21.1 (17.5)             | 20             | 512              | 3.53                |

| AES-128-CTR | 15.0 (11.1)             | 11             | 128              | 5.10                |

| AES-256-CTR | 15.0 (11.1)             | 15             | 128              | 7.56                |

**Table 2:** Comparison of CS-PRNG designs

**Figure 8:** Analysis of SHAKE-128, SHAKE-256, AES-128-CTR, AES-256-CTR and ChaCha20 in terms of energy per bit, bits per cycle and area-energy product.

Figure 9: Architecture of discrete distribution sampler with Keccak-based PRNG core.

required in serial architectures. Fig. 9 shows the overall architecture our discrete distribution sampler with the energy-efficient SHA-3 core. Pseudo-random bits generated by SHAKE-128 or SHAKE-256 are stored in the 1600-bit Keccak state register, and shifted out 32 bits at a time as required by the sampler. The sampler then feeds these bits, AND-ed with the appropriate bit mask to truncate them to desired size, to the post-processing logic to perform one of the following five types of operations—rejection sampling in [0,q), binomial sampling with standard deviation  $\sigma$ , discrete Gaussian sampling with standard deviation  $\sigma$  and desired precision up to 32 bits, uniform sampling in  $[-\eta,\eta]$  for  $\eta < q$  and trinary sampling in  $\{-1,0,+1\}$  with specified weights for the +1 and -1 samples.

#### 4.2 Rejection Sampling

The public polynomial a in Ring-LWE and the public vector a in Module-LWE have their coefficients uniformly drawn from  $\mathbb{Z}_q$  through rejection sampling, where uniformly random numbers of desired bit size are obtained from the PRNG as candidate samples and only numbers smaller than q are accepted. The probability that a random number is not accepted is known as the rejection probability.

| Prime   | Bit  | Rej. Prob.     | Scaling | Rej. Prob.   | Decrease in |

|---------|------|----------------|---------|--------------|-------------|

|         | Size | (w/o. scaling) | Factor  | (w. scaling) | Rej. Prob.  |

| 7681    | 13   | 0.06           | 1       | 0.06         | -           |

| 12289   | 14   | 0.25           | 5       | 0.06         | 0.19        |

| 40961   | 16   | 0.37           | 3       | 0.06         | 0.31        |

| 65537   | 17   | 0.50           | 7       | 0.12         | 0.38        |

| 120833  | 17   | 0.08           | 1       | 0.08         | -           |

| 133121  | 18   | 0.49           | 7       | 0.11         | 0.38        |

| 184321  | 18   | 0.30           | 11      | 0.03         | 0.27        |

| 8380417 | 23   | $\approx 0$    | 1       | $\approx 0$  | -           |

| 8058881 | 23   | 0.04           | 1       | 0.04         | -           |

| 4205569 | 23   | 0.50           | 7       | 0.12         | 0.38        |

| 4206593 | 23   | 0.50           | 7       | 0.12         | 0.38        |

| 8404993 | 24   | 0.50           | 7       | 0.12         | 0.38        |

Table 3: Rejection probabilities for different primes with and without fast sampling

For prime q, the rejection probability is calculated as  $(1-q/2^{\lceil\lg q\rceil})$ . In Table 3, we list the rejection probabilities for primes mentioned earlier in Section 3. Clearly, different primes have very different rejection probabilities, often as high as 50%, which can be a bottleneck in lattice-based protocols. To solve this problem, we refer to [GS16] where pseudo-random numbers smaller than 5q are accepted for q=12289, thus reducing the rejection probability from 25% to 6%. We extend this technique for any prime q by scaling the rejection bound from q to kq, for appropriate small integer k, so that the rejection probability is now  $(1-kq/2^{\lceil\lg kq\rceil})$ . We list these scaling factors for the primes in Table 3 along with the corresponding decrease in rejection probability.

| Design               | Platform         | Tech<br>(nm) | VDD<br>(V) | Freq<br>(MHz) | Parameters                                                           | Samp.<br>Cycles              | Samp.<br>Energy                    |

|----------------------|------------------|--------------|------------|---------------|----------------------------------------------------------------------|------------------------------|------------------------------------|

| This work            | ASIC             | 40           | 1.1        | 72            | (n = 256, q = 7681)<br>(n = 512, q = 12289)<br>(n = 1024, q = 12289) | 461<br>921<br>1,843          | 50.90 nJ<br>105.74 nJ<br>211.46 nJ |

| Software<br>[KRSS18] | ARM<br>Cortex-M4 | -            | 3.0        | 100           | (n = 256, q = 7681)<br>(n = 512, q = 12289)<br>(n = 1024, q = 12289) | 60,433<br>139,153<br>284,662 | 37.17 μJ<br>85.58 μJ<br>175.07 μJ  |

Table 4: Comparison of rejection sampling with software

Although this method reduces rejection rates, the output samples now lie in [0, kq) instead of [0, q). In [GS16], for q = 12289 and k = 5, the accepted samples are reduced to  $\mathbb{Z}_q$  by subtracting q from them up to four times. Since k is not fixed for our rejection sampler, we employ Barrett reduction [Bar86] for this purpose. Unlike modular multiplication, where the inputs lie in  $[0, q^2)$ , the inputs here are much smaller; so the Barrett reduction parameters are also quite small, therefore requiring little additional logic. In Table 4, we compare our rejection sampler performance (SHAKE-128 used as PRNG) with software implementation on ARM Cortex-M4 using assembly-optimized Keccak [KRSS18].

## 4.3 Binomial Sampling

For binomial sampling, we take two k-bit chunks from the PRNG and computes the difference of their Hamming weights, as proposed in [PAA<sup>+</sup>19]. The resulting samples follow a binomial distribution with standard deviation  $\sigma = \sqrt{k/2}$ . We allow configuring k to any value up to 32, thus providing the flexibility to support different standard deviations.

We compare our binomial sampling performance (SHAKE-256 used as PRNG) with state-of-the-art software and hardware implementations in Table 5. Our sampler is more than two orders of magnitude more energy-efficient compared to the software implementation on ARM Cortex-M4 which uses assembly-optimized Keccak [KRSS18]. It is also  $14 \times$  more efficient than [STCZ18] which uses Knuth-Yao sampling [KY76] for binomial distributions with ChaCha20 as PRNG.

| Design                  | Platform         | Tech<br>(nm) | VDD<br>(V) | Freq<br>(MHz) | Parameters                                                | Samp.<br>Cycles              | Samp.<br>Energy                    |

|-------------------------|------------------|--------------|------------|---------------|-----------------------------------------------------------|------------------------------|------------------------------------|

| This work               | ASIC             | 40           | 1.1        | 72            | (n = 256, k = 4)<br>(n = 512, k = 8)<br>(n = 1024, k = 8) | 505<br>1,009<br>2,018        | 58.20 nJ<br>116.26 nJ<br>232.50 nJ |

| Software<br>[KRSS18]    | ARM<br>Cortex-M4 | -            | 3.0        | 100           | (n = 256, k = 4)<br>(n = 512, k = 8)<br>(n = 1024, k = 8) | 52,603<br>155,872<br>319,636 | 32.35 μJ<br>95.86 μJ<br>196.58 μJ  |

| Song et al.<br>[STCZ18] | ASIC             | 40           | 0.9        | 300           | (n = 512, k = 16)                                         | 3,704                        | 1.25 μJ                            |

| Oder et al.<br>[OG17]   | FPGA             | -            | -          | 125           | (n = 1024, k = 16)                                        | 33,792                       | -                                  |

Table 5: Comparison of binomial sampling with state-of-the-art

```

Algorithm 8 Discrete Gaussian Sampling using Inversion Method [NAB+19]

Require: Random inputs r_0 \in \{0,1\}, r_1 \in [0,2^r) and table T_\chi = (T_\chi[0], \cdots, T_\chi[s])

Ensure: Sample e \in \mathbb{Z} from \chi

1: e \leftarrow 0

2: for (z = 0; z < s; z = z + 1) do

3: if r_1 > T_\chi[z] then

4: e \leftarrow e + 1

5: end if

6: end for

7: e \leftarrow (-1)^{r_0} \cdot e

```

**Table 6:** Comparison of discrete Gaussian sampling with software

| Design               | Platform         | Tech<br>(nm) | VDD<br>(V) | Freq<br>(MHz) | Parameters                                                                                                       | Samp.<br>Cycles               | Samp.<br>Energy                      |

|----------------------|------------------|--------------|------------|---------------|------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------------|

| This work            | ASIC             | 40           | 1.1        | 72            | $(n = 512, \sigma = 25.0, s = 54)$<br>$(n = 1024, \sigma = 2.75, s = 11)$<br>$(n = 1024, \sigma = 2.30, s = 10)$ | 29,169<br>15,330<br>14,306    | 1232.71 nJ<br>647.86 nJ<br>604.58 nJ |

| Software<br>[KRSS18] | ARM<br>Cortex-M4 | -            | 3.0        | 100           | $(n = 512, \sigma = 25.0, s = 54)$<br>$(n = 1024, \sigma = 2.75, s = 11)$<br>$(n = 1024, \sigma = 2.30, s = 10)$ | 397,921<br>325,735<br>317,541 | 244.72 μJ<br>200.33 μJ<br>195.29 μJ  |

#### 4.4 Discrete Gaussian Sampling

8: return e

Our discrete Gaussian sampler implements the inversion method of sampling [Fol14] from a discrete symmetric zero-mean distribution  $\chi$  on  $\mathbb Z$  with small support which approximates a rounded continuous Gaussian distribution, e.g., in Frodo [NAB<sup>+</sup>19] and R.EMBLEM [SPL<sup>+</sup>17]. For a distribution with support  $S_{\chi} = \{-s, \cdots, -1, 0, 1, \cdots, s\}$ , where s is a small positive integer, the probabilities  $\Pr(z)$  for  $z \in S_{\chi}$ , such that  $\Pr(z) = \Pr(-z)$  can be derived from the cumulative distribution table (CDT)  $T_{\chi} = (T_{\chi}[0], T_{\chi}[1], \cdots, T_{\chi}[s])$ , where  $2^{-r} \cdot T_{\chi}[0] = \Pr(0)/2 - 1$  and  $2^{-r} \cdot T_{\chi}[z] = \Pr(0)/2 - 1 + \sum_{i=1}^{i=z} \Pr(i)$  for  $z \in [1, s]$  for a given precision r. Given random inputs  $r_0 \in \{0, 1\}, r_1 \in [0, 2^r)$  and the distribution table  $T_{\chi}$ , a sample  $e \in \mathbb{Z}$  from  $\chi$  can be obtained using Algorithm 8 [NAB<sup>+</sup>19].

The sampling must be constant-time in order to eliminate timing side-channels, therefore the algorithm does a complete loop through the entire table  $T_\chi$ . The comparison  $r_1 > T_\chi[z]$  must also be implemented in a constant-time manner. Our implementation adheres to these requirements and uses a  $64 \times 32$  RAM to store the CDT, allowing the parameters  $s \le 64$  and  $r \le 32$  to be configured according to the choice of the distribution. In Table 6, we have compared our Gaussian sampler performance (SHAKE-256 used as PRNG) with software implementation on ARM Cortex-M4 using assembly-optimized Keccak [KRSS18], and we observe up to  $40 \times$  improvement in energy-efficiency after accounting for voltage scaling. Hardware architectures for Knuth-Yao sampling have been proposed by [RVM+14] and [STCZ18], but they are for discrete Gaussian distributions with larger standard deviation and higher precision, which we do not support.

#### 4.5 Other Distributions

Several lattice-based protocols, such as CRYSTALS-Dilithium [LDK<sup>+</sup>19] and qTESLA [BAA<sup>+</sup>19], require polynomials to be sampled with coefficients uniformly distributed in the range  $[-\eta, \eta]$  for a specified bound  $\eta < q$ . For this, we again use rejection sampling. Unlike rejection sampling from  $\mathbb{Z}_q$ , we do not require any special techniques since  $\eta$  is typically small or an integer close to a power of two.

Finally, we have also implemented a trinary sampler for polynomials with coefficients from  $\{-1, 0, +1\}$ . We classify these polynomials into three categories: (1) with m non-zero coefficients, (2) with  $m_0 + 1$ 's and  $m_1 - 1$ 's, and (3) with coefficients distributed as  $Pr(x = 1) = Pr(x = -1) = \rho/2$  and  $Pr(x = 0) = 1 - \rho$

**Algorithm 9** Trinary Sampling with m non-zero coefficients (+1's and -1's)

```

Require: m < n and a PRNG

Ensure: s = (s_0, s_1, \dots, s_{n-1})

1: s \leftarrow (0, 0, \dots, 0) ; i \leftarrow 0

2: while i < m \text{ do}

pos \in_R [0, n)

sign \in_R \{0,1\}

4:

if s_{pos} = 0 then

5:

6:

if sign = 0 then

s_{pos} \leftarrow 1

7:

8:

s_{pos} \leftarrow -1

9:

10:

end if

i \leftarrow i + 1

11:

12:

end if

13: end while

14: return s

```

**Algorithm 10** Trinary Sampling with  $m_0 + 1$ 's and  $m_1 - 1$ 's

```

Require: m_0 + m_1 < n and a PRNG

Ensure: s = (s_0, s_1, \dots, s_{n-1})

1: s \leftarrow (0, 0, \dots, 0); i \leftarrow 0

2: while i < m_0 do

pos \in_R [0, n)

3:

if s_{pos} = 0 then

s_{pos} \leftarrow +1

5:

i \leftarrow i+1

6:

end if

7:

8: end while

9:

while i < m_0 + m_1 \, do

pos \in_R [0, n)

10:

if s_{pos} = 0 then

11:

s_{pos} \leftarrow -1

12:

i \leftarrow i + 1

13:

end if

14:

15: end while

16: \mathbf{return} s

```

**Algorithm 11** Trinary Sampling with coefficients from  $\{-1,0,+1\}$  distributed according to  $\Pr(x=1) = \Pr(x=-1) = \rho/2$  and  $\Pr(x=0) = 1 - \rho$

```

Require: k \in [1,7], \rho = 1/2^k and a PRNG

Ensure: s = (s_0, s_1, \dots, s_{n-1})

1: for (i = 0; i < n; i = i + 1) do

x \in_{R} [0, 2^{k})

if x = 0 then

3:

4:

s_i \leftarrow 1

else if x = 1 then

5:

6:

s_i \leftarrow -1

else

7:

s_i \leftarrow 0

8:

9:

end if

10: end for

11: \mathbf{return} s

```

for  $\rho \in \{1/2, 1/4, 1/8, \dots, 1/128\}$ . Their implementations are described in Algorithms 9, 10 and 11. For the first two cases, we start with a zero-polynomial s of size n. Then, uniformly random coefficient indices  $\in [0, n)$  are generated, and the corresponding coefficients are replaced with -1 or +1 if they are zero [BAA+19, CHWZ17]. For the third case, sampling of the coefficients is based on the observation [CPL+17] that for a uniformly random number  $x \in [0, 2^k)$  we have  $\Pr(x = 0) = 1/2^k$ ,  $\Pr(x = 1) = 1/2^k$  and  $\Pr(x \in [2, 2^k)) = 1 - 1/2^k$ . Therefore, for the appropriate value of  $k \in [1, 7]$ , we can generate samples from the desired trinary distribution with  $\rho = 1/2^k$ . For all three algorithms, the symbol  $\in_R$  denotes pseudo-random number generation using the PRNG.

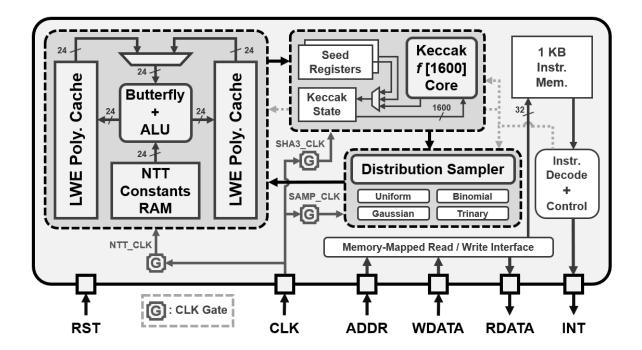

# 5 Chip Architecture

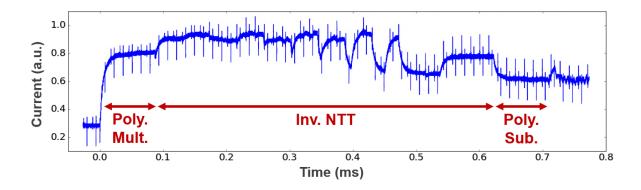

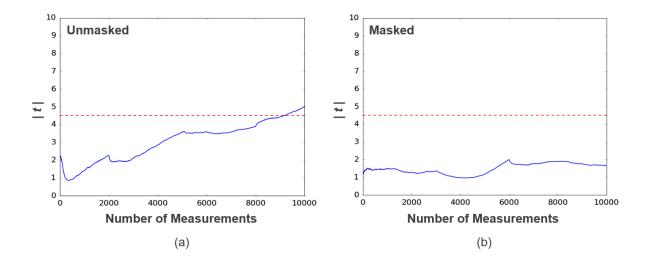

The top-level architecture of Sapphire is shown in Fig. 10. The efficient building blocks described in Sections 3 and 4 are integrated with a 1 KB instruction memory and an instruction decoder to form the core of our crypto-processor. It can be programmed using 32-bit custom instructions to perform different polynomial arithmetic, transform and sampling operations, as well as simple branching. For example, the following instructions generate polynomials  $a, s, e \in \mathcal{R}_q$ , and calculate  $a \cdot s + e$ , which is a typical computation in the Ring-LWE-based scheme NewHope-1024:

```

config (n = 1024, q = 12289)

# sample_a

rej_sample (prng = SHAKE-128, seed = r0, c0 = 0, c1 = 0, poly = 0)

# sample_s

bin_sample (prng = SHAKE-256, seed = r1, c0 = 0, c1 = 0, k = 8, poly = 1)

# sample e

bin_sample (prng = SHAKE-256, seed = r1, c0 = 0, c1 = 1, k = 8, poly = 2)

# ntt s

mult_psi (poly = 1)

transform (mode = DIF_NTT, poly_dst = 4, poly_src = 1)

# a_mul_s

poly_op (op = MUL, poly_dst = 0, poly_src = 4)

# intt_a_mul_s

transform (mode = DIT_INTT, poly_dst = 5, poly_src = 0)

mult_psi_inv (poly = 5)

# a mul s plus e

poly_op (op = ADD, poly_dst = 1, poly_src = 5)

```

The config instruction is first used to configure the protocol parameters n and q which, in this example, are the parameters from NewHope-1024. For n=1024, the polynomial cache is divided into 8 polynomials, which are accessed using the poly argument in all instructions. For sampling, the seed can be chosen from a pair of 256-bit registers r0 and r1, while two 16-bit registers c0 and c1 are used as

Figure 10: Sapphire lattice crypto-processor top-level architecture.

counters for sampling multiple polynomials from the same seed. For coefficient-wise operations poly\_op, the poly\_src argument indicates the first source polynomial while the poly\_dst argument is used to denote the second source (and destination) polynomial. Similarly, the following set of instructions are used to generate matrix of polynomials  $\mathbf{A} \in \mathcal{R}_q^{2 \times 2}$  and vectors of polynomials  $\mathbf{s}, \mathbf{e} \in \mathcal{R}_q^2$ , and calculate  $\mathbf{A} \cdot \mathbf{s} + \mathbf{e}$ , which is a typical computation in the Module-LWE-based scheme CRYSTALS-Kyber-512:

```

config (n = 256, q = 7681)

# sample s

bin_sample (prng = SHAKE-256, seed = r1, c0 = 0, c1 = 0, k = 3, poly = 4)

bin_sample (prng = SHAKE-256, seed = r1, c0 = 0, c1 = 1, k = 3, poly = 5)

# sample e

bin_sample (prng = SHAKE-256, seed = r1, c0 = 0, c1 = 2, k = 3, poly = 24)

bin_sample (prng = SHAKE-256, seed = r1, c0 = 0, c1 = 3, k = 3, poly = 25)

# ntt_s

mult psi (poly = 4)

transform (mode = DIF_NTT, poly_dst = 16, poly_src = 4)

mult_psi (poly = 5)

transform (mode = DIF_NTT, poly_dst = 17, poly_src = 5)

# sample A0

rej_sample (prng = SHAKE-128, seed = r0, c0 = 0, c1 = 0, poly = 0)

rej_sample (prng = SHAKE-128, seed = r0, c0 = 1, c1 = 0, poly = 1)

# A0_mul_s

poly_op (op = MUL, poly_dst = 0, poly_src = 16)

poly_op (op = MUL, poly_dst = 1, poly_src = 17)

init (poly = 20)

poly_op (op = ADD, poly_dst = 20, poly_src = 0)

poly_op (op = ADD, poly_dst = 20, poly_src = 1)

# sample A1

rej_sample (prng = SHAKE-128, seed = r0, c0 = 0, c1 = 1, poly = 0)

rej_sample (prng = SHAKE-128, seed = r0, c0 = 1, c1 = 1, poly = 1)

# A1 mul s

poly_op (op = MUL, poly_dst = 0, poly_src = 16)

poly_op (op = MUL, poly_dst = 1, poly_src = 17)

init (poly = 21)

poly_op (op = ADD, poly_dst = 21, poly_src = 0)

poly_op (op = ADD, poly_dst = 21, poly_src = 1)

# intt_A_mul_s

transform (mode = DIT_INTT, poly_dst = 8, poly_src = 20)

mult_psi_inv (poly = 8)

transform (mode = DIT_INTT, poly_dst = 9, poly_src = 21)

mult_psi_inv (poly = 9)

# A_mul_s_plus_e

poly_op (op = ADD, poly_dst = 24, poly_src = 8)

poly_op (op = ADD, poly_dst = 25, poly_src = 9)

```

In this example, parameters from CRYSTALS-Kyber-512 have been used. For n=256, the polynomial cache is divided into 32 polynomials, which are again accessed using the poly argument. The init instruction is used to initialize a specified polynomial with all zero coefficients. The matrix  $\boldsymbol{A}$  is generated one row at a time, following a *just-in-time* approach [KBRV18] instead of generating and storing all the rows together, to save memory, which becomes especially useful when dealing with larger matrices such as in CRYSTALS-Kyber-1024 and CRYSTALS-Dilithium-IV. We have written a Perl script to parse such plain-text programs and convert them into 32-bit binary instructions which can be decoded by the Sapphire crypto-processor. A complete list of instructions is provided in Appendix B.

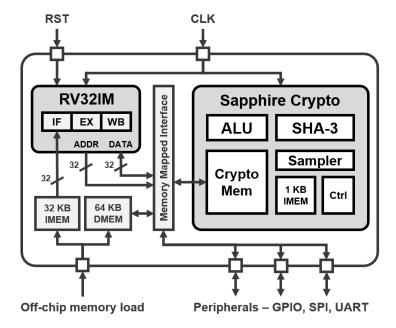

We use dedicated clock gates for fine-grained power savings during program execution, and an interrupt pin is used to indicate completion of the program. Its memory and data registers can be accessed through a simple memory-mapped interface. Using the same interface, it is also coupled with a

| Chip Specifications           |              |  |  |  |  |

|-------------------------------|--------------|--|--|--|--|

| Technology TSMC 40 nm LP CMOS |              |  |  |  |  |

| Supply voltage                | 0.68 – 1.1 V |  |  |  |  |

| Package                       | 64-pin QFN   |  |  |  |  |

| Die size                      | 2 mm x 2 mm  |  |  |  |  |

| Lattice Cryptography Processor (Sapphire) |                                          |  |  |  |  |

|-------------------------------------------|------------------------------------------|--|--|--|--|

| Total area                                | 0.28 mm <sup>2</sup>                     |  |  |  |  |

| Logic gates                               | 106k (NAND2 equiv.)                      |  |  |  |  |

| SRAM                                      | 40.25 KB                                 |  |  |  |  |

| Max. frequency                            | 12 MHz at 0.68 V and 72 MHz at 1.1 V     |  |  |  |  |

| Lattice parameters                        | N: 64 to 2048 and q: 24-bit configurable |  |  |  |  |

| CS-PRNG                                   | SHAKE - 128 / 256                        |  |  |  |  |

| Hash function                             | SHA-3 - 256 / 512                        |  |  |  |  |

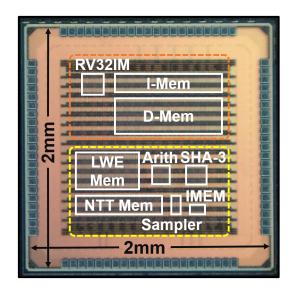

Figure 11: Chip micrograph and test chip specifications.

Figure 12: Chip architecture with Sapphire crypto-core and RISC-V micro-processor.

low-power RISC-V micro-processor [BJW<sup>+</sup>18], as shown in Fig. 12, with 32 KB instruction memory and 64 KB data memory, which implements the RV32IM instruction set [WLPA14] and has Dhrystone performance similar to ARM Cortex-M0. When executing cryptographic workloads in the Sapphire core, the RISC-V core can be clock-gated using the wait-for-interrupt (wfi) instruction. The processor is woken up by a dedicated interrupt from the Sapphire core, which is raised when the cryptographic operation is complete. Using the memory-mapped interface ensures that the cryptographic core can be accessed through simple load and store instructions, without requiring any custom instructions or changes to the compilation toolchain. While the cryptographic core is used to accelerate all lattice cryptography computations, the RISC-V processor is used for scheduling the cryptographic workloads as well as for compression and decompression of public keys and ciphertexts. The Keccak-f[1600] core inside Sapphire can be accessed standalone through RISC-V software, and is used to accelerate SHA-3 hashing and extendable output functions according to the requirements of the protocol.

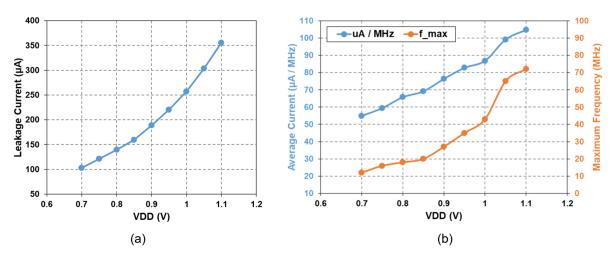

Our test chip was fabricated in the TSMC 40nm LP CMOS process, and the chip micrograph is shown in Fig. 11 with the key design components highlighted. The final placed-and-routed design of our

Sapphire core consists of 106k logic gates (76 kGE for synthesized design) and 40.25 KB SRAM, with a total area of 0.28 mm<sup>2</sup> (logic and memory combined). Our test chip supports supply voltage scaling from 0.68 V to 1.1 V. Although one of our key design objectives was to demonstrate a configurable lattice cryptography processor, our architecture can be easily scaled for more specific parameter sets. For example, in order to accelerate only NewHope-512 (n=512, q=12289), size of the polynomial cache can be reduced to 6.5 KB (=  $8 \times 512 \times 13$  bits) and the pre-computed NTT constants can be hard-coded in logic or stored in a 2.03 KB ROM (=  $2.5 \times 512 \times 13$  bits) instead of the 15 KB SRAM. Also, the modular arithmetic logic in the ALU can be simplified significantly to work with a single prime only.

We use the on-chip software-configurable clock gates (shown in Fig. 10) to accurately measure power consumption of different sub-modules inside the Sapphire core, e.g., sampling, NTT, arithmetic, etc. For example, the following instructions are executed to measure the average power consumption of NTT over 1000 executions:

The clock\_config instruction is used to control the clock gates, e.g., the PRNG and sampler clocks are gated when measuring NTT power (the RISC-V core is clock-gated using wfi as explained earlier). A simple loop is implemented using labels, comparison and conditional jump instructions, similar to assembly programs in general-purpose micro-controllers (please refer to Appendix B for details of our custom instructions). One of the chip GPIO pins is kept high during the execution of this program to indicate the measurement window, and the power consumption is measured using a source meter. This still includes leakage power from the rest of the chip, but it is only a small fraction of the total power compared to the dynamic power of the operation being measured. Similarly, power consumption of the RISC-V core is measured by clock-gating the Sapphire cryptographic core through software. Finally, leakage power of the chip is measured by externally gating the clock signal being supplied to the chip, so that all logic inside the chip is inactive.

The RISC-V processor consumes 45  $\mu$ W/MHz at 1.1 V (18  $\mu$ W/MHz at 0.68 V) when running the Dhrystone 2.1 benchmark. Power consumption of the cryptographic core is a strong function of the protocols being executed along with the associated parameters. Average power consumption of the lattice crypto-processor was measured to be around 8 mW at 1.1 V and 72 MHz (520  $\mu$ W at 0.68 V and 12 MHz). Total leakage power of the chip was measured to be 391  $\mu$ W at 1.1 V (70  $\mu$ W at 0.68 V). Since our chip operates on a single power domain, it is not possible to measure leakage power of different components of the chip. We report the individual module-wise leakage and dynamic power consumption, as obtained from post-place-and-route simulations of our design operating at 1.1 V and 72 MHz, in the table below:

| Module                    | $P_{leak}$ ( $\mu$ W) | $P_{dyn}$ ( $\mu W$ ) | $P_{tot}$ ( $\mu$ W) |

|---------------------------|-----------------------|-----------------------|----------------------|

| Butterfly + ALU           | 18.28                 | 9210.04               | 9228.32              |

| LWE Polynomial Cache      | 120.28                | 1660.18               | 1780.46              |

| NTT Constants RAM         | 76.50                 | 661.61                | 738.11               |

| Keccak Core + Sampler     | 41.15                 | 1053.58               | 1094.73              |

| RISC-V Processor + Memory | 320.15                | 2745.68               | 3065.83              |

Before moving on to the protocol implementations and measurements, we summarize some key architectural design techniques we have used to achieve energy-efficiency:

We have employed increased parallelism in the modular arithmetic and CS-PRNG modules in the

form of single-cycle butterfly computation and 1600-bit 24-cycle Keccak data-path respectively.

This reduces cycle count as well as data movement and control circuitry, thus decreasing overall

energy consumption.

- Based on overall computational complexity, we know that additions are much cheaper than multiplications. Therefore, we have exploited special properties of prime q and parameter m, wherever possible, during Barrett reduction to convert expensive multiplications into cheaper bit-shifts and additions / subtractions.

- Reading data from registers involves much smaller energy consumption compared to reading from SRAMs. We have used registers for storing PRNG seeds, temporary values and the Keccak state, and SRAMs are used to store only the polynomials. This significantly reduces overall energy consumption, especially for the Keccak core.

- Software-controlled clock gates (explicitly inserted in RTL, apart from tool-inserted clock gates) for the sampler, PRNG and NTT allow fine-grained dynamic power savings by gating inactive modules as required during program execution.

- The crypto-processor internal memory is efficiently utilized to store polynomials during protocol execution, thus avoiding access to the main processor's data memory as much as possible and reducing energy consumption.

# 6 Protocol Implementations and Measurement Results

To measure the efficiency of our design, we have implemented the following NIST Round 2 lattice-based cryptography protocols on our test chip:

| Algorithm          | Lattice Prob. | NIST Sec. | Parameter Set    |  |  |  |  |  |

|--------------------|---------------|-----------|------------------|--|--|--|--|--|

| CCA-KEM Algorithms |               |           |                  |  |  |  |  |  |

| NewHope            | Ring-LWE      | 1         | NewHope-512      |  |  |  |  |  |

| NewHope            | Tillg-LWE     | 5         | NewHope-1024     |  |  |  |  |  |

|                    |               | 1         | Kyber-512        |  |  |  |  |  |

| CRYSTALS-Kyber     | Module-LWE    | 3         | Kyber-768        |  |  |  |  |  |

|                    |               | 5         | Kyber-1024       |  |  |  |  |  |

|                    |               | 1         | Frodo-640        |  |  |  |  |  |

| Frodo              | LWE           | 3         | Frodo-976        |  |  |  |  |  |

|                    |               | 5         | Frodo-1344       |  |  |  |  |  |

|                    | Signature Alg | orithms   |                  |  |  |  |  |  |

|                    |               | 1         | qTESLA-I         |  |  |  |  |  |

| qTESLA             | Ring-LWE      | 3         | qTESLA-III-size  |  |  |  |  |  |

|                    |               | 3         | qTESLA-III-speed |  |  |  |  |  |

|                    |               | 1         | Dilithium-II     |  |  |  |  |  |

| CRYSTALS-Dilithium | Module-LWE    | 2         | Dilithium-III    |  |  |  |  |  |

|                    |               | 3         | Dilithium-IV     |  |  |  |  |  |

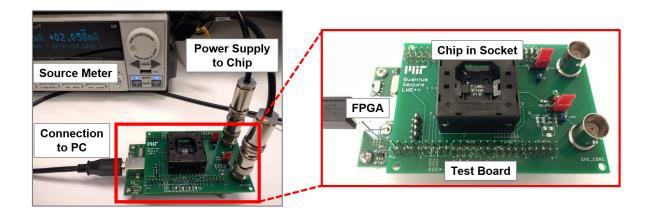

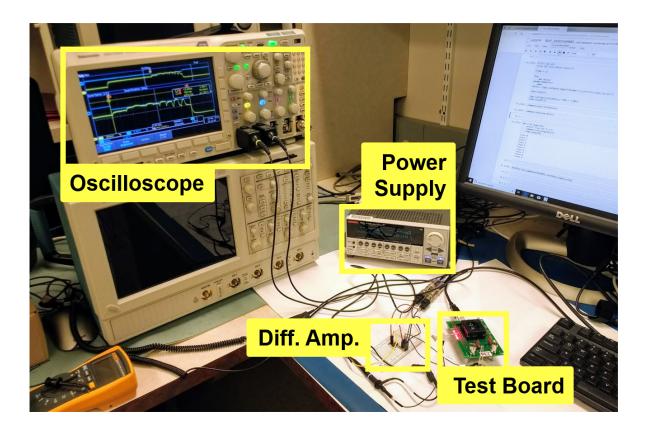

where NIST security levels 1-6 indicate brute-force security matching or exceeding that of AES-128, SHA3-256, AES-192, SHA3-384, AES-256 and SHA3-512 respectively. Fig. 13 shows our test board and measurement setup. The test chip is housed in a QFN64 socket soldered to the board, an Opal Kelly XEM7001 FPGA development board is used to interface with the chip, and a Keithley 2602A source meter supplies power to the chip. Both the FPGA and the source meter are controlled from a host computer through USB and GPIB interfaces respectively. The FPGA is used to transfer programs from the host computer to the instruction memory of our test chip. Also, a small ring-oscillator-based true random number generator [DG07] implemented on the FPGA is connected to our test chip through GPIO pins for providing fresh random inputs to the randombytes function which is part of the NIST API. All lattice cryptography programs are written using custom instructions and compiled with our script, while all RISC-V software is written in C and compiled using the riscv-gcc toolchain.

**Figure 13:** Measurement setup with our test chip.

#### 6.1 Protocol Implementations and Evaluation Results

Next, we describe some key aspects of our protocol implementations along with timing and energy profiling results. All polynomial arithmetic, transforms and sampling operations are accelerated using custom programs running in the Sapphire core, and all SHA-3 computations utilize the Keccak core inside Sapphire. The RISC-V processor is used only to read / write data and programs from / to the cryptographic core (both when executing polynomial computations and when utilizing the fast Keccak core for SHA-3 operations), generate initial randomness using the randombytes function, encode / decode messages and compress / decompress public keys and ciphertexts. For polynomials which need to be read from the polynomial cache and encoded (or decoded and written to the polynomial cache), we directly post-process the outputs (or pre-process the inputs) of the crypto-processor's internal memory, instead of first storing the data in intermediate temporary arrays and then processing them. This saves around 10-20% cycles in overall protocol run-time. Also, the internal clock gates are strategically enabled and disabled during program execution using the clock\_config instruction (please refer to Appendix B for details of our custom instructions) to reduce overall energy consumption.

For the NewHope and CRYSTALS-Kyber key exchange schemes, each of the CPA-secure public key encryption functions – CPA-PKE.KeyGen, CPA-PKE.Encrypt and CPA-PKE.Decrypt – has been written entirely (excluding the encoding and decoding operations) using Sapphire custom instructions with each of the corresponding programs fitting completely in its 1 KB instruction memory. The CCA-secure key encapsulation functions – CCA-KEM.KeyGen, CCA-KEM.Encaps and CCA-KEM.Decaps – involve calls to SHA-3 and the CPA-PKE functions (according to the Fujisaki-Okamoto transform [FO13]), which are implemented in software. Since the signature schemes qTESLA and CRYSTALS-Dilithium both involve probabilistic rejection of intermediate values, the associated polynomial computations are split into multiple custom programs instead of one each for the KeyGen, Sign and Verify functions. These blocks of code are scheduled using RISC-V software, which also handles encoding and decoding operations. The only exception is the KeyGen step in qTESLA, where high-precision discrete Gaussian sampling using large CDT tables is implemented in software, with the SHA-3 functions accelerated in hardware.

Since Module-LWE algorithms involve working with vectors or matrices of polynomials, it is particularly important to ensure that these polynomials fit inside the crypto-processor memory as much as possible (because reads and writes to the internal memory through software are not cheap). When multiplying the public matrix  $\bf A$  with the secret vector  $\bf s$ , the matrix  $\bf A$  is generated through rejection sampling, one row at a time, following the *just-in-time* approach from [KBRV18]. This reduces memory footprint so that the entire computation can fit in the polynomial cache.

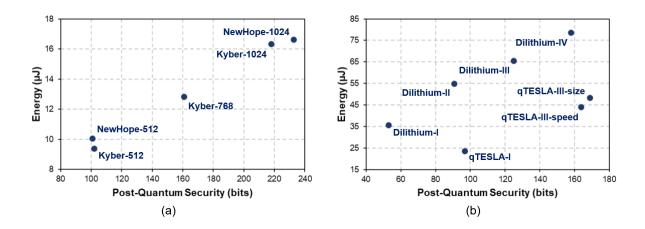

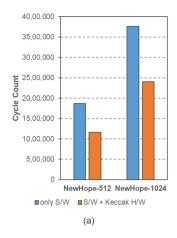

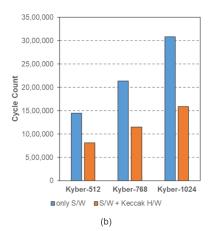

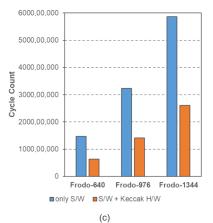

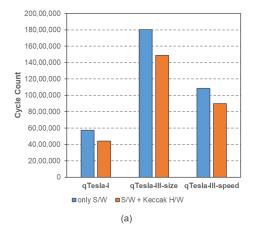

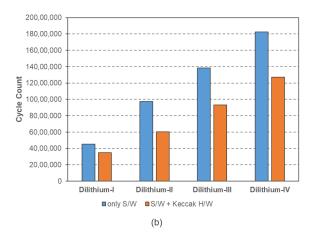

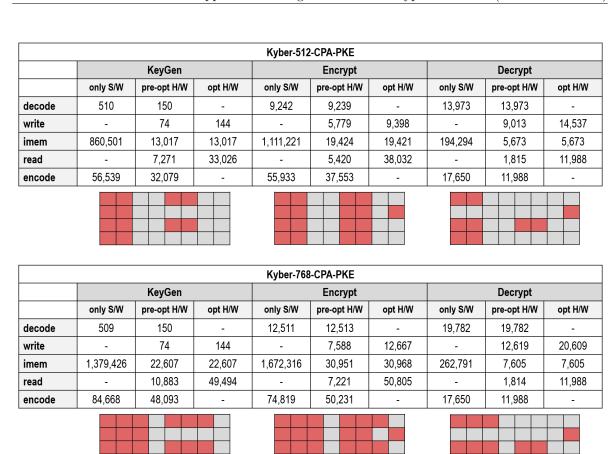

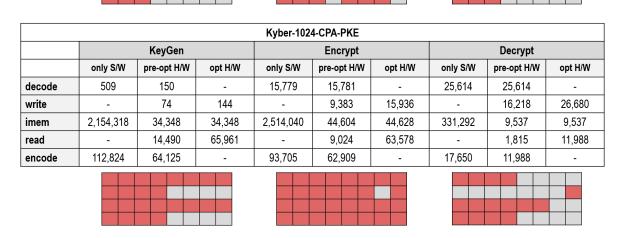

In Table 7, we compare cycle count and energy consumption of our implementations of the Ring-LWE and Module-LWE CPA-PKE schemes with assembly-optimized software on ARM Cortex-M4 micro-processor (from PQM4 [KRSS18]), with average cycle counts for 100 executions. The energy consumption of our test chip has been measured at 1.1 V and 72 MHz, while the energy consumption of the Cortex-M4 processor is estimated from cycle counts using average power (61.5 mW or 615 pJ/cycle at 3.0 V and 100 MHz) measured on NUCLEO-F411RE operating at 100 MHz. The cycle count and

| Protocol                    | Cortex-             | <b>M4</b> [KRSS18]        | This work <sup>†</sup> |                  |                           |  |  |  |  |

|-----------------------------|---------------------|---------------------------|------------------------|------------------|---------------------------|--|--|--|--|

|                             | Cycles              | Energy $(\mu \mathbf{J})$ | Cycles                 | Power (mW)       | Energy $(\mu \mathbf{J})$ |  |  |  |  |

|                             | NewHope-512-CPA-PKE |                           |                        |                  |                           |  |  |  |  |

| KeyGen                      | -                   | -                         | 18,667                 | 7.15             | 1.85                      |  |  |  |  |

| Encrypt                     | -                   | -                         | 53,499                 | 7.79             | 5.79                      |  |  |  |  |

| Decrypt                     | -                   | -                         | 29,099                 | 6.81             | 2.77                      |  |  |  |  |

|                             |                     | NewHope-1                 | 024-CPA-1              | PKE              |                           |  |  |  |  |

| KeyGen                      | 1,179,353           | 725.30                    | 38,012                 | 7.39             | 3.90                      |  |  |  |  |

| Encrypt                     | 1,663,023           | 1022.76                   | 106,611                | 8.10             | 12.00                     |  |  |  |  |

| Decrypt                     | 194,439             | 119.58                    | 56,061                 | 9.31             | 7.26                      |  |  |  |  |

|                             |                     | CRYSTALS-Ky               | ber-512-C              | PA-PKE           |                           |  |  |  |  |

| KeyGen                      | 609,923             | 375.10                    | 46,187                 | 7.61             | 4.90                      |  |  |  |  |

| Encrypt                     | 721,925             | 443.98                    | 66,851                 | 8.33             | 7.74                      |  |  |  |  |

| Decrypt                     | 95,894              | 58.97                     | 32,198                 | 7.67             | 3.45                      |  |  |  |  |

|                             |                     | CRYSTALS-Ky               | ber-768-C              | PA-PKE           |                           |  |  |  |  |