# New Circuit Minimization Techniques for Smaller and Faster AES SBoxes

Alexander Maximov and Patrik Ekdahl

Ericsson Research, Lund, Sweden {alexander.maximov,patrik.ekdahl}@ericsson.com

**Abstract.** In this paper we consider various methods and techniques to find the smallest circuit realizing a given linear transformation on n input signals and m output signals, with a constraint of a maximum depth, maxD, of the circuit. Additional requirements may include that input signals can arrive to the circuit with different delays, and output signals may be requested to be ready at a different depth. We apply these methods and also improve previous results in order to find hardware circuits for forward, inverse, and combined AES SBoxes, and for each of them we provide the fastest and smallest combinatorial circuits. Additionally, we propose a novel technique with "floating multiplexers" to minimize the circuit for the combined SBox, where we have two different linear matrices (forward and inverse) combined with multiplexers. The resulting AES SBox solutions are the fastest and smallest to our knowledge.

Keywords: AES SBox · circuit area · circuit depth · multiplexers · linear matrices

#### 1 Introduction

Efficient hardware design of AES SBoxes is a well-known subject. If you want the absolute maximum clocking speed of the hardware, you'd probably use a straightforward table-lookup implementation, which naturally leads to a large area. In many practical situations the area of the cryptographic subsystem is limited, and the designer cannot afford to implement table-lookup for the 16 SBoxes involved in an AES round. For these situations, we need to study how to implement an AES SBox with logical gates only, focusing on both area and maximum clocking speed. The maximum clocking speed of a circuit is determined by the *critical path* or *depth* of the circuit; the worst case time it takes to get stable output signals from a change in input signals.

Another aspect when implementing AES is, in particular, the need for the inverse cipher. Many modes of operation for a block cipher only use the encryption functionality and hence there is no need for the inverse cipher. In case you need both the forward and inverse SBox, it is often beneficial to combine the two circuits. This is because the main operation of the AES SBox is taking the inverse of a field element, which naturally is its own inverse, and we expect that many gates of the two circuits can be shared.

From a mathematical perspective, the forward AES SBox is defined as the composition of a non-linear function I(g) and an affine function A(g), such that SBox(g) = A(I(g)). The non-linear function  $I(g) = g^{-1}$  is the multiplicative inverse of an element g in the finite field  $GF(2^8)$  defined by the irreducible polynomial  $x^8 + x^4 + x^3 + x + 1$ . We will assume that the reader is familiar with the AES SBox, and refer to [oST01] for a more comprehensive description.

The first step towards a small area implementation was described by Rijmen [Rij00], where results from [IT88] was used. The idea is that the inverse calculation in  $GF(2^8)$

can be reduced to a much simpler inverse calculation in the subfield  $GF(2^4)$  by doing a base change to  $GF((2^4)^2)$ . In 2001, Satoh et al [SMTM01] took this idea further and reduced the inverse calculation to the subfield  $GF(2^2)$ . In 2005, Canright [Can05] built on the work of Satoh et al and investigated the importance of the representation of the subfield, testing many different isomorphisms that led to the smallest area design. This construction is perhaps the most cited and used implementation of an area-constrained combined AES SBox.

In a series of papers, Boyar, Peralta et al presented some very interesting ideas for both the subfield inverter as well as new heuristics for minimizing the area of logical circuits [BP10a, BP10b, BP12, BFP18]. They derived an inverter over  $GF(2^4)$  with depth 4 and a gate count of only 17. The construction in [BP12] is the starting point for this paper.

After Boyar, several other papers followed focusing on low depth implementations [JKL10, NNT<sup>+</sup>10, UHS<sup>+</sup>15]. In 2018 two papers by Reyhani et al [RMTA18a, RMTA18b] presented the best known implementation (up until now) of both the forward SBox as well as the combined SBox. In [LSL<sup>+</sup>19] the authors present a very nice way to include the depth into Boyar's SLP problem [BMP13]. But the algorithm does not work with multiplexers, and hence cannot be applied to the combined SBox.

As pointed out in [RMTA18a], there are misalignments between researchers in how to present and compare implementations of combinatorial circuits. One way is to simply count the total number of standard gates in the design and find the path through the circuit that contains the critical path to determine and compare the speed. In practice it is much more complicated than that. For this paper, we present both the simple measure using only the number of gates, as well as giving a Gate Equivalent (GE) number based on the typical area required for the gate compared to the NAND gate. So for example the 2-input NAND gate will have GE=1, while the XOR gate will have a GE=2.33. The relative numbers for the GE are dependent on the specific ASIC process technology used, as well as the drive strength needed from the gate. We have used the GE values obtained from the Samsung's STD90/MDL90  $0.35\mu$ m 3.3V CMOS technology [Sam00]. A comprehensive discussion on our choices for circuits comparison can be found in Appendix A. Additionally, we propose to count technological depth of a circuit normalized in terms of the delays of a XOR gate, which makes it possible to compare depths and the speed of various academic results.

The rest of the paper is organized as follows. In Section 2 we introduce the standard hardware architecture for the AES SBox. Section 3 we describe the fundamental problem we're are addressing, together with improvements to previously known techniques for solving it. The new idea of considering "floating multiplexers" is introduced in Section 4, followed by architectural improvements to the AES SBox in Section 5. The results, both theoretical and practical synthesis results are given in Section 6. The paper ends with some conclusions and acknowledgements in Sections 7 and 8.

# 2 Preliminaries

We will follow the notation used in both [Can05] and [BP12] when we now construct our tower field representation. The irreducible polynomials, roots, and normal basis can be found in Table 1.

**Table 1:** Definition of the subfields used to construct  $GF(2^8)$ .

| Target Field         | Irreducible Poly. | Root           | Coefficients in Field | Normal Base          |

|----------------------|-------------------|----------------|-----------------------|----------------------|

| $\overline{GF(2^2)}$ | ${x^2 + x + 1}$   | $\overline{W}$ | GF(2)                 | $\overline{[W,W^2]}$ |

| $GF(2^{4})$          | $x^2 + x + W^2$   | Z              | $GF(2^2)$             | $[Z^{2}, Z^{8}]$     |

| $GF(2^8)$            | $x^2 + x + WZ$    | Y              | $GF(2^4)$             | $[Y, Y^{16}]$        |

Following [Can05] and [BP12], we can now derive the expression for inverting a general element  $A = a_0 Y + a_1 Y^{16}$  in  $GF(2^8)$  as

$$\begin{split} A^{-1} &= (AA^{16})^{-1}A^{16} \\ &= ((a_0Y + a_1Y^{16})(a_1Y + a_0Y^{16}))^{-1}(a_1Y + a_0Y^{16}) \\ &= ((a_0^2 + a_1^2)Y^{17} + a_0a_1(Y^2 + Y^{32}))^{-1}(a_1Y + a_0Y^{16}) \\ &= ((a_0 + a_1)^2Y^{17} + a_0a_1(Y + Y^{16})^2)^{-1}(a_1Y + a_0Y^{16}) \\ &= ((a_0 + a_1)^2WZ + a_0a_1)^{-1}(a_1Y + a_0Y^{16}). \end{split}$$

The element inversion in  $GF(2^8)$  can be done over  $GF(2^4)$  according to

$$T_1 = (a_0 + a_1)$$

$T_2 = (WZ)T_1^2$   $T_3 = a_0a_1$   $T_4 = T_2 + T_3$

$T_5 = T_4^{-1}$   $T_6 = T_5a_1$   $T_7 = T_5a_0$  (1)

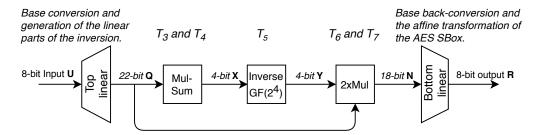

where the result is obtained as  $A^{-1} = T_6 Y + T_7 Y^{16}$ . In these equations we utilize several operations (addition, multiplication, scalar, and squaring) but only two of them are nonlinear over GF(2); multiplication and inversion. Furthermore, the standard multiplication operation also contains some linear operations. If we separate all the linear operations from the non-linear and combine the former with the linear equations needed to do the base change for the AES SBox input, which is represented in polynomial base using the AES SBox irreducible polynomial  $x^8 + x^4 + x^3 + x + 1$ , we will end up with an architecture of the SBox according to Figure 1, where we also indicate were the different parts of equations 1 are calculated.

Figure 1: Architecture of the forward SBox according to [Can05] and [BP12].

In case we are dealing with the inverse SBox, we naturally need to apply the inverse affine transform to the top linear matrix instead of the bottom.

This architecture will be our starting point, and we will now provide a set of new or enhanced algorithms for minimizing both the area and the depth of the two linear top and bottom matrices.

# 3 Circuits for binary linear system of equations

In this section, we will recapitulate the known techniques for linear circuit minimization and propose a few improvements. We start by stating the objectives.

#### 3.1 Basic problem statement

Given a binary matrix  $M_{m\times n}$  and the maximum allowed depth maxD, find the circuit of depth  $D \leq maxD$  with the minimum number of 2-input XOR gates such that it computes  $Y = M \cdot X$ . In other words, given n bits of input  $X = (x_0 \dots x_{n-1})$ , the circuit should

compute m linear combinations  $Y = (y_0 \dots y_{m-1})$ . Any circuit realization that implements a given system of linear expressions is called a **solution**.

The above problem is NP-hard [BMP08], and we have seen various heuristic approaches that help finding a sub-optimal solution in the literature. In all previous work we have studied, the assumption is that all input signals arrive in the same time, and all output signals are "ready" with delays at most maxD. In this paper we extend the original problem with AIR and AOR defined as follows.

Additional Input Requirement (AIR). The problem may be extended with an additional requirement on input signals X, such that each input bit  $x_i$  arrives with its own delay  $d_i$ , in terms of XOR-gates delays. The resulting depth  $D \leq maxD$  then includes input delays. For example, if some input  $x_i$  has the delay  $d_i > maxD$  then no solution exists. The AIR is useful while deriving the bottom matrix as described in Section 2, since after the non-linear part, the signals entering the bottom matrix will have different delays.

Additional Output Requirement (AOR). The problem may be extended by an additional requirement on the output signals. Each output signal  $y_i$  may be required to be "ready" at depth at most  $e_i \leq maxD$ . This is useful when some output signals continue to propagate in the critical path and other signals may be computed with larger delays, but still at most maxD. The AOR is used while deriving the top matrix as described in Section 2, since when we introduce multiplexers for the combined SBox, the output signals of the top matrix will be required to have different delays.

#### 3.2 Cancellation-free heuristics

Cancellation-free heuristics are algorithms that produces linear expressions  $z=a\oplus b$ , where both a and b are Boolean linear expressions in the input variables, and a and b share no common terms. In other words, as we add a and b we will not cancel out any term.

Paar [Paa97] suggested a greedy approach to solving the Basic Problem in 3.1. That solution starts with the matrix M and considers all pairs of columns (i,j) in M. Then a metric is defined (on the pairs of columns) as the number of rows where  $M_{r,i} = M_{r,j} = 1$ , i.e. where the input variables  $x_i$  and  $x_j$  both occur. For the column pair with the highest metric, we form a new variable  $x_n = x_i \oplus x_j$  and add that to the matrix (which now is of size  $m \times (n+1)$ ), and set positions  $M_{r,i} = M_{r,j} = 0$ , and  $M_{r,n+1} = 1$ .

Canright [Can05] also used this technique but instead of using the metric function, he performed an exhaustive search over all possible column pairs. This was possible due to the fact that the target matrix in his case was the base conversion matrix only of size  $8 \times 8$ . As we saw in Section 2, our bottom matrix will be considerably larger, and hence we need to take another approach. We also need to consider the AIR and the AOR.

Satisfying the AIR. When performing the above algorithm we should keep track of the depth of the newly added XOR gates. This is done by having a vector  $D = (d_0 \dots d_{n-1})$  with the current depth of all inputs and newly added signals  $x_i$ . When the new signal  $x_n = x_i \oplus x_j$  is added, the delay of  $x_n$  is trivially  $d_n = \max(d_i, d_j) + 1$ . We then also restrict the algorithm such that if  $d_n > \max D$  then we are not allowed to add  $x_n$  as a new input signal. The AIR is hereby satisfied automatically.

Satisfying the AOR. Similarly, when adding a new input variable  $x_n$ , we need to check if a solution is theoretically possible. An elegant solution to this is presented in Theorem 2 in [LSL<sup>+</sup>19] where they calculate the shortest circuit given additional delay constraints.

**Probabilistic heuristic approach.** Since we cannot perform a full exhaustive search on the bottom matrix due to its size, we need to confine the number of pairs to keep and further evaluate. We have found that keeping the K best candidates (based on the original metric by Paar) and then randomly selecting which one to pick for the next XOR gate is a good strategy. In our simulations, this probabilistic approach gave us much smaller circuits than only considering the best metric candidates. Naturally, the execution time will be too

long if we pick a too large K, and conversely picking a too small K decreases the chances of deriving a good circuit. In practice we found that  $K = 2, \ldots, 6$  is a reasonable number of candidates to keep and try.

#### 3.3 Cancellation-allowed heuristic

The cancellation-free approaches give sub-optimal results, as it was shown by Boyar and Peralta in [BP10a], where they also introduced a new algorithm that allows cancellations. This was later improved by Reyhani et al in [RMTA18a]. Next, we briefly describe the basic idea of that heuristic.

#### 3.3.1 Basic cancellation-allowed algorithm [BP10a]

Every row of M is an n-bit binary vector. That vector can be seen as a n-bit integer value. We define that integer value as a **target point**. Thus, the matrix M can be seen as the column vector of m target points. The input signals  $\{x_0, \ldots, x_{n-1}\}$  can also be represented as integer values  $x_i = 2^i$ , for  $i = 0, \ldots, n-1$ .

Let the base set  $S = \{s_0, \ldots, s_{n-1}\} = \{1, 2, 4, \ldots, 2^n\}$  initially represent the input signals. The key function of the algorithm is the distance function  $\delta_i(S, y_i)$  that returns the smallest number of XOR gates needed to compute a target point  $y_i$  from the set of known points S. The algorithm keeps a vector  $\Delta = [\delta_0, \delta_1, \ldots, \delta_{n-1}]$  which is initially set to the Hamming weight minus one of the rows of M, which would be the number of XOR gates needed without any sharing of intermediate gates.

The algorithm then proceeds by combining two base points  $s_i$  and  $s_j$  in the base set S, and xor them together producing a candidate point  $c = s_i \oplus s_j$ . The selection of  $s_i$  and  $s_j$  is performed by an exhaustive search over all distinct pairs, and then for each candidate point, the sum of the distance vector  $\sum \delta_i$ , for  $i \in [0, n-1]$ , is calculated. Note that the distance functions  $\delta_i$  now is computed over the set  $S \cup \{c\}$ . The pair which gives the smallest distance sum is picked and S is updated  $S = S \cup \{c\}$ . In case there is a tie, the algorithm picks the pair that maximizes the Euclidean norm  $\sqrt{\sum \delta_i^2}$ , for  $i \in [0, n-1]$ . If there is a tie after this step too, the authors in [BP10a] investigated different strategies and concluded that all strategies tested performed similarly, and hence a simple random selection can be used. The algorithm then repeats the step of picking two new base points and calculating the distance vector sum, until the distance vector is all-zeros and the targets are all found. In the original description, there is also a notion of "preemptive" choices. A preemptive choice is a candidate point c such that it directly fulfils a target row in the matrix M. If such a candidate is found, it is immediately used as the new point and added to S.

Reyhani et al [RMTA18a] improved the original algorithm from [BP10a] by directly searching for preemptive candidates in each round and add them all to the set S before the "real" candidate is added and the distance vector recalculated. They also improved the tie resolution strategy and kept all the candidates that were equally good under the Euclidean norm and recursively tried them all, keeping the one that was best in the next round.

When the maximum depth maxD is a required constraint, the newly proposed algorithm in [LSL<sup>+</sup>19] can be used. However, in our simulations for bottom matrices, it didn't produce better results than the cancellation-free algorithm with randomization factor.

#### 3.4 Exhaustive search methods

In this section we present an algorithm for an efficient exhaustive search of the minimal circuit. The overall complexity is exponential in the number of input signals, and linear in

the number of output signals. From our experiments we can conclude that this exhaustive search algorithm can be readily applied to circuits of up to approximately 10 input bits.

#### 3.4.1 Notations and data representation

Using the same integer representation of the rows of M, and the input signals  $x_i$  as in Section 3.3.1, we can re-phrase the basic problem statement: given the set of input points  $x_i$  we want to find the sequence of XORs on those points such that we get all the m wanted target points  $y_i$ , the rows of the matrix M, with the maximum delay maxD. Input and output points may have different delays  $d_i$  and  $e_i$ , respectively.

For data structures, we can store a set of  $2^n$  points as either a normal set, and/or as a bit-vector. The set makes it possible to loop through the points while the bit-mask representation is efficient to test set membership.

#### 3.4.2 Basic idea

The proposed exhaustive search algorithm is a recursive algorithm, iterating over the depths, starting at depth 1 and ending at maxD. At each depth D, we try to construct new points from the previous depths, thereby constructing circuits that are of exactly depth D. When all target points are found, we check the number of required XOR gates, keeping track of the smallest solution. We will need the following sets of points:

known[maxD+1] – the set of known points at certain depth D.

ignored[maxD+1] – the set of points that will be ignore at depth D.

targets - the set of target points.

candidates – the set of candidate points to be added to the set known at the current recursion step.

The initial set of known points is  $x_i$ , for  $i = 0 \dots n - 1$ , and the set of target points is  $y_i$ , for  $i = 0 \dots m - 1$ . AIR is met by initially placing the input point  $x_i$  to the known set at depth  $d_i$ . AOR is satisfied by setting the point  $y_i$  with output delay  $e_i$  to the ignore list on all depth levels that are larger than  $e_i$ .

We will now explain the steps executed at each depth of the recursion, assuming that we currently are at depth D.

**Step 1** – Preemptive points. Check the known[D] set to see if any pair can be combined (XOR:ed) to give a target point not yet found. If all targets are found, or if we have reached maxD, we return from this level of the recursion.

Step 2 – Collect candidates. Form all possible pairs of points from the  $\mathtt{known}[0..D-1]$  sets, where at least one of the points is from  $\mathtt{known}[D-1]$ , and XOR the pair to derive a new point. If the derived point is in the set  $\mathtt{ignored}[D]$  then we skip it, otherwise we add it to candidate set.

Step 3 – In this step we try to add points from the candidate set to the known list, and call the algorithm recursively again. We start by trying to add 1 point and do the recursive call. If that's not solving the target points, we'll try to add 2 points, and so on until all combinations (or a maximum number of combinations) of the points in the candidate set have been tried.

#### 3.4.3 Ignored points and other optimizations

In step 2, we check the candidate set against the ignored [D] set, the set of ignored points at depth D. The ignored set is constructed from a set of rules; Intersection: A candidate point p should be ignored if for all target points  $w_i$  we get  $(w_i \& p) \neq p$ . This means that the point p covers too many of the input variables, and is not covered by any of the points in the targets set; Forward Propagation: We can calculate all possible points on each level starting from the top level D = 0 with n known points and

going down to D = maxD. Those points that can never appear at some level d are then included into the ignored[d] set. If some target point w has another desired maximum delay  $e_i < maxD$ , then that point on the following depths should be ignored, i.e., we add w to  $ignored[e_i + 1..maxD]$ ; Sum of Direct Inputs: If any of the input signals  $x_i, x_j$  give the point  $p = x_i \oplus x_j$  on level d, then all consecutive levels > d must have the point p in the ignored list; Backward Propagation: As a last check, we can go backwards level by level, starting from d = maxD and ending at level d = 1, and for each allowed (not ignored) point on the level d we check whether there is still a not-ignored pair a, b at the previous levels (one of a or b must be on the level d-1) such that it gives  $p = a \oplus b$ . If not, then the point p should be added to the ignore[d] set; ignore Candidates: dynamically add a point w to the ignore[d] set if w has been one of the candidates at previous levels ignore d and ignore d set ignore d

#### 3.5 Remarks

Simulations show that regarding searching for the minimum solution the top matrix (with only 8 inputs) can be solved with the *exhaustive cancellation-allowed search* as in Section 3.4. The bottom matrix (with 18 inputs) is too large for a direct exhaustive search, and we should start with a *probabilistic cancellation-free heuristic* from Section 3.2, and then use a full exhaustive search for the ending part, when the Hamming weights of the remaining rows become small enough to perform the exhaustive search. This approach gave us the best result.

# 4 System of linear circuits with multiplexers

Assume we want to find a solution for the combined AES SBox, where the top and the bottom linear matrices need to be multiplexed based on the SBox direction. This means that the circuit for the combined linear expressions is basically doubled in size, plus the set of multiplexers. In this section we will show how to deal with multiplexed systems of linear expressions. We will show that the MUX and XOR gates can be considered in a combined way in order to achieve a very compact circuit.

#### 4.1 Floating multiplexers

Consider that for some signal Y we have to compute two linear expressions  $Y^F$  and  $Y^I$  for the forward and the inverse SBoxes respectively. Then we apply a multiplexer so that only one of the signals continues as Y. Assume further that the signals  $Y^F$  and  $Y^I$  share some part of the expression. Then it may be better to push that shared part after the multiplexer, and the resulting solution can be simplified.

For example, let  $Y^F = X_0 \oplus X_1$  and  $Y^I = X_0 \oplus X_2$ , then normally we should spend 2 XOR gates and 1 multiplexer, so that we get  $Y = MUX(\texttt{select}, X_0 \oplus X_1, X_0 \oplus X_2)$  with 3 gates. However, we can push the common part  $X_0$  after the multiplexer as follows:

$$Y = MUX(select, X_1, X_2) \oplus X_0,$$

then we get a circuit with only 2 gates. In general, one can pick any linear combination  $\Delta$  on input signals and make a substitution:

$$Y = MUX(\mathtt{select}, Y^F, Y^I) \to MUX(\mathtt{select}, Y^F \oplus \Delta, Y^I \oplus \Delta) \oplus \Delta,$$

where  $\Delta$  is then added to the linear matrix as an additional target signal to compute. If that substitution leads to a shorter circuit then we keep it. We should also choose such  $\Delta$  that the overall depth is not increased. Thus, various multiplexers will be "floating" over the depth of the circuit. Signals with  $\Delta \neq 0$  should have their maximum depth decreased by 1.

#### 4.1.1 Metrics and linear expressions to solve

We have n input signals  $X_1 ldots X_n$  and m output signals  $Y_1, ldots, Y_m$ , where each  $Y_i$  is represented in its most general form as a triple  $(A_i, B_i, C_i)$  such that

$$Y_i = A_i \oplus MUX(\mathtt{select}, B_i, C_i),$$

where  $A_i, B_i$ , and  $C_i$  are linear expressions on the input signals. We are allowed to modify the above expression as  $(A_i \oplus \Delta_i, B_i \oplus \Delta_i, C_i \oplus \Delta_i)$  for any  $\Delta_i$ , since the Boolean function of  $Y_i$  will not change.

Let ABC represent the linear matrix that describes all the rows  $A_i, B_i$ , and  $C_i$ , for i = 0, ..., m, such that

$$ABC \times X$$

gives the wanted linear system to realize using minimal number of gates and a given maxD. By choosing favorable values of  $\Delta_i$ , one can shrink the number of total gates, since some of the target points of ABC may become equal to each other, and hence ABC can be reduced by at least one row. Also, some of the targets may become 0 or having only one bit - i.e., they are equal to corresponding input signals. These targets are also removed from the linear system as they are trivial and cost zero gates. After the above reductions we get a system of linear expressions where all rows are distinct and have Hamming weight at least 2. As before, we interpret the rows of ABC as integers, and adding (XORing) a  $\Delta_i$  to the three rows  $A_i$ ,  $B_i$ , and  $C_i$  will change those three target points, but not the resulting  $Y_i$ .

Metric. The search for a good combination of  $\Delta s$  requires a lot of computations and it rapidly becomes infeasible to compute a minimal solution for each selection. Thus, we need to decide on a good metric that allows us to truncate the search space down to promising sets of  $\Delta s$ . We propose to adopt a metric that is based on the lower bound of the number of gates of a fixed system (when  $\Delta$  values are selected), and define the metric to be the number of rows of the reduced ABC matrix, plus the minimum number of extra gates needed to complete the circuit, such as multiplexers.

In the following we present several heuristic approaches to finding a good set of  $\Delta s$  while minimizing the metric.

#### 4.1.2 Iterative algorithms to find $\Delta s$ : metric $\rightarrow$ minimize

The below techniques only work for small n, but in our case they are readily applicable to the 8-input top matrix of the AES SBox.

Algorithm-A(k) – Select k triplets  $(A_i, B_i, C_i)$  and try to find matching  $\Delta_i$ s that minimize the metric. If some choice results in a smaller metric, we keep that choice and continue searching with the updated ABC matrix. The algorithm runs in a loop until the metric is not decreasing any more. Algorithm-A(1) is quite fast, and Algorithm-A(2) also has acceptable speed. For larger ks it becomes infeasible. Algorithm-A(k) works fine for a very quick/brief analysis of the given system but the result is quite unstable since for a random set of initial values of  $\Delta_i$ s the resulting metric fluctuates heavily.

**Algorithm-B** – unlike Algorithm-A this algorithm is trying to construct a linear system of expressions, starting from an empty set of knowns S and then trying to add new points to S one by one, until all targets of ABC become included in the set S. While testing whether a new candidate C should be added to S we loop through all  $(A_i, B_i, C_i)$  and for each one try to find a  $\Delta_i$  that minimizes the overall metric. This heuristic algorithm is a lot more stable and gives quite good results.

However, the smallest possible metric does not guarantee that the final solution will have the smallest number of gates, and the number of non-target intermediates needed is unclear. Thus, it would be a good idea to collect a number of promising systems whose metric is the smallest possible, then try to find the smallest solution amongst them. We will investigate this in the next section.

# 4.2 New generic heuristic technique for linear systems with floating multiplexers

If we generalize the idea of floating multiplexers and let them float even higher up in the circuit, and also sharing them wider, we could achieve better results. In this section we propose a generic heuristic algorithm that finds good circuits for such systems.

#### 4.2.1 Problem statement

We are given n-bit input signal  $X_n$ , binary matrices  $M_{m \times n}^F$  and  $M_{m \times n}^I$ , binary vectors  $A_n^F$ ,  $A_n^I$ ,  $B_m^F$ ,  $B_m^I$ , and vectors of delays  $D_n^X$  and  $D_m^Y$ . We want to find a smallest and shortest solution that computes the m-bit output signal Y:

$$Y^{F} = M^{F} \cdot (X \oplus A^{F}),$$

$$Y^{I} = M^{I} \cdot (X \oplus A^{I}),$$

$$Y = MUX(ZF, Y^{F} \oplus B^{F}, Y^{I} \oplus B^{I}),$$

where each input signal  $X_i$  has an input arrival delay  $D_i^X$  and each output signal  $Y_j$  must have the total delay  $at \ most \ D_j^Y$ .  $A^*$  and  $B^*$  are constant masking vectors for the input and output signals respectively (NOT-gates). ZF is the mux selector, when ZF=1 we pick the first  $(Y^F=$  "forward") output otherwise the second  $(Y^I=$  "inverse") output. We also assume there is a complement signal  $ZI=ZF\oplus 1$  that is also available as an input control signal.

#### 4.2.2 Preliminaries

Similar to our previous notation, we define a "point" to be tuple of a point value (.p) and a delay (.d):

$$point := \{ .p = [f(1 \ bit) | F(n \ bits) | i(1 \ bit) | I(n \ bits) ], .d = Delay \},$$

which is then translated into a 1-bit signal circuit

$$signal:=MUX(ZF, F \cdot X \oplus f, I \cdot X \oplus i),$$

with a total output delay point.d. I.e., F and I are linear combinations of the n-bit input X, and f and i are negate bits applied to the result in case the selector ZF is "forward" or "inverse", respectively. The n input points are then represented as:

input point

$$X_k := \{ .p = [A_k^F | \mathbf{2}^k | A_k^I | \mathbf{2}^k], .d = D_k^X \}, \text{ for } k = 0, ..., n-1,$$

and the target m points are:

target point

$$Y_k := \{ .p=[B_k^F | \mathbf{Y}_{\mathbf{k}}^F | B_k^I | \mathbf{Y}_{\mathbf{k}}^I], .d= \leq D_k^Y \}, \text{ for } k=0,\ldots,m-1.$$

We should also include the following 4 trivial points to the set of inputs:

$$\begin{array}{lll} \text{signal ZF} := \{.p = [1|\mathbf{0}|0|\mathbf{0}], .d = 0\}, & \text{signal 0} := \{.p = [0|\mathbf{0}|0|\mathbf{0}], .d = 0\}, \\ \text{signal ZI} := \{.p = [0|\mathbf{0}|1|\mathbf{0}], .d = 0\}, & \text{signal 1} := \{.p = [1|\mathbf{0}|1|\mathbf{0}], .d = 0\}. \end{array}$$

Given any two (ordered) points v and w there are at most 6 possible new points that can be generated based on the following gates:

```

\begin{split} & \texttt{MUX}(v,w) := \{ .\, \texttt{p=}[v.f|\mathbf{v}.\mathbf{F}|w.i|\mathbf{w}.\mathbf{I}], \ .\texttt{d=}D_{new} \}, \\ & \texttt{NMUX}(v,w) := \{ .\, \texttt{p=}[v.f\oplus 1|\mathbf{v}.\mathbf{F}|w.i\oplus 1|\mathbf{w}.\mathbf{I}], \ .\texttt{d=}D_{new} \}, \\ & \texttt{MUX}(w,v) := \{ .\, \texttt{p=}[w.f|\mathbf{w}.\mathbf{F}|v.i|\mathbf{v}.\mathbf{I}], \ .\texttt{d=}D_{new} \}, \\ & \texttt{NMUX}(w,v) := \{ .\, \texttt{p=}[w.f\oplus 1|\mathbf{w}.\mathbf{F}|v.i\oplus 1|\mathbf{v}.\mathbf{I}], \ .\texttt{d=}D_{new} \}, \\ & \texttt{XOR}(v,w) := \{ .\, \texttt{p=}[w.f\oplus v.f|\mathbf{w}.\mathbf{F}\oplus \mathbf{v}.\mathbf{F}|w.i\oplus v.i|\mathbf{w}.\mathbf{I}\oplus \mathbf{v}.\mathbf{I}], \ .\texttt{d=}D_{new} \}, \\ & \texttt{NXOR}(v,w) := \{ .\, \texttt{p=}[w.f\oplus v.f\oplus v.f\oplus v.f\oplus v.\mathbf{F}], \ .\mathbf{d=}D_{new} \}, \\ \end{split}

```

where  $D_{new} = \max\{v.d, w.d\}+1$ . Note that the inclusion of the 4 trivial points is important, since then we can limit the number of gate types to be considered. For example, a NOT-gate is then implemented as  $\mathtt{XOR}(v,1)$ , AND gate with ZF can be implemented as  $\mathtt{MUX}(v,0)$ , OR gate with ZI is  $\mathtt{MUX}(v,1)$ , etc.

#### 4.2.3 The floating multiplexers algorithm

We start with the set S of input points (of size n+4), and place all target points into the set T. At each step, we compute the set of candidate points C that is generated by applying the above 6 gates to any two points from the set S. Naturally, C should only contain unique points and exclude those already in S. We try to add one candidate point from C to S and compute the distances from S to each of the target points in T. Thereafter we compare metrics to decide which candidate point will be included into S at this step, and start over by calculating the possible candidates. The algorithm stops when the overall distance  $\delta$ -metric is S.

The metric consists of several values. The distance  $\delta(S, t_i)$  is the minimum number of basic gates (the above 6) required to get the target point  $t_i$  from the points in S, such that the delay is at most  $D_i^Y$ . Subsection 4.2.5 discusses how to compute  $\delta(S, t_i)$ . The applied metrics and their order of importance are then as follows:

$$\begin{split} \gamma &= (|S|-n-4) + \sum_{i=0}^{m-1} \delta(S,t_i) \to \min, \\ \delta &= \sum_{i=0}^{m-1} \left( \delta(S,t_i) - (\delta(S,t_i) == 1) \right) \to \max, \\ \tau &= \text{delay of the recent candidate point from } C \text{ added to } S \to \min, \\ \nu^2 &= \sum_{i=0}^{m-1} \left( \delta(S,t_i) - (\delta(S,t_i) == 1) \right)^2 \to \max. \end{split}$$

The metric  $\gamma$  is the *projected number of gates* in case there will be no more shared gates; that metric we should definitely minimize. In case there are several candidates that give the same value, then we look into the second metric  $\delta$ .

$\delta$  is the sum of distances excluding distances where only 1 gate is needed. Given the smallest  $\gamma$ , we must maximize  $\delta$ . The larger  $\delta$  the more opportunities to shrink  $\gamma$ . We exclude distances 1 because of the inclusion of the preemptive step that we will describe below. When we accept candidates to S one by one as described above, the metrics  $\delta$  and  $\gamma$  are similar, but will become distinct when we, in the next subsection, introduce a search tree where the size of |S| may differ.

$\tau$  selects the candidate having the minimum depth in case the above two metrics showed the same values for two candidates. In case there are no maximum depth constraints for target points then this metric is not needed.

$\nu$  is the Euclidean norm excluding the preemptive points (similar to  $\delta$ ). This is the last decision metric since it is not a very good predictor, a worse value may give a better result and vice versa. However, if there are two candidates with equal metrics  $\delta$ ,  $\gamma$ , and  $\tau$ , then ordering of the two candidates may be done based on  $\nu$ . An alternative approach in case of tie-candidates is to choose one of them randomly.

**Preemptive points.** If some distance  $\delta(S, t_i) = 1$  then we accept the point  $t_i$  into S immediately without the search through the candidates C. The inclusion of this step in the algorithm forces us to exclude such points from the metrics  $\delta$  and  $\nu$ .

In [RMTA18a] preemptive points were included into the metric, but we believe it was not fully correct. E.g., when two distance vectors  $\{1,2,\ldots\}$  and  $\{0,2,\ldots\}$  have the same projected gates, then they fall into a totally equal situation in terms of possible shared gates, thus they should result in the same  $\delta$ . The point with the distance 1 in the above vector will be included into the circuit immediately (preemptive point), and it does not give any advantage over the second choice where we have a point with the distance 0. Therefore, distances with the value 1 should be ignored in  $\delta$  and  $\mu$ , but they should be accounted in the projected gates  $\gamma$ , instead.

#### 4.2.4 Search tree

Additionally to the above algorithm, we propose to have a search tree where each node is a set S with metrics. Children of such a node are also nodes where S' is derived from S by adding one of the candidate point  $S \leftarrow C$ . Thus, every path from the root node to a leaf represents a sequence of accepted candidate points to the root set S. If, at some point, a leaf has metric  $\delta = 0$  then that leaf represents a possible solution path.

We keep a number of children nodes (in our experiments we kept at least 20-50 best children) whose metrics are the best (they may even have different projected gates  $\gamma$ ). We also define the maximum depth TD of the search tree (in our experiments we tried  $TD=1,\ldots,20$ ). When the tree at depth TD is constructed, we then examine the leaves and see where we get the best metric over all leaves at all different branches. Tracking back to the root, we then choose to keep the top branch that leads to the best leaf(s). Other top branches from the root are removed. We then advance the root node to the first child of the selected branch and try to extend the tree's depth again from the remaining leaves, thus, keeping the search tree at a constant depth TD.

If, at every depth of the tree, each leaf is extended with additional 20-50 sub-branches, then the number of leaves will increase exponentially. However, we can apply a **truncation** algorithm to the leaves before extending the tree to the next depth. We simply keep no more than a certain number of promising leaves that will be expanded to the next depth, and other, less promising leaves we just remove from the tree (in our experiments the truncation level was up to 400 leaves overall for the whole tree). This type of truncation makes it possible to select the best top branch of the root node by "looking further" basically at any depth TD. Notably, the complexity does not depend on the depth TD, but it depends on the truncation level.

**Truncation strategy.** In brief, we keep those leaves with the best metrics, but try to distribute nearly equal leaves among different branches, so that we keep as many *diverted solution paths* as possible.

#### 4.2.5 Computation of $\delta(S, t_i)$

The "heart" and the critical part of the algorithm is the subalgorithm to compute the distances  $\delta(S, t_i)$ , given a fresh S. There are many candidates to test at each step, and there are many branches to track, so we need to make this core algorithm as fast as possible.

Note that the length of a point (.p is an integer) is 2n + 2 bits, plus the delay value. We will ignore the delay (.d) value when doing Boolean operations over two points. Let us assign the number of possible points as:

$$N = 2^{2n+2}.$$

Let  $V_k[]$  be a vector of length N cells, each cell  $V_k[p]$  corresponds to a (2n+2)-bit point p represented as an integer index, and the value stored in the cell will be the minimum delay p.d of that point such that it can be derived from S with exactly k gates.

Set the initial vector  $V_0$  as  $\forall p \to V_0[p] = p.d$ , if  $p \in S$ , and  $V_0[p] = \infty$ , otherwise. Thereafter, the vector  $V_{k+1}$  can be derived from the previously derived vectors  $V_0 \dots V_k$  by applying the allowed 6 gates to points from some level  $0 \le l < k$  ( $V_l$ ) and the level k-l ( $V_{k-l}$ ), thus resulting in total l+(k-l)+1=k+1 gates. After a new  $V_{k+1}$  is derived, we simply check if it contains new distance values for the targets from T, and we repeat the procedure until all distances  $\delta(S,t_i)$  for all  $t_i$  in T are found. A high-level description of the algorithm is given in Algorithm 1, and in Appendix B.1 we provide a more detailed description alongside multiple computational tricks that can be made.

#### **Algorithm 1** Algorithm for computing $\delta(S, t_i)$

```

1: function Distances(S, T, max\delta) \rightarrow \Delta = \{\delta_i\}, i = 0, \dots, m-1\}

2:

Init \delta_i = \infty for i = 0, \ldots, m-1

Init \forall p : V_0[p] = p.d if p \in S, otherwise \infty

3:

Init k = 0

4:

while true do

5:

while \exists i : \delta_i = \infty and V_k[t_i] \leq t_i.d do

6:

7:

\delta_i = k

if \forall i : \delta_i < \infty then return OK

8:

if k \geq max\delta then return FAIL

9:

k \leftarrow k + 1

10:

11:

Init \forall p: V_k[p] = \infty

for all a, b : \mathbf{do}

12:

for p in \{MUX(a, b), NMUX(a, b), MUX(b, a), NMUX(b, a), XOR(a, b), NXOR(a, b)\} do

13:

for l \leftarrow \lfloor k/2 \rfloor to k-1 do

14:

d \leftarrow \max(V_{k-l-1}[a], V_l[b]) + 1

15:

V_k[p] \leftarrow \min(V_k[p], d)

16:

```

#### 4.2.6 Double and Useless points

"Double" points. When, at some step of the algorithm, we find a candidate point c that is already in S but now having a smaller depth, then the point c is kept in C and tested along with other candidates. If it turns that adding c to S gives the best metric, we add it to S. An alternative strategy would be to update the point c.p in S with the lower depth c.d and recalculate depths of dependent points. However, it is not clear what to do with the parent points that were used to generate that previous c.p in S. We leave this as an open question for further research.

"Useless" points. At the end of the algorithm (when  $\delta=0$ ), it could happen that S contains points that can be safely excluded while a solution can still be derived. As a final step, we try to remove points from S one by one and test if every target is reachable from the remaining S under the given depth constraints. In our experience this situation is rare, but it helped to remove 1-2 gates, mainly caused by "double" points.

The above problems with "double" and "useless" points are generic for such class of algorithms where certain depth constraints should be met, and Algorithm 1 in [LSL<sup>+</sup>19] also falls under this category.

# 5 Architectural improvements

Most known AES SBox architectures look quite similar, consisting of the Top and Bottom linear parts, and the middle non-linear part, as previously described in Section 2. In this section, we take that classic design and propose a number of improvements, along with a completely new architecture that focuses on low depth solutions.

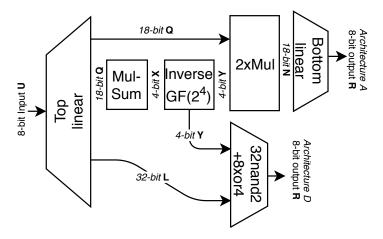

Figure 2: Difference between the architectures A and D.

#### **5.1** Two SBox architectures – Area and Depth

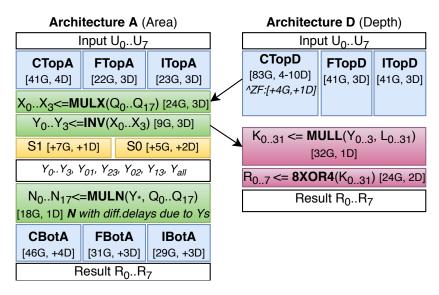

Referring to Figure 2, the architecture A (Area) is the classical one that implements designs based on tower and composite fields. It starts with the 8-bit input signal  $\mathbf U$  to the Top linear matrix, which produces a 22-bit signal  $\mathbf Q$  (as in [BP12]). We managed to reduce the number of needed  $\mathbf Q$ -signals to 18, and refactored the multiplication and linear summation block Mul-Sum to 24 gates and depth 3. (See Appendix D.2 for equations). The output from the Mul-Sum block is the 4-bit signal  $\mathbf X$  which is the input to the inversion over  $\mathrm{GF}(2^4)$ . The output from the inversion,  $\mathbf Y$ , is non-linearly mixed with the  $\mathbf Q$  signals, derived in the top matrix, and produces 18-bit signal  $\mathbf N$ . The final step is the Bottom linear matrix that takes 18-bit  $\mathbf N$  and linearly derives the output 8-bit signal  $\mathbf R$ . The top and bottom matrices incorporate the SBox's affine transformation that depends on the direction.

The new architecture D (Depth) is a new architecture where we tried to remove the bottom matrix and as a result shrinking the depth of the circuit as much as possible. The idea behind is that the bottom matrix only depends on the set of multiplications of the 4-bit signal Y and some linear combinations of the 8-bit input U. Thus, the result R can be achieved as follows:

$$\mathbf{R} = Y_0 \cdot M_0 \cdot \mathbf{U} \oplus \ldots \oplus Y_3 \cdot M_3 \cdot \mathbf{U},$$

where each  $M_i$  is a  $8 \times 8$  matrix representing 8 linear equations on the 8-bit input **U**, to be scalar multiplied by the  $Y_i$ -bit. Those 4x8 linear circuits can be computed as a 32-bits signal **L** in parallel with the circuit for the 4-bits of **Y**. The result **R** is achieved by

summing up four 8-bit sub-results. Therefore, in architecture D we get the depth 3 after the inversion step (critical path: MULL and 8XOR4 blocks), instead of the depth 5-6 in the architecture A. That new architecture D requires a bit more gates, since the assembling bottom circuit needs 56 gates: 32NAND2+8XOR4. The reward is the lower depth.

A more detailed sketch of the two architectures is given in Figure 3, that includes the components of the designs, delays and the number of gates.

**Figure 3:** More details on the architectures A and D.

#### 5.2 Six different scenarios of MULN

In the MULN block, where the 18-bit N-signals are computed, we need as input the 18-bit Q-signals and the inversion result Y. But we also need the following additional linear combinations of Y:  $Y_{02} = Y_0 \oplus Y_2$ ,  $Y_{13} = Y_1 \oplus Y_3$ ,  $Y_{23} = Y_2 \oplus Y_3$ ,  $Y_{01} = Y_0 \oplus Y_1$ ,  $Y_{00} = Y_{01} \oplus Y_{23}$  – these correspond to the signals M41-M45 in [BP12]. Thus, the Y vector is actually extended to 9 bits, and the delays of N bits become different, depending on which of the  $Y_i$  is used in the multiplication. For example, in the worst case, the delay of  $Y_{00}$  is +2 compared to the delay of  $Y_1$ . Thus, the resulting signals N will have different output delays. However, it is possible to compute these 5 additional Ys in parallel with the base signals  $Y_0, \ldots, Y_3$ . This will cost some extra gates, but then the +2 delay can either shrink down to +1 or +0. In general one can consider the following 6 scenarios:

- **S0**. We compute only the base signals  $Y_0, \ldots, Y_3$ , and the remaining  $\{Y_{01}, Y_{23}, Y_{02}, Y_{13}, Y_{00}\}$  we compute with XORs as above. The delay is +2 but it has the smallest number of gates:

- S1. Compute  $\{Y_{01}, Y_{23}\}$  in parallel, the delay is +1;

- **S2**. Compute  $\{Y_{02}, Y_{13}\}$  in parallel, the delay is +1;

- **S3**. Compute  $\{Y_{00}\}$  in parallel, the delay is +1;

- S4. Compute  $\{Y_{01}, Y_{23}, Y_{02}, Y_{13}\}$  in parallel, the delay is +1;

- **S5**. Compute  $\{Y_{01}, Y_{23}, Y_{02}, Y_{13}, Y_{00}\}$  in parallel, the delay is +0 as there is no signal left to compute afterwards.

In the next subsection we show how to find Boolean expressions for the above scenarios.

# 5.3 INV. Inversion over $GF(2^4)$

The inversion formulae are as follows:

$$\begin{split} Y_0 &= X_1 X_2 X_3 \oplus X_0 X_2 \oplus X_1 X_2 \oplus X_2 \oplus X_3, \\ Y_1 &= X_0 X_2 X_3 \oplus X_0 X_2 \oplus X_1 X_2 \oplus X_1 X_3 \oplus X_3, \\ Y_2 &= X_0 X_1 X_3 \oplus X_0 X_2 \oplus X_0 X_3 \oplus X_0 \oplus X_1, \\ Y_3 &= X_0 X_1 X_2 \oplus X_0 X_2 \oplus X_0 X_3 \oplus X_1 X_3 \oplus X_1. \end{split}$$

In [BP12] they found a circuit of depth 4 and 17 XORs, but we would like to shrink the depth even further by utilizing a wider range of standard gates.

We have adapted the algorithm from Section 4.2 to also find a small solution for the INV block. The idea is simple; each Y is a truth table of length 16 bits, based on a 4-bit input  $X_0,\ldots,X_3$ . We define our "point" to be a 16-bit value. All standard gates, AND, OR, XOR, MUX, NOT, including their negate versions, can be applied to any combination of "known" points (S), and distances to target points T can be computed in a similar manner as before. Using this slightly modified algorithm for floating multiplexers, we found a solution with only 9 gates and depth 3. The results are shown in Equation 2 and Table 2. The full listing of the formulae for scenarios S0-S5 can be found in D.2.

$$\begin{split} T0 &= \text{NAND}(X0, X2) & T3 &= \text{MUX}(X1, X2, 1) & Y1 &= \text{MUX}(T2, X3, T3) \\ T1 &= \text{NOR}(X1, X3) & T4 &= \text{MUX}(X3, X0, 1) & Y2 &= \text{MUX}(X0, T2, X1) \\ T2 &= \text{XNOR}(T0, T1) & Y0 &= \text{MUX}(X2, T2, X3) & Y3 &= \text{MUX}(T2, X1, T4) \end{split}$$

Table 2: Refactored INV block and scenarios S0-S5.

|                    | INV   | S0    | S1    | S2    | S3    | S4    | S5    |

|--------------------|-------|-------|-------|-------|-------|-------|-------|

| Std. area (gates)  | 9     | 14    | 16    | 17    | 16    | 19    | 19    |

| Std. depth (gates) | 3     | 5     | 4     | 4     | 4     | 4     | 3     |

| Tech. area (GE)    | 18.31 | 29.96 | 35.30 | 39.63 | 36.62 | 42.29 | 44.63 |

| Tech. depth(XORs)  | 2.31  | 4.31  | 3.31  | 3.77  | 3.76  | 3.59  | 3.11  |

In our tradeoff circuits we have used scenario S1, as it showed best results with respect to the area and depth. For the bonus circuits, we used S0 as it has the smallest area. For the fast circuit, only the INV formulae are needed. We also derived an alternative circuit for the inversion block without multiplexers, the results and formulae are given in B.2.

# 5.4 Additional Transformation Matrices (ATM)

We are solving the top matrices through exhaustive search and the bottom matrices with various heuristic techniques. The way those matrices look, naturally influence the final number of gates in the solution. Here we present a simple method to try different top and bottom matrices for the best solution.

Assume that the SBox is a black box and, when excluding the final addition of the constant, it performs the function:

$$SBox(x) = x^{-1} \cdot A_{8 \times 8},$$

where  $x^{-1}$  is the inverse element in the Rijndael field  $GF(2^8)$ , and the matrix  $A_{8\times8}$  is the affine transformation. In any field of characteristic 2: squaring, square root, and

multiplication by a constant – are linear functions, thus for a non-trivial choice  $(\alpha, \beta)$  we have:

$$Z(x) = \left(\alpha \cdot x^{2^{\beta}}\right)^{-1},$$

$$SBox(x) = \sqrt[2^{\beta}]{\alpha \cdot Z(x)} \cdot A_{8 \times 8}.$$

If the initial Top and Bottom matrices for the forward and inverse SBoxes were  $T_F, B_F, T_I, F_I$ , respectively, then one can choose any  $\alpha = 1, \ldots, 255$  and  $\beta = 0, \ldots, 7$ , and change the matrices as follows:

$$\begin{split} T_F' &= T_F \cdot E \cdot C_\alpha \cdot P_\beta \cdot E, \\ B_F' &= E \cdot A \cdot P_\beta^{-1} \cdot C_\alpha \cdot A^{-1} \cdot E \cdot B_F, \\ T_I' &= T_I \cdot E \cdot A \cdot C_\alpha \cdot P_\beta \cdot A^{-1} \cdot E, \\ B_I' &= E \cdot P_\beta^{-1} \cdot C_\alpha \cdot E \cdot B_I, \end{split}$$

where:

E – is the 8x8 matrix that switches bits endianness (in our circuits input and output bits are in Big Endian)

A- is the 8x8 matrix that performs the SBox's affine transformation

$C_{\alpha}$  – is the 8x8 matrix that multiplies a field element by the selected **constant**  $\alpha$

$P_{\beta}$  – is the 8x8 matrix that raises an element of the Rijndael field to the **power** of  $2^{\beta}$

$T_F/T_I$  – are the original (without modifications) 18x8 matrixes for the top linear transformation of the Forward/Inverse SBoxes, resp.

$B_F/B_I$  – are the original (without modifications) 8x18 matrixes for the bottom linear transformation of the Forward/Inverse SBoxes, resp.

There are 2040 choices for  $(\alpha, \beta)$  pair and each choice gives new linear matrices. It is easy to test all of them and find the best combination that gives the smallest SBox circuit. We have applied this idea to both the forward as well as the inverse SBox, for both architectures A and D. Note that a similar approach was recently and independently considered in [UHNA19] but in that work they only considered multiplication with a constant, and not squaring.

#### 5.4.1 ATM approach for the combined SBox

For the combined SBoxes we can apply the ATM approach to the forward and the inverse parts independently. This means that we have  $2040^2 = 4,161,600$  variants of linear matrices to test. We have focused on the architecture D, since there is no bottom matrix and thus we can do a more extensive search. We searched through all those 4 million variants and applied the heuristic algorithm from the Section 4.1 as a quick analysis method to select a set of around 4000 promising cases. We then applied the algorithm given in Section 4.2 to find a solution with floating multiplexers. In our case we have n=8 input bits and thus each point is encoded with 18 bits, and the complexity of calculating the distance  $\delta(S,t_i)$  is quadratic over  $N=2^{18}$  points. In the search we used the search tree with the maximum depth  $TD \leq 20$  and the truncation level of 400 leaves.

# 6 Results and comparisons

In this section we present our best solutions for the AES SBox, both forward and combined. The stand-alone inverse SBox is perhaps not as widely used, and those results can be found in Appendix C. We compare our area and depth using the techniques described

Table 3: Summary of which algorithms were used to derive the new SBoxes. BM is Bottom Matrix, and TM is Top Matrix.

|                                      |                             | Bonus            | and Tradoff (Arch. A)              | Fast            | (Arch. D, no BM)                     |

|--------------------------------------|-----------------------------|------------------|------------------------------------|-----------------|--------------------------------------|

| Section                              | Our contribution            | Fwd/Inv          | Combined                           | Fwd/Inv         | Combined                             |

| 3.2                                  |                             | -                |                                    |                 |                                      |

| Cancellation-free                    | Probabilistic approach with | $_{\mathrm{BM}}$ | BM + optimization of               |                 |                                      |

| heuristic                            | final exhaustive search.    |                  | MUXes by hand                      |                 |                                      |

| 3.3                                  |                             |                  |                                    |                 |                                      |

| Boyar's basic<br>algorithm and       |                             | Not used sine    | ce probabilistic heuristic with fi | inal exhaustive | search gave better resul             |

| [LSL+19]                             |                             |                  |                                    |                 |                                      |

| 3.4<br>Exhaustive                    | New contribution            | $_{ m TM}$       |                                    | $_{ m TM}$      |                                      |

| search                               | New contribution            | 1 M              |                                    | 1 M             |                                      |

| 4.1                                  | NT                          |                  |                                    |                 | T 11 11 11 11                        |

| Floating multi-<br>plexers (approxi- | New contribution            |                  |                                    |                 | In combination with<br>ATM to select |

| mative solution)                     |                             |                  |                                    |                 | preliminary set from                 |

| mative solution)                     |                             |                  |                                    |                 | ≈4M choices.                         |

| 4.2                                  |                             |                  |                                    |                 | 14 1111 011010001                    |

| Generic floating                     | New contribution            |                  | TM but applied after a             |                 | TM but applied after                 |

| multiplexers                         |                             |                  | first selection using ATM          |                 | first selection using                |

|                                      |                             |                  | approach.                          |                 | 4.1+ATM.                             |

| 5.2                                  |                             |                  |                                    |                 |                                      |

| MULN Scenario                        | New contribution            | S0(Bonus),       | S0(Bonus), S1(Tradeoff)            | INV             | INV                                  |

| used                                 |                             | S1(Tradeoff)     |                                    |                 |                                      |

| 5.4<br>Additional                    | New contribution. A         | Used             | Used                               | Used            | Used                                 |

| Transformation                       | similar approach was        | Used             | Osed                               | Used            | Used                                 |

| Matrixes                             | independently derived       |                  |                                    |                 |                                      |

| Maurines                             | in [UHNA19], but only       |                  |                                    |                 |                                      |

|                                      | constant multiplication was |                  |                                    |                 |                                      |

|                                      | considered.                 |                  |                                    |                 |                                      |

in Appendix A and where possible, we have recalculated the corresponding GE for other academic results for easier comparison. We present three different solutions for each SBox (forward, inverse, and combined): "fast", "tradeoff", and "bonus". The fast one is the solution with the lowest critical path, the tradeoff solution is a well-balanced trade-off between area and speed, and the bonus solution is given to establish a new record in terms of the smallest number of gates. Exact circuit expressions for all the derived solutions can be found in Appendix D, where we also indicate which algorithm was used in deriving the solution.

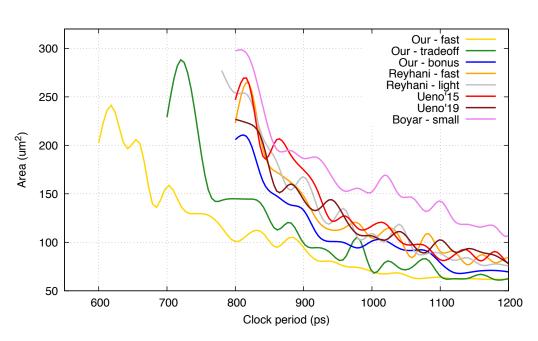

#### 6.1 Synthesis results

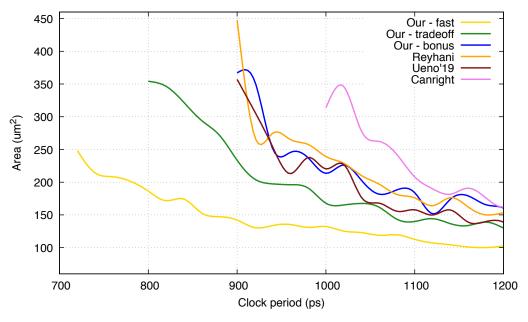

We have performed a synthesis of the results and compared with other recent academic work. The technology process is GlobalFoundries 22nm CSC20L [Glo19], and we have synthesized using Design Compiler 2017 from Synospys in topological mode with the compile\_ultra command. We also turned on the flag compile\_timing\_high\_effort to force the compiler to make as fast circuits as possible. In those graphs, the X axis is the clock period (in ps) and the Y axis is the resulting topology estimated area (in  $\mu m^2$ ). We have not restricted the available gates in any way, so the compiler is free to use non-standard gates e.g., a 3 input AND-OR gate. To get the graphs in the following subsections, we have started at a 1200 ps clock period ( $\sim 833$  MHz) and reduced the clock period by 20 ps until the timing constraints could not be met. We note that the area estimates by the compiler fluctuate heavily, and we believe that this is a result of the many different strategies the compiler has to minimize the depth. One strategy might be successful for say a 700 ps clock period, but a different strategy (which results in a significantly larger area) could be successful for 720 ps. There is also an element of randomness involved in the strategies for the compiler.

#### 6.2 Forward SBoxes

We have included a number of interesting previous results for comparison in Table 4. The most famous design by Canright is widely used and cited. Our tradeoff SBox is both

Forward (tradeoff)

$area/speed\ tradeoff$

$new\ record\ smallest$

Forward (bonus)

| Table 4: Forward SBo                    | x: Compariso | on of the resul | ts.        |                     |  |  |

|-----------------------------------------|--------------|-----------------|------------|---------------------|--|--|

| Forward SBox                            | Area Si      | ze/Gates        | Critical F | Critical Path/Depth |  |  |

|                                         | Std. gates   | Tech. GE        | Std. gates | Tech. XORs          |  |  |

| Previous Results                        |              |                 |            |                     |  |  |

| Canright [Can05]                        | 80X0+3       | 34ND+6NR        | 19X0+      | 3ND+1NR             |  |  |

| most famous design                      | 120          | 226.40          | 23         | 20.796              |  |  |

| Boyar et al [BP12]                      | 94X0         | )+34AD          | 13X        | O+3AD               |  |  |

| our starting point                      | 128          | 264.24          | 16         | 14.932              |  |  |

| Boyar et al [Boy]                       | 81X0+32ND    |                 | 21X        | 0+6ND               |  |  |

| $record\ smallest$                      | 113          | 220.73          | 27         | 23.508              |  |  |

| Ueno et al [UHS <sup>+</sup> 15]        | 91X0+48ND+   | 13NR (+4IV)     | 10X0+5N    | ND (+1IV)           |  |  |

| record fastest, formulas from [RMTA18a] | 151(+4)      | 270.71          | 15(+1)     | 12.449              |  |  |

| Reyhani-Light [RMTA18a]                 | 69X0+43ND-   | +7NR (+4IV)     | 16X0+4N    | VD (+1IV)           |  |  |

| at CHES 2018                            | 119(+4)      | 213.45          | 20(+1)     | 18.031              |  |  |

| Reyhani-Fast [RMTA18a]                  | 79X0+43ND    | +7NR (+4IV)     | 11X0+5N    | VD (+1IV)           |  |  |

| at CHES 2018                            | 129(+4)      | 236.75          | 16(+1)     | 13.449              |  |  |

| Ueno et al [UHNA19]                     | 90X0+4XN+100 | R+45AD (+10IV)  | 11X0+10R+  | +3AD (+1IV)         |  |  |

| recent result                           | 149(+10)     | 298.87          | 15(+1)     | 14.131              |  |  |

| Our Results                             |              |                 |            |                     |  |  |

| Forward (fast)                          | 77XO+1XN+4AD | )+37ND+5NR+6MX  | 7X0+1XN+1  | 1AD+2NR+1MX         |  |  |

| fast with depth 12                      | 130          | 243.04          | 12         | 10.496              |  |  |

61X0+8XN+27ND+5NR+8MX+2MI

58X0+6XN+27ND+5NR+6MX

216.75

195.10

111

102

8XO+2ND+1ND+2NR+1MX

18X0+2XN+1ND+2NR+1MX

12.263

22.263

14

24

Figure 4: Forward SBox: Synthesis results (the closer the curve is to the axes the better the result in terms of the area/speed trade-off).

| Table 5: | Combined | SBox: | Comparison | of | the | results. |

|----------|----------|-------|------------|----|-----|----------|

|----------|----------|-------|------------|----|-----|----------|

| Table 5: Combined SBox: Comparison of the results. |                |                     |             |               |  |  |  |

|----------------------------------------------------|----------------|---------------------|-------------|---------------|--|--|--|

| Combined SBox                                      | Area S         | Size/Gates          | Critical F  | Path/Depth    |  |  |  |

|                                                    | Std. gates     | Tech. GE            | Std. gates  | Tech. XORs    |  |  |  |

| Previous Results                                   |                |                     |             |               |  |  |  |

| Canright [Can05]                                   | 94X0+34ND+     | 6NR+16MX (+2IV)     | 20X0+3N     | D+20R+5NR     |  |  |  |

| $most\ famous\ design$                             | 150(+2)        | 297.64              | 30          | 25.644        |  |  |  |

| Reyhani et al [RMTA18b]                            | 81X0+32ND+40R  | R+16NR+16MI (+8IV)  | 17X0+2N     | D+30R+6NR     |  |  |  |

|                                                    | 149(+8)        | 290.13              | 28          | 23.608        |  |  |  |

| Ueno et al [UHNA19]                                | 112X0+7XN+100R | R+45AN+16MX (+10IV) | 11XO+3AN+10 | DR+2MX (+1IV) |  |  |  |

| recent result                                      | 190 (+10)      | 393.40              | 17(+1)      | 15.681        |  |  |  |

| Our Results                                        |                |                     |             |               |  |  |  |

| Combined (fast)                                    | 77X0+27XN+41   | ND+6NR+13MX+12MI    | 6X0+3XN+1ND | )+2NR+1MX+1MI |  |  |  |

| fast with depth 14                                 | 176            | 351.65              | 14          | 12.312        |  |  |  |

| Combined (tradeoff)                                | 70X0+21XN+2    | 7ND+5NR+17MX+5MI    | 7X0+4XN+1ND | )+2NR+1MX+1MI |  |  |  |

| $area/speed\ tradeoff$                             | 145            | 296.99              | 16          | 14.305        |  |  |  |

| Combined (bonus)                                   | 70X0+9XN+      | -27ND+5NR+16MX      | 15X0+4XN+   | 2ND+1NR+3MX   |  |  |  |

| new record smallest                                | 127            | 253.35              | 25          | 22.675        |  |  |  |

**Figure 5:** Combined SBox: Synthesis results (the closer the curve is to the axes the better the result in terms of the area/speed trade-off).

faster and smaller. We also included the work done by Boyar et al as their design was the starting point for our research.

The two results from CHES'18 by Reyhani et al are the most recent, and our tradeoff SBox has a similar area as their "lightweight" version in terms of GE, but around 30% faster. The tradeoff SBox is both smaller and faster than their "fast" circuit. Also, our "fast" version is faster by 25% than their "fast" version, while maintaining a decent area increase. The currently fastest SBox done by Ueno has 270.71GE and 12.449XORs depth, while our fast version is only 243GE with depth 10.496XORs, outperforming the known fastest circuit by around 23%.

We also included the current known smallest circuit (in terms of standard gates) done by Boyar in 2016, which has 113 gates (220.73GE) and depth 27 gates. Our "bonus" circuit is even smaller with only 102 gates and depth 24, reaching as low as 195.10GE. Synthesis results are shown in Figure 4.

#### 6.3 Combined SBoxes

Table 5 shows our results compared to the two previously known best results. Our tradeoff combined SBox has a similar size to that of [Can05] and [RMTA18b], but its speed is a lot faster due to a much lower depth of the circuit. The tradeoff circuit has depth 16 (in reality only 14.305XORs) and 145 gates (297GE), while Canright's combined SBox is of size 150(+2) gates (298GE) and the depth 30 (25.644XORs). The bonus solution in this paper has slightly smaller depth than the most recent result [RMTA18b] but is significantly smaller in size (127 vs 149(+8) standard gates). Finally, the proposed "fast" design using Architecture D has the best currently known depth. Our synthesis results are shown in the comparison Figure 5.

#### 7 Conclusions

In this paper we have introduced a number of heuristic and exhaustive search methods for minimizing the circuit realization of the AES SBox. We have proposed a novel idea on how to include the multiplexers of the combined SBox in the minimization algorithms, and derived smaller and faster circuit realizations for the forward, inverse, and combined AES SBox. We also introduced a new architecture where we remove the "irregular" bottom linear matrix, in order to derive a faster solution than previously known.

# 8 Acknowledgements

We would like to thank the Ericsson Research Data Center team for their patience and help with the compute resources that made this work possible, and our colleague Ben Smeets and all reviewers for providing valuable comments to the manuscript.

#### References

- [Art01] Artisan Components, Inc. TSMC 0.18μm Process 1.8-Volt SAGE-XTM Standard Cell Library Databook, 2001. http://www.utdallas.edu/~mx1095420/EE6306/Final%20project/tsmc18\_component.pdf.

- [BFP18] Joan Boyar, Magnus Find, and René Peralta. Small low-depth circuits for cryptographic applications. *Cryptography and Communications*, 11, 03 2018.

- [BHWZ94] Michael Bussieck, Hannes Hassler, Gerhard J. Woeginger, and Uwe T. Zimmermann. Fast algorithms for the maximum convolution problem. *Oper.*

- Res. Lett., 15(3):133-141, April 1994. http://citeseerx.ist.psu.edu/viewdoc/download?doi=10.1.1.3.5023&rep=rep1&type=pdf.

- [BMP08] Joan Boyar, Philip Matthews, and René Peralta. On the shortest linear straight-line program for computing linear forms. In Edward Ochmański and Jerzy Tyszkiewicz, editors, *Mathematical Foundations of Computer Science* 2008, pages 168–179, Berlin, Heidelberg, 2008. Springer Berlin Heidelberg.

- [BMP13] Joan Boyar, Philip Matthews, and René Peralta. Logic minimization techniques with applications to cryptology. *J. Cryptol.*, 26(2):280–312, April 2013.

- [Boy] Joan Boyar. Circuit minimization work. http://www.cs.yale.edu/homes/peralta/CircuitStuff/CMT.html.

- [BP10a] Joan Boyar and René Peralta. A New Combinational Logic Minimization Technique with Applications to Cryptology. In Paola Festa, editor, Experimental Algorithms, pages 178–189, Berlin, Heidelberg, 2010. Springer Berlin Heidelberg. https://eprint.iacr.org/2009/191.pdf.

- [BP10b] Joan Boyar and René Peralta. A new combinational logic minimization technique with applications to cryptology. In of Lecture Notes in Computer Science, pages 178–189. Springer, 2010.

- [BP12] Joan Boyar and René Peralta. A small depth-16 circuit for the AES S-Box. In Dimitris Gritzalis, Steven Furnell, and Marianthi Theoharidou, editors, SEC, volume 376 of IFIP Advances in Information and Communication Technology, pages 287–298. Springer, 2012. https://link.springer.com/chapter/10.1007/978-3-642-30436-1\_24.

- [Can05] D. Canright. A Very Compact S-Box for AES. In Josyula R. Rao and Berk Sunar, editors, Cryptographic Hardware and Embedded Systems CHES 2005, pages 441–455, Berlin, Heidelberg, 2005. Springer Berlin Heidelberg. https://www.iacr.org/archive/ches2005/032.pdf.

- [FAR06] FARADAY Technology Co. FSD0A\_A 90 nm Logic SP-RVT (Low-K) Process, 2006. https://www.cl.cam.ac.uk/research/srg/han/ACS-P35/documents/90nm-cell.pdf.

- [Glo19] GlobalFoundries. 22nm FDX process, 2019. https://www.globalfoundries.com/technology-solutions/cmos/fdx/22fdx.

- [Int01] International Business Machines Corporation. ASIC SA-27E Databook, Part I Base Library and I/Os. Data Book, 2001. http://people.csail.mit.edu/jasonm/nigel/base\_06-01.pdf.

- [IT88] Toshiya Itoh and Shigeo Tsujii. A fast algorithm for computing multiplicative inverses in GF(2M) using normal bases. *Inf. Comput.*, 78(3):171–177, September 1988. http://dx.doi.org/10.1016/0890-5401(88)90024-7.

- [JKL10] Yong-Sung Jeon, Young-Jin Kim, and Dong-Ho Lee. A compact memory-free architecture for the AES algorithm using resource sharing methods. *Journal of Circuits, Systems, and Computers*, 19:1109–1130, 2010.

- [LSL<sup>+</sup>19] Shun Li, Siwei Sun, Chaoyun Li, Zihao Wei, and Lei Hu. Constructing low-latency involutory mds matrices with lightweight circuits. *IACR Transactions on Symmetric Cryptology*, 2019(1):84–117, Mar. 2019.

- [MNG00] Microelectronics Group, Carl F. Nielsen, and Samuel R. Girgis. WPI 0.5 mm CMOS Standard Cell Library Databook, 2000. https://lsm.epfl.ch/files/content/sites/lsm/files/shared/Resources%20documents/data\_book.pdf.

- [NNT<sup>+</sup>10] Yasuyuki Nogami, Kenta Nekado, Tetsumi Toyota, Naoto Hongo, and Yoshitaka Morikawa. Mixed bases for efficient inversion in  $\mathbb{F}((2^2)^2)^2$  and conversion matrices of SubBytes of AES. pages 234–247, 08 2010.

- [oST01] National Institute of Standards and Technology. Advanced encryption standard. NIST FIPS PUB 197, 2001.

- [Paa97] Christof Paar. Optimized arithmetic for Reed-Solomon encoders. 04 1997.

- [Pet] Graham Petley. Internet resource: VLSI and ASIC Technology Standard Cell Library Design. http://www.vlsitechnology.org/index.html.

- [Rij00] Vincent Rijmen. Efficient implementation of the Rijndael S-Box. 2000. https://www.researchgate.net/publication/2621085\_Efficient\_Implementation\_of\_the\_Rijndael\_S-box.

- [RMTA18a] Arash Reyhani-Masoleh, Mostafa Taha, and Doaa Ashmawy. Smashing the implementation records of AES S-Box. *IACR Transactions on Cryptographic Hardware and Embedded Systems*, 2018(2):298–336, May 2018.

- [RMTA18b] Arash Reyhani-Masoleh, Mostafa M. I. Taha, and Doaa Ashmawy. New area record for the AES combined S-Box/inverse S-Box. 2018 IEEE 25th Symposium on Computer Arithmetic (ARITH), pages 145–152, 2018.

- [Sam00] Samsung Electronics Co., Ltd. STD90/MDL90 0.35µm 3.3V CMOS Standard Cell Library for Pure Logic/MDL Products Databook, 2000. https://www.digchip.com/datasheets/download\_datasheet.php?id=935791&part-number=STD90.

- [SMTM01] Akashi Satoh, Sumio Morioka, Kohji Takano, and Seiji Munetoh. A compact Rijndael hardware architecture with S-Box optimization. In Colin Boyd, editor, ASIACRYPT, volume 2248 of Lecture Notes in Computer Science, pages 239-254. Springer, 2001. http://antoanthongtin.vn/Portals/O/UploadImages/kiennt2/KyYeu/DuLieuNuocNgoai/1.Advances%20in% 20cryptology-Asiacrypt%202001-LNCS%202248/22480239.PDF.

- [UHNA19] Rei Ueno, Naofumi Homma, Yasuyuki Nogami, and Takafumi Aoki. Highly efficient  $GF(2^8)$  inversion circuit based on hybrid GF representations. *Journal of Cryptographic Engineering*, 9(2):101-113, Jun 2019.

- [UHS<sup>+</sup>15] Rei Ueno, Naofumi Homma, Yukihiro Sugawara, Yasuyuki Nogami, and Takafumi Aoki. Highly efficient GF(2<sup>8</sup>) inversion circuit based on redundant GF arithmetic and its application to AES design. In Tim Güneysu and Helena Handschuh, editors, Cryptographic Hardware and Embedded Systems CHES 2015 17th International Workshop, Saint-Malo, France, September 13-16, 2015, Proceedings, volume 9293 of Lecture Notes in Computer Science, pages 63–80. Springer, 2015.

# A Area and speed measurement methods

Firstly, we introduce some notations. Gate names are written in capital letters GATE (examples: AND, OR). The notation mGATEn means m gates of type GATE, each of which has n inputs (example: XOR4, 8XOR4, NAND3, 2AND2). When the number of inputs n is missing then the assumption is that the gate has minimum inputs, usually only 2 (3 for MUX).

Cells that are constructed as gates combinations can be described as GATES1-GATE2, meaning that we first perform one or more gates on the first level GATES1, then the result goes to the gate on the second level 2. Example: NAND2-NOR2, means that the cell has 3 inputs (a, b, c) and the corresponding Boolean function is NOR2(a, NAND2(b, c)).

We present two different methods of comparing circuits; the standard method and the technology method.

#### A.1 Standard method

Cells. The basic elements that are considered in the standard method are:

{XOR, XNOR, AND, NAND, OR, NOR, MUX, NMUX, NOT}.

**Negotiation of NOT gates.** In some places of the circuit there is a need to use the inverted version of a signal. This can be done in several ways, without the explicit use of a NOT gate. Here we list a few of them.

Method 1. One way to implement a NOT gate is to change the previous gate that generates that signal to instead produce an inverted signal. For example, switch XOR into XNOR, AND into NAND, etc.

Method 2. In several technologies some gates can produce both the straight signal and the inverted version. For example, XOR gates in many implementations produce both signals simultaneously, and thus the inverted value is readily available.

Method 3. We can change the gates following the inverted signal such that the resulting scheme would produce the correct result given the inverted input, using e.g. De Morgan's laws

Summarizing the above, we believe that NOT gates may be ignored while evaluating a circuit with the standard method, since it can hardly be counted as a full gate. However, for completeness, we will print out the number of NOT gates in the resulting tables.

**Area.** For area comparisons the number of basic elements is counted without any size distinction between them. The NOT-gates are ignored.