# Fixslicing: A New GIFT Representation

# Fast Constant-Time Implementations of GIFT and GIFT-COFB on ARM Cortex-M

Alexandre Adomnicai<sup>1,2</sup>, Zakaria Najm<sup>1,2,3</sup> and Thomas Peyrin<sup>1,2</sup>

<sup>1</sup> Nanyang Technological University, Singapore

<sup>2</sup> Temasek Laboratories, Singapore

<sup>3</sup> TU Delft, Netherlands

firstname.lastname@ntu.edu.sg

**Abstract.** The GIFT family of lightweight block ciphers, published at CHES 2017, offers excellent hardware performance figures and has been used, in full or in part, in several candidates of the ongoing NIST lightweight cryptography competition. However, implementation of GIFT in software seems complex and not efficient due to the bit permutation composing its linear layer (a feature shared with PRESENT cipher).

In this article, we exhibit a new non-trivial representation of the GIFT family of block ciphers over several rounds. This new representation, that we call *fixslicing*, allows extremely efficient software bitsliced implementations of GIFT, using only a few rotations, surprisingly placing GIFT as a very efficient candidate on micro-controllers. Our constant time implementations show that, on ARM Cortex-M3, 128-bit data can be ciphered with only about 800 cycles for GIFT-64 and about 1300 cycles for GIFT-128 (assuming pre-computed round keys). In particular, this is much faster than the impressive PRESENT implementation published at CHES 2017 that requires 2116 cycles in the same setting, or the current best AES constant time implementation reported that requires 1617 cycles. This work impacts GIFT, but also improves software implementations of all other cryptographic primitives directly based on it or strongly related to it. For example, we observe that with the fixslicing technique GIFT-COFB performs faster than Ascon on ARM Cortex-M processors.

Keywords: GIFT  $\cdot$  implementation  $\cdot$  bitslice  $\cdot$  lightweight cryptography

# 1 Introduction

In parallel to the rise of pervasive computing and IoT, lightweight cryptography has naturally been a very hot topic in the past decade. Many new primitives have been proposed, from block ciphers to hash functions and authenticated encryption schemes, for various goals such as minimization of area, energy or power consumption, latency, etc. One can remark that there is no single algorithm that is more efficient than all others on every possible platform. Even though designers try to produce a primitive aiming at a particular class of platforms while maintaining good performance otherwise, we can generally observe that hardware-oriented ciphers tend to be less efficient on software and vice-versa. For example, the NSA did not propose only a single lightweight block cipher, but two of them [BSS<sup>+</sup>15]: one oriented for constrained hardware platforms (SIMON) and one oriented for constrained software platforms (SPECK).

In hardware, it seems that the community is reaching a limit in terms of performances, with recent schemes [BSS<sup>+</sup>15, BJK<sup>+</sup>16, BPP<sup>+</sup>17] that can be implemented efficiently using a very small data-path (minimizing area and power), while allowing also efficient trade-offs

for fast and low-energy implementations. Yet, constrained software platforms such as small micro-controllers will play a very important role in the future. Even though hardware-oriented designs use a very small total number of bitwise operations when compared to classical designs such as AES, their situation in software is not so bright: many of these ciphers use hardware-friendly diffusion layers and an important number of cycles will be required to move these bits around, without much possibility to benefit from vectorization. This is especially true for ciphers using bit permutation such as PRESENT [BKL<sup>+</sup>07] or GIFT [BPP<sup>+</sup>17]. Since this bit permutation is basically free in hardware (it consists of simple wirings), designers concentrated on how to maximize security when choosing this permutation layer. For example, GIFT permutation layer has been chosen with security as the only criterion (more precisely, maximizing its resistance against differential and linear attacks).

When high parallelism can be achieved in the operating mode where the primitive will be placed, one can always use highly bitsliced implementations (see performances of SIMON, SKINNY and GIFT on recent Intel processors with AVX2 instructions [BPP<sup>+</sup>17]) that can lead to excellent performance: these ciphers again use a very small number of bitwise operations and the high parallelism will allow to strongly reduce the cycles wasted in moving bits around by unrolling the implementation. However, this strategy will not be applicable in the case of constrained micro-controllers, as these devices will not offer enough registers to perform such highly bitsliced implementations efficiently. These highly bitsliced implementations will also not be possible for serial operating modes, which are quite widespread in practice and are even more relevant for lightweight cryptography as it can save some area.

It remains rather unexplored how efficient hardware-oriented ciphers can be in software. Yet, this topic is quite important with the ongoing NIST LightWeight Cryptography (NIST LWC) competition, that started in 2018, with the goal of selecting the future authenticated encryption standard(s) for constrained environments. A first answer was given at CHES 2017, with a new very efficient implementation of PRESENT cipher on various micro-controllers [RAL17]. It is based on a decomposition of the permutation layer over two consecutive rounds, resulting in a more software-friendly representation.

However, PRESENT has a rather low security margin with regards to linear cryptanalysis and its advanced extensions. It also has the disadvantage to only come in a 64-bit block version, which is to be avoided [BL16] unless a Beyond-Birthday-Bound (BBB) operating mode can be used (generally much more costly). Actually, one can observe that none of the NIST LWC candidates use PRESENT as internal primitive, even though it is widely considered as one of the first lightweight ciphers. Recently, at CHES 2017, the GIFT family of block ciphers was proposed to correct these two issues with PRESENT. GIFT has a 128-bit version and provides a much stronger resistance against linear cryptanalysis than PRESENT, thanks to a careful choice of its S-box, its diffusion layer and how they operate together. It has actually been used as a basic block for several NIST LWC candidates, such as ESTATE [CDJ<sup>+</sup>19a], GIFT-COFB [BCI<sup>+</sup>19], HYENA [CDJN19], LOTUS-AED [CDJ<sup>+</sup>19b], LOCUS-AED [CDJ<sup>+</sup>19b], SIMPLE [GL19], SUNDAE-GIFT [BBP<sup>+</sup>19] and TGIF [IKM<sup>+</sup>19]. The problem is that software performance of GIFT is believed to be poor on microcontrollers, because even using table-based implementations, moving the bits around for the diffusion layer will cost many expensive rotations, shifts, masks, exclusive-ORs, etc. To the best of our knowledge, no micro-controller implementation has been previously reported for GIFT.

**Our Contributions.** In this article, we propose a new non-trivial representation of both versions of the GIFT cipher over several rounds. More precisely, we show how the seemingly-complex bit permutation of GIFT-64 can be rewritten over 4 consecutive rounds, using only a few simple operations. This new very clean representation, that we named *fixslicing*, allows an efficient bitsliced implementation of GIFT-64 on ARM Cortex-M3,

requiring only about 800 cycles to cipher two 64-bit input blocks. Our setting assumes that round keys are precomputed, but we also provide an efficient implementation of the GIFT-64 key schedule.

The situation is more difficult for GIFT-128, as its bit permutation operates on twice as many bits. Yet, a more systematic search approach led to a new representation of GIFT-128 over 5 rounds, again using only a few simple operations. This new very clean representation allows an efficient bitsliced implementation of GIFT-128 on ARM Cortex-M3, requiring only about 1300 cycles to encrypt one single 128-bit input block.

Our implementations show that GIFT is very efficient in software, as they are much faster than the impressive PRESENT implementation published at CHES 2017 that requires 2116 cycles in the same setting, or the current best AES constant time implementation reported that requires 1617 cycles. This work impacts GIFT, but also all other cryptographic primitives directly based on it or strongly related to it. In particular, we benchmarked that GIFT-COFB runs at 96 cycles per byte on ARM Cortex-M3 for long messages, placing this scheme as a very fast candidate. Notably, it outperforms the ARM optimized implementation of Ascon [DEMS19], another NIST LWC submission, on this platform.

# 2 The GIFT family of block ciphers

In this section, we will describe the  $\mathsf{GIFT}$  family of block ciphers but refer to  $[\mathsf{BPP}^+17]$  for the full specifications.

GIFT is a family of lightweight block ciphers, with two members: GIFT-64 and GIFT-128 which have a block size of 64 and 128 bits respectively. They are composed of a Substitution-Permutation Network (SPN) with a key length of 128-bit. They are 28-round and 40-round iterative block ciphers respectively, with identical round function.

There are different ways to perceive GIFT-64 and GIFT-128. The classical one is to represent it with an SPN view (see Section 2 of [BPP<sup>+</sup>17] for a graphical representation), which looks like a PRESENT-like cipher with 16 (or 32) 4-bit S-boxes and a 64-bit (or 128-bit) bit permutation (see Figure 1 that illustrates 2 rounds of GIFT-64). Since we will be proposing new bitsliced implementations, we will be using the bitsliced description instead, which is similar to Appendix A of the GIFT paper.

Instead of collecting the input stream S-box per S-box, we can also consider that the data arrives already in bitsliced ordering. This changes absolutely nothing to the quality of the cipher, as a bit permutation is simply applied at the start (plaintext) and at the end (ciphertext) of the encryption process (to compensate for the state bitslice packing/unpacking). We note that such ciphers have been already used in some NIST LWC candidates such as GIFT-COFB [BCI<sup>+</sup>19]. We will denote GIFTb-64 and GIFTb-128 the bitsliced-input versions of GIFT-64 and GIFT-128 respectively.

#### 2.1 Round function

Each round of  $\mathsf{GIFT-64}$  (or  $\mathsf{GIFT-128}$ ) consists of 3 steps: SubCells, PermBits, and AddRoundKey.

<u>Initialization</u>. The 64-bit (or 128-bit) plaintext is loaded into the cipher state S which will be expressed as 4 16-bit (or 32-bit) segments. In the perspective of a 2-dimensional array, the bit ordering is from top-down, then right to left. Namely, for GIFT-64, we have:

$$S = \begin{bmatrix} S_0 \\ S_1 \\ S_2 \\ S_3 \end{bmatrix} \leftarrow \begin{bmatrix} b_{60} & \cdots & b_8 & b_4 & b_0 \\ b_{61} & \cdots & b_9 & b_5 & b_1 \\ b_{62} & \cdots & b_{10} & b_6 & b_2 \\ b_{63} & \cdots & b_{11} & b_7 & b_3 \end{bmatrix}$$

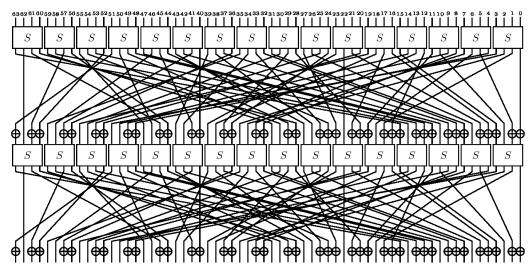

Figure 1: 2 rounds of GIFT-64 (from https://www.iacr.org/authors/tikz/).

while for GIFT-128 we have:

$$S = \begin{bmatrix} S_0 \\ S_1 \\ S_2 \\ S_3 \end{bmatrix} \leftarrow \begin{bmatrix} b_{124} & \cdots & b_8 & b_4 & b_0 \\ b_{125} & \cdots & b_9 & b_5 & b_1 \\ b_{126} & \cdots & b_{10} & b_6 & b_2 \\ b_{127} & \cdots & b_{11} & b_7 & b_3 \end{bmatrix}.$$

The 128-bit secret key is loaded into the key state KS partitioned into 8 16-bit words. In the perspective of a 2-dimensional array, the bit ordering is from right to left, then bottom-up.

$$KS = \begin{bmatrix} W_0 & \parallel & W_1 \\ W_2 & \parallel & W_3 \\ W_4 & \parallel & W_5 \\ W_6 & \parallel & W_7 \end{bmatrix} \leftarrow \begin{bmatrix} b_{127} & \cdots & b_{112} & \parallel & b_{111} & \cdots & b_{98} & b_{97} & b_{96} \\ b_{95} & \cdots & b_{80} & \parallel & b_{79} & \cdots & b_{66} & b_{65} & b_{64} \\ b_{63} & \cdots & b_{48} & \parallel & b_{47} & \cdots & b_{34} & b_{33} & b_{32} \\ b_{31} & \cdots & b_{16} & \parallel & b_{15} & \cdots & b_2 & b_1 & b_0 \end{bmatrix}$$

<u>SubCells.</u> The substitution layer of 16 (or 32) identical 4-bit S-boxes can be applied in parallel with the following operations.

$$\begin{split} S_1 \leftarrow S_1 \oplus (S_0 \ \land \ S_2) \\ S_0 \leftarrow S_0 \oplus (S_1 \ \land \ S_3) \\ S_2 \leftarrow S_2 \oplus (S_0 \ \lor \ S_1) \\ S_3 \leftarrow S_3 \oplus S_2 \\ S_1 \leftarrow S_1 \oplus S_3 \\ S_3 \leftarrow \neg \ S_3 \\ S_2 \leftarrow S_2 \oplus (S_0 \ \land \ S_1) \\ \{S_0, S_1, S_2, S_3\} \leftarrow \{S_3, S_1, S_2, S_0\}, \end{split}$$

where  $\land$ ,  $\lor$  and  $\neg$  are logical AND, OR and NOT operation respectively.

<u>PermBits.</u> The bit permutation of  $\mathsf{GIFT}$  has the special property that each bit located in a slice *i* remains in the same slice through this permutation. Now, different 16-bit (or

32-bit) permutations are applied to each  $S_i$  independently. They map a bit located at position j in slice i to position  $P_i(j)$  in the same slice i. We provide in Tables 1 and 2 the  $P_i(j)$  values for GIFT-64 and GIFT-128 respectively.

| i        | 0  |    | 2  | -  |    |    |    | 7  |    | -  |    |    |    | 13 | 14 | 15 |

|----------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| J        |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| $P_0(j)$ | 0  | 12 | 8  | 4  | 1  | 13 | 9  | 5  | 2  | 14 | 10 | 6  | 3  | 15 | 11 | 7  |

| $P_1(j)$ | 4  | 0  | 12 | 8  | 5  | 1  | 13 | 9  | 6  | 2  | 14 | 10 | 7  | 3  | 15 | 11 |

| $P_2(j)$ | 8  | 4  | 0  | 12 | 9  | 5  | 1  | 13 | 10 | 6  | 2  | 14 | 11 | 7  | 3  | 15 |

| $P_3(j)$ | 12 | 8  | 4  | 0  | 13 | 9  | 5  | 1  | 14 | 10 | 6  | 2  | 15 | 11 | 7  | 3  |

Table 1: Specifications of GIFT-64 bit permutation.

| j        | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

|----------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| $P_0(j)$ | 0  | 24 | 16 | 8  | 1  | 25 | 17 | 9  | 2  | 26 | 18 | 10 | 3  | 27 | 19 | 11 |

| $P_1(j)$ | 8  | 0  | 24 | 16 | 9  | 1  | 25 | 17 | 10 | 2  | 26 | 18 | 11 | 3  | 27 | 19 |

| $P_2(j)$ | 16 | 8  | 0  | 24 | 17 | 9  | 1  | 25 | 18 | 10 | 2  | 26 | 19 | 11 | 3  | 27 |

| $P_3(j)$ | 24 | 16 | 8  | 0  | 25 | 17 | 9  | 1  | 26 | 18 | 10 | 2  | 27 | 19 | 11 | 3  |

|          |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| j        | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

| $P_0(j)$ | 4  | 28 | 20 | 12 | 5  | 29 | 21 | 13 | 6  | 30 | 22 | 14 | 7  | 31 | 23 | 15 |

| $P_1(j)$ | 12 | 4  | 28 | 20 | 13 | 5  | 29 | 21 | 14 | 6  | 30 | 22 | 15 | 7  | 31 | 23 |

| $P_2(j)$ | 20 | 12 | 4  | 28 | 21 | 13 | 5  | 29 | 22 | 14 | 6  | 30 | 23 | 15 | 7  | 31 |

| $P_3(j)$ | 28 | 20 | 12 | 4  | 29 | 21 | 13 | 5  | 30 | 22 | 14 | 6  | 31 | 23 | 15 | 7  |

AddRoundKey. This step consists of adding the round key and round constant. Two 16-bit (or 32-bit) segments U, V are extracted from the key state as the round key: RK = U || V. Then, for the addition of round key, U and V are XORed to  $S_1$  and  $S_0$  of the cipher state respectively for GIFT-64, or  $S_2$  and  $S_1$  of the cipher state respectively for GIFT-128:

> $S_1 \leftarrow S_1 \oplus U, \quad S_0 \leftarrow S_0 \oplus V \quad \text{for GIFT-64}$  $S_2 \leftarrow S_2 \oplus U, \quad S_1 \leftarrow S_1 \oplus V \quad \text{for GIFT-128.}$

For the addition of round constant,  $S_3$  is updated as follows:

| $S_3 \leftarrow S_3 \oplus$ 0x80XY              | for GIFT-64  |

|-------------------------------------------------|--------------|

| $S_3 \leftarrow S_3 \oplus \texttt{0x800000XY}$ | for GIFT-128 |

where the byte  $XY = 00c_5c_4c_3c_2c_1c_0$ .

#### 2.2 Key schedule and round constants

The key schedule and round constants are the same for both versions of GIFT, the only difference is the round key extraction. A round key is *first* extracted from the key state before the key state update. For GIFT-64, two 16-bit words of the key state are extracted as the round key RK = U || V

$$U \leftarrow W_6, V \leftarrow W_7,$$

while for GIFT-128, four 16-bit words of the key state are extracted as the round key RK = U || V.

$$U \leftarrow W_2 || W_3, V \leftarrow W_6 || W_7$$

The key state is then updated as follows,

| $W_0$          | $W_1$ |              | $W_6 \gg 2$ | $W_7 \gg 12$ |   |

|----------------|-------|--------------|-------------|--------------|---|

| $W_2$<br>$W_4$ | $W_3$ | ,            | $W_0$       | $W_1$        |   |

| $W_4$          | $W_5$ | $\leftarrow$ | $W_2$       | $W_3$        | , |

| $W_6$          | $W_7$ |              | $W_4$       | $W_5$        |   |

where  $\gg i$  is an *i* bits right rotation within the 16-bit word.

The round constants are generated using a 6-bit affine LFSR, whose state is denoted as  $c_5c_4c_3c_2c_1c_0$ . Its update function is defined as:

```

c_5 \|c_4\| c_3 \|c_2\| c_1 \|c_0 \leftarrow c_4 \|c_3\| c_2 \|c_1\| c_0 \|c_5 \oplus c_4 \oplus 1.

```

The six bits are initialized to zero, and updated *before* being used in a given round. The values of the constants for each round are given in the table below, encoded to byte values for each round, with  $c_0$  being the least significant bit.

| Rounds  | Constants                                       |

|---------|-------------------------------------------------|

| 1 - 16  | 01,03,07,0F,1F,3E,3D,3B,37,2F,1E,3C,39,33,27,0E |

| 17 - 32 | 1D,3A,35,2B,16,2C,18,30,21,02,05,0B,17,2E,1C,38 |

| 33 - 48 | 31,23,06,0D,1B,36,2D,1A,34,29,12,24,08,11,22,04 |

# 3 Naive bitsliced implementation of GIFT

Naive bitsliced implementations of the GIFT family of block ciphers can be achieved by following straightforwardly the specifications. First, in the case of GIFT-64 and GIFT-128, one has to rearrange the inputs in their bitsliced representation. This can be done using the SWAPMOVE technique [MPC00]:

$$\begin{split} \texttt{SWAPMOVE}(A,B,M,n):\\ T &= (B \oplus (A \gg n)) \ \land \ M\\ B &= B \oplus T\\ A &= A \oplus (T \ll n) \end{split}$$

which consists in swapping the bits in B masked by M with the bits in A masked by  $(M \ll n)$ . Regarding the substitution layer, the 4-bit S-boxes can be computed in parallel in only 13 operations as described in Section 2. The main difficulty lies in the diffusion layer as it refers to the least bitslice-friendly operation. For the sake of clarity, let us consider the case of GIFT-64. In order to apply the 16-bit permutation  $P_0$  to  $S_0$ , a basic approach would be to move the bits using masks and shifts, resulting in the following operations:

which requires about 27 cycles on ARM Cortex-M processors. In the same way,  $P_1, P_2$  and  $P_3$  can be implemented in approximately 14, 27 and 18 cycles, respectively. Therefore, the diffusion layer requires about 100 cycles for a single round. This highlights why ciphers using bit permutation are generally considered inappropriate for software implementations on micro-controllers.

Still, it is possible to minimize the impact on performances by operating on several blocks in parallel for 32-bit (and above) architectures. In order to give some insights on how GIFT performs on ARM Cortex-M3 and M4 using the naive bitsliced implementation, we benchmarked a code fully written in C language, compiled by arm-none-eabi-gcc 9.2.1 using the flag -03 for optimized speed results, on the STM32L100C and STM32F407VG development boards. Note that our benchmark simply measures the execution time to expand the key and to encrypt 128-bit data, without any operating mode. Implementation results are listed in Table 3. For encryption functions, the data in ROM refers to precomputed round constants while under RAM usage, I/O refers to the amount of memory needed to store the input and ouput plus the temporary variables (excluding the round keys).

| Versions of <b>Gi</b> 1.        |          |         |                |         |         |                        |       |  |

|---------------------------------|----------|---------|----------------|---------|---------|------------------------|-------|--|

| Algorithm                       | Parallel | Speed   | (cycles/block) | ROM     | (bytes) | $\mathbf{RAM}$ (bytes) |       |  |

| Aigorithiin                     | Blocks   | M3      | M4             | Code    | Data    | I/O                    | Stack |  |

| GIFT-64 key exp.                | -        | 2 2 9 6 | 2 304          | 392     | 0       | 112                    | 24    |  |

| $GIFTb-64\ \mathrm{encryption}$ | 2        | 5710    | 5729           | 1 812   | 28      | 52                     | 48    |  |

| GIFT-64 encryption              | 2        | 6008    | 6027           | 2724    | 28      | 52                     | 48    |  |

| GIFT-128 key exp.               | -        | 3 4 3 3 | 3479           | 316     | 0       | 320                    | 24    |  |

| GIFTb-128 encryption            | 1        | 21872   | 22432          | 2 188   | 40      | 52                     | 48    |  |

| GIFT-128 encryption             | 1        | 22480   | 23040          | 3 0 8 8 | 40      | 52                     | 48    |  |

Table 3: Naive bitsliced implementation results on ARM Cortex-M3 and M4 for various versions of GIFT

As expected, the result is that GIFT is not well suited for software bitsliced implementations on micro-controllers. While our C implementation requires about 10000 cycles to encrypt 128-bit data using GIFT-64, twice as much are required when using GIFT-128. This gap is due to the fact that, on top of having more rounds than GIFT-64, the slice permutations  $P_0, \dots, P_3$  of GIFT-128 operate on 32 bits instead of 16, increasing the number of masks and shifts to compute. However, the next section introduces a new GIFT representation which challenges this conclusion.

#### 4 A new GIFT representation

#### GIFT-64 4.1

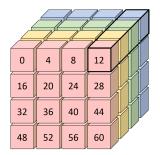

Let us consider a bitsliced representation of the cipher state: for each nibble, bit 0 is placed in the slice 0, bit 1 in slice 1, bit 2 in slice 2 and bit 3 in slice 3. For ease of description, a slice can be placed in matrix form, as shown in the top row of Figure 3. During the SubCells application, when each slice is stored in independent words, all the 16 S-boxes are implemented in parallel in bitslice manner, as seen in Figure 2. Then, according to the GIFT designers  $[BPP^+17]$ , the bit permutation can be implemented as follows:

- Take the transpose of each individual slice matrix

- Apply the following row swaps:

- Slice 0 matrix: swap row 1 with 3

- Slice 1 matrix: swap row 0 with 1, and swap row 2 with 3

- Slice 2 matrix: swap row 0 with 2

- Slice 3 matrix: swap row 0 with 3, and swap row 1 with 2

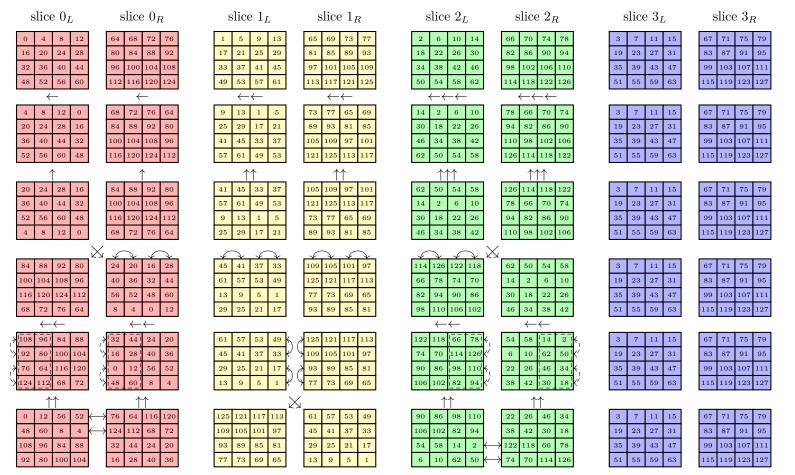

We give a graphical representation of 4 rounds of this process in Figure 3.

Figure 2: Cubic representation of the main state of GIFT-64. Each color refer to a slice matrix while the black cuboid is where an Sbox is applied.

As explained in Section 3, the diffusion layer requires bits to be moved around individually in the slice (and not entire chunks of the slice), resulting in a significant overhead. In order to avoid these issues, we propose a new way to represent GIFT-64. The idea is to fix the first slice matrix to never move and find the easiest operations that could keep the bits of other slice matrices synchronised after application of the linear layer (so that the S-box computation that comes after will indeed involve the proper bits). This representation is given in Figure 4 and one can see that even though the bit positions are different, each S-box will have exactly the same bits indexes involved when compared to the classical representation given in Figure 3. For example, after one round, the classical representation will have bits 16/21/26/31 in row 0 and column 1 and we can see that the exact same quartet will appear as well in the new representation, but in row 1 and column 0 instead. The fact that this quartet appears in a different row/column has no impact on the actual computation of the Sbox right after, since the computation is bitsliced.

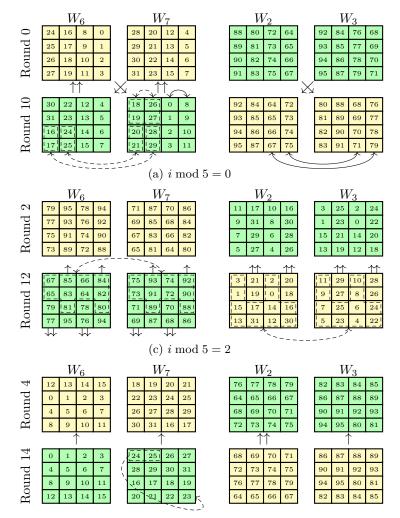

The very nice property of this new representation is that it requires very few operations: each round, we only apply a row or column rotation to the three last slice matrices, while the first slice matrix is never moved. More precisely, for a round i:

- if i%4=0, rotate slice j matrix by j columns to the left

- if i%4=1, rotate slice j matrix by j rows to the top

- if i%4=2, rotate slice j matrix by j columns to the right

- if i%4=3, rotate slice j matrix by j rows to the bottom

This entire process, which applies different functions for each 4 consecutive rounds, will be much less costly in software than having to transpose and then swap rows around. Even better: the new and the classical representations are naturally fully synchronised again after applying these 4 rounds, which avoids any representation correction to be applied at the end of the cipher (since GIFT-64 has 28 rounds, which is a multiple of 4). This is due to the fact that  $P_i^4 = Id$  for all *i*. Therefore, no matter which slice matrix is fixed, the new and the classical representations will be fully synchronised after 4 rounds anyway.

|    | slic | e 0 |    |        | slic | e 1 |    |    | slic | e 2 |    |   |    | slic | e 3 |    |

|----|------|-----|----|--------|------|-----|----|----|------|-----|----|---|----|------|-----|----|

| 0  | 4    | 8   | 12 | 1      | 5    | 9   | 13 | 2  | 6    | 10  | 14 |   | 3  | 7    | 11  | 15 |

| 16 | 20   | 24  | 28 | 17     | 21   | 25  | 29 | 18 | 22   | 26  | 30 |   | 19 | 23   | 27  | 31 |

| 32 | 36   | 40  | 44 | 33     | 37   | 41  | 45 | 34 | 38   | 42  | 46 | • | 35 | 39   | 43  | 47 |

| 48 | 52   | 56  | 60 | <br>49 | 53   | 57  | 61 | 50 | 54   | 58  | 62 |   | 51 | 55   | 59  | 63 |

|    |      |     |    |        |      |     |    |    |      |     |    |   |    |      |     |    |

| 0  | 16   | 32  | 48 | 5      | 21   | 37  | 53 | 10 | 26   | 42  | 58 |   | 15 | 31   | 47  | 63 |

| 12 | 28   | 44  | 60 | 1      | 17   | 33  | 49 | 6  | 22   | 38  | 54 |   | 11 | 27   | 43  | 59 |

| 8  | 24   | 40  | 56 | 13     | 29   | 45  | 61 | 2  | 18   | 34  | 50 |   | 7  | 23   | 39  | 55 |

| 4  | 20   | 36  | 52 | 9      | 25   | 41  | 57 | 14 | 30   | 46  | 62 |   | 3  | 19   | 35  | 51 |

|    |      |     |    |        |      |     |    |    |      |     |    |   |    |      |     |    |

| 0  | 12   | 8   | 4  | 21     | 17   | 29  | 25 | 42 | 38   | 34  | 46 |   | 63 | 59   | 55  | 51 |

| 48 | 60   | 56  | 52 | 5      | 1    | 13  | 9  | 26 | 22   | 18  | 30 |   | 47 | 43   | 39  | 35 |

| 32 | 44   | 40  | 36 | 53     | 49   | 61  | 57 | 10 | 6    | 2   | 14 |   | 31 | 27   | 23  | 19 |

| 16 | 28   | 24  | 20 | 37     | 33   | 45  | 41 | 58 | 54   | 50  | 62 |   | 15 | 11   | 7   | 3  |

|    |      |     |    |        |      |     |    |    |      |     |    |   |    |      |     |    |

| 0  | 48   | 32  | 16 | 17     | 1    | 49  | 33 | 34 | 18   | 2   | 50 |   | 51 | 35   | 19  | 3  |

| 4  | 52   | 36  | 20 | 21     | 5    | 53  | 37 | 38 | 22   | 6   | 54 |   | 55 | 39   | 23  | 7  |

| 8  | 56   | 40  | 24 | 25     | 9    | 57  | 41 | 42 | 26   | 10  | 58 |   | 59 | 43   | 27  | 11 |

| 12 | 60   | 44  | 28 | 29     | 13   | 61  | 45 | 46 | 30   | 14  | 62 |   | 63 | 47   | 31  | 15 |

|    |      |     |    |        |      |     |    |    |      |     |    | 1 |    |      |     |    |

| 0  | 4    | 8   | 12 | 1      | 5    | 9   | 13 | 2  | 6    | 10  | 14 |   | 3  | 7    | 11  | 15 |

| 16 | 20   | 24  | 28 | 17     | 21   | 25  | 29 | 18 | 22   | 26  | 30 |   | 19 | 23   | 27  | 31 |

| 32 | 36   | 40  | 44 | 33     | 37   | 41  | 45 | 34 | 38   | 42  | 46 |   | 35 | 39   | 43  | 47 |

| 48 | 52   | 56  | 60 | 49     | 53   | 57  | 61 | 50 | 54   | 58  | 62 |   | 51 | 55   | 59  | 63 |

Figure 3: Classical representation of the GIFT-64 round function during 4 rounds. Each cell represents a bit, and the numbers in the cells then denote the actual index of that particular bit in the state. Slice 0 (resp. 1/2/3) depicted in red (resp. yellow/green/blue) represents all the bits at position 0 (resp. 1/2/3) of the S-boxes of the cipher state.

We call this technique *fixslicing*. Note that it is close to the software optimization of PRESENT in [RAL17] which consists in decomposing the permutation over 2 rounds, as our new representation can be seen as a decomposition of  $P_0, \dots, P_3$  over 4 rounds. Actually, the fixslicing technique is a particular case for permutations which ensures that, from a bitsliced perspective, all bits within a slice remains in the same one through the permutation. Therefore, it can be applied to all permutations that verify this property, and the number of rounds to consider for the decomposition equals  $min(order(P_i))$  for all *i*.

Figure 4: New representation of the GIFT-64 round function during 4 rounds. Each cell represents a bit, and the numbers in the cells then denote the actual index of that particular bit in the state. Slice 0 (resp. 1/2/3) depicted in red (resp. yellow/green/blue) represents all the bits at position 0 (resp. 1/2/3) of the S-boxes of the cipher state.

The other side of the coin of this new representation is that the round keys and round constants have to be adapted to fit the new way the bits are positioned. While this is not an issue for the round constants by using a precomputed look-up table, adapting the key schedule might result in some computational overhead. The naive approach would be to run the key schedule using the classical representation, before rearranging bits for all round keys. However, one can take advantage of the fact that after 4 rounds all key words are back in the same position within the key state (yet the words themselves will be rotated because of the rotation operations in the key schedule). In other terms, because  $RK^i = U^i ||V^i|$  and  $RK^{i+4} = U^i \gg 2 ||V^i| \gg 12$ , each key word has to go through the same bit reordering every 4 rounds. Therefore a more efficient approach is to rearrange bits for the first 4 round keys only, and to adapt the key schedule accordingly. More details on how to compute the key schedule in the fixsliced representation are given in Appendix A.1.

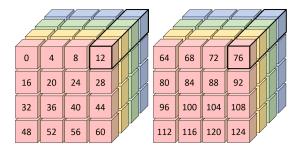

#### 4.2 GIFT-128

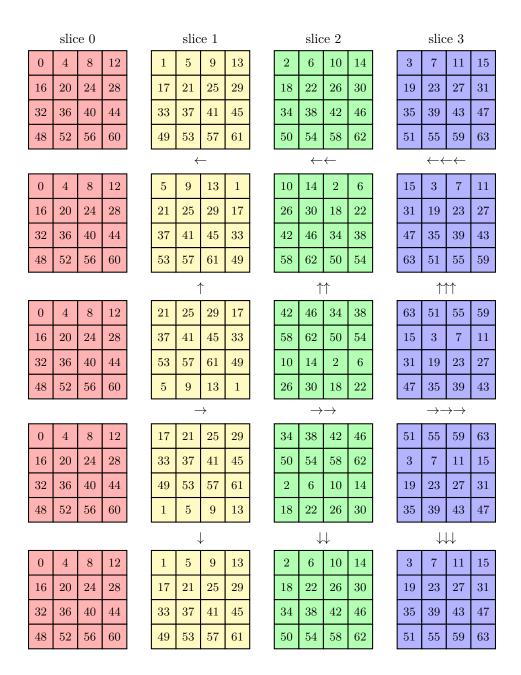

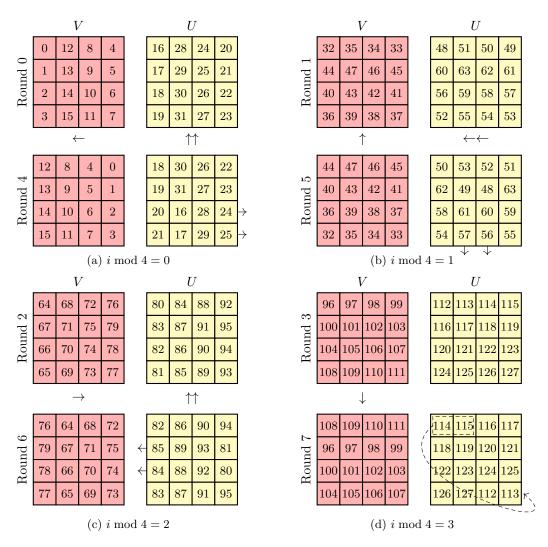

As for GIFT-64, we consider a bitsliced representation of the cipher state. For ease of description, a slice i can be represented as a pair of matrices  $i_L$  and  $i_R$ , as shown in the top row of Figure 6. During the SubCells application, when each slice is stored in independent words, all the 32 S-boxes are implemented in parallel in a bitsliced manner, as seen in Figure 5.

Figure 5: Cubic representation of the main state of GIFT-128. The black cuboid is where an S-box is applied for both matrices.

Then, according to the  $\mathsf{GIFT}$  designers [BPP<sup>+</sup>17], the bit permutation can be implemented as follows:

- Take the transpose of each individual slice matrix

- Shuffle the left and right matrices of each slice (i.e. shuffle  $i_L$  and  $i_R$  for all i).

- Apply the following row swaps:

- Slice 0: swap the 2 bottom halves

- Slice 1: swap the top and bottom halves of the slices independently

- Slice 2: swap the 2 top halves

- Slice 3: cross swap the top and bottom halves

We give a graphical representation of 5 rounds of this process in Figure 6.

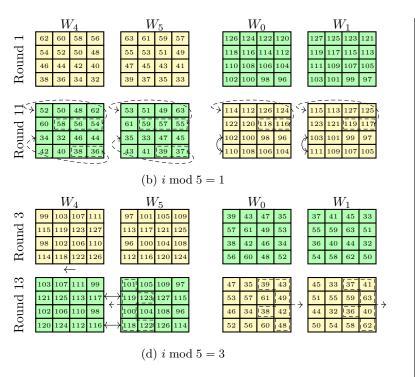

As for GIFT-64, one can see that the process will be very costly in software, with lots of transpositions, shuffle and swaps. We therefore propose a new way to represent GIFT-128, thanks to the fixslicing technique. However, unlike GIFT-64, note that the classical and the new representation will not be synchronised anymore after 4 rounds since  $P_i^4 \neq Id$  for all *i*. For GIFT-128 we have  $P_0^{31} = P_1^{10} = P_2^{31} = P_5^5 = Id$ . In other terms, by fixing the fourth slice to never move, we can define a routine so that the classical and new representation are naturally synchronised after 5 rounds. Since GIFT-128 has 40 rounds (which is a multiple of 5), it avoids any correction to be applied at the end of the cipher. This representation is depicted in Figure 7.

| slice $0_L$                                                                                                                                                                     | slice $0_R$                                                                                                                                                                          | slice $1_L$                                                                                                                                                                       | slice $1_R$                                                                                                                                                                          | slice $2_L$                                                                                                                                                                      | slice $2_R$                                                                                                                                                                       | slice $3_L$                                                                                                                                                                          | slice $3_R$                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0         4         8         12           16         20         24         28           32         36         40         44           48         52         56         60      | 64         68         72         76           80         84         88         92           96         100         104         108           112         116         120         124 | 1         5         9         13           17         21         25         29           33         37         41         45           49         53         57         61        | 65         69         73         77           81         85         89         93           97         101         105         109           113         117         121         125 | 2         6         10         14           18         22         26         30           34         38         42         46           50         54         58         62      | 667074788286909498102106110114118122126                                                                                                                                           | 3         7         11         15           19         23         27         31           35         39         43         47           51         55         59         63          | 67         71         75         79           83         87         91         95           99         103         107         111           115         119         123         127 |

| 0         16         32         48           64         80         96         112           12         28         44         60           76         92         108         124 | 8         24         40         56           72         88         104         120           4         20         36         52           68         84         100         116      | 5         21         37         53           69         85         101         117           1         17         33         49           65         81         97         113    | 13         29         45         61           77         93         109         125           9         25         41         57           73         89         105         121     | 10         26         42         58           74         90         106         122           6         22         38         54           70         86         102         118 | 2         18         34         50           66         82         98         114           14         30         46         62           78         94         110         126   | 15     31     47     63       79     95     111     127       11     27     43     59       75     91     107     123                                                                | 7         23         39         55           71         87         103         119           3         19         35         51           67         83         99         115       |

| 0         64         12         76           8         72         4         68           48         112         60         124           56         120         52         116  | 32         96         44         108           40         104         36         100           16         80         28         92           24         88         20         84     | 21         85         17         81           29         93         25         89           5         69         1         65           13         77         9         73        | 53         117         49         113           61         125         57         121           37         101         33         97           45         109         41         105 | 42         106         38         102           34         98         46         110           26         90         22         86           18         82         30         94 | 1074670266147858122541185011462126                                                                                                                                                | 63         127         59         123           55         119         51         115           47         111         43         107           39         103         35         99 | 31         95         27         91           23         87         19         83           15         79         11         75           7         71         3         67          |

| 0         8         48         56           32         40         16         24           76         68         124         116           108         100         92         84 | 12         4         60         52           44         36         28         20           64         72         112         120           96         104         80         88      | 85         93         69         77           117         125         101         109           21         29         5         13           53         61         37         45  | 81         89         65         73           113         121         97         105           17         25         1         9           49         57         33         41       | 38         46         22         30           6         14         54         62           106         98         90         82           74         66         122         114  | 42         34         26         18           10         2         58         50           102         110         86         94           70         78         118         126  | 123     115     107     99       91     83     75     67       59     51     43     35       27     19     11     3                                                                  | 127         119         111         103           95         87         79         71           63         55         47         39           31         23         15         7     |

| 0         32         76         108           12         44         64         96           56         24         116         84           52         20         120         88 | 48         16         124         92           60         28         112         80           8         40         68         100           4         36         72         104      | 93         125         29         61           89         121         25         57           85         117         21         53           81         113         17         49 | 77     109     13     45       73     105     9     41       69     101     5     37       65     97     1     33                                                                    | 22         54         90         122           26         58         86         118           46         14         98         66           34         2         110         78  | 38         6         106         74           42         10         102         70           30         62         82         114           18         50         94         126  | 99         67         35         3           103         71         39         7           107         75         43         11           111         79         47         15       | 115         83         51         19           119         87         55         23           123         91         59         27           127         95         63         31    |

| 0         12         56         52           48         60         8         4           108         96         84         88           92         80         100         104   | 76         64         116         120           124         112         68         72           32         44         24         20           16         28         40         36    | 125121117113109105101979389858177736965                                                                                                                                           | 61         57         53         49           45         41         37         33           29         25         21         17           13         9         5         1           | 90         86         98         110           106         102         82         94           54         58         14         2           6         10         62         50   | 22         26         46         34           38         42         30         18           122         118         66         78           74         70         114         126 | 3         7         11         15           19         23         27         31           35         39         43         47           51         55         59         63          | 67         71         75         79           83         87         91         95           99         103         107         111           115         119         123         127 |

Figure 6: Classical representation of the GIFT-128 round function during 5 rounds. Each cell represents a bit, and the numbers in the cells then denote the actual index of that particular bit in the state. Slice 0 (resp. 1/2/3) depicted in red (resp. yellow/green/blue) represents all the bits at position 0 (resp. 1/2/3) of the S-boxes of the cipher state.

|12

Figure 7: New representation of the GIFT-128 round function during 5 rounds. Each cell represents a bit, and the numbers in the cells then denote the actual index of that particular bit in the state. Slice 0 (resp. 1/2/3) depicted in red (resp. yellow/green/blue) represents all the bits at position 0 (resp. 1/2/3) of the S-boxes of the cipher state.

One can again see that even though the bit positions are different, each S-box will have exactly the same bit indexes involved when compared to the classical representation given in Figure 6. We recall that this representation implies that the key schedule and constant addition have to be adapted to fit the new way the bits are positioned.

The first 2 rounds are similar to the ones used for GIFT-64. Namely, in the first round, we simply rotate each matrix of each slice i (thus  $i_L$  and  $i_R$  for all i) by i columns to the left. In the second round, we simply rotate each matrix of each slice i (thus  $i_L$  and  $i_R$  for all i) by i rows to the top. For the third round, we swap the matrices  $i_L$  and  $i_R$ for  $i \in \{0, 2\}$  before swapping the first and third columns with the second and fourth ones respectively, for matrixes  $0_R, 1_L, 1_R$  and  $2_L$ . During the fourth round, we swap the first and third rows with the second and fourth ones respectively, for each matrix of slice 1. Then, for each matrix of slice 0 (resp. slice 2), we rotate by 2 columns to the left before swapping rows of the left-half block (resp. right-half block). Finally, the fifth round consists in swapping  $1_L$  with  $1_R$ , rotating  $i_L$  and  $i_R$  by 2 rows to the top for  $i \in \{0, 2\}$  and swapping the first and second rows of each matrix for slice 0, while swapping the third and fourth rows of each matrix for slice 2. All these operations are illustrated in Figure 7 for greater clarity.

The above mentioned method to adapt the key schedule for GIFT-64 cannot be straightforwardly applied to GIFT-128. Indeed, the new and the classical representations of the state are synchronised after 5 rounds, but the key schedule part is almost synchronised after 4 rounds (the key word will return to its original position after 4 rounds, albeit rotated). Thus, it looks like the synchronisation will happen only every  $4 \times 5 = 20$  rounds. However, one can remark that twice as much subkey material is used for GIFT-128 compared to GIFT-64, and there the key words used every two rounds are the same (albeit rotated, and for different part of the internal state). Thus, we have an almost synchronisation that will happen only every  $2 \times 5 = 10$  rounds instead. In other terms, each key word has to match every new representation of the state at some point. Instead of applying the naive approach for all round keys, which consists in running the key schedule using the classical representation and then rearranging bits, we suggest to apply it only for the first 10 round keys. At this stage, all key words will be expressed in each representation, allowing to adapt the key schedule for each of them, without reordering bits. More details on how to compute the key schedule in the fixsliced representation are given in Appendix A.2.

## 5 Efficient software implementations of GIFT

This section shows how to take advantage of the fixslicing technique to achieve efficient implementations of GIFT on ARM Cortex-M processors. We also briefly discuss the gap for other platforms that do not come with an inline barrel shifter or rotate instruction.

#### 5.1 GIFT-64

In the case of GIFT-64, thanks to our new fixsliced representation, the linear layer consists in rotating either rows or columns depending on the round number. Depending on how the bits are arranged within the slices (i.e. row-wise or column-wise bitsliced representation), these operations refer to either half-word (16-bit) or nibble (4-bit) rotations. In the rest of this section we consider a row-wise bitsliced representation. The ARM Cortex-M being a 32-bit architecture (and since we have 4 slices in GIFT-64), two 64-bit blocks B and B'can be processed at a time. Instead of simply concatenating 16-bit slices of both blocks within a 32-bit words, we suggest to interleave the nibbles as follows:  $S_{0} \leftarrow b_{60} \ b_{56} \ b_{52} \ b_{48} \ b_{60}' \ b_{56}' \ b_{52}' \ b_{48}' \cdots \ b_{12} \ b_{8} \ b_{4} \ b_{0} \ b_{12}' \ b_{8}' \ b_{4}' \ b_{0}'$   $S_{1} \leftarrow b_{61} \ b_{57} \ b_{53} \ b_{49} \ b_{61}' \ b_{57}' \ b_{53}' \ b_{49}' \cdots \ b_{13} \ b_{9} \ b_{5} \ b_{1}' \ b_{13}' \ b_{9}' \ b_{5}' \ b_{1}'$   $S_{2} \leftarrow b_{62} \ b_{58} \ b_{54} \ b_{50} \ b_{62}' \ b_{58}' \ b_{54}' \ b_{50}' \cdots \ b_{14} \ b_{10} \ b_{6} \ b_{2} \ b_{14}' \ b_{10}' \ b_{6}' \ b_{2}'$   $S_{3} \leftarrow b_{63} \ b_{59} \ b_{55} \ b_{51}' \ b_{63}' \ b_{59}' \ b_{55}' \ b_{51}' \cdots \ b_{15}' \ b_{11}' \ b_{7}' \ b_{3}' \ b_{15}' \ b_{11}' \ b_{7}' \ b_{3}''$

so that 16-bit rotations are now 32-bit rotations, which can be implemented in a single cycle using the **ror** instruction. Actually, it can be computed for free by taking advantage of the inline barrel shifter, since instructions can shift or rotate one of their operands without any additional cost. Therefore, the implementation cost of the linear layer is now equivalent to 42 nibble rotations (3 have to be computed every 2 rounds). Such rotations can be computed in 3 cycles on ARM Cortex-M processors assuming that the required masks are already loaded in some general purpose registers, resulting in a total of  $42 \times 3 = 126$  cycles. The following calls to the SWAPMOVE routine lead to the above mentioned row-wise nibble-interleaved bitsliced representation.

| $S_0 \leftarrow b_{31} \cdots b_0  S_1 \leftarrow b'_{31} \cdots b'_0$ | $S_2 \leftarrow b_{63} \cdots b_{32}  S_3 \leftarrow b'_{63} \cdots b'_{32}$ |

|------------------------------------------------------------------------|------------------------------------------------------------------------------|

| $\texttt{SWAPMOVE}(S_0,S_0,\texttt{0x0a0a0a0a},3);$                    | $\texttt{SWAPMOVE}(S_1,S_1,\texttt{OxOaOaOaOa},3);$                          |

| $\texttt{SWAPMOVE}(S_2,S_2,\texttt{0x0a0a0a0a},3);$                    | $\texttt{SWAPMOVE}(S_3,S_3,\texttt{OxOaOaOaOa},3);$                          |

| $\texttt{SWAPMOVE}(S_0,S_0,\texttt{0x00cc00cc},6);$                    | $\texttt{SWAPMOVE}(S_1,S_1,\texttt{OxOOccOOcc},6);$                          |

| $\texttt{SWAPMOVE}(S_2,S_2,\texttt{0x00cc00cc},6);$                    | $\texttt{SWAPMOVE}(S_3,S_3,\texttt{OxOOccOOcc},6);$                          |

| $\texttt{SWAPMOVE}(S_0,S_0,\texttt{0x0000ff00},8);$                    | $\texttt{SWAPMOVE}(S_1,S_1,\texttt{Ox0000ff00},8);$                          |

| $\texttt{SWAPMOVE}(S_2,S_2,\texttt{0x0000ff00},8);$                    | $\texttt{SWAPMOVE}(S_3,S_3,\texttt{0x0000ff00},8);$                          |

| $\texttt{SWAPMOVE}(S_0,S_1,\texttt{OxOfOfOfOf},4);$                    | $\texttt{SWAPMOVE}(S_2,S_3,\texttt{OxOfOfOfOf},4);$                          |

| $\texttt{SWAPMOVE}(S_0,S_2,\texttt{0x0000ffff},16);$                   | $\texttt{SWAPMOVE}(S_1,S_3,\texttt{0x0000ffff},16);$                         |

Although a bitsliced representation without interleaving the nibbles could be built for 12 SWAPMOVE instead of 16, each half-word rotation would require at least 3 cycles, therefore doubling the cost of the linear layer to at least 252 cycles. Regarding the non-linear layer, it is possible to save 1 instruction by omitting the NOT operation. Indeed, this operation applies to a slice that will be then exclusive-ORed with the round key. Therefore, we suggest to compute the NOT on the corresponding round keys. Moreover, because the key schedule is completely linear, one can simply apply the logical negation to the right chunks of the key:

$k_{127} \cdots k_{112} \overline{k_{111} \cdots k_{96}} k_{95} \cdots k_{80} \overline{k_{79} \cdots k_{64}} k_{63} \cdots k_{48} \overline{k_{47} \cdots k_{32}} k_{31} \cdots k_{16} \overline{k_{15} \cdots k_{06}} k_{15} \cdots k_{16} \overline{k_{15} \cdots k_{16}} k_{15} \cdots k_$

before computing the key schedule. Note that this can be done once, when the encryption key is being derived and/or stored on the device, therefore saving 28 cycles per 128-bit data encryption.

On the other hand, a nibble-interleaved bitsliced representation requires twice as much memory to store the round keys and constants in order to avoid extra computations on the fly. It would still be possible to store these variable as 16-bit words but one would have to pay extra cycles to expand them into 32-bit words, nibble-interleaved with theirselves. As a matter of efficiency, we did not consider this option for our implementations. The round keys and constants are stored in 32-bit words, leading to a memory requirement of 112 and 224 bytes for all the round constants and the round keys, respectively.

#### 5.2 GIFT-128

Regarding GIFT-128, because only a single block can be processed at a time on 32-bit processors, we consider a row-wise bitsliced representation without any interleaving. Unlike

GIFT-64, it is not possible to distinguish only 2 but 5 kind of operation since each step of the new representation requires different slice transformations. At steps 1, 2, 4 and 5, these transformations can be implemented by means of nibble, half-word, byte and full-word rotations, respectively. The third step does not clearly refer to any *n*-bit rotation but can be simply computed using the SWAPMOVE process. Again, full-word rotations can be implemented for free on ARM thanks to the inline barrel shifter. Even though the nibble, byte and half-word rotations can be implemented in at least 3 cycles, our implementation requires 5 cycles as 2 additional cycles are spent in loading the appropriate masks into registers. This is due to the fact that, unlike GIFT-64, it is not possible to keep all the masks in registers during the entire encryption routine as 12 different ones are needed. The same statement also applies to SWAPMOVE calculations, leading to a cost of 5 cycles per process. As a result, the linear layer of GIFT-128 can be implemented in about  $12 \times 5 \times 8 = 480$  cycles in total, according to our new representation.

Note that row ordering matters to match with this interpretation of the new representation. Our GIFT-128 implementations use a row ordering from top-down, which can be achieved using the 14 following calls to the SWAPMOVE process:

| $S_0 \leftarrow b_{79} \cdots b_{64} b_{15} \cdots b_0$     | $S_1 \leftarrow b_{95} \cdots b_{80} b_{31} \cdots b_{16}$   |

|-------------------------------------------------------------|--------------------------------------------------------------|

| $S_2 \leftarrow b_{111} \cdots b_{96} b_{47} \cdots b_{32}$ | $S_3 \leftarrow b_{127} \cdots b_{112} b_{63} \cdots b_{48}$ |

| $\texttt{SWAPMOVE}(S_0,S_0,\texttt{0x0a0a0a0a},3);$         | $\texttt{SWAPMOVE}(S_1,S_1,\texttt{0x0a0a0a0a},3);$          |

| $\texttt{SWAPMOVE}(S_2,S_2,\texttt{0x0a0a0a0a},3);$         | $\texttt{SWAPMOVE}(S_3,S_3,\texttt{0x0a0a0a0a},3);$          |

| $\texttt{SWAPMOVE}(S_0,S_0,\texttt{0x00cc00cc},6);$         | $\texttt{SWAPMOVE}(S_1,S_1,\texttt{OxOOccOOcc},6);$          |

| $\texttt{SWAPMOVE}(S_2, S_2, \texttt{0x00cc00cc}, 6);$      | $\texttt{SWAPMOVE}(S_3,S_3,\texttt{OxOOccOOcc},6);$          |

| $\texttt{SWAPMOVE}(S_0, S_1, \texttt{0x000f000f}, 4);$      | $\texttt{SWAPMOVE}(S_0, S_2, \texttt{0x000f000f}, 8);$       |

| $\texttt{SWAPMOVE}(S_0,S_3,\texttt{0x000f000f},12);$        | $\texttt{SWAPMOVE}(S_1, S_2, \texttt{0x00f000f0}, 4);$       |

| $\texttt{SWAPMOVE}(S_1,S_3,\texttt{0x00f000f0},8);$         | $\texttt{SWAPMOVE}(S_2, S_3, \texttt{OxOfOOOfOO}, 4);$       |

Regarding the non-linear layer, contrary to GIFT-64, it is not possible to get rid of the NOT operation within the S-box computation as the round keys are not exclusively-ORed to  $S_0$ . Therefore, our implementation of the non-linear layer follows straightforwardly the specification and requires  $13 \times 40 = 520$  cycles in total.

#### 5.3 Without rotate instruction

Thanks to the inline barrel shifter, our fixsliced implementations fit very well the ARM architecture since the linear layer can be computed for free every 2 and 5 rounds for GIFTb-64 and GIFTb-128, respectively. However, one could ask oneself how it would perform on platforms that do not come with an inline barrel shifter and/or rotate instructions. For instance, RISC-V has no rotate instruction without an appropriate extension (e.g., Bitmanip [Wol20]). In this case, one rotation can be computed by means of 2 shifts and 1 OR, resulting in at least 3 cycles. Therefore, instead of having the linear layer for free every 2 and 5 rounds, it would require at least  $4 \times 3 = 12$  cycles, leading to a minimum overhead of  $12 \times 14 = 168$  and  $12 \times 8 = 96$  cycles for GIFTb-64 and GIFTb-128, respectively. Moreover, nibble, byte and half-word rotations on RISC-V cannot be computed in 3 but 5 cycles because the barrel shifter is not inlined, resulting in an additional overhead of  $2 \times 4 \times 14 = 112$  for GIFT-64. On the other hand, this should not affect GIFT-128 since our implementation spends 5 cycles for all these rotations because 2 additional cycles are spent to load the appropriate masks in registers. While ARM Cortex-M processors only have 14 general purpose registers, RISC-V has 32 such registers, so all the masks can be kept in registers during the entire encryption process. Finally, the SWAPMOVE process would require 6 cycles instead of 4, increasing the cost to pack the input and unpack the output

to  $16 \times 4 = 64$  and  $14 \times 4 = 56$  cycles for GIFT-64 and GIFT-128, respectively. Note that it would also add  $(6-5) \times 3 \times 8 = 24$  cycles to GIFTb-128 since it relies on 3 SWAPMOVE calls in order to compute the linear layer every 5 rounds.

As a result, on platforms without inline barrel shifter or rotate instruction, we estimate a total overhead of 168 + 112 = 280 (i.e. 140 per block) and 96 + 24 = 120 cycles for our fixsliced implementations of GIFTb-64 and GIFTb-128, respectively. Taking into account the overhead to pack/unpack the data would lead to a total overhead of and 280 + 64 = 344 (i.e. 172 per block) and 120 + 56 = 176 cycles for GIFT-64 and GIFT-128, respectively. Overall, this means a penalty of around 40% cycles for GIFT-64 and 15% cycles for GIFT-128. Therefore, fixslicing is still of interest on such platforms compared to the classical representation, although the ARM architecture allows to boost its performance.

# 6 Results

#### 6.1 The GIFT block ciphers

Our GIFT implementations, which are written in ARM assembly, are put into the public domain and available at https://github.com/aadomn/gift. Results for various lightweight block ciphers including GIFT are provided in Table 4.

The implementations of RECTANGLE-64/128, SIMON-64/128 and SPECK-64/128 are the ones from scenario 2 - Best execution time - of the FELICS framework  $[DCK^+19]$ . In this scenario, the key schedule is not taken into account as the round keys are assumed to be precomputed and stored in RAM. The benchmark consists in measuring the time required to encrypt 128-bit data using the CTR mode. We followed the same approach for our GIFT implementations to ensure a fair comparison. The results for  $\mathsf{PRESENT-64/128}$  are taken from [RAL17] and were obtained using the same methodology. Regarding the key schedule, results from the FELICS framework were extracted from the scenario 0, which consists in a simple benchmark of the key schedule and a block encryption/decryption. Except for RECTANGLE, for which implementations are written in ARM assembly, note that the results for the other above mentioned ciphers come from C codes. Therefore, better results can be expected for these algorithms by considering assembly implementations. Table 4 also includes results for the current best AES constant-time implementation from [SS16]. Note that, as in Table 3, RAM usage for encryption functions does not take into account the memory required for the round keys to be compliant with the results from the FELICS framework.

As expected, our new GIFT fixsliced representation allows extremely efficient software bitsliced implementations, requiring at best 766 and 838 cycles to encrypt 128-bit data for GIFTb-64 and GIFT-64, respectively. Note that this is about 13 times more efficient than our naive bitsliced implementations written in C reported in Table 3. On the other hand, the amount of memory to store the round keys is increased by a factor 2. GIFT-64 outperforms all other 64-bit ciphers listed in Table 4, except SPECK-64/128 which is well known for its outstanding performances thanks to its ARX structure. Especially, our implementation of the GIFT-64 key schedule according to the new representation outperforms all the other ones. GIFT-64 key exp. refers to the key schedule including the rearrangement of the encryption key to match the fixsliced representation, while GIFTb-64 key exp. assumes a key already in the right representation as input. Note that rearranging the encryption key can be done only once, when this latter is being derived and/or stored on the device, at the same time that the S-box optimization described in Section 5.

Regarding GIFT-128, we observe a factor of 1.6 in terms of performance compared to GIFT-64. Considering that the factor in terms of rounds is about 1.4, it is a remarkable result since its new representation is slightly more complex. However, the cost of the key

Table 4: Constant-time implementation results on ARM Cortex-M3 and M4 for various versions and representations of GIFT, as well as other lightweight block ciphers. For encryption routines, speed is expressed in cycles per block. Emboldened (resp. italic) results refer to speed (resp. code size) oriented implementations.

| Algorithm                       | Ref                   | Parallel | Speed | l (cycles) | ROM  | (bytes) | <b>RAM</b> (bytes) |           |  |  |  |  |

|---------------------------------|-----------------------|----------|-------|------------|------|---------|--------------------|-----------|--|--|--|--|

| Aigoritinn                      | Iter                  | Blocks   | M3    | M4         | Code | Data    | I/O                | Stack     |  |  |  |  |

| 64-bit ciphers with 128-bit key |                       |          |       |            |      |         |                    |           |  |  |  |  |

| GIFTb-64 key exp.               |                       | _        | 339   | 338        | 972  | 0       | <b>224</b>         | 52        |  |  |  |  |

| dif 15-04 key exp.              |                       | _        | 381   | 383        | 226  | 0       | 224                | 56        |  |  |  |  |

| GIFTb-64 encryption             |                       | 2        | 383   | 383        | 2666 | 0       | 40                 | 48        |  |  |  |  |

| Sil 10 01 cheryption            | Ours                  | 2        | 415   | 415        | 756  | 112     | 40                 | 52        |  |  |  |  |

| GIFT-64 key exp.                | ouis                  | _        | 488   | 487        | 1575 | 0       | <b>224</b>         | 52        |  |  |  |  |

| on rorkey exp.                  |                       |          | 530   | 533        | 828  | 0       | 224                | 56        |  |  |  |  |

| GIFT-64 encryption              |                       | 2        | 419   | 419        | 2962 | 0       | 40                 | 48        |  |  |  |  |

| Gir i of cheryption             |                       | 2        | 458   | 456        | 1058 | 112     | 40                 | 52        |  |  |  |  |

| PRESENT key exp.                | [RAL17]               | -        | 5043  | 3464       | •    | •       | •                  | •         |  |  |  |  |

| PRESENT encryption              | [ICILLI/]             | 2        | 1058  | 800        | 2476 | •       | •                  | •         |  |  |  |  |

| RECTANGLE key exp.              |                       | _        | 1106  |            | 15   | 7       | 232                | 44        |  |  |  |  |

| RECTANGEE Key exp.              | [DCK <sup>+</sup> 19] | _        | 1106  | •          | 15   | 7       | 232                | 44        |  |  |  |  |

| RECTANGLE encryption            | [DOR 15]              | 1        | 854   |            | 800  |         | 76                 | 24        |  |  |  |  |

|                                 |                       | 1        | 1185  | -          | 44   | 0       | 52                 | 24        |  |  |  |  |

| SIMON-64 key exp.               |                       |          | 1195  |            | 11   | 2       | 200                | 8         |  |  |  |  |

| Simon-04 key exp.               | [DCK <sup>+</sup> 19] | -        | 1202  | •          | 10   | 8       | 200                | 12        |  |  |  |  |

| SIMON-64 encryption             | [DUK 19]              | 1        | 650   |            | 45   | 6       | 48                 | <b>24</b> |  |  |  |  |

| Siwon-04 encryption             |                       | 1        | 1281  | •          | 33   | 6       | 40                 | 24        |  |  |  |  |

| SPECK-64 key exp.               |                       |          | 475   | _          | 40   | 3       | 132                | 12        |  |  |  |  |

| JFECN-04 key exp.               | [DCK <sup>+</sup> 19] | -        | 484   | •          | 40   | 6       | 132                | 12        |  |  |  |  |

| SPECK-64 encryption             | [DOI: 19]             | 1        | 285   |            | 62   | 8       | 36                 | 24        |  |  |  |  |

| 51 LCIX-04 encryption           |                       | 1        | 518   |            | 25   | 4       | 36                 | 24        |  |  |  |  |

128-bit ciphers with 128-bit key

| AES-128 key exp.      | [SS16] | - | 1028 | 1034 | 3384  | 1036 | 368 | 188 |

|-----------------------|--------|---|------|------|-------|------|-----|-----|

| AES-128 encryption    | [0166] | 2 | 1617 | 1618 | 12120 | 12   | 48  | 108 |

| GIFT-128 key exp.     |        | - | 966  | 969  | 3510  | 0    | 320 | 48  |

| Gii 1-120 key exp.    |        |   | 1813 | 1812 | 1100  | 0    | 320 | 56  |

| CIETh 129 anonymption | Ours   | 1 | 1169 | 1172 | 4250  | 0    | 48  | 56  |

| GIFTb-128 encryption  |        |   | 1297 | 1279 | 834   | 160  | 48  | 64  |

| CIET 129 onerwation   |        | 1 | 1316 | 1319 | 4868  | 0    | 48  | 56  |

| GIFT-128 encryption   |        |   | 1444 | 1427 | 1332  | 160  | 48  | 64  |

schedule is more than doubled due to the fact that the optimization for GIFT-64 does not apply to GIFT-128 as stated in Section 5. Still, it allows a slightly better performance than the AES key schedule. Note that, unlike for GIFT-64, we do not make a distinction between GIFTb-128 key exp. and GIFT-128 key exp. as our adapted key schedule starts from the key in its classical representation anyway. For encryption routines, it results that our GIFT-128 implementations largely outperforms the current best AES one reported in the literature, with GIFTb-128 saving about 28% cycles on AES-128, for a code size 2.9

times smaller when loops are fully unrolled. It requires 1169 and 1316 cycles for GIFTb-128 and GIFT-128, respectively, which is about 17 times more efficient than our naive bitsliced implementations reported in Table 3. Moreover, note that these AES results benefit from being averaged over 4096 bytes encryption, versus 16 bytes for GIFT-128.

#### 6.2 Adding first-order masking

On top of running in constant-time, secure embedded cryptographic implementations should integrate countermeasures against power based side-channel analysis since they are typical targets for these kind of attacks. A well-known approach to overcome such attacks is the masking countermeasure [CJRR99], which consists in splitting intermediate values in statistically independent shares by means of randomn masks. Thereafter, we report implementation results when applying first-order masking (i.e. splitting all intermediate values in two shares).

Table 5: Masked constant-time implementation results of GIFT and AES on ARM Cortex-M4. For encryption routines, speed is expressed in cycles per block. Emboldened (resp. italic) results refer to speed (resp. code size) oriented implementations.

| Algorithm Ref | Parallel | Speed (cycles) | <b>ROM</b> (bytes) |      | <b>RAM</b> (bytes) |       |

|---------------|----------|----------------|--------------------|------|--------------------|-------|

|               | Blocks   | Speed (cycles) | Code               | Data | I/O                | Stack |

| GIFTb-64 key exp.     | -        | $\begin{array}{c} 641 (+196) \\ 723 (+196) \end{array}$ | <b>1950</b><br><i>360</i> | <b>0</b><br>0 | <b>448</b><br><i>448</i> | <b>68</b><br>68 |

|-----------------------|----------|---------------------------------------------------------|---------------------------|---------------|--------------------------|-----------------|

| GIFTb-64 encryption   | 2        | <b>911</b> (+98)<br>1014 (+98)                          | <b>6646</b><br>1516       | 0<br>112      | <b>40</b><br>40          | 64<br>72        |

| O<br>GIFT-64 key exp. | urs<br>- | 965 (+196) $993 (+196)$                                 | <b>3160</b><br><i>944</i> | 0<br>0        | <b>448</b><br>448        | 68<br>68        |

| GIFT-64 encryption    | 2        | <b>940</b> (+98)<br>1051 (+98)                          | <b>6942</b><br>1722       | 0<br>112      | <b>40</b><br>40          | 64<br>72        |

64-bit ciphers with 128-bit key

#### 128-bit ciphers with 128-bit key

| AES-128 encryption   | [SS16] | 2 | <b>5290</b> (+2133) | 39916 | 12  | 48  | 1588 |

|----------------------|--------|---|---------------------|-------|-----|-----|------|

| GIFT-128 key exp.    |        |   | <b>1994</b> (+196)  | 6816  | 0   | 640 | 64   |

| GIFT-126 key exp.    |        | - | 2202 (+196)         | 2168  | 0   | 640 | 72   |

| GIFTb-128 encryption | Ours   | 1 | $2815\ (+196)$      | 10266 | 0   | 48  | 64   |

|                      |        |   | 3049 (+196)         | 1532  | 160 | 48  | 72   |

| GIFT-128 encryption  |        | 1 | $2972 \ (+196)$     | 10906 | 0   | 48  | 64   |

|                      |        |   | 3203 (+196)         | 2172  | 160 | 48  | 72   |

While linear operations can be simply computed on both shares independently, nonlinear operations are more challenging to compute securely. In the case of GIFT, the only nonlinear gates are 1 OR and 3 AND during the S-box computation. Our masked implementations rely on the secure AND and OR operations introduced in [BDLCU18], which run in 6 cycles on ARM Cortex-M processors and do not require any additional randomness. Table 5 reports implementation results for GIFT and AES on ARM Cortex-M4 as the STM32F407VG incorporates a random number generator. Because the number of clock cyles required to generate randomn numbers is platform dependent, it is enclosed in parentheses separately. Our GIFT implementations only require 4 32-bit random words to mask the internal state

at the beginning of the algorithm. Regarding the key schedules, the same amount of randomness is required to mask the initial key. For both GIFT-64 and GIFT-128, the internal state fits in 4 registers. Therefore, it is possible to handle the state and the masks in 8 registers, avoiding any additional memory access during the encryption routine.

When taking first-order masking into consideration, the advantage of GIFT-128 over AES-128 is even more significant since the number of nonlinear operations to secure is smaller. However, note that the reported results for AES do not take advantage of the optimized AND gate from [BDLCU18] and therefore bear the cost of additional operations and randomness generation. Compared to our unmasked implementation results reported in Table 4, we observe a penalty factor about 2.5 in terms of execution time, showing that GIFT is well suited for software masked implementations thanks to our fixsliced representation.

#### 6.3 The GIFT-COFB authenticated cipher

Since GIFTb-128 defines the underlying block cipher of GIFT-COFB, we can easily have a look at the benefits of our fixsliced representation when applied to this authenticated cipher. To do so, our GIFT-COFB implementation computes the COFB mode using C code while calls to the GIFTb-128 primitive are handled by our assembly implementation. Tables 6 and 7 summarize our implementation results for GIFT-COFB and Ascon [DEMS19], another submission to the NIST LWC competition. For both versions of Ascon, namely Ascon-128 and Ascon-128a, we consider the ARM optimized implementations bi32\_arm, available online at https://github.com/ascon. We believe this is a fair comparison since the core function is written in assembly in a fully unrolled manner, while the rest of the algorithm is handled by C code, just like our GIFT-COFB implementation.

Table 6: Constant-time implementation results on ARM Cortex-M3 and M4 for GIFT-COFB and Ascon to secure 16 bytes of message along with 16 bytes of additional data. Emboldened (resp. italic) results refer to speed (resp. code size) oriented implementations.

| Algorithm                                                | Ref                      | Speed (cycles) |              | <b>ROM</b> (bytes) |      | <b>RAM</b> (bytes) |       |  |

|----------------------------------------------------------|--------------------------|----------------|--------------|--------------------|------|--------------------|-------|--|

| Algorithmin iter                                         |                          | M3             | M4           | Code               | Data | I/O                | Stack |  |

| Without masking                                          |                          |                |              |                    |      |                    |       |  |

| GIFT-COFB                                                | Ours                     | 5375           | 5297         | 10724              | 0    | 376                | 396   |  |

| GIFT-COFB OUIS                                           | Ours                     | 5969           | 5995         | 4472               | 160  | 376                | 416   |  |

| Ascon-128                                                | 129                      | 6649           | 6681         | 6272               | 0    | 92                 | 304   |  |

| ASCOII-120                                               | https://github.com/ascon | 7186           | 7239         | 2288               | 0    | 92                 | 336   |  |

| Ascon-128a                                               | (Our measurements)       | 6284           | 6307         | 7714               | 0    | 92                 | 392   |  |

| ASCOII-120a                                              |                          | 6793           | 6829         | 3258               | 0    | 92                 | 440   |  |

| With 1st-order masking (including randomness generation) |                          |                |              |                    |      |                    |       |  |

| GIFT-COFB                                                | Ours                     | •              | 11378 (+579) | 21232              | 0    | 696                | 1032  |  |

| GILL-COLP                                                | Ours                     | •              | 12675 (+579) | 5660               | 160  | 696                | 1104  |  |

|                                                          |                          |                |              |                    |      |                    |       |  |

According to our benchmark, fixslicing makes GIFT-COFB a very efficient authenticated cipher, running at 96 cycles per byte for long messages, versus 178 and 126 cycles per byte under the same setting for Ascon-128 and Ascon-128a, respectively. We observe that for small messages, our first-order masked implementation of GIFT-COFB requires about twice as much cycles as Ascon, taking into account the randomness generation on the STM32F407VG micro-controller. On the other hand, one can see the penalty factor falls around 1.5 and 1.3 when compared to Ascon-128 for messages of 64 and 256 bytes,

respectively. However, first-order masked implementations of Ascon should outperform our fixsliced GIFT-COFB implementations for long messages (e.g. larger than 256 bytes) since masking can be restricted to the initialization and finalization phases as done in [AFM18].

Table 7: Running time (cycles) of constant-time speed-oriented implementations of GIFT-COFB and Ascon on ARM Cortex-M4 for different message sizes along with 16 bytes of additional data.

| Algorithm Ref                                            |                          | Message size (bytes) |       |       |        |        | _       |

|----------------------------------------------------------|--------------------------|----------------------|-------|-------|--------|--------|---------|

|                                                          |                          | 16                   | 64    | 256   | 1024   | 4096   | 16384   |

| Without masking                                          |                          |                      |       |       |        |        |         |