# Masking in Fine-Grained Leakage Models: Construction, Implementation and Verification

Gilles Barthe<sup>1,2</sup>, Marc Gourjon<sup>3,4</sup>, Benjamin Grégoire<sup>5</sup>, Maximilian Orlt<sup>6</sup>, Clara Paglialonga<sup>6</sup>, and Lars Porth<sup>6</sup>

<sup>1</sup> MPI-SP, Germany

<sup>2</sup> IMDEA Software Institute, Spain gjbarthe@gmail.com

<sup>3</sup> Hamburg University of Technology, Germany, firstname.lastname@tuhh.de

<sup>4</sup> NXP Semiconductors, Germany

<sup>5</sup> Inria, France, firstname.lastname@inria.fr

<sup>6</sup> TU Darmstadt, Germany, firstname.lastname@tu-darmstadt.de

Abstract. We propose a new approach for building efficient, provably secure, and practically hardened assembly implementations of masked algorithms. Our approach is based on a Domain Specific Language in which users can write efficient assembly implementations *and* fine-grained leakage models. The latter are then used as a basis for formal verification, allowing for the first time formal guarantees for a broad range of leakage effects not addressed by prior work. The practical benefits of our approach are demonstrated through a case study of the PRESENT S-Box: we develop a highly optimized and provably secure masked implementation, and show through practical evaluation based on TVLA that our implementation is practically resilient. Our approach significantly narrows the gap between formal verification of masking and practical security.

Keywords: Side-channel resilience  $\cdot$  Higher-order masking  $\cdot$  Probing security  $\cdot$  Verification  $\cdot$  Domain-Specific-Languages

## 1 Introduction

Physical measurements (noise, time, power, EM radiations) of program execution on physical devices reveal information beyond the program inputs and outputs, for instance values of intermediate computations. This information, known as side-channel leakage, can be used to mount effective side-channel attacks.

The masking countermeasure splits secret data a into d shares  $(a_0, \ldots, a_{d-1})$  such that it is easy to compute a from all shares but impossible from less than d shares [CJRR99, ISW03]. This requires attacks to recover d shares instead of a single secret value. An active line of research considers the construction of masked algorithms, denoted "gadgets", which compute some functionality on masked inputs while enforcing that secrets cannot be recovered from less than d intermediate values.

Construction of gadgets is particularly difficult when considering side-channel leakage which allows to observe more than just the intermediate computation steps. Extended leakage models have been devised to consider additional sidechannel information in systematic manner [FGP+18, PR13, DDF14, BGI+18].

Naturally, the question arises whether the masking countermeasure has been applied correctly to a gadget and whether it provides an improvement of security. There exist two main, and fairly distinct, approaches to evaluate effectiveness of the applied countermeasures: (I) Physical validation performing specific attacks or statistical tests on physical measurements [DSM17,DSV14,SM15,PV17,MOW17] and (II) Provable resilience based on attacker and leakage models [CJRR99, ISW03,FGP<sup>+</sup>18,PR13,DDF19] and automated verification [BBD<sup>+</sup>15,BBD<sup>+</sup>16, Cor18,EWS14]. We review the strengths and weaknesses of both approaches.

The main benefit of reproducing attacks is the close correspondence to security; a successful attack implies a real threat, an unsuccessful attack rules out a vulnerability from exactly this attack under the specific evaluation parameters. The drawback is the inherently limited attacker scope to only those attacks which have been performed and the fact that exhaustive evaluation of all attacks remains untractable in most cases. Statistical evaluation allows to bound the retrievable side-channel information, the success rate of retrieval, or to detect side-channel information leakage without considering actual attacks [SM15, DSM17, DSV14]. Nonetheless, the evaluation remains specific to the input data and measurement environment used during assessment. In both cases it is difficult to decide at which point to stop the evaluation and to declare an implementation to be secure. In addition, these methods have large computational requirements which imply an increased wait time for the evaluation results. This prevents fast iterative development cycles with repeated proposal of implementations and evaluation thereof. Put vice versa; the implementer has to carefully produce good implementations to avoid too frequent evaluation, limiting creative freedom.

Provable resilience provides a rigorous approach for proving the resilience of masked algorithms. The main benefit of this approach is that guarantees hold in all environments which comply with the assumptions of the proof and that assessment ends when such a proof is found. Inherent to all formal security notions for side-channel is (I) a formal *leakage model* which defines the sidechannel characteristics considered in the proof and (II) an *attacker model*. The leakage model defines which side-channel information leakages (observations) are accessible to the attacker during execution of a masked program whereas the formal attacker model defines the capabilities of the attacker exploiting this information, e.g. how many side-channel measurements an attacker can perform.

Threshold probing security is arguably the most established approach for provable resilience. In this approach, execution leaks the value of intermediate computations, and the attacker can observe at most t side-channel leakages during an execution of a program masked with d > t shares. The notion of threshold probing security proves perfect resilience against adversaries observing at most tleakages but cannot provide assurance for attackers which potentially observe more. In case the side-channel model accurately captures the device's leakage characteristics the program enjoys security against practical attackers s.t. the chosen notion. The main benefit of probing security is that it can be used to rule out classes of attacks entirely, in difference to physical evaluation such as Test Vector Leakage Assessment (TVLA). Variations of threshold probing security such as the t-Non-interference (t-NI) and t-Strong-Non-interference (t-SNI) refinements exist which are easier to evaluate (check) or guarantee additional properties [BBD<sup>+</sup>16].

A further benefit of provable resilience, and in particular of threshold probing security, is that it is amenable to automated verification. The main benefit of automated verification is that it delegates the formal analysis to a computer program and overcomes the combinatorial explosion that arises when analyzing complex gadgets at high orders.

The main critique of formal security notions for side-channel security is related to the large gap between formal model and behavior in practice, resulting in security assurance that are sometimes hard to interpret. In particular, implementations of verified threshold probing secure algorithms frequently enjoy much less practical side-channel resilience as precisely analyzed by Balasch et al. [BGG<sup>+</sup>14]. The advantage of physical evaluation is preeminent in that the increasing diversity of discovered side-channel leakage effects is not entirely considered by existing verification frameworks. One of the reasons being that the considered leakage effects are inherently integrated into the tool and therefore prevent flexible and fine-grained modeling. In the current setting, new leakage behavior with distinct behavior requires to modify the tool's implementation to be considered. But the diversity of power side-channel leakage encountered in practice is expected to grow as long as new execution platforms are developed [PV17, BGG<sup>+</sup>14, CGD18, MOW17, SSB<sup>+</sup>19, Ves14].

#### 1.1 Our Work

In this paper, we illustrate that automated verification can deliver provably resilient and practically hardened masked implementations with low overhead.

Fine-Grained Modelling of Leakage We define a Domain-Specific Language, called IL, for modelling assembly implementations and specifying fine-grained leakage models. The dual nature of the Domain-Specific Language IL has significant benefits. First, it empowers implementers to capture leakage models encountered in practice, and ultimately ensures that the purported formal resilience guarantees are in close correspondence with practical behavior. Second, it supports efficient assembly level implementations of masked algorithms, and bypasses thorny issues with secure compilation. Third, it forms the basis of a generic automated verification framework in which assembly implementations can be analyzed generically, without the need to commit to a fixed or pre-existing leakage model. Specifically, we present a tool (built as a front-end to MaskVerif) that takes as input an implementation and checks whether the implementation is secure w.r.t. the security notion associated with the leakage models given with the implementation. This stands in sharp contrast with prior work on automated verification, which commits to one or a fixed set of leakage models.

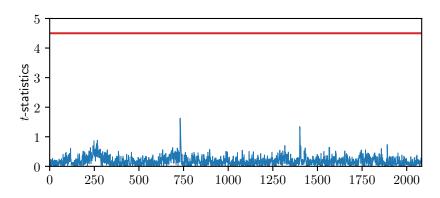

Optimized Hardening of Masking The combination of fine-grained leakage models and reliable verification enables construction of masked implementations which exhibit no detectable leakage in physical assessment, known as "hardened masking" or "hardening" of masked implementations. We demonstrate several improvement in constructing hardened gadgets and a hardened PRESENT S-Box at 1<sup>st</sup> and 2<sup>nd</sup> order which exhibit no detectable leakage beyond one Million measurements in TVLA. We provide generic optimization strategies which reduce the overhead from hardening by executing the code of a secure composition of gadgets in an altered order instead of introducing overhead by inserting additional instructions as countermeasure. The resulting overhead reduction of almost 73% for the first order implementation and of 63% for the second order shows a need to consider composition strategies in addition to established secure composition results. Our contributions outperforms the "lazy strategy" [BGG<sup>+</sup>14] of doubling the number of shares in masking instead of performing hardening; Our contributions allow to gain a security or for free as our optimized 2<sup>nd</sup> order hardened PRESENT S-Box is as fast as a non-optimized 1<sup>st</sup> order hardened PRESENT S-Box.

## 1.2 Related Work

For the sake of clarity, we organize related work by areas:

Provable Resilience Provable resilience of masked implementations was initiated by Chari et al. [CJRR99], and later continued by Ishai, Sahai and Wagner (ISW) [ISW03] and many others. As of today, provable resilience remains a thriving area of research, partially summarized in [KR19], with multiple very active sub-areas. One such relevant area is the study of leakage models, involving the definition and comparison of new models, including the noisy leakage model. the random probing model, the threshold probing model with glitches [PR13, DDF14, BGI<sup>+</sup>18]. Leakage effects were for the first time summarized in a general model by the Robust Probing model [FGP+18]. Later, Meyer et al. in [DBR19], introduce their concept of glitch immunity and unify security concepts such as (Strong) Non-Interference in an information theoretic manner. In comparison to these works, our Domain Specific Language (DSL) offers a much higher flexibility in terms of leakages, since it allows to take into account a broader class of leakages, and consequently more realistic scenarios. Another relevant area tackles the problem of composing secure gadgets; a prominent new development is the introduction of strong non-interference, which achieves desirable composition properties that cannot be obtained under the standard notion of threshold probing security [BBD<sup>+</sup>16]. Belaid, Goudarzi et Rivain present an elegant alternative approach to solve the problem of composition; however their approach is based on the assumption that only ISW gadgets are used [BGR18]. The formal analysis of composability in extended leakage models started to receive more attention with the analysis of Faust et al. in [FGP+18], which formalized the physical leakages of glitches, transitions and couplings with the concept of extended-probes and proved the ISW multiplication scheme to be probing secure against glitches in two cycles. Later, Cassiers *et al.* in [CGLS20] proposed the concept of Hardware Private

Circuits, which formalizes compositional probing security against glitches, and presented gadgets securely composable at arbitrary orders against glitches. Our work augments the t-NI and t-SNI notions to capture resilience and composition in any fine-grained model which can be expressed using our DSL and in the presence of stateful execution, as required for provably secure compilers such as MaskComp and Tornado [BBD<sup>+</sup>16, BDM<sup>+</sup>20]. The research area of optimization of hardened masking did not receive much attention in the literature, for the best of our knowledge.

Automated Verification Proving resilience of masked implementations at high orders incurs a significant combinatorial cost, making the endeavour error-prone, even for relatively simple gadgets. Moss et al [MOPT12] were the first to show how this issue can be managed using program analysis. Although their work is focused on first-order implementations, it has triggered a spate of works, many of which accomodate high orders [BRNI13, EWS14, BBD<sup>+</sup>15, Cor18, ZGSW18]. MaskVerif [BBD<sup>+</sup>15, BBC<sup>+</sup>19], which we use in our work, is arguably one of the most advanced tools, and is able to verify different notions of security, including t-NI and t-SNI at higher orders, for different models, including ISW, ISW with transitions, and ISW with glitches. Furthermore, the latest version of MaskVerif captures multiple side-channel effects for hardware platforms, which are configurable by the user. However, the input language of MaskVerif lacks the expressiveness of IL, making it difficult to capture the rich class of potential leakage in assembly implementations.

Modeling Side-Channel Behavior Side-channel behavior is also expressed for analysis purposes other than provable resilience. Papagiannopoulos and Veshchikov construct models of platform specific side-channel effects they discover in practice [PV17]. Their tool ASCOLD prevents combinations of shares in the considered leakage effects, which are hard-coded into the tool. Most importantly, they are successful in showing that implementations enjoy improved practical security when no shares are combined in their leakage model, which is reminiscent of first order probing security in extended leakage models. Our contributions allow users to provide fine-grained leakage specifications in IL to verify widely established formal security notions at higher orders.

ELMO [MOW17], MAPS [CGD18] and SILK [Ves14] intend to simulate physical measurements based on detailed models. The tools assume fixed leakage effects but allow customization by the user in form of valuation functions. This degree of detail is relevant to simulate good physical measurements but not necessary for our information theoretic notions of security. The authors of MAPS distinguish effects which are beyond what is captured in ELMO's fixed set of combinations and show the need to remain unbiased towards leakage specifications when developing tools for side-channel resilience evaluation. Most notably, ELMO is able to accurately simulate measurements from models inferred in an almost automated manner and is now being used in works attempting to automate the construction of hardened implementations [SSB<sup>+</sup>19].

## 2 Expressing Side-Channel Leakage

Verification of side-channel resilience requires suitable representation of the implementation under assessment. This representation must express a program's functional semantic and information observable per side-channel. It is well known that the leakage behavior of execution platforms differs and this diversity must be expressible to gain meaningful security assurance from verification.

## 2.1 A Domain Specific Language with Explicit Leakage

Already at CHES 2013 the authors of [BRNI13] point out the difficulty of expressing arbitrary side-channel leakage behavior yet providing a "good interface" to users willing to specify *individual* side-channel characteristics. The reason can be related to the fundamental approach of implicitly augmenting the underlying language's operators with side-channel. In such setting, the addition of two variables  $c \leftarrow a + b$ ; implicitly models information observable by an adversary, but what is leaked (e.g. a, b, or a + b) must be encoded in the language semantics (i.e., the meaning of  $\leftarrow$  and +) and thus prevents flexible adoption of leakage characteristics.

The concept of "explicit leakage" is an alternative as it requires to *explicitly* state what side-channel information is emitted. We present a Domain Specific Language (DSL) exerting this concept as the language is free of side-channel, except for a dedicated statement "leak" which can be understood as providing specific information to an adversary. The given example can now be stated as  $c \leftarrow a + b$ ; leak  $\{a + b\}$ ;. This has two important benefits: First, verification and representation of programs can be decoupled to become two independent tasks. Second, specification of side-channel behavior becomes more flexible in that a diverse set of complex side-channel can be expressed and altered without effort.

Our DSL, named "IL" for "intermediate language" has specific features to support representation of low-level software. A Backus Normal Form representation is given in Figure 1. Its building blocks are states  $\chi$ , expressions e, commands (statements) c and global declarations g of variables and macros with local variables  $x_1, \ldots, x_k$ .

```

\begin{split} \chi &::= x \mid x[e] \mid \langle e \rangle \\ e &:= \chi \mid n \in z \mid l \mid o(e_1, \dots, e_j) \\ i &:= \chi \leftarrow e \mid \mathsf{leak} \{e_1, \dots, e_j\} \mid m(e_1, \dots, e_j) \\ \mid \mathsf{label} \mid \mathsf{goto} \ e \\ \mid \mathsf{if} \ e \ \mathsf{then} \ c \ \mathsf{else} \ c \mid \mathsf{while} \ e \ \mathsf{do} \ c \\ c &::= i* \\ g &::= \mathsf{var} \ x \mid \mathsf{macro} \ m(x_1, \dots, x_j) \ x_1, \dots, x_k \ \{c\} \end{split}

```

Fig. 1: Simplified syntax of the intermediate language where n ranges on integers, x on variables, m on macro identifiers, o on operations and l on label identifiers.

A state element  $\chi$  is either a variable x, an array x with an indexing expression e, or a location in memory  $\langle e \rangle$ . Memory is distinguished to allow specifications of disjoint memory regions which enables formal verification to circumvent aliasing problems of pointer operations. Expressions are built from state elements  $\chi$ , constant integers n, unique labels l, and operators o applied to expressions. Infix abbreviations for logical "and"  $\otimes$ , "exclusive-or"  $\oplus$ , addition + and right shift  $\gg$  are used in the following.

Allowed statements *i* are assignments  $\chi \leftarrow e$ , explicit leaks leak  $\{e_1, \ldots, e_j\}$  of one or more expressions and call to a previously defined macro  $m(e_1, \ldots, e_j)$  where *m* is the name of the macro. Additional statements for if conditionals and while loops are supported as well.

Labels l are needed to represent the execution of microcontrollers (MCUs) which is based on the address of an instruction. They are defined by a dedicated statement, enabling execution to proceed at the instruction subsequent to this label. Static jumps to unique labels and indirect jumps based on expressions of labels are supported to represent control-flow.

In a nutshell, executable implementations consist of an unstructured list of hardware instructions where each instruction is located at a specific address and execution steps over addresses. In the following we represent implementations as a list of IL label definitions and macro calls: every instruction is represented by an IL label corresponding to the address of this instruction and a macro call representing the hardware instruction and its operands. A line of Assembly code "0x16E: ADDS R0 R1" becomes almost identical IL code: label 0x16E; ADDS(R0, R1);.

The DSL enables construction of individual *leakage models* of instructions specifying fine-grained semantic and side-channel behavior. Leakage models are then used to express implementations of masked algorithms in the manner explained above, such that formal verification can operate on a close representation of real side-channel behavior yet remain free of assumptions on leakage behavior. In this light, verifying side-channel resilience of implementations involves three steps: (I) modeling behavior of instructions, (II) representing an implementation using such a model and (III) analyzing or verifying the representation (Section 3).

We stress the significant benefit: verification and representation become separate concerns, i.e., automated verification is now defined over the semantic of our DSL and the separate leakage model of step (I) can be freely modified or exchanged without altering the work-flow in stages (II) and (III). In particular, our tool, named "scVerif" allows the user to provide such leakage specification in conjunction with an implementation for verification of side-channel resilience.

#### 2.2 Modeling Instruction Semantics

The DSL allows to construct models which are specific to the device executing an implementation by attaching *device specific* side-channel behavior. This is especially, important for the Arm and RISC-V Instruction Set Architectures (ISAs) since these are implemented in various MCUs which execute instructions differently, causing potentially distinct side-channel information. The instruction

Algorithm 1 Low-level model of addition with carry and instruction for addition.

```

1: macro ADDWITHCARRY (x, y, carry, result, carryOut, overflow)

2:

var unsignedSum, var signedSum {

3:

signedSum \leftarrow (uint) x + (uint) y + (uint) carry;

4:

unsignedSum \leftarrow (int) x + (int) y + (int) carry;

5:

result \leftarrow (w32) unsignedSum;

6:

carryOut \leftarrow \neg ((uint) result = unsignedSum);

7:

overflow \leftarrow \neg ((int) result = signedSum);

8: }

9: macro ADDS (rd, rn) {

\triangleright model of rd \leftarrow rd + rn

ADDWITHCARRY(rd, rn, 0, rd, apsrc, apsrv);

10:

11:

apsrz \leftarrow rd = 0;

\texttt{apsrn} \leftarrow (\texttt{rd} \gg 31) = 1;

12:

13:

if rd \simeq_n pc then

14:

goto rd;

15:

end if

16: \}

```

semantic must be modeled since some leakage effects depend not only on intermediate state but also on the order of execution (e.g. control flow). In the following, we show construction of models for Arm Cortex M0+ (CM0+) instructions which are augmented with leakage in Section 2.3. The DSL enables construction of leakage models for other architectures or programming languages as well.

IL enables to express architecture flags, carry bits, unsigned/signed operations, cast between data types, bit operations, control flow, etc. in close correspondence to ISA specifications. The instructions of the CM0+ ISA operate on a set of globally accessible registers and flags, denoted *architecture state*. They can be modeled as global variables in IL: var R0; var R1; ... var PC; var apsrc; (carry flag) var apsrv; (overflow flag) var apsrz; (zero flag) var apsrn; (negative flag).

Addition is used in the ADDS instruction and instructions operating on pointers such as LDR (load) and STR (store). Expressing the semantic of addition with carry requires casting 32 bit values to unsigned, respective signed values and comparing the results of addition to assign the carry and overflow flags correctly. The IL model of ADDS is expressed in Algorithm 1, closely following the Arm ISA specification in [ARM18] with six parameters for inputs, output, carry and overflow flags<sup>7</sup>. unsignedSum and signedSum are local values. The ADDS instruction is modeled by calling the macro and expressing the side-effect to global flags. A special case of addition to pc requires to issue a branch to the resulting address (represented as a label). The operator  $\simeq_n$  is used to compare whether the parameter rd is equal to register with name pc and conditionally issue the branch.

IL does not provide an operator for sampling randomness. Sampling randomness, e.g. in the form of queries to random number generators, can be expressed

<sup>&</sup>lt;sup>7</sup> Called macros are substituted in-place and modify input parameters instead of returning values.

by reading from a tape of pre-sampled randomness in global state and augmenting the tape pointer successively.

#### 2.3 Modeling Leakage

We augment the instruction models with a representation of power side-channel specific to threshold probing security. For this security notion it is sufficient to model the dependencies of leakages, which is much simpler and more portable than modeling the constituting function defining the actual value observable by an adversary. Specifying multiple expressions within a single leak $\{e_1, e_2, \ldots\}$  statement allows the threshold probing attacker to observe multiple values (expressions) at the cost of a single probe. On hardware this is known from "glitch" leakage effect which allows to observe multiple values at once [FGP<sup>+</sup>18]. The leak statement allows generic specification of such *multi-variate leakage* both for side-channel leakage effects but also as worst-case specifications of observations. In particular, a program which is resilient w.r.t. leak $\{e_1, e_2\}$  is necessarily resilient w.r.t. any function f(a, b) in leak $\{f(e_1, e_2)\}$  but not vice versa. We proceed to model the worst case in the following.

The ADDS instruction is augmented with leakage, which is representative for ANDS (logical conjunction) and EORS (exclusive disjunction) as they behave similar in our model. Observable leakage arises from computing the sum and can be modeled by the statement leak  $\{rd + rn\}$ ;. Transient leakage as in the robust probing model of  $[FGP^+18]$  are modeled in worst case manner, i.e., instead of a single, combined value there are two values leakaged at the cost of a single probe: leak  $\{rd, rd + rn\}$ ;. The order of execution matters, thus this leakage must be added at the top of the function, before assigning  $rd^8$ .

For better clarity we expose these two leakage effects as macros. The resulting specification of ADDS can be found in Algorithm 2.

**Definition 1 (Computation Leakage Effect).** The computation leakage effect produces an observation on the value resulting from the evaluation of an expression *e*.

1: macro EMITCOMPUTATIONLEAK (e) {

2: leak {e};

3: }

**Definition 2 (Transition Leakage Effect).** The transient leakage effect provides an observation on state x and the value e which is to be assigned.

1: macro EMITTRANSITIONLEAK (x, e) { 2: leak  $\{x, e\}$ ; 3: }

<sup>&</sup>lt;sup>8</sup> The order in which leak statements are placed does not matter since leaks have no semantic side-effect.

| Algo | Algorithm 2 Leakage model of ADDS instruction. |  |  |  |  |

|------|------------------------------------------------|--|--|--|--|

| 1: m | 1: macro LEAKYADDS (rd, rn) {                  |  |  |  |  |

| 2:   | EmitComputationLeak $(rd + rn)$ ;              |  |  |  |  |

| 3:   | EmitTransientLeak( $rd, rd + rn$ );            |  |  |  |  |

| 4:   | EmitRevenantLeak(opA, rd);                     |  |  |  |  |

| 5:   | EmitRevenantLeak(opB, rn);                     |  |  |  |  |

| 6:   | ADDS(rd, rn);                                  |  |  |  |  |

| 7: } |                                                |  |  |  |  |

Power side-channel encountered in practice sometimes depends on previously executed instructions. Corre *et al.* encounter a leakage effect, named "operand leakage", which leaks a combination of current and previous operands of two instructions (e.g. parameters to ADDS) [CGD18]. A similar effect on memory accesses was encountered by Papagiannopoulos and Veshchikov, denoted as "memory remnant" in [PV17]. The explicit leak statements enables modeling of such cross-instruction leakage effects by introducing additional state elements  $\chi$ . We denote this additional state as "leakage state", which enables modeling side-channel effects which depend on past execution. In general, leakage effects which depend on one value **p** from past execution and one value **c** from current instruction can be modeled by placing **p** in global state opA during the first instruction and emitting a leak of global state and current value in leak {opA, **p**} in the latter instruction.

The operand and memory remnant leakage effects always emit leakage and update leakage state jointly. We put forward a systematization under the name "revenant leakage", leaning its name to the (unexpected) comeback of sensitive data from past execution steps and, in the figurative sense, haunting the living cryptographer during construction of secure masking. The leakage effect is modeled in Definition 3 and applied to the ADDS instruction in Algorithm 2. The definition can easily be modified such that the state change is conditional to a user-defined predicate or the leakage is extended to a history of more than one instruction.

**Definition 3 (Revenant Leakage Effect).** The "revenant" leakage effect releases a transition leakage prior updating some leakage state  $x \leftarrow p$ .

1: macro EMITREVENANTLEAK (x, p) { 2: leak {x, p}; 3:  $x \leftarrow p$ ; 4: }

The leakage effects are applied within instruction models by calling the EMITREVENANTLEAK macro with the distinct leakage state used for caching the value (e.g. opA) and the value leaking in combination, e.g. the first operand to an addition.

**Algorithm 3** Simplified power side-channel leakage model for CM0+ instructions.

| 1: var R0; var R1; var R12; var PC;                               | ▷ Global registers                                     |

|-------------------------------------------------------------------|--------------------------------------------------------|

| 2: var opA; var opB; var opR; var opW;                            | ▷ Global leakage state                                 |

| 3: macro XOR (rd, rn) {                                           | 0                                                      |

| 4: $leak \{opA, rd, opB, rn\};$                                   | $\triangleright$ combination of revenants              |

| 5: EMITTRANSIENTLEAK (rd, rd $\oplus$ r                           | n);                                                    |

| 6: EMITREVENANTLEAK(opA, rd);                                     |                                                        |

| 7: EMITREVENANTLEAK(opB, rn);                                     |                                                        |

| 8: $rd \leftarrow rd \oplus rn;$                                  |                                                        |

| 9: }                                                              |                                                        |

| 10: macro AND (rd, rn) {                                          |                                                        |

| 11: $leak \{opA, rd, opB, rn\};$                                  | $\triangleright$ combination of revenants              |

| 12: EmitTransientLeak( $rd, rd \otimes r$                         | m);                                                    |

| 13: EmitRevenantLeak(opA, rd);                                    |                                                        |

| 14: EmitRevenantLeak(opB, rn);                                    |                                                        |

| 15: $rd \leftarrow rd \otimes rn;$                                |                                                        |

| 16: }                                                             |                                                        |

| 17: macro LOAD (rd, rn, $i$ ) {                                   |                                                        |

| 18: leak {opA, rn, opB, $i$ };                                    | $\triangleright$ Manual multivariate leakage           |

| 19: EmitRevenantLeak( $opA$ , $rn$ );                             | $\triangleright$ mixed mapping                         |

| 20: EmitRevenantLeak(opB, rd);                                    | $\triangleright$ note: destination register propagated |

| 21: EmitRevenantLeak( $opR$ , $\langle rn$ , $\langle rn \rangle$ | $\left. i \right\rangle$ ) ;                           |

| 22: EmitTransientLeak( $rd$ , $\langle rn, i \rangle$             | ));                                                    |

| 23: $rd \leftarrow \langle rn, i \rangle;$                        |                                                        |

| 24: }                                                             |                                                        |

| 25: macro STORE (rd, rn, $i$ ) {                                  |                                                        |

| 26: leak {opA, rn, opB, $i$ };                                    | $\triangleright$ Manual multivariate leakage           |

| 27: EMITREVENANTLEAK( $opA$ , $rn$ );                             | $\triangleright$ mixed mapping                         |

| 28: EmitRevenantLeak(opB, rd);                                    | $\triangleright$ mixed mapping                         |

| 29: EmitRevenantLeak( $opW$ , rd);                                | $\triangleright$ note: individual state                |

| 30: $\langle \texttt{rn}, i \rangle \leftarrow \texttt{rd};$      |                                                        |

| 31: }                                                             |                                                        |

The overall leakage model for a simplified ISA is depicted in Algorithm 3, it corresponds to the model used for CM0+ Assembly<sup>9</sup>. In our model the leakage state elements are denoted by opA, opB, opR, opW to model four distinct revenant effects for the 1<sup>st</sup> and 2<sup>nd</sup> operand of computation as well as for LOAD and STORE separately. Some effects have been refined to match the behavior encountered in practice, which diverges in the mapping of operands and an unexpected propagation of the destination register in LOAD instructions.

Veshchikov and Papagiannopoulos report the "neighboring" leakage effect, representing a coupling between registers [PV17]. We did not encounter this behavior on CM0+ microcontrollers, although [MOW17] indicate different leakage

<sup>&</sup>lt;sup>9</sup> The full model is provided in combination with our tool scVerif at https://github.com/scverif/scverif

behavior in the higher registers R8 to R12 which we have not used for sensitive data so far. Neighboring leakage can be modeled by using the  $\simeq_n$  operator as shown in Definition 4.

**Definition 4 (Neighboring Leakage Effect).** The neighboring leakage effect causes a leak of an unrelated register RN when register RM is accessed.

1: macro EMITNEIGHBORLEAK (e) { 2: if  $e \simeq_n RM$  then 3: leak {RN, RM}; 4: end if 5: }

The DSL in combination with the concept of explicit leakage enables to model all leakage effects known to us such that verification of threshold probing security becomes aware of these additional leakages. Our effect definitions can serve as building block to construct models such as our model in Algorithm 3 but can be freely modified to model behavior not yet publicly known. In particular, the expressiveness of modeling appears not to be limited except in that further computation operations o might need to be added to our small DSL.

## 3 Stateful (S)NI and Automated Verification

In this section, we lay the foundations for proving security of IL implementations. We first define security notions for IL gadgets: following a recent trend [BBD<sup>+</sup>16], we consider two notions: non-interference (NI) and strong non-interference (SNI), which achieve different composability properties. Then, we present an effective method for verifying whether an IL gadget satisfies one of these notions.

#### 3.1 Security Definitions

We first start with a brief explanation of the need for a new security definition. At a high level, security of stateful computations requires dealing with residual effects on state. Indeed, when a gadget is executed on the processor, it does not only return the computed output but it additionally leaves "residue" in registers, memory, or leakage state. Code subsequently executed might produce leakages combining these residues with output shares, breaking secure composability. As an example, let us consider the composition of a stateful refreshing gadget with a stateful multiplication scheme: Refr(Mult(x, y)). In the case of non-stateful gadgets, if Mult is t-NI and Refr is t-SNI, such a composition is t-SNI. However, if the gadgets are stateful this is not necessarily anymore the case. We give a concrete example: Consider a modified ISW multiplication such that it is t-SNI even with the leakages defined in the previous chapter, the output state  $s_{out}$  of the multiplication, in combination with the revenant leakage effect in the scmacroload of Algorithm 3 can be used to retrieve information about the secret as follows: After the multiplication one register could contain the last output

share of the multiplication gadget and the gadget is still secure. If the refreshing first loads the first output share of the multiplication in the same register, the revenant effect emits an observation containing both values (the first and last output share of the multiplication) in a single probe. Thus the last probes can be used to get the remaining output shares of the multiplication which means that the composition is clearly vulnerable.

We first introduce the notion of gadget, on which our security definitions are based. Informally, gadgets are IL macros with security annotations.

**Definition 5 (Gadget).** A gadget is an IL macro with security annotations:

- a security environment mapping inputs and outputs to a security level: secret (H) or public (L),

- a memory typing mapping memory locations to a security level: secret (H), public (L), random (R),

- share declarations, consisting of tuples of inputs and outputs. We adopt the convention that all tuples are of the same size, and disjoint, and that all inputs and outputs must belong to a share declaration.

We now state our two notions of security. Our first notion is an elaboration of the usual notion of non-interference, and is stated relative to a public input state  $s_{in}$  and public output state  $s_{out}$ . The definition is split in two parts: the first part captures that the gadget does not leak, and the second part captures that the gadget respects the security annotations.

**Definition 6 (Stateful** t–NI). A gadget with input state  $s_{in}$  and output state  $s_{out}$  is stateful t-Non-Interfering (t–NI) if every set of t observations can be simulated by using at most t shares of each input and any number of values from the input state  $s_{in}$ . Moreover, any number of observations on the output state  $s_{out}$  can be simulated without using any input share, but using any number of values from the input state  $s_{in}$ .

Our second notion is an elaboration of strong non-interference. Following standard practice, we distinguish between internal observations (i.e., observations that differ from outputs) and output observations.

**Definition 7 (Stateful** t-SNI). A gadget with input state  $s_{in}$  and output state  $s_{out}$  is stateful t-Strong-Non-Interfering (t-SNI), if every set of  $t_1$  observations on the internal observations,  $t_2$  observations on the output values, combined with any number of observations on the output state  $s_{out}$  can be simulated by using at most  $t_1$  shares of each input and any number of values from the input state  $s_{in}$ .

We note that there exists a third notion of security, called probing security. We do not define this notion formally here, but note that for stateful gadgets t-SNI implies probing security, provided the masked inputs are mutually independent families of shares, and the input state is probabilistic independent of masked inputs and internal randomness.

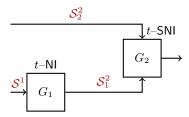

We validate our notions of security through a proof that they are composable— Section 4 introduces new and optimized composition theorems. **Proposition 1.** Let  $G_1(\cdot, \cdot)$  and  $G_2(\cdot)$  two stateful gadgets as in Figure 2. Assuming  $G_2$  is stateful t-SNI and  $G_1$  is stateful t-NI, then the composition  $G_2(G_1(\cdot), \cdot)$  is stateful t-SNI.

*Proof.* Let  $s_{in}^1$  and  $s_{out}^1$  be respectively the state input and state output of  $G_1$  and  $s_{in}^2$  and  $s_{out}^2$  respectively the state input and state output of  $G_2$ . We prove in the following that the composition  $G_2(G_1(\cdot), \cdot)$  is stateful *t*-SNI.

Let  $\Omega = (I, \mathcal{O})$  be the set of observations on the whole composition, where  $I_i$  are the observations on the internal observations of  $G_i$ ,  $I = I_1 + I_2 \leq t_1$  and  $|I| + |\mathcal{O}| \leq t$ .

Since  $G_2$  is stateful t-SNI and  $|I_2 \cup \mathcal{O}| \leq t$ , then there exist observation sets  $S_1^2$ and  $S_2^2$  such that  $|\mathcal{S}_1^2| \leq |I_2|$ ,  $|\mathcal{S}_2^2| \leq |I_2|$  and all the observations on internal and output values combined with any number of observations on the output state  $s_{out}^2$ can be simulated by using any number of values from the input state  $s_{in}^2$  and the shares of each input with index respectively in  $\mathcal{S}_1^2$  and  $\mathcal{S}_2^2$ .

Since  $G_1$  is stateful t-NI,  $|I_1 \cup S_1^2| \leq |I_1 \cup I_2| \leq t$  and  $s_{out}^1 = s_{in}^2$ , then it exists an observation set  $S^1$  such that  $|S^1| \leq |I_1| + |S_1^2|$  and all the observations on internal and output values combined with any number of observations on the output state  $s_{out}^2$  can be simulated by using any number of values from the input state  $s_{in}^1$  and the shares of the input with index in  $S^1$ .

Now, composing the simulators that we have for the two gadgets  $G_1$  and  $G_2$ , all the observations on internal and output values of the circuit combined with any number of observations on the output state can be simulated from  $|\mathcal{S}^1| \leq |I_1| + |\mathcal{S}^2_1| \leq |I_1| + |I_2| \leq t_1$  shares of the first input and  $|\mathcal{S}^2_2| \leq |I_2|$  shares of the second input and any number of values from the input state  $s_{in}^1$ . Therefore we conclude that the circuit is stateful *t*–SNI.

#### 3.2 Automated Verification

In this section, we consider the problem of formally verifying that an IL program is secure at order t, for  $t \ge 1$ . The obvious angle for attacking this problem is to extend existing formal verification approaches to IL. However, there are two important caveats. First, some verification approaches make specific assumptions on the programs—e.g. [BGR18] assumes that gadgets are built from ISW core gadgets. Such assumptions are reasonable for more theoretical models, but are

Fig. 2: Example of composition

difficult to transpose to a more practical model; besides they defeat the purpose of our approach, which is to provide programmers with a flexible environment to build verified implementations. Second, adapting formal verification algorithms to IL is a very significant engineering endeavour. Therefore we follow an alternative method: we define a transformation T that maps IL programs into a fragment that coincides with the core language of MaskVerif, and reuse the verification algorithm of MaskVerif for checking the transformed program. The transformation is explained below, and satisfies correctness and precision. Specifically, the transformation T is correct: if T(P) is secure at order t then P is secure at order t (where security is either NI or SNI). The transformation T is also precise: if P is secure at order t and T(P) is defined then T(P) is secure at order t. Thus, the sole concern with the approach is the partiality of the transformation T. While our approach rejects legitimate programs, it works well on a broad range of examples.

*Target language and high-level algorithm* The core language of MaskVerif is a subset of IL:

$$\begin{split} &\chi ::= x \mid x[n] \\ &e ::= \chi \mid n \mid o \left( e_1, \dots, e_j \right) \\ &i ::= s \leftarrow e \mid \mathsf{leak} \left\{ e_1, \dots, e_j \right\} \\ &c ::= i * \end{split}$$

The main differences between IL and MaskVerif is that the latter:

- does not have memory accesses, macros and control-flow instructions;

- limits array accesses to constant indexes.

Our program transformation proceeds in two steps: first, all macros are inlined; then the expanded program is partially evaluated.

*Partial evaluation* The partial evaluator takes as input an IL program and a public initial state and returns another IL program. The output program is equivalent to the original program w.r.t. functionality and leakage, under some mild assumptions about initial memory layout, explained below.

Our partial evaluator manipulates abstract values and tuples of abstract values, and abstract memories. An abstract value  $\vartheta$  can be either a base value corresponding to concrete base values like Boolean *b* or integer *n*, a label *l* that represent abstract code pointers and are used for indirect jumps, and abstract pointers  $\langle x, n \rangle$ . The latter are an abstract representation of a real pointer. Initially the abstract memory is split into different (disjoint) regions modeled by fresh arrays with maximal offset that do not exist in the original program. Those regions is what we call the memory layout. A base value  $\langle x, n \rangle$  represents a pointer to the memory region *x* with the offset *n* (an integer). This encoding is helpful to deal with pointer arithmetic. Formally,

$$\begin{array}{l} \vartheta ::= b \mid n \mid l \mid \langle x, n \rangle \mid \bot \\ v ::= \vartheta \mid [\vartheta; \dots; \vartheta] \end{array}$$

For example:

```

region mem w32 a[0:1]

region mem w32 b[0:1]

region mem w32 c[0:1]

region mem w32 rnd[0:0]

region mem w32 stack[-4:-1]

```

means that the initial memory is split into 5 distinct region **a**, **b**, **c**, **rnd**, **stack**, where **a** is an array of size 2 with index 0 and 1. Remark that the initial assumption is not checked (and cannot be checked by the tool). Then another part of the memory layout provides some initialisation for registers (IL variables):

```

init r0 <rnd, 0>

init r1 <c, 0>

init r2 <a, 0>

init r3 <b, 0>

init sp <stack, 0>

```

In particular, this assumes that initial the register r0 is a pointer to the region rnd. Some extra information is also provided to indicate which regions initially contain random values, or correspond to input/output shares.

The partial evaluator is parameterized by a state  $\langle p, c, \mu, \rho, ec \rangle$ , where p is the original IL program, c is the current command,  $\mu$  a mapping from p variables to their abstract value,  $\rho$  a mapping from variable corresponding to memory region to their abstract value, and ec is the sequence of commands that have been partially executed. The partial evaluator iteratively propagates values, removes branching instructions, and replaces memory accesses by variable accesses (or constant array accesses). Figure 3 provides some selected rules for the partial evaluator. A complete description of the partial evaluator will appear in the full version.

For expressions, the partial evaluator computes the value  $\vartheta$  of e in  $\mu$  and  $\rho$  (which can be  $\perp$ ) and a expression e' where memory/array accesses are replaced by variables/constant array accesses, i.e.  $\llbracket e \rrbracket_{\mu}^{\rho} = (\vartheta, e')$ . If the expression is of the form  $o(e_1, \ldots, e_n)$  where all the arguments are partially evaluated, the resulting expression is the operator applied to the resulting expressions  $e'_i$  of the  $e_i$  and the resulting value is the partial evaluation of  $\tilde{o}(\vartheta_1, \ldots, \vartheta_n)$  where  $\tilde{o}$  check is the  $\vartheta_i$  are concrete values in that case it compute the concrete value else it return  $\perp$  (the partial evaluator sometime uses more powerful simplification rules like  $0 \tilde{\oplus} \vartheta \rightsquigarrow \vartheta$ ).

If the expression is a variable, the partial evaluator simply return the value stored in  $\mu$  and the variable itself. The case is similar for array accesses, first the index expression is evaluated and the resulting value should be an integer n, the resulting expression is simple x[n] and the resulting value is the value stored in  $\mu(x)$  at position n (the partial evaluator checks that n is in the bound of the array). For memory access  $\langle e \rangle$  the partial evaluation of e should lead to an abstract pointer  $\langle x, ofs \rangle$ , is this case the resulting expression is x[ofs] and the value is  $\rho(x)[ofs]$ .

$$\begin{split} & \frac{\llbracket e_i \rrbracket_{\mu}^{\rho} = (\vartheta_i, e_i')}{\llbracket o(e_1, \dots, e_n) \rrbracket_{\mu}^{\rho} = (\tilde{o}(\vartheta_1, \dots, \vartheta_n), o(e_1', \dots, e_n'))} \quad \overline{\llbracket x \rrbracket_{\mu}^{\rho} = (\mu(x), x)} \\ & \frac{\llbracket e \rrbracket_{\mu}^{\rho} = (n, e')}{\llbracket x [e] \rrbracket_{\mu}^{\rho} = (\mu(x) [n], x[n])} \quad \frac{\llbracket e \rrbracket_{\mu}^{\rho} = (\langle x, \text{ofs} \rangle, e')}{\llbracket \langle e \rangle \rrbracket_{\mu}^{\rho} = (\rho(x) [\text{ofs}], x[\text{ofs}])} \\ & \frac{\llbracket x \rrbracket_{\mu}^{\rho} = (\vartheta, \chi')}{\llbracket x \rrbracket_{\mu}^{\rho} = \chi'} \\ & \frac{i = \chi \leftarrow e \quad i' = \chi' \leftarrow e' \quad \llbracket e \rrbracket_{\mu}^{\rho} = (v, e') \quad \llbracket s \rrbracket_{\mu}^{\rho} = s' \quad (\mu, \rho) \{s' \leftarrow v\} = (\mu', \rho')}{\langle p, i; c, \mu, \rho, ec \rangle \rightsquigarrow \langle p, c, \mu', \rho', ec; i' \rangle} \\ & \frac{\llbracket e_i \rrbracket_{\mu}^{\rho} = (\vartheta_i, e_i')}{[\text{leak} \{e_1, \dots, e_j\} \rightarrowtail \text{leak} \{e_1', \dots, e_j'\}} \quad \frac{i = \text{goto } e \quad \llbracket e \rrbracket_{\mu}^{\rho} = (l, e') \quad p_l = c'}{\langle p, i; c, \mu, \rho, ec \rangle \leadsto \langle p, c', \mu, \rho, ec \rangle} \\ & \frac{i = \text{if } e \ c_t \ c_f \quad \llbracket e \rrbracket_{\mu}^{\rho} = (b, e')}{\langle p, i; c, \mu, \rho, ec \rangle \rightarrowtail \langle p, c_i, \mu, \rho, ec \rangle} \quad \frac{i = \text{while } e \ c_w \quad i' = (\text{if } e \ c_w; i); c}{\langle p, i; c, \mu, \rho, ec \rangle \leadsto \langle p, i', \mu, \rho, ec \rangle} \end{split}$$

Fig. 3: Partial evaluation of expressions and programs

To partially evaluate a left value  $[\![\chi]\!]_{\mu}^{\rho}$ , we partially evaluate the  $\chi$  (viewing it as an expression) using the partial evaluation of expressions. Note that the resulting expression  $\chi'$  is itself a left value.

Partial evaluation of commands proceeds as expected. For assignment and leak instructions, the partial evaluator simply propagates known information into the command. For control-flow instructions, the partial evaluator tries to resolve the control-flow and eliminates the instruction. For goto statements, the partial evaluator tries to resolve the next instruction to be executed, and eliminates the instruction.

The transformation is sound.

**Proposition 2 (Informal).** Let P and P' be an IL gadget and the corresponding MaskVerif gadget output by the partial evaluator. For every initial state s satisfying the memory layout assumptions, the global leakage of P w.r.t. s and a set of inputs is equal to the global leakage of P' w.r.t. the same inputs.

We briefly comment on proving Proposition 2. In order to provide a formal proof, a formal semantics of gadgets is needed. Our treatment so far has intentionally been left informal. However, the behavior of gadgets can be made precise using programming language semantics. We briefly explain how. Specifically, the execution of gadgets can be modelled by a small-step semantics that captures one-step execution between states. This semantics is mostly standard, except for the **leak** statements which generate observations. Using the small-step semantics, one can model global leakage as a function that takes as input initial values for the inputs and an initial state and produces a sequence of observations, a list of outputs and a final state. Last, we transform global leakage into a probabilistic function by sampling all inputs tagged with the security type R independently and uniformly from their underlying set. This yields a function that takes as input initial values for the inputs and an initial partial state (restricted to the non-random values), a list of observations selected by the adversary and returns a joint distribution over tuples of values, where each tuple corresponds to an observation selected by the adversary.

#### 3.3 Implementation

We have implemented the partial evaluator as a front-end to MaskVerif, named "scVerif". Users can write leakage models, annotations and programs in IL or provide programs in Assembly code. If the output program lies in the MaskVerif fragment, then verification starts with user specified parameters such as security order, or which property to verify. Else, the program is rejected.

## 4 Representative Proofs of Efficient Masking

In this section, we describe the construction of gadgets that do not exhibit vulnerable leakage at any order  $t \leq d-1$ , where d is the number of shares. That is, we harden masked implementations to be secure at the optimal order t = d-1 in fine-grained leakage models, opposed to the "lazy" strategy of masking in a basic model at higher orders with the intention to achieve security at lower orders t < d-1 in fine-grained leakage models [BGG<sup>+</sup>14].

Creating a secure gadget is an iterative process which involves three tasks: (a) understanding and modeling the actual leakage behavior (b) constructing an (efficient) implementation which is secure in the fine-grained model (c) optionally performing physical evaluation of side-channel resilience to assess the quality of the model for the specific target platform. Protecting an implementation against side-channel effects mandates insertion of instructions to circumvent vulnerable combination of masked secrets.

#### 4.1 Hardened Masking

In this section, we discuss the development of gadgets which enjoy security in any fine-grained leakage model. We design gadgets first in the simplified IL model depicted in Algorithm 3. Designing in IL is more flexible than Assembly since shortcuts such as leakage free operations and abstract countermeasures are available. Once the gadget is hardened the gadget is implemented in assembly and verified again, which is to large degree trivial but requires to substitute abstract countermeasures by concrete instructions.

Each gadget takes as input one or two values a and b, respectively encoded in  $(a_0, \ldots, a_{d-1})$  and  $(b_0, \ldots, b_{d-1})$ , and gives as output the shares  $(c_0, \ldots, c_{d-1})$ , encoding of a value c. By convention, inputs and outputs are stored in memory to allow construction of implementations at higher orders. Our gadgets, provided in the Supplementary material, use the registers R0, R1, R2, and R3 as memory

address pointing to inputs, outputs and random values stored in memory. The registers R4, R5, R6, and R7 are instead used to perform the elementary operations. Registers beyond R7 are used rarely.

A gadget which is correctly masked in the basic leakage model, i.e., secure against computation leakage (Definition 1), can be secured by purging the architecture and leakage state at selected locations within the code<sup>10</sup>. The reason is simple: every **leak** must be defined over elements of the state and removing sensitive data from these elements prior the instruction causing such **leak** mitigates the ability to observe the sensitive data.

We distinguish "scrubbing" countermeasures, which purge architecture state, and "clearing" countermeasures, which remove values residing in leakage state. Two macros serve as abstract countermeasures, SCRUB(RO) and CLEAR(opA) assign some value which is independent of secrets to RO, respectively opA. On Assembly level these need to be substituted by available instructions. Clearing opA or opB is mostly done by ANDS(RO, RO); since RO is a public memory address. Purging opR (respective opW) requires to execute LOAD (respectively STORE) instruction reading (writing) a public value from memory, but the side-effects of both instructions require additional care. Sometimes multiple countermeasures can be combined in Assembly.

Moreover we approach the problem of securing a composition against the leakage effects introduced in Section 2.1 by ensuring that all the registers involved in the computation of a gadget are completely cleaned before the composition with the next gadget. This, indeed, easily guarantees the requirements of stateful t-SNI in Definition 7. We use FCLEAR as abstract placeholder for the macro run after each gadget to clear the state  $s_{out}$ . Additional clearings are needed between intermediate computations in the gadgets; these macros are represented as CLEAR<sub>i</sub>, where the index distinguishes between the different macros in the gadget since each variety of leakage needs a different countermeasure.

Finally, randomness is employed in order to randomize part of the computation, especially in the case of non-linear gadgets, where otherwise with one probe the attacker could get the knowledge of several shares of the inputs. We indicate with RND a value picked uniformly at random from  $\mathbb{F}_2^{32}$ , prior execution.

For giving an intuition of our strategy, we depict in Algorithm 4 and Algorithm 5 respectively an addition and a multiplication scheme at 1<sup>st</sup> order of security. Some other examples of stateful-t-SNI addition, multiplication and refreshing schemes for different orders can be found in section A of the Supplementary material. They have all been verified to be stateful-t-SNI with the use of our new tool. Some algorithms are clearly inspired by schemes already existing in the literature, as the ISW multiplication [ISW03] and the schemes in [BBP<sup>+</sup>16]. The methodology just described, despite being easy to apply, can be expensive, as it requires an extensive use of clearings, especially for guaranteeing secure composition. However, a couple of strategies can be adopted in order to overcome

$<sup>^{10}</sup>$  All  $t-\mathsf{NI}$  and  $t-\mathsf{SNI}$  algorithms enjoy this property since computation leakage is inherent to masking.

Algorithm 4 Addition scheme at 1<sup>st</sup> order of security

| Inp | <b>Input:</b> $a = (a_0, a_1), b = (b_0, b_1)$                                  |                                                                 |  |  |  |  |

|-----|---------------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|--|--|

| Out | <b>Output:</b> $c = (c_0, c_1)$ , where $c_0 = a_0 + b_0$ and $c_1 = a_1 + b_1$ |                                                                 |  |  |  |  |

| 1:  | LOAD(R4, R1, 0);                                                                | $\triangleright$ Load $a_0$ into register $r_4$                 |  |  |  |  |

| 2:  | LOAD(R5, R2, 0);                                                                | $\triangleright$ Load $b_0$ into register $r_5$                 |  |  |  |  |

| 3:  | XOR(R4, R5);                                                                    | $\triangleright$ after XOR $r_4$ contains $a_0 + b_0$           |  |  |  |  |

| 4:  | STORE(R4, R0, 0);                                                               | $\triangleright$ Store the value of $r_4$ as output share $c_0$ |  |  |  |  |

| 5:  | CLEAR(OPW);                                                                     |                                                                 |  |  |  |  |

| 6:  | LOAD(R5, R1, 1);                                                                | $\triangleright$ Load $a_1$ into register $r_5$                 |  |  |  |  |

| 7:  | LOAD(R6, R2, 1);                                                                | $\triangleright$ Load $b_1$ into register $r_6$                 |  |  |  |  |

| 8:  | XOR(R5, R6);                                                                    | $\triangleright$ after XOR $r_5$ contains $a_1 + b_1$           |  |  |  |  |

| 9:  | STORE(R5, R0, 1);                                                               | $\triangleright$ Store the value of $r_5$ as output share $c_1$ |  |  |  |  |

| 10: | SCRUB(R4); SCRUB(R5); SCRUB(R6);                                                |                                                                 |  |  |  |  |

| 11: | : CLEAR(OPA); CLEAR(OPB); CLEAR(OPR); CLEAR(OPW);                               |                                                                 |  |  |  |  |

this drawback and optimize the use of clearings. We describe such optimization strategies in the following.

#### 4.2 Optimized Composition of Linear Gadgets

The first scenario of optimization we analyze the case when linear gadgets are composed to each other. In the rest of the paper, we refer to this situation as *linear composition*. In this case, we exploit the fact that operations are performed independently share-wise and we modify the order in which the operation are usually performed, in such a way that initially all the operations of the first shares are applied, then all the ones on the second shares, and so on.

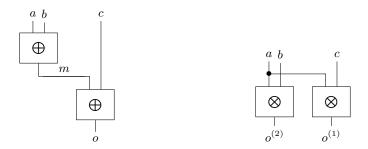

More formally, let a, b, c be d-shared encodings  $(a_i)_{i \in [d]}, (b_i)_{i \in [d]}, (c_i)_{i \in [d]}$  and let  $\mathcal{F}(a, b) := (\mathcal{F}_0(a_0, b_0), \text{CLEAR}_0, \ldots, \mathcal{F}_{d-1}(a_{d-1}, b_{d-1}), \text{CLEAR}_{d-1}, \text{FCLEAR})$  be a share wise simulatable linear gadget with, e.g.  $\mathcal{F}_i(a_i, b_i)$  outputs  $a_i \oplus b_i$  as described in Figure 4 (left) and CLEAR are the leakage countermeasures between each share-wise computation as explained in Sections 4.1. In the following we consider a composition  $\mathcal{F}(\mathcal{F}(a, b), c)$  and present a technique to optimize the efficiency of both gadgets. Instead of performing first the inner function  $\mathcal{F}(a, b) =:$ m and then the outer function  $\mathcal{F}(m, c) =: o$ , our idea is to perform

$$\hat{\mathcal{F}}(a, b, c) = \left( \left( \hat{\mathcal{F}}_i(a_i, b_i, c_i), \text{CLEAR}_i \right)_{i \in [d]}, \text{FCLEAR} \right)$$

with  $\hat{\mathcal{F}}_i(a_i, b_i, c_i) = \mathcal{F}_i(\mathcal{F}_i(a_i, b_i), c_i)$ . In other words, we change the order of computation to  $m_0, o_0, \ldots, m_{d-1}, o_{d-1}$ , rather than  $m_0, \ldots, m_{d-1}, o_0, \ldots, o_{d-1}$ .

This method allows us to save up on the number of CLEAR, LOAD, and STORE operations. In a normal execution, we first need to m when it is given as output of the first gadget, and then we need to load it for injecting it as the input of the second gadget. With the optimized execution, instead, we do not need to have such LOADs and STORES, since the two gadgets are performed at the same time. Additionally, by considering the composition as a unique gadget, we can save on

Algorithm 5 FIRSTMULT: Multiplication scheme at 1<sup>st</sup> order of security

| <b>Input:</b> $a = (a_0, a_1), b = (b_0, b_1)$<br><b>Output:</b> $c = (c_0, c_1)$ , such that |                                                                            |  |  |  |  |

|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|

|                                                                                               | $c_0 = a_0 b_0 + \text{rnd}_0 + a_0 b_1$                                   |  |  |  |  |

|                                                                                               | $c_1 = a_1 b_1 + \operatorname{RND}_0 + a_1 b_0$                           |  |  |  |  |

| 1: $LOAD(R4, R2, 0);$                                                                         |                                                                            |  |  |  |  |

| 2: $LOAD(R5, R1, 0);$                                                                         |                                                                            |  |  |  |  |

| 3: $AND(R4, R5);$                                                                             | $\triangleright$ after AND $r_4$ contains $a_0b_0$                         |  |  |  |  |

| 4: $LOAD(R6, R3, 0);$                                                                         |                                                                            |  |  |  |  |

| 5: $XOR(R6, R4);$                                                                             | $\triangleright$ after XOR $r_6$ contains $a_0b_0 + \text{RND}_0$          |  |  |  |  |

| 6: $LOAD(R7, R2, 1);$                                                                         |                                                                            |  |  |  |  |

| 7: $AND(R5, R7);$                                                                             | $\triangleright$ after AND $r_4$ contains $a_0b_1$                         |  |  |  |  |

| 8: $XOR(R5, R6);$                                                                             | $\triangleright$ after XOR $r_5$ contains $a_0b_1 + a_0b_0 + \text{RND}_0$ |  |  |  |  |

| 9: $STORE(R5, R0, 0);$                                                                        | $\triangleright$ Store the value of $r_5$ as output share $c_0$            |  |  |  |  |

| 10: $CLEAR(OPW);$                                                                             |                                                                            |  |  |  |  |

| 11: $SCRUB(R4);$                                                                              |                                                                            |  |  |  |  |

| 12: $SCRUB(R6);$                                                                              |                                                                            |  |  |  |  |

| 13: $LOAD(R4, R1, 1);$                                                                        |                                                                            |  |  |  |  |

| 14: $AND(R7, R4);$                                                                            | $\triangleright$ after AND $r_7$ contains $b_1a_1$                         |  |  |  |  |

| 15: $LOAD(R6, R3, 0);$                                                                        |                                                                            |  |  |  |  |

| 16: $XOR(R6, R7);$                                                                            | $\triangleright$ after XOR $r_7$ contains $b_1a_1 + \text{RND}_0$          |  |  |  |  |

| 17: $LOAD(R5, R2, 0);$                                                                        |                                                                            |  |  |  |  |

| 18: $AND(R5, R4);$                                                                            | $\triangleright$ after AND $r_5$ contains $b_0 a_1$                        |  |  |  |  |

| 19: $XOR(R6, R5);$                                                                            | $\triangleright$ after XOR $r_6$ contains $b_0a_1 + b_1a_1 + \text{RND}_0$ |  |  |  |  |

| 20: $STORE(R6, R0, 1);$                                                                       | $\triangleright$ Store the value of $r_6$ as output share $c_1$            |  |  |  |  |

| 21: $SCRUB(R4);$                                                                              |                                                                            |  |  |  |  |

| 22: $SCRUB(R5);$                                                                              |                                                                            |  |  |  |  |

| 23: $SCRUB(R6);$                                                                              |                                                                            |  |  |  |  |

| 24: $SCRUB(R7);$                                                                              |                                                                            |  |  |  |  |

| 25: $CLEAR(OPA);$                                                                             |                                                                            |  |  |  |  |

| 26: $CLEAR(OPB);$                                                                             |                                                                            |  |  |  |  |

| 27: $CLEAR(OPR);$                                                                             |                                                                            |  |  |  |  |

| 28: $CLEAR(OPW);$                                                                             |                                                                            |  |  |  |  |

the clearings that would be otherwise needed after the first gadget to ensure the stateful *t*-SNI. In the following, we give a security proof for  $\hat{\mathcal{F}}(a, b, c)$ .

**Proposition 3.** The optimized gadget  $\hat{\mathcal{F}}(a, b, c)$  as described above, is statefult-NI.

*Proof.* We show that all observations in the gadget depend on at most one share of each input. Since the attacker can perform at most n-1 observations, this implies that any combination of its observations is independent of at least one share of each input. More precisely, the computation of the  $i^{th}$  output of  $\hat{\mathcal{F}}(a,b,c)$  only depends on the  $i^{th}$  shares of a, b or c. Hence the observations in each iteration only leak information about the  $i^{th}$  share since we clear the

Fig. 4: Examples of linear composition (left) and non-linear composition (right)

state after the computation of each output share. Therefore any combination of  $t \leq d-1$  observations is dependent on at most t shares of each input, and any set t observations is simulatable with at most t shares of each input bundle.

In the supplementary material we give a concrete construction how to apply Proposition 3 to Algorithm 4.

## 4.3 Optimized Composition of Gadgets with (partly) Independent Inputs

The second scenario that we take into account is the one described in Figure 4 (right), where two non-linear gadgets, e.g. two multiplication algorithms, sharing one of the inputs are performed. We refer in the following to this situation as non-linear composition. In this case, it is possible to reduce the number of loadings and clearings, by re-using the shares in common, once loaded into the registers and replacing the intermediate clearings of a gadget by independent computations of another gadget. The optimization technique described to save clearings also holds for two gadgets with independent inputs. The intermediate clearings in a gadget ensure that two computations on two different shares of the same secret do not leak together. Since this clearing is only a computation independent of the secret, the clearing can be replaced by a useful computation of another gadget. With our tool, we have proven that the merge of stateful t-SNI multiplications, given in Section A of the Supplementary material, is also stateful t-SNI. Since we only need the more efficient special optimization for the present S-Box, we will continue to focus on two multiplications with shared input. In total, we save 59% cycles for second order. The overhead from clearings and scrubs is reduced by 75%, and the amount of loads and stores is reduced by 47%.

## 4.4 Case study: Masking the PRESENT S-Box

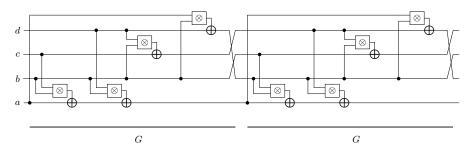

To estimate the impact of our methodology on a complex circuit, we apply to the PRESENT block cipher masked at first and second order the basic rules for composability, defined in Section 3, and successively the optimizations of Section 4.2 and 4.3. We found out that the structure of the S-Box of PRESENT allows the adoption of the optimization techniques, both in the linear and in the non-linear composition.

We consider the first and second order implementation of the S-Box. Based on [CFE16], the S-Box consists of two affine functions and a non-affine one. The non-affine part is depicted in Figure 5. A more complete description of the S-Box is provided in the supplementary material.

Our masked implementation of the PRESENT S-Box, using the trivial solution for composability, is provided as a Supplementary material. Algorithm 12 in Section C depicts the masked S-Box, where the subroutines CALCA in Algorithm 14, CALCB in Algorithm 15 and CALCG in Algorithm 16 are first order NI gadgets. The optimized version of it, instead, employs our optimization techniques which are given in the subroutines CALCA\_OPT, CALCB\_OPT and CALCG\_OPT, respectively in Algorithms 17, 18 and 19. The optimized S-Box implementation is given in Algorithm 13.

As metric to measure the improvements of our optimization techniques, we take the amount of basic operations used in the implementations, as shown in Figure 1. From this comparison, we can see that both implementations use almost the same amount of core operations (XOR and AND), since the two versions implement the same algorithm. More precisely, the non-optimized version requires two XOR operations less, thanks to the parallel calculation of all output values in CALCG\_OPT, where  $b \cdot d$  needs to be added to a' and d'. On the other hand, since in the non-optimized version more intermediate values need to be stored and loaded inside the functions, while in the optimized version it is only needed to store intermediate values between the functions, the number of STORES and LOADS employed is lower, producing an improvement in terms of operation count. Additionally, the amount of LOADS is reduced further in the optimized version by loading every input share once per output share. This holds with exception of the limited amount of registers requiring to load  $a_1$  and  $d_1$  twice for the second output share and  $b_0$  and  $b_1$  only are needed to load once in the whole gadget.

In Table 1 we evaluate the efficiency of our approach, by comparing the ratio between the operation needed for the calculation and the overhead given by

Fig. 5: The Non-Linear Layer of the Present S-Box

|               | 1 <sup>st</sup> | order     |                    | 2 <sup>nd</sup> | order     |                    |

|---------------|-----------------|-----------|--------------------|-----------------|-----------|--------------------|

|               | composition     | optimized | $\frac{opt}{comp}$ | composition     | optimized | $\frac{opt}{comp}$ |

| load          | 115             | 60        | 0.52               | 251             | 136       | 0.54               |

| and           | 24              | 24        | 1                  | 54              | 54        | 1                  |

| xor           | 57              | 59        | 1.054              | 133             | 142       | 1.07               |

| store         | 72              | 48        | 0.67               | 93              | 48        | 0.52               |

| scrub         | 95              | 16        | 0.17               | 211             | 53        | 0.25               |

| clear_opA     | 35              | 12        | 0.34               | 67              | 20        | 0.3                |

| clear_opB     | 130             | 43        | 0.33               | 314             | 80        | 0.25               |

| $clear_{opR}$ | 130             | 26        | 0.2                | 260             | 73        | 0.28               |

| $clear_{opW}$ | 56              | 4         | 0.07               | 93              | 10        | 0.11               |

| cycles        | 1097            | 440       | 0.4                | 2173            | 883       | 0.41               |

Table 1: Operation and cycle count for the normally composed and optimized PRESENT s-Box at  $1^{st}$  and  $2^{nd}$  order

| Normal compositionOptimizationNormal compositionOptimization#clearings<br>#operations1.660.451.780.62 | 1 <sup>st</sup> orde | er           | 2 <sup>nd</sup> ord | er           |

|-------------------------------------------------------------------------------------------------------|----------------------|--------------|---------------------|--------------|

|                                                                                                       | Normal composition   | Optimization | Normal composition  | Optimization |

|                                                                                                       | <br>1.66             | 0.45         | 1.78                | 0.62         |