# Perfectly Secure Oblivious Parallel RAM with $O(\log^3 N / \log \log N)$ Overhead\*

| T-H. Hubert Chan | Wei-Kai Lin | Kartik Nayak | Elaine Shi |

|------------------|-------------|--------------|------------|

| HKU              | Cornell     | Duke         | Cornell    |

hubert@cs.hku.hk, wklin@cs.cornell.edu, kartik@cs.duke.edu, runting@gmail.com

#### Abstract

Oblivious RAM (ORAM) is a technique for compiling any program to an oblivious counterpart, i.e., one whose access patterns do not leak information about the secret inputs. Similarly, Oblivious Parallel RAM (OPRAM) compiles a *parallel* program to an oblivious counterpart. In this paper, we care about ORAM/OPRAM with *perfect security*, i.e., the access patterns must *identically distributed* no matter what the program's memory request sequence is. We show two novel results.

The first result is a new perfectly secure OPRAM scheme with  $O(\log^3 N/\log \log N)$  expected overhead. In comparison, the prior literature has been stuck at  $O(\log^3 N)$  for more than a decade.

The second result is a new perfectly secure OPRAM scheme with  $O(\log^4 N/\log \log N)$  worstcase overhead. To the best of our knowledge, this is the first perfectly secure OPRAM scheme with polylogarithmic worst-case overhead. Prior to our work, the state of the art is a perfectly secure ORAM scheme with more than  $\sqrt{N}$  worst-case overhead, and the result does not generalize to a parallel setting. Our work advances the theoretical understanding of the asymptotic complexity of perfectly secure OPRAMs.

# 1 Introduction

Oblivious RAM (ORAM) is an algorithmic construction that provably obfuscates a (parallel) program's access patterns. It was first proposed in the ground-breaking work by Goldreich and Ostrovsky [GO96, Gol87], and its parallel counterpart Oblivious Parallel ORAM (OPRAM) was proposed by Boyle et al. [BCP16]. ORAM and OPRAM are fundamental building blocks for enabling various forms of secure computation on sensitive data, e.g., either through trustedhardware [RYF<sup>+</sup>13, FRY<sup>+</sup>14, MLS<sup>+</sup>13, LHM<sup>+</sup>15] or relying on cryptographic multi-party computation [GKK<sup>+</sup>12, LWN<sup>+</sup>15]. Since their proposal, ORAM and OPRAM have attracted much interest from various communities, and there has been a line of work dedicated to understanding their asymptotic and concrete efficiencies. It is well-known [GO96, Gol87, LN18] that any O(P)RAM scheme must incur at least a logarithmic *blowup* (also known as *overhead* or *simulation overhead*) in (parallel) runtime relative to the insecure counterpart. On the other hand, ORAM/OPRAM schemes with poly-logarithmic overhead have been known [GO96, Gol87, GM11, KLO12, SCSL11, SvDS<sup>+</sup>13, WCS15, PPRY18], and the very recent exciting work of Asharov et al. [AKL<sup>+</sup>20a] showed how to match the logarithmic lower bound in the sequential ORAM setting, assuming the existence of one-way functions and a computationally bounded adversary.<sup>1</sup>

<sup>\*</sup>The full version is also posted on Cryptology ePrint Archive: Report 2020/604 [CLNS20].

<sup>&</sup>lt;sup>1</sup>For the parallel setting, how to achieve optimality remains open.

Motivation for perfectly secure ORAMs/OPRAMs. With the exception of very few works, most of the literature has focused on either *computationally* secure [GO96,Gol87,AKL<sup>+</sup>20a,KLO12. GM11, PPRY18, CGLS17] or statistically secure [SCSL11, SvDS<sup>+</sup>13, WCS15, Ajt10, CLP14] ORAMS. Recall that a computationally secure (or statistically secure, resp.) ORAM guarantees that for any two request sequences of the same length, the access patterns incurred are computationally (or statistically resp.) indistinguishable. Most known computationally secure or statistically secure schemes [GO96, Gol87, SCSL11, SvDS<sup>+</sup>13, WCS15, BCP16, CS17] suffer from a small failure probability that is negligible in the ORAM's size henceforth denoted N (assuming the schemes are parametrized to achieve  $poly \log N$  overhead). If the ORAM/OPRAM's size is large, say,  $N \geq \lambda$  for some desired security parameter  $\lambda$ , then the failure probability would also be negligible in the security parameter. Unfortunately, for small choices of N (e.g.,  $N = poly \log \lambda$ ), these schemes actually do not give the commonly believed polylogarithmic performance overhead (assuming that  $negl(\lambda)$  failure probability is desired). But we do care about small ORAMs/OPRAMs with perfect security, since they frequently serve as an essential building block in many application settings, such as in the construction of searchable encryption schemes [DPP18], oblivious algorithms [SCSL11, ACN<sup>+</sup>19, AKL<sup>+</sup>20a, PPRY18] including notably, the recent OptORAMa work [AKL<sup>+</sup>20a] that constructed an optimal ORAM.

The study of *perfectly* secure ORAMs/OPRAMs is partly motivated by the aforementioned mismatch, besides the fact that *perfect security* has long been a topic of interest in the multi-party computation and zero-knowledge proof literature [IKO<sup>+</sup>11,GIW16], and its theoretical importance widely-accepted. Historically, perfect security is viewed as attractive since 1) the security holds in any computational model even if quantum computers or other forms of computers can be built; and 2) perfectly secure schemes often have clean compositional properties.

State of affairs for perfectly secure ORAMs/OPRAMs. Despite the sustained and lively progress in understanding the asymptotic overhead of computationally and statistically secure ORAMs/OPRAMs, our understanding of perfectly secure ORAMs/OPRAMs has been somewhat stuck. In general, few results are known in the perfect security regime: in 2011, Damgård et al. [DMN11] first showed a perfectly secure ORAM scheme with  $O(\log^3 N)$  amortized bandwidth overhead and  $O(\log N)$  server storage blowup. Recently, Chan et al. [CNS18] show an improved and simplified construction that removed the log N server storage blowup; and moreover, they showed how to extend the approach to the parallel setting resulting in a perfectly secure OPRAM scheme with  $O(\log^3 N)$  blowup. There is no known super-logarithmic lower bound for perfect security, and thus we do not understand yet whether the requirement of perfect security would inherently incur more overhead than computationally secure ORAMs. Therefore, an exciting and extremely challenging open direction is to understand the exact asymptotic complexity of perfectly secure ORAMs and OPRAMs, that is, to seek a matching upper- and lower-bound. This is a very ambitious goal and in this paper, we aim to take the next natural step forward. Since all prior upper bounds seem stuck at  $O(\log^3 N)$ , we ask the following natural question:

# Does there exist an ORAM/OPRAM with $o(\log^3 N)$ asymptotic overhead?

To achieve perfect security, the prior perfect ORAM/OPRAM constructions of Damgård et al. [DMN11] and Chan et al. [CNS18] pay a price: their stated  $O(\log^3 N)$  overhead is in an *expected* sense, and the ORAM scheme can occasionally run for a long time if certain unlucky events happen. More specifically, the smaller the choice of N, the more likely that the ORAM can run much longer than the expectation. In other words, such ORAM schemes are Las Vegas algorithms. The very recent work of Raskin et al. [RS19] (Asiacrypt'19) was the first to explicitly discuss this issue, and they ask how to construct perfectly secure ORAMs with *deterministic* (i.e., worst-case) performance bounds. They were the first to show a perfectly secure ORAM with  $O(\sqrt{N} \frac{\log N}{\log \log N})$  worst-case overhead (assuming O(1) client-side storage).<sup>2</sup> While conceptually interesting, in comparison with the  $O(\log^3 N)$  scheme by Damgård et al. [DMN11] and Chan et al. [CNS18], the price to pay for the deterministic performance bounds seems somewhat unreasonably high. We therefore ask another natural question:

Does there exist perfectly secure ORAMs/OPRAMs with worst-case polylogarithmic overhead?

# 1.1 Our Results and Contributions

We answer both of the above questions affirmatively. First, we show a novel perfect ORAM/OPRAM scheme whose overhead is upper bounded by  $O(\log^3 N/\log \log N)$  with high probability as stated in the following theorem.

**Theorem 1.1** (Informal: perfect OPRAM with expected performance bounds). There exists a perfectly secure OPRAM scheme that consumes only O(1) blocks of client private cache and O(N) blocks of server-space; moreover the scheme achieves  $O(\log^3 N/\log \log N)$  expected simulation overhead.

In fact, we additionally prove that the  $O(\log^3 N/\log \log N)$  simulation overhead holds with  $1-\exp(-\Omega(\log^2 N))$  probability — note that here the failure probability pertains to the performance bound while security and correctness can never be violated. When N is small, however, say, polylogarithmic in the security parameter, then the performance bound may fail with more than negligible probability (and almost all prior perfect ORAM/OPRAM schemes suffer from the same drawback with the exception of Raskin et al. [RS19]).

Second, we show a perfectly secure OPRAM scheme with  $O(\log^4 N/\log \log N)$  worst-case overhead. Not only is our asymptotic overhead significantly better than the prior work of Raskin et al. [RS19], our scheme also works in the parallel setting, whereas the scheme by Raskin et al. [RS19] is inherently sequential (i.e., it is *not* intended as an OPRAM). To the best of our knowledge, our scheme is the first perfectly secure OPRAM scheme with any non-trivial worst-case performance overhead. We state our second result in the following theorem.

**Theorem 1.2** (Informal: perfect OPRAM with deterministic performance bounds). There exists a perfectly secure OPRAM scheme that achieves  $O(\log^4 N/\log \log N)$  simulation overhead (with probability 1). Further, the scheme consumes only O(1) blocks of client private cache and O(N) blocks of server-space.

# 1.2 Technical Highlight

We briefly describe the novel techniques needed to achieve the  $O(\log^3 N/\log \log N)$  expectedoverhead result, and our result with worst-case overhead can be attained by changing one of the underlying building blocks to a slightly more expensive algorithm but with deterministic running time.

To improve the overhead of perfectly secure ORAMs/OPRAMs to  $O(\log^3 N/\log \log N)$ , our techniques are inspired by the rebalancing trick of Kushilevitz et al. [KLO12] (SODA'12), and yet departs significantly from Kushilevitz et al. [KLO12]. We observe that existing perfect ORAM/OPRAM constructions suffer from an imbalance of costs in the "offline maintain phase" and the "online fetch phase"; specifically, in Chan et al. [CNS18], the offline maintain phase costs  $O(\log^3 N)$  per request

<sup>&</sup>lt;sup>2</sup>Their overhead can be improved to  $O(\sqrt{N})$  if we allowed a linear amount of client-side storage.

whereas the online fetch phase costs only  $O(\log^2 N)$ . A natural idea is to modify the scheme and rebalance the costs of the offline maintain phase and the online fetch phase, such that both phases would cost only  $O(\log^3 N/\log \log N)$ . Unfortunately, existing techniques such as Kushilevitz et al. [KLO12] completely fail for rebalancing perfect ORAMs/OPRAMs — we describe the technical reasons in detail in Appendix B.

We devise a combination of novel techniques and design a new ORAM/OPRAM scheme whose offline maintenance phase and online fetch phase cost asymptotically the same, that is,  $O(\log^3 N/\log \log N)$ . To achieve this, we rely on a combination of several novel techniques.

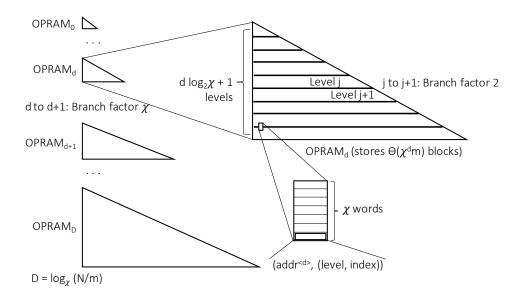

Our starting point is the recent perfectly secure ORAM construction by Chan et al. [CNS18] in which the maintain phase costs  $O(\log^3 N)$  and the fetch phase costs only  $O(\log^2 N)$ . Specifically, their construction consists of  $D = O(\log N)$  number of ORAMs such that except for the last ORAM which stores the actual data blocks, every other ORAM serves as a (recursive) index structure into the next ORAM — for this reason, these D ORAMs are also called D recursion depths; and all of the recursion depths jointly realize an implicit logical index structure that is in fact isomorphic to a binary tree (which has a branching factor of 2).

First, we show how to use a *fat-block* trick to increase the branching factor and hence reduce the number of recursion depths by a log log N factor. In Chan et al. [CNS18]'s construction, the implicit index structure's branching factor is 2, since each block can store the pointers (later called position labels in our construction) for two blocks in the next recursion depth. A fat-block is defined as a bundle of logarithmically many normal blocks and hence each fat-block can store logarithmically many pointers. In this way, the logical index structure implemented by the recursion has a branching factor of log N and thus its depth is reduced by a log log N factor. The price, however, is that the fetch phase now costs a logarithmic factor more per recursion depth (since obliviously accessing a fat-block is a logarithmic factor more costly than accessing a normal block).

The primary challenge is how to realize the maintain phase such that the amortized *per-depth* maintain-phase cost preserves the same asymptotics as Chan et al. [CNS18], despite the fat-block now being logarithmically fatter than normal blocks. To accomplish this we rely on the following two key insights:

- 1. Exploit residual randomness. First, we rely on an elegant observation first made in the PanORAMa work [PPRY18] in the context of computationally secure ORAMs. Here we make the same observation for perfectly secure ORAMs. At the core of Chan et al. [CNS18]'s ORAM construction is a data structure called an oblivious "one-time-memory" (OTM). When an OTM is initialized, all elements in it are randomly permuted (and the randomness concealed from the adversary) note that in our setting, each element is a fat-block. The critical observation is that after accessing a subset of the elements in this OTM data structure, the remaining unvisited elements still appear in a random order. By exploiting such residual randomness, when we would like to build a new OTM consisting of the remaining unvisited elements, we can avoid performing expensive oblivious sorting (which would take time  $O(n \log n)$  to sort n elements) and instead rely on linear-time operations.

- 2. Exploit sparsity. In Chan et al. [CNS18]'s construction, the D ORAMs at all recursion depths must perform a "coordinated shuffle" operation during the maintain phase. An important step in this coordinated shuffle is for each recursion depth to inform the parent depth the locations of its fat-blocks after the reshuffle. In Chan et al. [CNS18], two adjacent recursion depths perform such "communication" through oblivious sorting, and thus incurring  $O(n \log n)$  cost per-depth to rebuild a data structure of size n.

Our key observation is that the fat-blocks contained in each OTM data structure in each recursion

depth are sparsely populated. In fact, most entries in the fat-blocks are empty and only a  $1/\log N$  fraction of them are populated. Thus, at this point, we employ oblivious tight compaction to compress away the wasted space — note that the recent work OptORAMa [AKL+20a] showed how to achieve such compaction in linear time. After this compression, the OTM becomes logarithmically smaller and at this point, we can apply oblivious sorting.

New building block: a perfectly oblivious parallel Intersperse procedure. Last but not the least, to extend the above techniques to the parallel setting, we devise a novel, *perfectly oblivious* algorithmic building block called Intersperse. Intersperse was first proposed in the very recent OptORAMa [AKL<sup>+</sup>20a] work. Given two input arrays of equal length each of which has been randomly permuted, Intersperse merges them into a single randomly permuted array without leaking any information through its access patterns. The Intersperse primitive proposed in OptORAMa [AKL<sup>+</sup>20a] is inherently sequential, and takes O(n) work and parallel runtime to merge two input arrays of length n. In the subsequent work of Asharov et al. [AKL<sup>+</sup>], the parallel runtime is improved to logarithmic while the work is still O(n), but the algorithm is only statistically oblivious. Our scheme is adapted from Asharov et al. [AKL<sup>+</sup>], it achieves O(n) work and logarithmic parallel runtime as well, and it is *perfectly oblivious* at the cost of revealing the lengths of the two input arrays. Therefore, in a parallel setting, our speedup w.r.t. the construction in OptORAMa is exponential. We will elaborate on this difference in Section 4. This new parallel and perfectly oblivious Intersperse might be of independent interest and useful in the construction of other parallel oblivious algorithms.

**Practical efficiency.** Our paper focuses on the *theoretical* understanding of the asymptotic complexity of perfectly secure ORAMs/OPRAMs. Our asymptotic constant is huge due to using AKS sorting network [AKS83] and the linear tight compaction. Comparing to earlier works that also use AKS sorting [DMN11, CNS18], the constants are similar so that our scheme is better. Comparing to Raskin et al. [RS19] with  $\Omega(\sqrt{N} \cdot \log N / \log \log N)$  overhead but a small constant, we can replace both sorting and compaction with bitonic sorter [Bat68] which yields one more logarithmic factor but a small constant;<sup>3</sup> then, as  $\log^4 N$  out performs  $\sqrt{N} \cdot \log N$  after  $N > 2^{32}$ , our scheme is better for practically large data. We also note that some earlier works have made perfectly secure ORAMs concretely efficient in 3-server settings [CKN<sup>+</sup>18].

# 1.3 Additional Related Work

Oblivious RAM (ORAM) was first proposed by Goldreich and Ostrovsky in a seminal work [GO96, Gol87]. The parallel counterpart, called Oblivious Parallel RAM (OPRAM), was first proposed by Boyle, Chung, and Pass [BCP16]. As Boyle et al. argue, OPRAM is important due to the parallelism that is prevalent in modern computing architectures such as multi-core processors and large-scale compute clusters. As mentioned, in this paper, we focus on ORAM/OPRAM constructions that satisfy perfect security. Perfectly secure ORAMs, first studied by Damgård et al. [DMN11], requires that the (oblivious) program's memory access patterns be *identically distributed* regardless of the inputs to the program; and thus with probability 1, no information can be leaked about the secret inputs to the program.

**Importance of perfect security.** The recent work by Chan et al. [CNS18] explains the importance of studying perfect security: first, when computationally or statistically secure ORAMs are applied to problems of small size (relative to the desired security parameter), we often need security

<sup>&</sup>lt;sup>3</sup>While the standard bitonic sort takes  $O(n \log^2 n)$  work, to sort only 0/1 elements (i.e., tight compaction), a bitonic sort augmented with counting takes only  $O(n \log n)$  work.

failures to happen with probability that is not just negligible, but sub-exponentially small in the problem's size. Thus for problems of small size, perfectly secure ORAMs can perform asymptotically better than known computationally or statistically secure ORAMs. Exactly for this reason, existing works on searchable encryption [DPP18] and oblivious algorithms [AKL+20a, SCSL11] adopt perfectly secure ORAMs as a building block for solving small-sized sub-problems that are necessary for solving the bigger problem. Finally, as Chan et al. [CNS18] point out, perfectly secure ORAM can also have theoretical applications in perfectly secure multi-party computation (MPC) and other contexts.

**Prior results on perfectly secure ORAMs and OPRAMs.** Prior works have considered two types of perfect ORAM/OPRAM constructions:

- 1. Constructions whose performance bounds hold in expectation [DMN11, CNS18]: typically these constructions are Las Vegas algorithms that might occasionally runs longer than the desired performance bounds. Specifically, the original perfect ORAM construction by Damgård et al. [DMN11] achieves  $O(\log^3 N)$  expected simulation overhead and  $O(\log N)$  server space blowup. Subsequently, Chan et al. [CNS18] improved Damgård et al. [DMN11]'s result and achieved  $O(\log^3 N)$  expected performance overhead and only O(1) server space blowup. Furthermore, Chan et al. [CNS18] also extended their construction to the parallel setting resulting in an OPRAM scheme with the same asymptotics. For both Damgård et al. [DMN11] and Chan et al. [CNS18], the stated performance bounds hold not just in expectation but in fact, with  $1 - \exp(-\Omega(\log^2 N))$  probability. However, if N is small, say, polylogarithmic in some security parameter, this failure probability can be non-negligible.

- 2. Constructions with deterministic performance bounds. It would obviously be nice to have perfect ORAM/OPRAM constructions whose performance bounds hold not just in expectation or with high probability, but with probability 1. With this goal in mind, Raskin et al. [RS19]<sup>4</sup> show a perfect ORAM construction achieving a worst-case simulation overhead of  $O(\sqrt{N} \frac{\log N}{\log \log N})$ .

As mentioned earlier, our new techniques enable asymptotical improvements for both of these above categories.

# 2 Technical Overview

We start with an informal and intuitive exposition of our main technical ideas before formalizing the definitions, constructions, and proofs in subsequent sections. For simplicity, in the roadmap we first focus on describing the sequential ORAM version. We briefly comment on the technicalities that lie in the way of parallelizing the scheme in Section 2.4, deferring the full details of the parallel construction to the formal technical sections later.

# 2.1 Background on Perfect ORAM

In a recent work, Chan et al. [CNS18] propose a perfectly secure ORAM with  $O(\log^3 N)$  simulation overhead. At a high level, their scheme is inspired by the hierarchical ORAM paradigm by Goldreich and Ostrovsky [GO96,Gol87], but relies on a non-blackbox "recursive position map" trick to remove the pseudo-random function (PRF) in Goldreich and Ostrovsky's construction [GO96,Gol87].

<sup>&</sup>lt;sup>4</sup>In different settings presented by Raskin et al., we focus on the setting of O(1) client storage [RS19, Fig. 1].

#### 2.1.1 Position-based Hierarchical ORAM

First, imagine that the client can store per-block metadata and we will later remove this strong assumption through a non-blackbox recursion technique. Specifically, imagine that the client remembers where exactly each block is residing on the server. In this case, we can construct a perfectly secure ORAM as follows — henceforth this building block is called "position-based ORAM" since we assume that the correct position label for every requested block is known to the client.

**Hierarchical levels.** The server-side data structure is organized into  $\log N + 1$  levels numbered  $0, 1, \ldots, \log N$  where level *i* is

- either *empty*, in which case it stores no blocks;

- or *full*, in which case the level stores  $2^i$  real blocks plus  $2^i$  dummy blocks in a randomly permuted fashion (we also say that the level has *capacity*  $2^i$ ).

Each block, whose logical addresses range from 0 to N-1, resides in exactly one of the levels at a random position within the level.

**Fetch phase.** Every time a block with address addr is requested, the client looks up the block's position. Suppose that the block resides in the *i*-th position of level  $\ell$ . The client now visits for one block per full level from the server — note that the levels are visited in a fixed order from 0 to log N:

- for level  $\ell$  (i.e., where the desired block resides), the client reads precisely the *i*-th position to fetch the real block; it then marks the visited position as dummy;

- for every other level  $\ell' \neq \ell$ , the client reads a random unvisited dummy block (and marks the corresponding block on the server as dummy for obliviousness).

Maintain phase. Every time a block B has been fetched by the client, it updates the block B's contents if this is a write request. Now, imagine that levels  $0, 1, \ldots, \ell^*$  are all full and either level  $\ell^* + 1$  is empty or  $\ell^* = \log N$ . The client will now merge the newly fetched (and possibly updated) block B and levels  $0, 1, \ldots, \ell^*$  into the "target" level  $\ell_{tgt} := \min(\ell^* + 1, \log N)$  — this procedure is often called "rebuilding" the level  $\ell_{tgt} := \min(\ell^* + 1, \log N)$ . At the end of the rebuild, it marks level  $\ell_{tgt}$  as full and every smaller level as empty.

To merge consecutively full levels into the next empty level (or the largest level), the goal is to implement the following ideal functionality *obliviously*:

- 1. extract all *real* blocks to be merged and place them in an array called A;

- 2. pad A with dummy blocks to a total length of  $2 \cdot 2^{\ell_{\text{tgt}}}$  and randomly permute the resulting array.

Chan et al. [CNS18] shows how to achieve the above obliviously — even though the client has only O(1) blocks of private cache — through oblivious sorting (which can be instantiated using the AKS sorting network [AKS83]). The cost of rebuilding a level of capacity n is dominated by the oblivious sorting on O(n) blocks, which hast a cost of  $O(n \log n)$ .

Note that the above construction guarantees that whenever a real block is accessed, it is moved into a smaller level. Thus, in every level, each real or dummy block is accessed at most once before the level is rebuilt; and this is important for obliviousness. For this reason, later in our technical sections, we name each level in this hierarchy an oblivious "one-time memory". Note also that the number of dummies in a level must match the total number of accesses the level can support before it is rebuilt again. Additional details about dummy positions. The above description implicitly assumed that for a level the desired block does not reside in, the client is informed of the position of a random unvisited dummy block. If the client does not store this information locally, it can construct a (per-level) metadata array M on the server every time a level is rebuilt. When a block is being requested, the client can sequentially scan the metadata array at *every* level (including the level where the desired block resides) to discover the location of the next unvisited dummy (residing at a random unvisited location in the level).

As Chan et al. [CNS18] show, such a dummy metadata array can be constructed with  $O(n \log n)$  overhead using oblivious sorting too, at the time a level of capacity n is rebuilt.

**Overhead.** Summarizing, in the position-based ORAM, after every  $2^{\ell}$  requests, the level  $\ell$  will be rebuilt, paying  $O(2^{\ell} \cdot \log(2^{\ell}))$  cost. Amortizing the total cost over the sequence of requests, it is not difficult to see that the average cost per request is  $O(\log^2 N)$ .

# 2.1.2 Recursive Position Map

So far we have assumed that whenever the client wants to fetch a block, it can magically find out the block's position on the server. To remove this assumption, Chan et al. [CNS18] propose to recursively store the blocks' position labels in smaller ORAMs until the ORAM's size becomes constant, resulting in  $O(\log N)$  ORAMs henceforth denoted  $ORAM_0, ORAM_1, \ldots, ORAM_D$  respectively, where  $ORAM_i$  stores the position labels of all blocks in  $ORAM_{i+1}$  for  $i \in \{0, 1, \ldots, D\}$ . We often call  $ORAM_D$  the "data ORAM" and every other ORAM a "metadata ORAM"; we also refer to the index i as the *depth* of  $ORAM_i$ . Now, suppose that each block can store  $\Omega(\log N)$  bits of information, such that we can pack the position labels of at least 2 blocks into a single block. In this case, each  $ORAM_i$  is twice smaller in capacity than  $ORAM_{i+1}$  and thus  $ORAM_0$  would be of O(1) size — thus operations to  $ORAM_0$  can be supported trivially by scanning through the whole  $ORAM_0$  consuming only constant cost.

As Chan et al. [CNS18] show, in the hierarchical ORAM context such a recursion idea does not work in a straightforward blackbox manner, but needs a special "coordinated rebuild" technique which we now explain. Henceforth, suppose that each block's logical address addr is  $\log N$  bits long, and we use the notation  $\operatorname{addr}^{\langle d \rangle}$  to denote the address addr, written in binary format, truncated to the first d bits.

- Fetch phase (straightforward): To fetch a block at some logical address addr, the client looks up logical address addr<sup> $\langle d \rangle$ </sup> in each ORAM<sub>d</sub> for d = 0, 1, ..., D sequentially. Since the block at logical address addr<sup> $\langle d \rangle$ </sup> in ORAM<sub>d</sub> stores the position labels for the two blocks at logical addresses addr<sup> $\langle d \rangle$ </sup> ||0 addr<sup> $\langle d \rangle$ </sup>||1 in ORAM<sub>d+1</sub>, the client is always able to find out the position of the block in the next recursion depth before it performs a lookup there.

- Maintain phase (coordinated rebuild): The maintain phase needs special treatment such that the rebuilds at all recursion depths are coordinated. Specifically, whenever the data  $ORAM_D$  is rebuilding the level  $\ell$ , each other recursion depth  $ORAM_d$  would be rebuilding level min $(\ell, d)$  in a coordinated fashion note that each  $ORAM_d$  has only d levels.

The main goal of the coordination is for each  $\mathsf{ORAM}_d$  to pass the blocks' updated position labels back to the parent depth  $\mathsf{ORAM}_{d-1}$ . More specifically, recall that when  $\mathsf{ORAM}_d$  rebuilds a level  $\ell$ , all real blocks in the level would now be placed at a new random position. When these new positions have been decided,  $\mathsf{ORAM}_d$  must inform the corresponding metadata blocks in  $\mathsf{ORAM}_{d-1}$ the new position labels. The coordinated rebuild is possible due to the following invariant which is not hard to observe (recall that  $\mathsf{addr}^{\langle d \rangle}$  is the block that stores the position labels for the block  $\mathsf{addr}^{\langle d+1 \rangle}$  in  $\mathsf{ORAM}_{d+1}$ ):

For every addr, the block at address  $\operatorname{addr}^{\langle d \rangle}$  in  $\operatorname{ORAM}_d$  is always stored at a smaller or equal level relative to the block at address  $\operatorname{addr}^{\langle d+1 \rangle}$  in  $\operatorname{ORAM}_{d+1}$ .

Chan et al. [CNS18] show how to rely on oblivious sorting to accomplish this coordinated rebuild, paying  $O(n \log n)$  to pass the new position labels of level- $\ell$  in ORAM<sub>d</sub> to the parent ORAM<sub>d-1</sub> where  $n = 2^{\ell}$  is the level's capacity.

# 2.1.3 Analysis

It is not hard to see that the entire fetch phase consumes  $O(\log^2 N)$  overhead where one  $\log N$  factor comes from the number of levels within each recursion depth, and another comes from the number of recursion depths. The maintain phase, on the other hand, consumes  $O(\log^3 N)$  amortized cost where one logarithmic factor arises from the number of depths, one arises from the number of levels within each depth, and the last one stems from the additional logarithmic factor in oblivious sorting.

To asymptotically improve the overhead, one promising idea is to somehow balance the fetch and maintain phases. This idea has been explored in computationally secure ORAMs first by Kushilevitz et al. [KLO12] and later improved in subsequent works [CGLS17]. Unfortunately as we explain in Appendix B, Kushilevitz et al.'s rebalancing trick is not compatible with known perfectly secure ORAMs. Thus we need fundamentally new techniques for realizing such a rebalancing idea.

# 2.2 Building Blocks

Before we introduce our new algorithms, we describe two important oblivious algorithm building blocks that were discovered in very recent works [AKL<sup>+</sup>20a, Pes18].

**Tight compaction.** Tight compaction is the following task: given an input array containing m balls where each ball is tagged with a bit indicating whether it is real or dummy, produce an output array containing also m balls such that all real balls in the input appear in the front and all dummies appear at the end.

In a very recent work called OptORAMa [AKL<sup>+</sup>20a], the authors show how to accomplish tight compaction obliviously in O(1) overhead. Their algorithm can be expressed as a linear-sized circuit (of constant fan-in and fan-out), consisting only of boolean gates and swap gates, where a boolean gate can perform boolean computations on two input bits; and a swap gate takes in a bit and two balls, and decides to either swap or not swap the two balls.

**Intersperse.** The same work OptORAMa [AKL<sup>+</sup>20a] described another linear-time, randomized oblivious algorithm called "intersperse", which can be used to accomplish the following task: given two randomly shuffled input arrays  $\mathbf{I}$  and  $\mathbf{I'}$  (where the permutations used in the shuffles are hidden from the adversary), create an output array of length  $|\mathbf{I}| + |\mathbf{I'}|$  that contains all elements from the two input arrays, and moreover, all elements in the output array are randomly shuffled in the view of the adversary.

### 2.3 A New Rebalancing Trick for Perfectly Secure ORAMs

We propose new techniques for instantiating such a rebalancing trick. Our idea is to introduce a notion called a fat-block. A fat-block is a bundle of  $\chi := \log N$  normal blocks; thus to access a fat-block requires paying  $\chi = \log N$  cost.

Imagine that in each metadata ORAM, the atomic unit of storage is a fat-block (rather than a normal block). Since each fat-block can pack  $\chi = \log N$  position labels, the depth of the recursion is now  $\log_{\chi} N = \log N / \log \log N$ , i.e., a  $\log \log N$  factor smaller than before (see Section 2.1.2). More concretely, a metadata ORAM  $\operatorname{ORAM}_d$  at depth d stores a total of  $\chi^d$  metadata fat-blocks — for the time being we assume that N is a power of  $\chi$  for simplicity, and let  $D := \log_{\chi} N + 1$  be the number of recursion depths such that the total storage is still O(N) blocks (but our idea can easily be generalized to the case when N is not a power of  $\chi$ ). Within each  $\operatorname{ORAM}_d$ , as before, we have a total of  $d \log \chi + 1$  levels where each level  $\ell$  can store  $2^{\ell}$  fat-blocks.

It is not hard to see that the fetch phase would now incur  $O(\log^3 N/\log \log N)$  cost across all recursion depths — in comparison with before, the extra log N factor arises from the cost of reading a fat-block, and the log log N factor saving comes from the log log N saving in depth.

Our hope is that now with the smaller recursion depth, we can accomplish the maintain phase in amortized  $O(\log^3 N/\log \log N)$  cost. Recall that each level  $\ell$  in a metadata  $\mathsf{ORAM}_d$  now contains  $2^{\ell}$  fat-blocks. The crux is to be able to rebuild a level containing  $2^{\ell}$  fat-blocks in cost that is linear in the level's total size, that is,  $2^{\ell} \cdot \chi$ . Note that if we naïvely used oblivious sorting on fat-blocks (like in Section 2.1.1) to accomplish this, the cost would have been  $2^{\ell} \cdot \chi \cdot \log(2^{\ell})$ .

To resolve this challenge, the following two insights are critical:

- Sparsity: First, observe that each level in a metadata ORAM is sparsely populated: although the entire level, say, level  $\ell$ , has the capacity to store  $2^{\ell} \cdot \chi$  position labels, the level is rebuilt after every  $2^{\ell}$  requests. Thus in fact only  $2^{\ell}$  of these position label entries are populated.

- Residual randomness: The second important observation is that the unvisited fat-blocks contained in any level appear in a random order where the randomness of the permutation is hidden from the adversary — note that a similar observation was first made in the recent PanORAMa work [PPRY18] by Patel et al.

More specifically, suppose that to start with, a level contains n fat-blocks including some reals and some dummies, and all of these n fat-blocks have been randomly permuted (where the randomness of the permutation is hidden from the adversary). As the client visits fat-blocks in a level, the adversary learns which blocks are visited. Now, among all the unvisited blocks, there are both real and dummy blocks and all these blocks are equally likely to appear in any order w.r.t. the adversary's view.

We now explain how to rely on the above insights to rebuild a level containing  $n = 2^{\ell}$  fat-blocks in  $O(n \cdot \chi)$  overhead — note that at most half of these fat-blocks are real, and the remaining are dummy. From Section 2.1.2, we learned that to rebuild a level containing n fat-blocks, it suffices to realize the following functionality obliviously:

- a) *Merge.* The first step of the rebuild is to merge consecutively full levels plus the newly accessed fat-block into the next empty level (or the largest level). After this merge step, this new level is marked full and every smaller level is marked empty.

- b) *Permute.* After the above merge step, the resulting array containing n fat-blocks must be randomly permuted (and their positions after the permutation will then be passed to the parent depth).

- c) Update. After the permutation step, each real fat-block in the level whose logical address is addr must receive up to  $\chi$  updated positions from the child recursion depth, i.e., the fat-block at logical address addr wants to learn where the fat-blocks at logical addresses addr||0, addr||1, ..., addr $||(\chi 1)$  newly reside in the child depth.

d) Create dummy metadata. Finally, create a dummy metadata array to accompany this level: the dummy metadata array containing n entries where each entry is  $O(\log N)$  bits (note that an entry is a normal block, not a fat-block). This array should store the positions of all dummy fat-blocks contained in the level in a randomly permuted order, and padded with  $\perp$  to a length of n.

**Realizing "merge + permute".** We first explain how to accomplish the "merge + permute" steps. For simplicity we focus on explaining the case where consecutive full levels are merged into the next empty level (since it would be fine if the merging into the largest level *alone* is done naïvely using oblivious sort on all fat-blocks). Here it is important to rely on the residual randomness property mentioned earlier. Suppose the levels to be merged contain  $1, 2, 4, \ldots, n/2$  fat-blocks respectively; besides these, the most recently accessed fat-block also wants to be merged. Recall that in all of these levels to be merged, the unvisited blocks appear in a random order w.r.t. the adversary's view. Thus, we can simply do  $O(\log n)$  cascading merges using **Intersperse**, every time merging two arrays each containing  $2^i$  fat-blocks into an array containing  $2^{i+1}$  fat-blocks.

**Realizing "update".** At this moment, let us not view the level as an array of n fat-blocks any more, but as an array of  $O(n \cdot \chi)$  position entries. For realizing the "update" step in  $O(n \cdot \chi)$  overhead, the key insight is to exploit the sparsity.

Recall that the problem we need to solve boils down to the following. Imagine there is a destination array D consisting  $O(n \cdot \chi)$  position entries among which O(n) entries are populated (i.e., real), and all remaining entries are dummy. Additionally, there is a source array S consisting of O(n) entries. In both the source S and the destination D, each real entry is of the form (k, v) where k denotes a key and v denotes a payload value; further, in the destination D, every real entry must have a distinct key. Now, we would like to route each real entry  $(k, v) \in S$  to the corresponding entry with the same key in the destination array D.

Exploiting the sparsity in the problem definition, we devise the following algorithm where an important building block is linear-time *oblivious tight compaction* (see Section 2.2).

First, we rely on oblivious tight compaction to compact the destination array D, resulting in a compacted array  $\tilde{D}$  consisting of only O(n) entries. Moreover, recall that oblivious tight compaction can be viewed as a *circuit* consisting of boolean gates and swap gates. When we compact the destination array D, each swap gate remembers the routing decision since later it will be useful to run this circuit in the reverse direction. After the compaction, we can now afford to pay the cost of oblivious sorting. Through O(1) oblivious sort operations, each entry in the source Scan route itself to each entry in the compacted destination  $\tilde{D}$  — this can be accomplished through a standard technique called oblivious routing [CS17, BCP16], which has a cost of  $O(n \log n)$ . Now, by running the aforementioned tight compaction circuit in the reverse direction, we can route each element of the compacted destination  $\tilde{D}$  back into the original destination array D.

It is not difficult to see that the above steps require only  $O(n \cdot (\chi + \log n))$  cost.

**Obliviously create dummy metadata array.** Finally, obliviously creating the dummy metadata array is easy: this can be accomplished by writing down  $O(\log N)$  bits of metadata per fat-block, and then by performing a combination of oblivious random permutation and oblivious sort on the resulting metadata array.

#### 2.4 Parallelizing the Scheme

So far, for simplicity we have focused on the sequential case. To obtain our OPRAM result, we need to make the above scheme parallel. To this end, we will rely on the OPRAM techniques by Chan et al. [CNS18]. However, we are faced with the new challenge of how to make the **Intersperse**

algorithm parallel. Recall that given two randomly shuffled arrays  $\mathbf{I}_0$  and  $\mathbf{I}_1$ , **Intersperse** produces a randomly shuffled output array combining the two input arrays. The linear-time **Intersperse** algorithm described by Asharov et al. [AKL<sup>+</sup>20a] consists of two steps: 1) sample a random auxiliary array consists of a  $|\mathbf{I}_0|$  number of 0s and  $|\mathbf{I}_1|$  number of 1s; and 2) run tight compaction on the auxiliary array, and then apply the reverse routing to the elements of  $\mathbf{I}_0||\mathbf{I}_1$ . While the second step can be parallelized [AKL<sup>+</sup>20b], the first step is inherently sequential in Asharov et al. [AKL<sup>+</sup>20a]. Our task therefore is to parallelize the first step, and importantly, we want that the output array to be *perfectly* randomly permuted — however we allow the algorithm to be Las Vegas and this will get us the  $O(\log^3 N/\log \log N)$  result where the performance bound holds with high probability. We will use algorithmic ideas from Asharov et al. [AKL<sup>+</sup>] (which was proposed earlier but only for statistical obliviousness), and the algorithmic details on how to achieve this are deferred to Section 4. Note that since the runtime of the Las Vegas algorithm leaks information about the lengths of the two input arrays  $\mathbf{I}_0$  and  $\mathbf{I}_1$ , our **Intersperse** abstraction is in fact slightly weaker than that of Asharov et al. [AKL<sup>+</sup>20a] — we leak the lengths of both input arrays and not just the sum of the two lengths. However, it turns out that the weaker version is enough to get our result.

# 2.5 Roadmap of Subsequent Formal Sections

In the subsequent technical sections, we formalize the blueprint described in this section. Our formal description is modularized which will facilitate formal analysis and proofs. Moreover, in our formal section we will directly present the OPRAM result (since the sequential ORAM is a special case of the more general OPRAM result).

# **3** Preliminaries

# 3.1 PRAMs and Oblivious Simulation

**PRAMs and OPRAMs.** We consider how to obliviously simulate parallel algorithms in the standard Parallel Random-Access Machine (PRAM) model. Both the original (insecure) algorithm and the obliviously simulated algorithm run on a PRAM machine with m CPUs; and it is required that the oblivious counterpart must always give the same output distribution as the original PRAM on any input. Let [N] be the address space of the shared memory in the PRAM. We assume without loss of generality that  $N \geq m$  throughout this paper<sup>5</sup>.

More concretely, the original PRAM algorithm will generate a batch of *m* memory requests in each parallel step, where each memory request wants to either read a logical address or write a logical address. In essence we need to devise an oblivious method to serve every batch of *m* memory requests and always ensure correctness. *Obliviousness requires that every request sequence of the same length results in identical access pattern distribution*. Throughout the paper, the memory access pattern of a PRAM means the ordered vector of the physical memory locations accessed by each CPU in all steps (and within each step, the physical locations are ordered by the identifiers of the CPUs making the access).

For write conflict resolution, we allow the original (insecure) PRAM to support concurrent reads and concurrent writes (CRCW) with an arbitrary, parametrizable rule for write conflict resolution. In other words, there exists some priority rule to determine which write operation takes effect if there are multiple concurrent writes in some parallel step. For the oblivious-simulation PRAM,

<sup>&</sup>lt;sup>5</sup>If N < m, the oblivious simulation can be achieved by assigning at most one address to each CPU and then performing oblivious routing [BCP16], which takes only  $O(\log m)$  overhead.

we assume a "concurrent read, exclusive write" PRAM (CREW). In other words, our OPRAM algorithm must ensure that there are no concurrent writes at any time. Note that allowing the original PRAM to be CRCW but restricting the compile oblivious PRAM to be CREW makes it a stronger result.

In our paper, we will assume that each CPU can perform word-level operations including addition, subtraction, and bit-wise boolean operations in unit time. Further, we make the following assumptions related to sampling the randomness required by the algorithm: 1) let w denote the number of bits in a word, we shall assume that each CPU can sample a uniform random number from [m] for any  $m \leq 2^w$  in unit time; 2) we assume that for any  $a < b \leq 2^w$ , each CPU can sample a Bernoulli random variable with probability a/b in unit time (which follows by the first assumption). Specifically, the first assumption above is needed by the Alonso and Schott [AS96] oblivious random permutation and the second assumption is needed by our parallel **Intersperse** algorithm in Section 4.

Appendix A provides more detailed definitions on PRAMs and OPRAMs.

Metrics. We will use the standard notion of *simulation overhead* to characterize an OPRAM's performance. If a PRAM that consumes m CPUs and completes in T parallel steps can be obliviously simulated by an OPRAM that completes in  $\gamma \cdot T$  steps also with m CPUs, then we say that the simulation overhead is  $\gamma$ .

More generally, suppose that an ample (i.e., unbounded) number of CPUs are available: in this case if algorithm can be completed in T parallel steps consuming  $m_1, m_2, \ldots, m_T$  CPUs in each step respectively, then we say that the algorithm can be completed in T depth and  $W := \sum_{t \in [T]} m_t$  total work. Therefore, for an OPRAM, if each parallel step of the original PRAM (i.e., a batch m memory requests) can be completed in W total work and T = O(W/m) depth then the OPRAM has simulation overhead W/m.

**Oblivious simulation of a non-reactive functionality.** For defining the security of intermediate building blocks, we now define what it means to *obliviously realize* a non-reactive functionality. Let  $\mathcal{F} : \{0,1\}^* \to \{0,1\}^*$  be a possibly randomized functionality. We say that  $M_{\mathcal{F}}$  is a perfect oblivious simulation (or oblivious simulation for short) of  $\mathcal{F}$  with leakage  $\mathcal{L}$ , iff there exists a simulator Sim, such that for every input  $x \in \{0,1\}^*$ , the following real-world and ideal-world distributions are identical:

- Real world: execute  $M_{\mathcal{F}}(x)$  and let y be the output and Addr be the memory access patterns; output  $(y, \operatorname{Addr})$ ;

- *Ideal world*: output  $(\mathcal{F}(x), Sim(\mathcal{L}(x)))$ .

For simplicity, if the leakage function  $\mathcal{L}(x) = |x|$ , we often say that  $M_{\mathcal{F}}$  is a perfect oblivious simulation of  $\mathcal{F}$  (omitting the leakage function) for short.

Modeling input assumptions. Some of our building blocks provide perfect obliviousness only if the input array is randomly shuffled and the corresponding randomness concealed. More formally, suppose that a machine M(A, x) and a functionality  $\mathcal{F}(A, x)$  both take in an array  $A \in D^n$  where  $D \in \{0, 1\}^{\ell}$  as input and possibly an additional input  $x \in \{0, 1\}^*$ . Formally, we say that "the machine M is a perfect oblivious simulation of the functionality  $\mathcal{F}$  with leakage  $\mathcal{L}$  assuming that the input array A is randomly shuffled", iff for every  $A \in D^n$  and every  $x \in \{0, 1\}^*$ , the following real-world and ideal-world distributions are identical:

• Real world: randomly shuffle the array A and obtain A', execute  $M_{\mathcal{F}}(A', x)$  and let y be the output and Addr be the memory access patterns; output (y, Addr);

• *Ideal world*: output  $(\mathcal{F}(A, x), \mathsf{Sim}(\ell, \mathcal{L}(A, x)))$ .

Note that the above definition considers only a single input array A, but there is a natural generalization for algorithms that take two or more input arrays — in this case we may require that some or all of these input arrays be randomly shuffled to achieve perfect obliviousness.

# 3.2 Oblivious Algorithm Building Blocks

We describe some algorithmic building blocks. Unless otherwise noted, for algorithms that operate on arrays of n elements, we always assume that a single memory word is wide enough to store the index of each element within the array, i.e.,  $w \ge \log n$  where w is the bit-width of each PRAM word. We typically use the following notation: let B denote the bit-width of each element, and let  $\beta := \lceil B/w \rceil$  denote the number of memory words it takes to store each element.

### 3.2.1 Oblivious Sort

Oblivious sorting can be accomplished through a sorting network such as the famous construction by Ajtai, Komlós, and Szemerédi [AKS83]. We restate this result in the context of PRAM algorithms:

**Theorem 3.1** (Oblivious sorting [AKS83]). There exists a deterministic, oblivious algorithm that sorts an array of n elements consuming  $O(\beta \cdot n \log n)$  total work and  $O(\log n)$  depth where  $\beta \geq 1$  denotes the number of memory words it takes to represent each element.

### 3.2.2 Oblivious Random Permutation

Let ORP be an algorithm that upon receiving an input array X, outputs a permutation of X. Let  $\mathcal{F}_{perm}$  denote an ideal functionality that upon receiving the input array X, outputs a perfectly random permutation of X. We say that ORP is a *perfectly oblivious* random permutation, iff it is a perfect oblivious simulation of the functionality  $\mathcal{F}_{perm}$ .

Alonso and Schott [AS96] construct a parallel random permutation algorithm that takes  $O(n \log^2 n)$  total work and  $\log^2 n$  depth to randomly permute *n* elements. Although achieving obliviousness was not a goal of their paper, it turns out that their algorithm is also perfectly oblivious, giving rise to the following theorem:

**Theorem 3.2** (Alonso-Schott ORP). Suppose that for any integer  $m \in [n]$ , each CPU of the PRAM can sample an integer uniformly at random from [m] in unit time. Then, there is a perfectly oblivious algorithm that permutes an array of n elements in  $O(\beta \cdot n \log n + n \log^2 n)$  total work and  $O(\log^2 n)$  depth where  $\beta \geq 1$  denotes the number of memory words for representing each element.

A few recent works [CCS17,AKL<sup>+</sup>20a] describe another perfectly oblivious random permutation algorithm which is asymptotically more efficient but the algorithm is Las Vegas, i.e., the algorithm satisfies perfect obliviousness and correctness, but with a small probability the algorithm may run longer than the stated bound.<sup>6</sup> Below, we restate this result in the form that we desire in this paper — the specific theorem stated below arises from the improved analysis of Asharov et al. [AKL<sup>+</sup>20a]; for the performance bounds, we state an *expected* version and a *high-probability* version.

**Theorem 3.3** (A Las Vegas ORP algorithm). Let  $\beta \geq 1$  denote the number of memory words it takes to represent each element. There exists a Las Vegas perfectly oblivious random permutation

$<sup>^{6}</sup>$ Using more depth but only unbiased random bits, Czumaj [Czu15] shows a Las Vegas switching network to achieve the same abstraction.

construction that completes in expected  $O(\beta \cdot n \log n)$  total work and expected  $O(\log n)$  depth. Furthermore, except with  $n^{-\Omega(\sqrt{n})}$  probability, the algorithm completes in  $O(\beta \cdot n \log n)$  total work and  $O(\log n)$  depth.

Note that the above theorem gives a high-probability performance bound for sufficiently large n. Later in our OPRAM construction, we will adopt ORP for problems of different sizes — we will use Theorem 3.3 for sufficiently large instances and use Theorem 3.2 for small instances.

# 3.2.3 Oblivious Routing

Oblivious routing [BCP16] is the following primitive where n source CPUs wish to route data to n' destination CPUs based on the key.

• Inputs: The inputs contain two arrays: 1) a source array  $\operatorname{src} := \{(k_i, v_i)\}_{i \in [n]}$  where each element is a (key, value) pair or a dummy element denoted  $(\bot, \bot)$ ; and 2) a destination array  $\operatorname{dst} := \{k'_i\}_{i \in [n']}$  containing a list of (possibly dummy) keys.

We assume that each (non-dummy) key appears no more than C times in the src array where C = O(1) is a known constant; however, each (non-dummy) key can appear any number of times in dst.

• Outputs: We would like to output an array  $\mathsf{Out} := \{v'_{i,j}\}_{i \in [n'], j \in [C]}$  where  $(v'_{i,1}, \ldots, v'_{i,C})$  contains all the values contained in **src** whose keys match  $k'_i$  (padded with  $\perp$ ).

**Theorem 3.4** (Oblivious routing [BCP16,CS17,CCS17]). There exists a perfectly oblivious routing algorithm that accomplishes the above task in  $O(\log(n + n'))$  depth and  $O(\beta \cdot (n + n') \log(n + n'))$  total work where  $\beta \geq 1$  denotes the number of words it takes to represent each element.

# 3.2.4 Tight Compaction

As mentioned in Section 2.2, tight compaction is the following task: given an input array containing n elements where each element is tagged with a bit indicating whether it is real or dummy, produce an output array containing also n elements such that all real elements in the input appear in the front and all dummies appear at the end. We will use the parallel oblivious tight compaction of Asharov et al. [AKL<sup>+</sup>20b] running in linear work and logarithmic depth.

**Theorem 3.5** (Oblivious tight compaction [AKL<sup>+</sup>20b]). There exists a deterministic, oblivious tight compaction algorithm that compacts an array of n elements in total work  $O(\beta \cdot n)$  and depth  $O(\log n)$  where  $\beta \geq 1$  denotes the number of words it takes to represent each element.

We point out that Asharov et al.'s oblivious parallel compaction algorithm [AKL+20b] works in the so-called *indivisibility* model, that is, the payload of the elements are moved around as opaque strings.

# 4 Parallel Intersperse

# 4.1 Definition

Inspired by recent works [PPRY18, AKL<sup>+</sup>20a], we define a building block called **Intersperse** which can be used to mix two input arrays. Here we adopt a definition that differs slightly from Asharov et al. [AKL<sup>+</sup>20a] — in our definition the algorithm receives the two input arrays separately and

the lengths of both input arrays are *publicly known*. In comparison, in Asharov et al. [AKL<sup>+</sup>20a]'s definition, the **Intersperse** algorithm receives the concatenation of the two input arrays and only the sum of their lengths is public but not each array's individual length (i.e., our definition is weaker in hiding the lengths of input arrays). More specifically, **Intersperse** has the following syntax.

- Input. Two arrays  $(\mathbf{I}_0, \mathbf{I}_1)$  of size  $n_0$  and  $n_1$ , where  $n_0 + n_1 = n$ .

- **Output.** An array **B** of size *n* that contains all elements of  $\mathbf{I}_0$  and  $\mathbf{I}_1$ . Each position in **B** will hold an element from either  $\mathbf{I}_0$  or  $\mathbf{I}_1$ , chosen uniformly at random and the choices are concealed from the adversary.

We now define the security notion required for **Intersperse**. We require that when we run **Intersperse** on two input arrays  $\mathbf{I}_0$  and  $\mathbf{I}_1$  that are both randomly shuffled (based on a secret permutation), the resulting array will be randomly shuffled (based on a secret permutation) too. More formally stated, we require that **Intersperse** is a perfect oblivious simulation of the following  $\mathcal{F}_{\text{shuffle}}(\mathbf{I}_0, \mathbf{I}_1)$  functionality with leakage ( $|\mathbf{I}_0|, |\mathbf{I}_1|$ ), provided that the two input arrays are randomly shuffled. Henceforth we assume that the bit-width of each element in the input arrays is a publicly known parameter that the scheme is implicitly parametrized with.

$\mathcal{F}_{shuffle}(\mathbf{I}_0, \mathbf{I}_1)$ :

- 1. Choose a permutation  $\pi : [n] \to [n]$  uniformly at random where  $n := |\mathbf{I}_0| + |\mathbf{I}_1|$ .

- 2. Let  $\mathbf{I}$  be the concatenation of  $\mathbf{I}_0$  and  $\mathbf{I}_1$ .

- 3. Initialize an array **B** of size *n*. Assign  $\mathbf{B}[i] := \mathbf{I}[\pi(i)]$  for every i = 1, ..., n.

- 4. **Output:** The array **B**.

The recent work OptORAMa by Asharov et al.  $[AKL^+20a]$  showed how to construct an **Inter-sperse** algorithm in linear time, i.e., O(n); however, their algorithm is inherently sequential. A manuscript by Asharov et al.  $[AKL^+]$  considered how to devise a parallel version of **Intersperse** in an attempt to make OptORAMa  $[AKL^+20a]$  parallel; but their parallel **Intersperse** algorithm achieves only statistical security. Below we describe a variant of the parallel algorithm of Asharov et al.  $[AKL^+]$  that is perfectly secure but leaks  $(|\mathbf{I}_0|, |\mathbf{I}_1|)$  as defined above.

# 4.2 A Parallel Intersperse Algorithm

# 4.2.1 Warmup

Asharov et al. [AKL<sup>+</sup>20a] used the following method to construct an **Intersperse** algorithm:

1. First, initialize an array Aux of size n that has  $n_0$  zeros and  $n_1$  ones, where the zeros' positions are chosen uniformly at random (and the remaining positions are ones). More formally, the algorithm must obliviously simulate the following  $\mathcal{F}_{\text{SampleAux}}(n, n_0)$  functionality with leakage  $(n, n_0)$ .

$\mathcal{F}_{\text{SampleAux}}(n, n_0)$  – Sample Auxiliary Array

- Input: Two numbers  $n, n_0 \in \mathbb{N}$  such that  $n_0 \leq n$ .

- The functionality: Sample an array Aux of n bits uniformly at random conditioned on having  $n_0$  zeros and  $n n_0$  ones. Output Aux.

2. Next, we route elements 1-to-1 from  $\mathbf{I}_0$  to zeros in Aux and 1-to-1 route elements from  $\mathbf{I}_1$  to ones in Aux. This can be accomplished by running oblivious tight compaction circuit (Theorem 3.5) to pack all the 0s in Aux in the front. During the process, all swap gates remember their routing decisions. Now, we can run the oblivious tight compaction circuit in reverse and on the input array  $\mathbf{I}_0 || \mathbf{I}_1$ . It is not hard to see that in the outcome, every 0 position in Aux would receive an element from  $\mathbf{I}_0$  and every 1 position in Aux would receive an element from  $\mathbf{I}_1$ .

Asharov et al.  $[AKL^+20a]$  proved that the above algorithm indeed realizes the **Intersperse** abstraction as defined above.<sup>7</sup> Moreover, their oblivious tight compaction algorithm is parallel in nature (see Section 3.2.4); unfortunately they adopt a highly sequential procedure for generating the Aux array.

Therefore, it suffices to devise a parallel procedure for generating such an Aux array. More formally, we would like to devise an algorithm that obliviously simulates the functionality  $\mathcal{F}_{\text{SampleAux}}(n, n_0)$ allowing leakage  $(n, n_0)$ .

# 4.2.2 A Naive Algorithm

A naïve algorithm is the following: simply write down exactly  $n_0$  number of 0s and  $n - n_0$  number of 1s, apply an oblivious random permutation to permute the array, and output the result. If we use Theorem 3.2 to instantiate this naïve algorithm, we obtain the following theorem:

**Theorem 4.1** (Naïve parallel algorithm for sampling Aux). For any  $n_0 \leq n$ , there exists an algorithm that perfectly obliviously simulates  $\mathcal{F}_{\text{SampleAux}}(n, n_0)$ ; moreover, for sampling an Aux array of length n, the algorithm completes in  $O(n \log^2 n)$  total work and  $O(\log^2 n)$  depth.

This immediately gives rise to the following corollary for **Intersperse** due to the result of Asharov et al. [AKL<sup>+</sup>20a]:

**Corollary 4.2** (Naïve parallel **Intersperse**). There exists an algorithm that perfectly obliviously simulates  $\mathcal{F}_{\text{shuffle}}$  for two randomly shuffled input arrays. Moreover, the algorithm completes in  $O(\beta n + n \log^2 n)$  total work and  $O(\log^2 n)$  depth where n denotes the sum of the lengths of the two input arrays, and  $\beta \geq 1$  denotes the number of memory words required to represent each element.

# 4.2.3 A More Efficient Las Vegas Algorithm

Below we describe a more efficient Las Vegas Algorithm 4.3 that obliviously simulates the functionality  $\mathcal{F}_{\text{SampleAux}}(n, n_0)$  with leakage  $(n, n_0)$ . The algorithm is adapted from the manuscript of Asharov et al. [AKL<sup>+</sup>]; the main difference is that the previous algorithm may abort and fail with a negligible probability, but our algorithm below performs Retry in that abort event. Such negligible event does reveal the input  $(n, n_0)$ . This is exactly the reason why are  $n_0$  and n revealed in our definition of perfect security but not in the definition of statistical/computational security of Asharov et al. [AKL<sup>+</sup>].

Algorithm 4.3: PSampleAuxArray – Sample Auxiliary Array with Low Depth

• Input: Two numbers  $n, n_0 \in \mathbb{N}$  such that  $n_0 \leq n$ .

<sup>&</sup>lt;sup>7</sup>As mentioned, they prove a slightly stronger version where only the total length of the two input arrays is revealed but not each individual array's length.

#### • The Algorithm:

Let  $n_1 = n - n_0$ . In the following, without loss of generality, we assume  $n_0 \leq n_1$  (otherwise, simply swap the roles of 0s and 1s and run a symmetric algorithm). Let  $\lambda$  be the largest integer that such that  $n \geq \log^6 \lambda$ .

- 1. Approximate initialization. If  $n_0 < \log^4 \lambda$ , write down an initial array of size *n* containing all 1s. Else if  $n_0 \ge \log^4 \lambda$ , write down an initial array where each element is set to 0 with probability  $\frac{n_0}{n}$  and set to 1 otherwise. Let X denote the outcome array of this step. Let  $n'_0$  be the number of 0s in X and  $n'_1$  be the number of 1s.

- 2. Number of bits to flip. If  $n'_0 > n_0$ , let  $b^* = 0$  and if  $n'_1 > n_1$ , let  $b^* = 1$ . Let  $F^* = n'_{b^*} n_{b^*}$ . (i.e.,  $F^*$  is the number of 0s or 1s in the array X that are needed to be flipped to reach our target of having exactly  $n_0$  number of 0s.) We can obliviously compute  $b^*$  and  $F^*$  in O(n) total work and  $O(\log n)$  depth by summing up the array in a tree-like manner.

- 3. Subsampling by  $\frac{1}{\log \lambda}$  factor. Make a copy of X and call it Y. For each coordinate  $i \in [n]$  in Y, sample a random indicator bit that is 1 with probability  $\frac{1}{\log \lambda}$  and attach it to the entry.

Run the oblivious tight compaction (Section 3.2.4) on Y to get all the elements that are tagged with a 1 in the front. During this process, each swap gate in the circuit remembers its routing decision such that later we could perform reverse routing to route a fine-tuned version of Y back into X. If the number of elements tagged with a 1 is more than  $\frac{1.5n}{\log \lambda}$ , then Retry from Step 1. Let  $Y' := Y[1..\frac{1.5n}{\log \lambda}]$ .

- 4. Fine-tuning. Obliviously sort the array Y' such that all the  $b^*$  bits appear in the front and flip the first  $F^*$  bits of the outcome array. If there are less than  $F^*$  such  $b^*$  bits, Retry from Step 1. Perform an oblivious random permutation algorithm (Theorem 3.3) on Y', and then overwrite the front Y with Y' by Y[i] := Y'[i] for each  $i \in [\frac{1.5n}{\log \lambda}]$ .

- 5. Reverse-routing. Reverse route the array Y back to the input array, overwriting the corresponding positions in the input. This is performed using the information we recorded in Step 3: each swap gate in the tight compaction circuit remembered its routing decision so we can reverse-route the array Y back to the array X. Output X.

**Theorem 4.4** (PSampleAuxArray). For any parameters  $n_0 \leq n$ , the algorithm PSampleAuxArray $(n, n_0)$  is a perfect oblivious simulation of  $\mathcal{F}_{\text{SampleAux}}(n, n_0)$  with leakage  $(n, n_0)$ . Except with probability  $e^{-\Omega(n^{1/3})}$ , the algorithm completes in O(n) total work and  $O(\log n)$  depth. Furthermore, the above stated performance bounds also apply in expectation.

Proof. We first analyze the performance of PSampleAuxArray, assuming that there is no Retry. With no Retry, the performance of the algorithm is dominated by tight compaction on (bit-)arrays of size O(n), oblivious sort and oblivious random permutation on arrays of size  $\Theta(\frac{n}{\log \lambda}) = \Omega(n^{\frac{5}{6}})$ . By Theorem 3.3, it runs in  $O(n + \frac{n \log n}{\log \lambda})$  total work and  $O(\log n)$  depth, either in expectation or except with probability  $n^{-\Theta(n^{5/12})} \leq e^{-\Omega(n^{1/3})}$ .

To show the performance with Retry, we bound the probability of Retry, which readily adds to the final failure probability for the high probability statement. With the high probability statement, observing the number of times of Retry is a geometric distribution, the expected number of times of Retry is O(1), which gives the desired expected performance. To give an upper bound of the probability of Retry, we consider the following bad events. Let Z be the set of subsamples chosen at Step 3 (i.e., an element  $a \in Y$  is in Z iff a is tagged with 1). Let  $E_1$  be the event  $|Z| \notin [\frac{0.5n}{\log \lambda}, \frac{1.5n}{\log \lambda}]$  (so that  $E_1$  is a superset of the Retry event at Step 3). By Chernoff bound, we have  $\Pr[E_1] = \Pr\left[\left||Z| - \frac{n}{\log \lambda}\right| > \frac{0.5n}{\log \lambda}\right] \leq e^{-\Omega(\frac{n}{\log \lambda})}$ . Then, at Step 4, let  $Z_{b^*}$  be the number of  $b^*$  bits chosen in Z, and let  $E_2$  be the (superset of the) Retry event  $Z_{b^*} < F^*$ . In both cases of  $n_0$  at Step 1, the total probability of Retry is at most  $\Pr[E_1 \cup E_2]$ , and we bound it by considering two cases separately.

If

$$n_0 < \log^4 \lambda$$

, then  $\Pr[E_1 \cup E_2] \le \Pr[E_1] + \Pr[E_2 | \neg E_1]^8$ . As  $F^* \le \log^4 \lambda, Z_{b^*} = |Z|$ , we have

$$\Pr[E_2|\neg E_1] = \Pr[Z_{b^*} < F^*|\neg E_1] \le \Pr\left[\left|Z\right| < \log^4 \lambda \left| |Z| \in \left[\frac{0.5n}{\log \lambda}, \frac{1.5n}{\log \lambda}\right]\right] = 0$$

for all  $n \ge \log^6 \lambda$ , which implies that  $\Pr[E_1 \cup E_2] \le e^{-\Omega(\frac{n}{\log \lambda})} \le e^{-\Omega(n^{1/3})}$ .

Otherwise,  $n_0 \ge \log^4 \lambda$ . To bound  $\Pr[E_2]$ , let  $E_3$  be the event  $F^* > \frac{1}{2}\sqrt{n_{b^*}}\log\lambda$ . Then, we have

$$\Pr[E2] \le \Pr[(E_2 \cap \neg E_3) \cup E_3] \le \Pr[E_2 \cap \neg E_3] + \Pr[E_3].$$

The probability of  $E_3$  is implied by Chernoff bound:  $\Pr[E_3] = \Pr[F^* > \frac{1}{2}\sqrt{n_{b^*}} \cdot \log \lambda] \leq \Pr[|F^* - n_{b^*}| > \frac{1}{2}\sqrt{n_{b^*}} \cdot \log \lambda] \leq e^{-\Omega(\log^2 \lambda)}$ . Also, we have

$$\Pr[E_2 \cap \neg E_3] = \Pr[(Z_{b^*} < F^*) \cap (F^* \le \frac{1}{2}\sqrt{n_{b^*}}\log\lambda)] \le \Pr[Z_{b^*} < \frac{1}{2}\sqrt{n_{b^*}}\log\lambda].$$

Let S be the set of the first  $n_{b^*}$  elements of  $b^*$  (among total  $n'_{b^*}$ ) in X, and  $\bar{Z}_{b^*}$  be the number of elements in S that is also tagged in Y. Then,  $\bar{Z}_{b^*} \leq Z_{b^*}$ , and  $\mathbb{E}[\bar{Z}_{b^*}] = \frac{n_{b^*}}{\log \lambda}$ . Using the assumption  $n \geq \log^6 \lambda$  and  $n_0 \geq \log^4 \lambda$ , we have  $n_{b^*} \geq \log^4 \lambda$  and  $\mathbb{E}[\bar{Z}_{b^*}] > \frac{1}{2}\sqrt{n_{b^*}}\log \lambda$ . Hence,

$$\Pr\left[Z_{b^*} < \frac{1}{2}\sqrt{n_{b^*}}\log\lambda\right] \le \Pr\left[\bar{Z}_{b^*} < \frac{1}{2}\sqrt{n_{b^*}}\log\lambda\right] \le \Pr\left[|\bar{Z}_{b^*} - \mathbb{E}[\bar{Z}_{b^*}]| > \mathbb{E}[\bar{Z}_{b^*}] - \frac{1}{2}\sqrt{n_{b^*}}\log\lambda\right].$$

Using Chernoff bound and each  $b^*$  bit in S is sampled independently into Y, and then by  $\mathbb{E}[\bar{Z}_{b^*}] - \frac{1}{2}\sqrt{n_{b^*}}\log\lambda \geq \frac{1}{2}\mathbb{E}[\bar{Z}_{b^*}]$ , the RHS is at most  $e^{-\Omega(\mathbb{E}[\bar{Z}_{b^*}])} = e^{-\Omega(\log^3 \lambda)}$ . Plugging in  $n \geq \log^6 \lambda$  and by union bound, the total probability of Retry is at most  $e^{-\Omega(\log^2 \lambda)} = e^{-\Omega(n^{1/3})}$  in both cases.

To prove perfect obliviousness, given n and  $n_0 \leq n$ , observe that the distribution of the access pattern depends only on n and  $n_0$ . Hence, it suffices to check every step of PSampleAuxArray.

- 1. Approximate initialization. This step samples a  $\{0, 1\}$ -Bernoulli random variable for every element, and the access pattern is deterministic.

- 2. *Number of bits to flip.* This step performs oblivious addition using a tree-like structure, whose access pattern is fixed and deterministic.

- 3. Subsampling by  $\frac{1}{\log \lambda}$  factor. This step further samples another Bernoulli random variable for each element, and performs tight compaction. So far, the access pattern is still fixed and deterministic.

Then, the element with index  $\frac{1.5n}{\log \lambda}$  is examined to determine whether Retry is needed. Observe the Retry probability depends only on  $n_0$  and n, and the event of Retry is independent of the element contents and whether there are any previous Retry attempts.<sup>9</sup>

<sup>&</sup>lt;sup>8</sup>For all events A, B, if  $\Pr[\neg A] > 0$ , then we have  $\Pr[A \cup B] = \Pr[A \cup (B \cap \neg A)] \leq \Pr[A] + \Pr[B \cap \neg A] = \Pr[A] + \Pr[B|\neg A] \Pr[\neg A] \leq \Pr[A] + \Pr[B|\neg A]$ .

<sup>&</sup>lt;sup>9</sup>This dependence of Retry event on  $n_0$  and n is exactly the reason why are  $n_0$  and n both revealed. Also notice that the Retry probability is only negligible, so it reveals only a negligible amount of information about  $n_0$ , which is acceptable for statistical security, e.g., the manuscript by Asharov et al. [AKL<sup>+</sup>].

4. Fine-tuning. This step uses oblivious sort, which has fixed and deterministic access pattern. Again, the probability of the next Retry event depends only on  $n_0$  and n, and is independent of whether there are previous Retry attempts.

Moreover, a perfectly oblivious random permutation algorithm (Theorem 3.3) on Y' is performed, whose access pattern is guaranteed to be independent of its input contents.

5. *Reverse-routing.* This step carries out oblivious tight compaction in reverse, whose access pattern is fixed and deterministic.

Finally, from the construction, every  $\binom{n}{n_0}$  configuration of choosing  $n_0$  out of n positions to be 0 is equally likely. Moreover, the access pattern is independent of the output configuration. Hence, it follows that **Intersperse** is perfectly oblivious, with the desired performance.

Now due to the work of Asharov et al. [AKL<sup>+</sup>20a], we can combine PSampleAuxArray and oblivious tight compaction (Theorem 3.5) to achieve Intersperse. This gives rise to the following corollary.

**Corollary 4.5** (Parallel Intersperse). Let  $\beta \geq 1$  be the number of words used to represent an element. There is an Intersperse algorithm that is a perfectly oblivious simulation of  $\mathcal{F}_{\text{shuffle}}$  on two randomly shuffled input arrays; moreover, except with  $\exp(-\Omega(n^{1/3}))$  probability, the algorithm completes in  $O(\beta n)$  total work and  $O(\log n)$  depth. Moreover, the stated performance bounds also apply in expectation.

# 5 One-Time Memory

We describe an abstract data structure called an oblivious one-time memory (OTM) which will serve as a core building block in our OPRAM construction. Roughly speaking, a one-time memory (OTM) is initialized with a set of elements using a procedure called Build. Once initialized, it allows each element stored in it to be looked up *at most once* using a procedure called Lookup. Further, it is assumed that when each lookup request arrives, the request is accompanied by a correct "position label" for the element requested. When the OTM is no longer needed, one can call a Getall operation to extract the set of remaining unvisited elements. A similar notion of oblivious OTM was formulated by Chan et al. [CNS18]. Moreover, assuming that each element can be represented with  $\chi \geq 1$  words, Chan et al. [CNS18] show how to construct a perfectly oblivious OTM that consumes  $O(\chi n \log n)$  total work to initialize an OTM data structure containing *n* elements; and where each lookup incurs only  $O(\chi)$  overhead.

In this section, we construct an oblivious OTM assuming that the input array of elements provided to the OTM at initialization has already been randomly shuffled (and the randomness hidden from the adversary). Our goal is to allow each lookup to be supported with  $O(\chi)$  total work as before (as long as a correct position label accompanies each lookup request); however, we would like the initialization procedure to consume only  $O(n \cdot (\chi + \log n))$  total work which is asymptotically better than the OTM of Chan et al. [CNS18] when  $\chi$  dominates  $\log n$ . In other words, in our construction, the initialization procedure is allowed to perform only linear work moving and/or copying the fat elements (i.e., a bundle of  $\chi$  words), but is additionally allowed  $O(n \log n)$  amount of computation on metadata.

# 5.1 Definition

A parallel oblivious one-time memory supports three operations: 1) Build, 2) Lookup, and 3) Getall. Build is called once upfront to create the data structure: it takes in a set of randomly permuted real elements (each tagged with its logical address) and creates a data structure that facilitates lookup. After this data structure is created, a sequence of lookup operations can be performed: each lookup can request a real element identified by its logical address or a dummy address denoted  $\perp$  — if the requested element has a real address, we assume that the correct position label is supplied to indicate where in the data structure the requested element is. Finally, when the data structure is no longer needed, one may call a Getall operation to obtain a list of real elements (tagged with their logical addresses) that have not been looked up yet, mixed with an appropriate number of dummies, and permuted according to a secret random permutation.

We require that our oblivious one-time memory data structure retain obliviousness as long as 1) the sequence of real addresses looked up all exist in the data structure (i.e., it appeared as part of the input to Build), and 2) each real address is looked up at most once.

### 5.1.1 Formal Definition

A (parallel) one-time memory scheme denoted  $OTM^{[n,m,t]}$  is parametrized by three parameters: n denotes the upper bound on the number of real elements; m is the batch size for lookups; t is the number of batch lookups supported.

The scheme  $OTM^{[n,m,t]}$  is comprised of the following possibly randomized, stateful algorithms (Build, Lookup, Getall), to be executed on a *Concurrent-Read, Exclusive-Write* PRAM — note that since the algorithms are stateful, every invocation will update an implicit data structure in memory. Henceforth we use the terminology key and value in the formal description but in our OPRAM scheme later, a real key will be a logical memory address and its value refers to its content.

•  $U \leftarrow \text{Build}(S)$ : The algorithm takes as input an array S of n elements, where each element is either a *real* key-value pair of the form  $(k_i, v_i)$ , or *dummy* denoted  $(\bot, \bot)$ ; moreover any two real elements in S must have distinct keys. The algorithm then creates an in-memory data structure to facilitate subsequent lookup requests (not included in the output); moreover it outputs a position-label array U containing exactly n key-position pairs each of the form (k, pos). Further, every real key in the input S will appear exactly once in the list U; and the list U is padded with  $\bot$  to a length n.

Recall that each value  $v_i$  in the input S can be "fatter" than its position label **pos** that is included in the output U. Later in our OPRAM scheme (Section 6), this key-position list U will be propagated back to the parent recursion depth during a coordinated rebuild<sup>10</sup>.