# Racing BIKE: Improved Polynomial Multiplication and Inversion in Hardware

Jan Richter-Brockmann<sup>1,2</sup>, Ming-Shing Chen<sup>1</sup>, Santosh Ghosh<sup>2</sup> and Tim Güneysu<sup>1,3</sup>

Ruhr-Universität Bochum, Horst-Görtz Institute for IT-Security, Bochum, Germany

Security and Privacy Research, Intel Labs, Intel Coorperation, Hillsboro, Oregon

DFKI, Bremen, Germany

**Abstract.** BIKE is a Key Encapsulation Mechanism selected as an alternate candidate in NIST's PQC standardization process, in which performance plays a significant role in the third round. This paper presents FPGA implementations of BIKE with the best area-time performance reported in literature. We optimize two key arithmetic operations, which are the sparse polynomial multiplication and the polynomial inversion. Our sparse multiplier achieves time-constancy for sparse polynomials of indefinite Hamming weight used in BIKE's encapsulation. The polynomial inversion is based on the extended Euclidean algorithm, which is unprecedented in current BIKE implementations. Our optimized design results in a 5.5 times faster key generation compared to previous implementations based on Fermat's little theorem.

Besides the arithmetic optimizations, we present a united hardware design of BIKE with shared resources and shared sub-modules among KEM functionalities. On Xilinx Artix-7 FPGAs, our light-weight implementation consumes only 3777 slices and performs a key generation, encapsulation, and decapsulation in 3797  $\mu$ s, 443  $\mu$ s, and 6896  $\mu$ s, respectively. Our high-speed design requires 7332 slices and performs the three KEM operations in 1672  $\mu$ s, 132  $\mu$ s, and 1892  $\mu$ s, respectively.

**Keywords:** BIKE  $\cdot$  QC-MDPC  $\cdot$  PQC  $\cdot$  Reconfigurable Devices  $\cdot$  FPGA.

#### 1 Introduction

Due to extensive research and advanced progress in quantum computation during the last decades [Gam20], in 2017, the National Institute of Standards and Technology (NIST) announced a Post-Quantum Cryptography (PQC) standardization process with the target to find public-key cryptographic algorithms that provide security in the presence of quantum computers [NIS17].

After the call for proposals, the NIST received 69 submissions which were revised with respect to security, efficiency (e.g., key sizes and latency), and implementation costs for software and hardware. Eventually, after the third round, they selected seven finalists and eight alternate candidates [NIS20b]. While the finalists are all considered for standardization, the alternate candidates will be reviewed and may be evaluated in a fourth round such that they potentially could be standardized as well [NIS20b].

The Bit Flipping Key Encapsulation (BIKE) [ABB<sup>+</sup>20] is one of the NIST's alternate candidates in the Key Encapsulation Mechanism (KEM) category. The security of BIKE relies on the hardness of decoding linear error-correcting codes. More specifically, as underlying linear codes, BIKE utilizes Quasi-Cyclic Moderate-Density Parity-Check (QC-MDPC) codes, which were first presented by Misoczki et *al.* [MTSB13] in 2013.

In this work, we target to improve the efficiency of the KEM functionalities of BIKE by an Field-Programmable Gate Array (FPGA) hardware design. Since NIST announced that performance plays an important role in their PQC standardization efforts [NIS20a], researchers presented several optimization techniques for BIKE on the suggested platforms including the AVX2 instruction set on x86, embedded microprocessors, and FPGAs. For example, Drucker et al. [DGK20a] optimized BIKE for x86 Central Processing Units (CPUs). Chen et al. [CCK21] presented optimization techniques for x86 and Arm Cortex M4. Richter-Brockmann et al. [RBMG21] proposed an optimized scalable hardware implementation for reconfigurable devices. In this paper, we propose new optimization techniques for efficient FPGA implementations of BIKE and report significant improvements compared to previous works.

Related Works on FPGAs. Although there were several early works implementing QC-MDPC codes on hardware devices for variants of the McEliece cryptosystem [VMG14, HVMG13] and for the Niederreiter framework [HC17], the first hardware implementation of BIKE was presented with the round-two submission of NIST's PQC standardization process [ABB<sup>+</sup>19]. The implementation was designed for an older version of BIKE (called BIKE-1) and only supported the key generation and encapsulation.

In 2020, Reinders et al. [RMGS20] proposed a complete hardware design which, however, targets the older parameters of BIKE. Besides, they presented an efficient hardware implementation for a novel constant-time decoder.

Recently, Richter-Brockmann et al. [RBMG21] presented the first complete hardware design of the current BIKE version [ABB<sup>+</sup>20]. They implemented for the first time the Black-Gray-Flip (BGF) decoder on hardware, introduced an optimized polynomial inversion module (based on Fermat's little theorem), and proposed a scalable multiplier.

In further detail, BIKE poses several challenges on the arithmetic level. For improving the polynomial multipliers in code-based schemes, Hu et al. [HWCW19] presented two different approaches. While the first design is based on a schoolbook multiplication, the second multiplier improves multiplications by exploiting the sparseness of the polynomials used in QC-MDPC codes. Additionally, they instantiated their designs to create a key generation module based on previous parameter sets of BIKE.

Barenghi et al. [BFG<sup>+</sup>19] presented similar approaches to implement polynomial multiplications for the code-based scheme LEDAcrypt [BBC<sup>+</sup>19]. They explored different configurations of schoolbook and sparse multipliers for Xilinx FPGAs.

Contribution. In this work, we revise previous concepts and identify significant improvements and systematic explorations of the hardware implementation of BIKE on FPGAs. Specifically, we introduce an optimized polynomial multiplier that exploits the sparseness of QC-MDPC codes while performing all multiplications applied in BIKE in constant time. In addition to that, we present a novel component for polynomial inversion based on the extended Euclidean algorithm (extGCD) accelerating the key generation in hardware. For that we adapt the extGCD from the constant-time algorithm recently proposed by Bernstein and Yang [BY19], and demonstrate that this approach clearly outperforms previous implementations based on Fermat's little theorem in the specific case of BIKE. As a design constraint, our implementation is highly scalable to instantiate specifically tailored cryptographic components for any use-case.

Besides these major arithmetic-oriented optimizations, we also substitute symmetric cryptography from encapsulation and decapsulation implementations presented in [RBMG21] with a single Keccak core to demonstrate the authors' assertion of achieving a lower footprint by applying this modification. Additionally, we present a combined hardware implementation of BIKE that consolidates all three KEM algorithms in one single, united design. This approach enables resource and module sharing between the

KEM algorithms achieving a design that reduces the overall implementation costs.

Our implementations are written in Verilog and are publicly available at <a href="https://github.com/Chair-for-Security-Engineering/RacingBIKE">https://github.com/Chair-for-Security-Engineering/RacingBIKE</a>.

**Outline.** In Section 2, we briefly introduce BIKE and cover the background of polynomial arithmetic that is necessary for our hardware implementations. Section 3 starts with an introduction of our design considerations. Afterwards, we introduce our modifications with respect to the random oracles, present our multiplier and inversion modules, and describe the composition of an united hardware design. In Section 4, we evaluate all designs with respect to implementation costs and performance. Before we conclude our work in Section 6, we briefly discuss the resistance against side channels and address the transferability of our approaches to software implementations in Section 5.

#### 2 Preliminaries

In this section, we describe the algorithms and parameters forming BIKE. Then, we summarize important polynomial arithmetic.

#### 2.1 Notations

Throughout this work, we use the following notations:

- $\mathbb{F}_2$ : Finite field of two elements  $\{0,1\}$ .

- F<sub>2</sub>[X]: Polynomials with coefficients in F<sub>2</sub>, or bit polynomials.

In this work, we store a polynomial a = a<sub>0</sub> + a<sub>1</sub>X + ··· ∈ F<sub>2</sub>[X] as a bit sequence of coefficients (a<sub>0</sub>, a<sub>1</sub>, ...). The 0-th bit corresponds to the coefficient a<sub>0</sub>; the first bit corresponds to the coefficient a<sub>1</sub>; and so on.

- $\bullet$  r: The parameter defining the length of polynomials in BIKE.

- $\mathcal{R} := \mathbb{F}_2[X]/(X^r 1)$ : The cyclic polynomial ring used in BIKE. Multiplication in  $\mathcal{R}$  is generally implemented as multiplication of bit polynomials in  $\mathbb{F}_2[X]$  and followed by a modulo operation by  $X^r - 1$  for terms of degrees  $\geq r$ .

- |f|: Hamming weight of a bit polynomial f.

- b: Bandwidth (in bits) for accessing data from memory in our FPGA implementation.

- f[i] is the *i*-th *b*-bit chunk of a polynomial f for  $0 \le i < \lceil \frac{r}{b} \rceil$ .

#### **2.2 BIKE**

We divide this section in three paragraphs describing the KEM functions of BIKE, introducing required hash functions, and summarizing BIKE's parameters.

**KEM Functions.** The BIKE KEM comprises three algorithms — key generation, encapsulation, and decapsulation. The key generation (see Algorithm 1) outputs a key pair. It randomly samples two sparse polynomials  $(h_0, h_1) \in \mathbb{R}^2$  and a random string  $\sigma$  as the private key. By inverting  $h_0$  and multiply the result by  $h_1$ , the key generation computes the public key h as shown in line 3.

Algorithm 2 describes the encapsulation which starts by sampling a message m and deriving two error polynomials  $(e_0, e_1)$  from  $\mathbf{H}(m)$ . Afterwards, it computes the first part of the cryptogram  $e_0$  by multiplying  $e_1$  by the public key h and adding (xor) the result to

#### **Algorithm 1:** Key Generation.

```

Input: BIKE parameters n, w, t, \ell.

```

**Output:** Private key  $(h_0, h_1, \sigma)$  and public key h.

- 1 Generate  $(h_0, h_1) \stackrel{\$}{\leftarrow} \mathbb{R}^2$  both of odd weight  $|h_0| = |h_1| = w/2$ .

- **2** Generate  $\sigma \stackrel{\$}{\leftarrow} \{0,1\}^{\ell}$  uniformly at random.

- **3** Compute  $h \leftarrow h_1 h_0^{-1}$ .

- 4 Return  $(h_0, h_1, \sigma)$  and h.

#### **Algorithm 2:** Encapsulation.

```

Input: Public key h.

```

**Output:** Encapsulated key K and ciphertext  $C = (c_0, c_1)$ .

- 1 Generate  $m \stackrel{\$}{\leftarrow} \{0,1\}^{\ell}$  uniformly at random.

- **2** Compute  $(e_0, e_1) \leftarrow \mathbf{H}(m)$ .

- **3** Compute  $C = (c_0, c_1) \leftarrow (e_0 + e_1 h, m \oplus \mathbf{L}(e_0, e_1)).$

- 4 Compute  $K \leftarrow \mathbf{K}(m, C)$ .

- **5** Return (C, K).

#### Algorithm 3: Decapsulation.

```

Input: Private key (h_0, h_1, \sigma) and ciphertext C = (c_0, c_1).

```

Output: Decapsulated key K.

- 1 Compute syndrome  $s \leftarrow c_0 h_0$ .

- 2 Compute  $\{(e_0', e_1'), \bot\} \leftarrow \mathsf{decoder}(s, h_0, h_1).$

- **3** Compute  $m' \leftarrow c_1 \oplus \mathbf{L}(e'_0, e'_1)$ .

- 4 if  $\mathbf{H}(m') \neq (e'_0, e'_1)$  then

- 5 Compute  $K \leftarrow \mathbf{K}(\sigma, C)$ .

- 6 else

- 7 Compute  $K \leftarrow \mathbf{K}(m', C)$ .

- 8 Return K.

$e_0$ . This step represents the encoding procedure of linear codes but with the difference that the errors are added intentionally. The second part of the cryptogram  $c_1$  is generated by adding the message m to the output of the hash function  $\mathbf{L}$ . Eventually, the algorithm derives the shared key K by hashing the cryptogram and the message with  $\mathbf{K}$ .

Algorithm 3 shows the decapsulation that recovers the error polynomials  $(e_0, e_1)$  from the cryptogram C. It first computes the syndrome s in line 1 as a common procedure for decoding linear codes. The syndrome and the private key  $(h_0, h_1)$  are then fed into a decoder to determine the error polynomials  $(e'_0, e'_1)$ . The BIKE specification [ABB<sup>+</sup>21] applies a BGF decoder which was extensively investigated in [DGK20b]. If the decoding is successful, the algorithm calculates the message m' from the ciphertext C and the error polynomials (cf. line 3). To ensure that m' and the determined error polynomials match the one generated in the encapsulation, it applies the same sampling algorithm  $\mathbf{H}$  to m' and compares the result to the error polynomials returned from the decoder. In case the pair is valid, it computes the shared key  $K = \mathbf{K}(m', C)$ . Otherwise it computes K using the secret string  $\sigma$  belonging to the private key.

**Hash Functions.** In BIKE, the encapsulation and decapsulation utilize the three functions  $\mathbf{H}$ ,  $\mathbf{K}$ , and  $\mathbf{L}$  which are modeled as random oracles and defined over the following domains:

| Security | r     | $\overline{w}$ | t   |

|----------|-------|----------------|-----|

| Level 1  | 12323 | 142            | 134 |

| Level 3  | 24659 | 206            | 199 |

| Level 5  | 40973 | 274            | 264 |

$$\mathbf{H}: \{0,1\}^{\ell} \to \{0,1\}_{[t]}^{2r} \qquad \mathbf{K}: \{0,1\}^{r+2\ell} \to \{0,1\}^{\ell} \qquad \mathbf{L}: \{0,1\}^{2r} \to \{0,1\}^{\ell}$$

The latest specification [ABB<sup>+</sup>21] unifies the three random oracles to hash functions based on Keccak [BDPA13]. **H** maps an  $\ell$ -bit string into a 2r-bit string with Hamming weight t. It is implemented by a SHAKE256-based Pseudo-Random Number Generator (PRNG) while it was realized by AES-256 in previous versions. **K** and **L** uses a SHA3-384 implementation replacing the SHA2-384 of previous versions.

**Parameters.** Table 1 summarizes the parameters of BIKE for various security levels of NIST's PQC standardization process. As already introduced above, the parameter r represents the length of polynomials used in BIKE. The parameter w specifies the Hamming weight of the private key polynomials  $(h_0, h_1)$ , satisfying  $|h_0| = |h_1| = w/2$ . The parameter t defines the decoding radius, i.e., the Hamming weight of the errors randomly sampled in the encapsulations. Eventually,  $\ell$  specifies the length of the shared key of the KEM, which is fixed to 256 bits for all security levels.

### 2.3 Polynomial Multiplication by Sparse Polynomials

In BIKE, all multiplications in  $\mathcal{R}$  comprise a sparse operand  $f \in \mathcal{R}$  with  $|f| \ll r$ . For the key generation,  $h_1$  is the sparse polynomial in the multiplication  $h_1 \cdot h_0^{-1}$ . For the encapsulation,  $e_1$  is sparse in  $e_1 \cdot h$ . For the decapsulation,  $h_0$  is sparse in  $e_0 \cdot h_0$ . The decoder contains some additional multiplications by the sparse polynomials  $(h_0, h_1)$  which are part of the private key.

We represent a sparse polynomial as a set of indexes corresponding to its non-zero terms. For example, the set  $I_f = \{i_1, \ldots, i_t\}$  represents the sparse polynomial  $f = X^{i_1} + \cdots + X^{i_t}$  with the Hamming weight |f| = t. Multiplying a dense polynomial g by the sparse polynomial f simply accumulates f products of multiplications f for f for f for f since f is represented as a bit sequence, multiplication by f shifts the bit sequence f-bit to the left and modulo by f noves the shifted bit segment exceeding the f-th bit to the empty bit segment starting from the 0-th bit. In other words, the multiplication simply accumulates f rotated f by f by f bits.

#### 2.4 Polynomial Inversion with the Extended Euclidean Algorithm

The key generation (cf. Algorithm 1) computes the multiplicative inverse of a secret polynomial  $h_0 \in \mathcal{R}$ . Previous works, e.g., [ABB<sup>+</sup>20, HWCW19, RBMG21], computed the inversion by raising  $h_0$  to the power of  $2^r - 2$  (Fermat's little theorem).

In this work, we compute the inversion with the extended Euclidean algorithm (extGCD). The extGCD takes two input polynomials (f,g) and outputs three polynomials  $(\gcd(f,g),u,v)$ , where  $\gcd(f,g)$  is the great common divisor of f and g and  $\gcd(f,g)=u\cdot f-v\cdot g$ . All polynomials are in  $\mathbb{F}_2[X]$  in the context of BIKE.

In a nutshell, we compute  $\operatorname{extGCD}(X^r-1,h_0)$  for the inverse  $h_0^{-1}$ . Under the parameters of BIKE, the polynomial  $X^r-1$  has two factors  $X^r-1=(X-1)(\sum_{i=0}^{r-1}X^i)$ . Since  $|h_0|=w/2$  is an odd number,  $h_0$  is not a multiple of X-1. Since  $|h_0|\neq r$ ,  $h_0$  is also

not the polynomial  $\sum_{i=0}^{r-1} X^i$ . Hence, the extGCD $(X^r-1,h_0)$  outputs (1,u,v) s.t.  $1 = u \cdot (X^r-1) - v \cdot h_0$ , and v is the inverse  $h_0^{-1}$  since  $v \cdot h_0 \equiv 1 \mod (X^r-1)$ .

However, a traditional extGCD is unsuitable for cryptographic applications because it usually contains branches that depend on the inputs. While the inputs are secret, an attacker can collect the information about the inputs through running-time differences. Hence, we have to apply a constant-time extGCD to prevent the leakage of timing side-channel information.

In this work, we adopt the constant-time version of the extGCD proposed by Bernstein and Yang [BY19]. In contrast to the traditional extGCD that eliminates the head coefficients of polynomials at any degree, the constant-time extGCD in [BY19] always eliminates the 0-th bit of polynomials. This leads to extra coefficient reversal processes for inputs to move its head coefficient to the 0-th bit position and before output for recovering the polynomial to its original coefficient order. Considering for example an input polynomial f, the coefficient process is equivalently to perform the  $f' \leftarrow f(1/X) \cdot X^{\deg(f)}$  operation. This operation moves the original head coefficients of f to a new position of degree 0, which is accessed by f'[0]. Thus the extGCD always eliminates the head coefficients at the 0-th bit.

Division Steps and Transition Matrix. In this work, we simplify the extGCD in [BY19] regarding  $\mathbb{F}_2[X]$  for the BIKE application. The algorithm consists of a constant number of simple division steps (divsteps) for the two input polynomials. Define divstep:  $\mathbb{Z} \times \mathbb{F}_2[X] \times \mathbb{F}_2[X] \to \mathbb{Z} \times \mathbb{F}_2[X] \times \mathbb{F}_2[X]$  as

$$\mathtt{divstep}(\delta,f,g) = \begin{cases} (1-\delta,g,(g(0)f-f(0)g)/X) & \text{if } \delta>0 \text{ and } g(0)\neq 0,\\ (1+\delta,f,(f(0)g-g(0)f)/X) & \text{otherwise.} \end{cases}$$

Here,  $\delta$  means the degree difference between f and g. The divstep outputs two polynomials. The first polynomial aims for the polynomial of the higher degree among two input polynomials. The other is the result of subtraction of two polynomials for eliminating one head term, and it adjusts the new head term to the degree-0 coefficient by the division of X.

Since the division of X causes negative degrees, we adjust the representation of polynomials to prevent negative degrees. If the polynomial f contains a monomial of negative degree, e.g.,  $1/X^i$ , we will store f as an alternative polynomial f' s.t.  $f = f' \cdot (1/X)^i$  and degrees of all monomials of f' are non-negative. For applying divstep multiple times, define  $(\delta_n, f_n, g_n) = \text{divstep}^n(\delta, f, g)$ , i.e., applying the divstep to inputs  $(\delta, f, g)$  for n times.

Bernstein and Yang describe the transition of the two polynomials (f,g) under the divstep operation as a matrix-vector multiplication. Let  $T(\delta, f, g)$  be a  $2 \times 2$  transition matrix which performs the transition  $(f,g) \to (f_1,g_1)$  as matrix multiplication:

$$\begin{pmatrix} f_1 \\ g_1 \end{pmatrix} = T(\delta, f, g) \begin{pmatrix} f \\ g \end{pmatrix}, \text{ where } T(\delta, f, g) = \begin{cases} \begin{pmatrix} 0 & 1 \\ \frac{g(0)}{X} & \frac{-f(0)}{X} \end{pmatrix} & \text{if } \delta > 0 \text{ and } g(0) \neq 0, \\ \begin{pmatrix} 1 & 0 \\ \frac{-g(0)}{X} & \frac{f(0)}{X} \end{pmatrix} & \text{otherwise.} \end{cases}$$

Define the transition matrix of *i*-th step as  $T_i = T(\delta_i, f_i, g_i)$ . After *n* steps, the input polynomials (f, g) become

$$\begin{pmatrix} f_n \\ g_n \end{pmatrix} = T_{n-1} \cdots T_0 \cdot \begin{pmatrix} f \\ g \end{pmatrix} = \begin{pmatrix} u_n & v_n \\ q_n & w_n \end{pmatrix} \begin{pmatrix} f \\ g \end{pmatrix}.$$

<sup>&</sup>lt;sup>1</sup>See [BY19, Section 6.5] for an alternative method skipping the reversal. It requests a post-process for polynomials before output.

Note that we use w instead of the original r in [BY19] to avoid the symbol conflict.

Since we aim for the polynomial inversion in BIKE, we keep only two vectors (f,g) and (v,w) in our storage space for storing all  $(f_i,g_i)$  and  $(v_i,w_i)$  for i in  $0,\ldots n$ , instead of tracking full transition matrices. The polynomials (f,g) and (v,w) are stored in different formats. Since  $(v_i,w_i)^T$  is part of the transition matrix, they are polynomials with monomials of negative degrees. Hence, we store the vector  $(v_i,w_i)$  in a form of  $(v_i',w_i')\cdot (1/X)^i$  and i increases with steps to keep the polynomials  $(v_i',w_i')$  with nonnegative degrees. Since  $(f_i,g_i)^T$  and  $(v_i,w_i)^T$  are multiplied by the same transition matrix, we update the two vectors with similar operations except the degree adjustment. We remove the coefficient of the constant term of g for the division by X but increase the coefficients of v by one degree to keep the correct form of  $(v_i',w_i')\cdot (1/X)^i$ .

Last, we describe the overall algorithm for the polynomial inversion in BIKE. We initialize the two input polynomials  $f = X^r - 1$ ,  $g = h_0(1/X) \cdot X^r$ , and their degree difference  $\delta = 1$ . Note that g is initialized as a bit-reversal form. The (v, w) polynomials are initialized to (0,1) as the right column of an identity matrix. Then we perform 2r - 1 divsteps to update  $(\delta, f, g)$  and (v, w) as well. After divsteps, we reverse the coefficients of the polynomial v and output it as the inverse  $h_0^{-1}$ .

## 3 Optimization Strategies

In this section, we propose several optimization strategies to improve the hardware implementation of BIKE. We start by describing the exchange of the symmetric cryptographic building blocks, i.e., AES-256 and SHA2-384 with a single Keccak core. Then, we introduce a new design of a multiplier exploiting the sparseness of QC-MDPC polynomials. Afterwards, we present an improved inversion module based on the algorithm proposed by Bernstein and Yang [BY19]. We conclude this section with an united hardware design which consolidates all three KEM algorithms of BIKE in one implementation.

#### 3.1 Design Considerations

We start with our design considerations. First, our implementations utilize the framework presented in [RBMG21] while we modify and optimize several hardware modules described in the following sections. Besides these modifications, the main structure is based on the original implementation. However, we translate all modules to Verilog.

Second, we keep the same bandwidth parameter b in our modified modules as proposed in the original implementations from [RBMG21]. Hence, our design is scalable with b as well, and we benchmark our designs with the same instantiations of  $b \in \mathcal{B} = \{32, 64, 128\}$ . Larger b generally improve the latency of the corresponding computation since b-bit chunks of polynomials can be accessed and processed in parallel.

#### 3.2 Random Oracles

The BIKE team recently updated the random oracles **H**, **K**, and **L** in their latest specification of version 4.2 [ABB<sup>+</sup>21]. They adapted the core components of these functions from AES256 and SHA2-384 to SHAKE256 and SHA3-384 with an unified Keccak core, respectively. While Richter-Brockmann et *al.* suggested the unified symmetric core would be beneficial for a hardware implementation, they, however, did not test their suggestions in [RBMG21].

In this work, we modify the implementations presented in [RBMG21] to the latest specification of hash functions and report the comparisons in Section 4.1. Therefore, we implement a simple Keccak core which only contains the round function and a controlling

interface. In the following, we describe the implementations of wrappers that are connected to the Keccak core and form the random oracles.

First, for the **H** function, we instantiate a SHAKE256 from the KECCAK's round function. As in Algorithm 2, **H** uses a 256-bit message m as seed for SHAKE256 which is requested by an dedicated interface in our implementation. Then, with correct padding and controlling of the KECCAK core, the wrapper divides the 1088 output bits into 32-bit chunks. The integrated sampler uses the chunks to generate the indexes of error polynomials  $(e_0, e_1)$  and rejects illegal samplings. If the sampler has consumed all randomness, the wrapper initiates an additional squeezing phase of SHAKE256.

Second, for generating the private key  $(h_0, h_1)$  in the key generation (cf. Algorithm 1), our wrapper operates similarly to the **H** function besides different Hamming weights.

Third, for the **L** function, the wrapper uses the error polynomials  $(e_0, e_1)$  and provides them in the absorbing phases to the Keccak core. In this case, it performs a SHA3-384 hashing operations. Besides the correct padding, the wrapper ensures to concatenate the error polynomials by eight-bit blocks. Last, it truncates the 384-bit hash value to a 256-bit value and adds it to m.

Fourth, our wrapper for the **K** function is realized similarly to the **L** function. However, the input to the SHA3-384 slightly differs since a 256-bit string needs to be concatenated with an r-bit polynomial and with another 256-bit string. Nevertheless, it truncates the 384-bit output to 256 bits in the same way.

#### 3.3 Sparse Polynomial Multiplier

In this section, we present the hardware design of the sparse polynomial multiplier for BIKE. In 2019, Hu et al. [HWCW19] already applied the approach of sparse multiplications to BIKE. However, compared to their design, our optimized implementation achieves a better area-time product and reduces the latency (for detailed information see Section 4.2). Additionally, our design keeps the time-constancy for the encapsulation while computing  $e_0 + e_1 \cdot h$  with the indefinite Hamming weight of  $e_1$ .

As in Section 2.3, given a multiplication  $p_{\rm res} = p_{\rm sparse} \cdot p_{\rm arb.}$  where  $p_{\rm sparse}, p_{\rm arb.} \in \mathcal{R}$  and  $|p_{\rm sparse}| \ll r$ . Further, the polynomial  $p_{\rm sparse}$  is represented as a set of indexes of non-zero terms and  $p_{\rm arb.}$  is a r-bit sequence divided into  $\lceil \frac{r}{b} \rceil$  chunks. Then, we conduct the multiplication by reading the non-zero indexes of  $p_{\rm sparse}$ , rotating  $p_{\rm arb.}$  by the indexes to the left, and accumulating the rotated results to the product  $p_{\rm res.}$

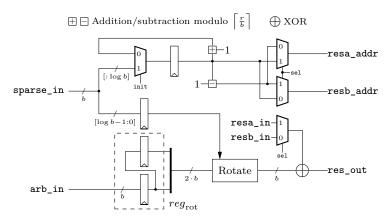

**General Sparse Multiplier.** Figure 1 shows a simplified architecture of the general sparse multiplier which iterates over the indexes of the sparse polynomial  $p_{\rm sparse}$ . Each iteration is initiated by reading a non-zero index from  $p_{\rm sparse}$ . Meanwhile, it starts to access the values of the polynomial  $p_{\rm arb}$  in an ascending order starting at the second uppermost address, proceeding with the uppermost, and then keep going from address zero. This procedure simplifies to deal with the most-significant bits in  $p_{\rm arb}$  since  $r \mod b \neq 0$  (r is always prime). Figure 1 neglects the hardware to deal with this exception (mostly multiplexers) for clarity.

While processing a particular index from  $p_{\rm sparse}$ , the lower  $\log b$  bits of the index determine the number of bits to shift the input from  $p_{\rm arb}$  to the left. The shifted output is added to the current intermediate result depicted by the xor-gates in Figure 1. We instantiate two memories to store the intermediate results of the multiplication. This allows us to read the current intermediate result from one memory and write the new result to the other one in the same clock cycle.

The upper part of the schematic in Figure 1 determines the addresses for both memories. When an index of the sparse polynomial is read, the upper bits are sampled in a register used as initial value for a counter. To handle the jump from the highest address (i.e.,  $\lfloor \frac{r}{b} \rfloor$ ) to zero, our final design contains slightly more logic. Again, Figure 1 neglects this logic

Figure 1: Schematic architecture of the general sparse multiplier.

for the sake of clarity. However, the output of the counter is subtracted by one, and two multiplexers decide which of the address values are used to access which of the memories. The decision signal sel is determined based on the LSB from the address counter used to read out the indexes of the sparse polynomial.

For each index of the sparse polynomial, our multiplier spends  $\lceil \frac{r}{b} \rceil + 4$  clock cycles for shifting and accumulating the intermediate results. The total latency is given by

$$L_{\text{mult}}(th) = \left( \left\lceil \frac{r}{b} \right\rceil + 4 \right) \cdot th + 1 \tag{1}$$

where th denotes the weight of the sparse polynomial (e.g., for the key generation in BIKE  $th = \frac{w}{2}$ ). The circuit switches to the DONE state in the additional clock cycle.

This design iterates over a fixed number of indexes of the sparse polynomial. While this approach is capable of processing the secret polynomials  $(h_0, h_1)$ , it cannot process the multiplication  $e_1 \cdot h$  in the encapsulation with a constant latency since the Hamming weight of  $e_1$  is unknown. Therefore, we modify the design of the general sparse multiplier into a dedicated multiplier for BIKE in the next paragraph.

**Tailored Constant-time Multiplier for BIKE.** To deal with the indefinite weight of  $e_1$  in the encapsulation, we utilize the relation  $|e_0| + |e_1| = t$  defined by BIKE. It allows to rephrase the encoding operation as an addition of two multiplications

$$c_0 = e_0 \cdot 1 + e_1 \cdot h. \tag{2}$$

For computing  $c_0$ , we modify the general sparse multiplier introduced above and add a multiplexer choosing h or 1 as input for  $p_{arb}$  depending on  $e_0$  or  $e_1$ . To indicate whether  $e_0$  or  $e_1$  is processed, we add an additional leading bit to the indexes and set the MSB of the indexes belonging to  $e_0$  to '1'. We embed this operation directly into the sampling function  $\mathbf{H}$ . Hence, the multiplexer selects its output according to the MSB of the indexes of the sparse polynomial.

In order to illustrate the two modes of the multiplication engine, we provide a small example for r=11, b=4, and  $p_{\rm arb.}=X^{10}+X^8+X^7+X^6+X^5+X^4+X^3+1=101$  1111 1001 (corresponds to h in Equation 2). For the error polynomials, we exemplary assume  $e_0=X^5$  and  $e_1=X^7$  and their corresponding indexes  $e_{0,\rm idx}=1$  0101 and  $e_{1,\rm idx}=0$  0111, respectively. For both modes, we assume that the current intermediate result is  $p_{\rm int}=0$ 10 1001 0110.

Figure 2 visualizes the multiplication  $e_1 \cdot p_{\rm arb.}$  where each dashed line separates the data flow between the clock cycles. In this case, the expected result is

$X^7 \cdot 101 \ 1111 \ 1001 \oplus 010 \ 1001 \ 0110 = 100 \ 1101 \ 1111 \oplus 010 \ 1001 \ 0110 = 110 \ 0100 \ 1001.$

|                           |              | I            | I         | I         | I         | I                          |

|---------------------------|--------------|--------------|-----------|-----------|-----------|----------------------------|

| $p_{\mathrm{arb.}}$ in:   | 1111         | 0101         | 1001      | 1111      | 0101      | <br>                       |

| $reg_{\mathrm{rot}}$ in:  | 0001 0000    | 1011 0000    | 1001 1011 | 1111 1001 | 0101 1111 | 1<br>1                     |

| $reg_{\mathrm{rot}}$ out: | 0000 0000    | 0001 0000    | 1011 0000 | 1001 1011 | 1111 1001 | 0101 1111                  |

| shifted:                  | 0000 0000    | 1000 0000    | 1000 0000 | 1101 1000 | 1100 1000 | 1111 1000                  |

| $p_{ m int}$ in:          |              | l            | <br>      | 1001      | 0010      | 0110                       |

| result out:               |              | <br>         | <br>      | 0100      | 0110      | 1001                       |

|                           |              |              |           | <u> </u>  | ↑         | †                          |

| index of the              | sparse polyn | omial: 0 011 | .1        | write to  | write to  | write to                   |

|                           |              |              |           | addr 0x01 | addr 0x02 | $\operatorname{addr} 0x00$ |

Figure 2: Example for a multiplication with an index from  $e_1$ .

| $p_{ m one}$ in:          | 0000         | 0000          | 0001      | 0000      | 0000      | <br>      |

|---------------------------|--------------|---------------|-----------|-----------|-----------|-----------|

| $reg_{ m rot}$ in:        | 0000 0000    | 0000 0000     | 0001 0000 | 0000 0001 | 0000 0000 | 1         |

| $reg_{\mathrm{rot}}$ out: | 0000 0000    | 0000 0000     | 0000 0000 | 0001 0000 | 0000 0001 | 0000 0000 |

| shifted:                  | 0000 0000    | 0000 0000     | 0000 0000 | 0010 0000 | 0000 0010 | 0000 0000 |

| $p_{ m int}$ in:          |              |               | <br>      | 1001      | 0010      | 0110      |

| result out:               |              |               | <br>      | 1011      | 0010      | 0110      |

| index of the              | sparse polyn | iomial: 1 010 | )1        | write to  | write to  | write to  |

|                           | - * *        |               |           | addr 0x01 | addr 0x02 | addr 0x00 |

Figure 3: Example for a multiplication with an index from  $e_0$ .

As described above, the module first reads the second uppermost chunk from the input polynomial which is 1111 in our example. Since r=11 and b=4, only the most significant bit from this chunk is required and stored in the register  $reg_{\rm rot}$  (cf. Figure 1). The remaining three bits are taken from the uppermost chunk. Afterwards, the process proceeds in a regular pattern by reading a new chunk and moving the old chunk to the lower part of  $reg_{\rm rot}$ . The multiplier determines the starting address to read the first chunk from the intermediate result by the upper bits of the error index, i.e., 0x01 in our example. This describes the required shift on word level. The output of the register is shifted to the left by 3 bit which are the least  $\log(b)$  bits from index  $e_{1,\rm idx}$  and describe the required shift on bit level. Hence, the first chunk of the new intermediate result is written to address 0x01. Note, when the multiplier writes the result to address 0x02, the most significant bit is set to 0 since it does not belong to a valid polynomial of size r=11.

The procedure for a multiplication with the index  $e_{0,\mathrm{idx}}$  is similar. Instead of providing the polynomial  $p_{\mathrm{arb.}}$  to the multiplier, the polynomial  $p_{\mathrm{one}} = 1 = 000~0000~0001$  is selected by the most signification bit of  $e_{0,\mathrm{idx}}$ . The corresponding data flow is visualized in Figure 3. It is clearly visible that the multiplication with an index from  $e_0$  requires the same amount of clock cycles such that a constant-time operation is guaranteed.

To this end, Figure 4 shows the adjustment for processing the operand  $p_{\rm arb.}$  in the multiplier. Note, the polynomial of one does not require an extra memory but is generated on the fly. While accessing the 0-th chunk of  $p_{\rm arb.}$ , the circuit feeds a b-bit chunk of 0...01 to the multiplexer. Otherwise, the multiplexer always gets a zero b-bit chunk. Hence, the multiplier always finishes the multiplication from Equation 2 in  $L_{\rm mult}(t)$  clock cycles.

Figure 4: Modifications to the input operand of the tailored multiplier.

Last, we add an additional input to the multiplier design determining the number of non-zero indexes of the sparse polynomial for the two possible weights (t, w/2) of the sparse input polynomials.

#### 3.4 Polynomial Inversion

We present our hardware design and optimization for the polynomial inversion in this section. In 2020, Marotzke [Mar20] had reported an implementation for the polynomial inversion required in NTRU Prime, a post-quantum KEM. The inversion module utilizes Bernstein and Yang's extGCD algorithm [BY19] optimized to perform inversions of polynomials of degree 760 with coefficients in prime fields, where the arithmetic takes place in Digital Signal Processor (DSP) units. Since our design targets to invert polynomials in  $\mathcal R$  with large degrees (i.e.,  $\geq 12\,323$ ), the two implementations pursue different purposes and are not directly comparable.

In the following, we first divide the computation of divstep into two subroutines. Then, we introduce the main framework of the inversion and the two subroutines followed by our hardware designs.

**Performing the divstep.** Recalling Section 2.4, an extGCD for polynomial inversion computes 2r-1 divsteps. In [BY19], based on the shape of the transition matrix, Bernstein and Yang optimized the multiplication by the transition matrix in a single divstep as two simple functions:

- 1. a conditional swap: replacing  $(\delta, f, g)$  with  $(-\delta, g, f)$  if  $\delta > 0$  and  $g(0) \neq 0$ .

- 2. an elimination: replacing  $(\delta, f, g)$  with  $(1 + \delta, f, (f(0)g g(0)f)/X)$ .

Since the head coefficient f(0) is always one for computing the inversion in BIKE, we need only two information bits deduced from  $(\delta, g(0))$  in each divstep as instructions for updating (f,g) and (v,w). The first bit indicates the swap operation and the second bit is g(0) used in the elimination operation. We refer to the two information bits as *control bits* of one divstep in this paper. Furthermore, we split one divstep into two operations:

- 1. get\_control\_bits(): calculates the control bits based on the values of  $\delta$  and the necessary coefficients of the polynomials (f,g), and

- 2. update\_fg\_or\_vw(): updates the polynomials (f,g) and (v,w) based on the computed control bits.

Main Framework. Algorithm 4 describes the main framework of the polynomial inversion. As introduced above, the algorithm uses four temporary polynomials f, g, v, and w while g is initialized with the bit-reversed input polynomial  $g_{\rm in}$ . The main parts of the algorithm are 2r-1 divsteps, which are decoupled into series of get\_control\_bits() and update\_fg\_or\_vw() subroutines. Last, the algorithm shifts v one bit to the right, reverses its coefficients, and returns v as the inverse of the input polynomial.

Algorithm 4: Main framework for the polynomial inversion.

```

Input: Input polynomial g_{in} and step size s.

Output: Inverted polynomial g_{\text{out}} = g_{\text{in}}^{-1}

1 N \leftarrow \left| \frac{r}{b} \right|;

2 f[N], g[N], v[N], w[N] \leftarrow 0;

// Initialize polynomials (arrays)

3 w[0] = 1; f[0] = 1; f[N-1] \leftarrow 2^{r \bmod b};

4 q \leftarrow \text{bitreverse}(g_{\text{in}});

// Reverse the bits of the input polynomial

5 \delta \leftarrow 1;

// Degree difference of polynomials f and g

6 \tau \leftarrow 2r - 1;

// Number of divsteps to be executed

7 while \tau \geq s do

\delta, c \leftarrow \texttt{get\_control\_bits}(\delta, f[0], g[0], s);

for j=0 to N do

9

f_0, f_1 \leftarrow f[j], ((j+1) > N? 0: f[j+1]);

10

g_0, g_1 \leftarrow g[j], ((j+1) > N ? 0 : g[j+1]);

11

f[j], g[j] \leftarrow \text{update\_fg\_or\_vw}(c, f_1, f_0, g_1, g_0, s, 1);

12

13

end

for j = N to 0 do

14

v_0, v_1 \leftarrow (j == 0 ? 0 : v[j-1]), v[j];

15

w_0, w_1 \leftarrow (j == 0 ? 0 : w[j-1]), w[j];

16

v[j], w[j] \leftarrow \text{update\_fg\_or\_vw}(c, v_1, v_0, w_1, w_0, s, 0);

17

end

18

\tau \leftarrow \tau - s;

19

20 end

21 if \tau > 0 then

\delta, c \leftarrow \texttt{get\_control\_bits}(\delta, f[0], g[0], \tau);

for j = N to 0 do

23

v_0, v_1 \leftarrow (j == 0 ? 0 : v[j-1]), v[j];

24

w_0, w_1 \leftarrow (j == 0 ? 0 : w[j-1]), w[j];

25

v[j], w[j] \leftarrow \text{update\_fg\_or\_vw}(c, v_1, v_0, w_1, w_0, s, 0);

26

end

27

28 end

29 v \leftarrow \text{shift\_right}(v);

// Shift one bit to the right

30 return bitreverse (v);

```

In the algorithm, we introduce a parameter s to control the  $step\ size$ , allowing to proceed s divsteps in each iteration in parallel (cf. line 7). The get\_control\_bits() and the update\_fg\_or\_vw() take the parameter as well and proceed s steps accordingly. Therefore, the subroutine get\_control\_bits() determines 2s control bits and updates  $\delta$  based on the state of  $(\delta, f[0], g[0])$ . Afterwards, a loop iterates over all four polynomials f, g, v, and w and updates them by update\_fg\_or\_vw() for s steps in each call. Starting from line 22, the algorithm covers the remaining steps and updates only (v, w) accordingly.

Besides the step size s, the execution time of Algorithm 4 scales with the bandwidth parameter b as well. Enlarging b decreases the number of chunks N and therefore, less numbers of iteration are executed in the inner loop since update\_fg\_or\_vw() updates one chunk in each execution. In our design, the choice for s is also limited by  $s \leq b$  since get\_control\_bits() takes inputs of one polynomial chunk only. We describe the details of get\_control\_bits() and update\_fg\_or\_vw() in the following paragraphs.

**Determining Control Bits.** Algorithm 5 details the process of get\_control\_bits(). The algorithm takes four inputs, which are the degree difference  $\delta$ , two b-bit chunks

```

Algorithm 5: Compute control bits.

```

```

Input: Current \delta, f[0], g[0], and the step size s.

Output: Updated \delta and an array of control bits c[2s]

1 f, g \leftarrow f[0], g[0];

2 for i = 0 to s - 1 do

3 |swap \leftarrow ((-\delta < 0)?1:0) \& (g \land 1);

4 \alpha \leftarrow g \land 1;

5 c[i \cdot 2] \leftarrow swap;

6 c[i \cdot 2 + 1] \leftarrow \alpha;

7 \delta \leftarrow swap? - \delta + 1:\delta + 1;

8 f, g \leftarrow (swap?g:f), (g \oplus (f \cdot \alpha))/2;

9 end

10 return \delta, c;

```

Figure 5: Hardware design for the computation of the control bits.

(f[0],g[0]) from the polynomials (f,g), and the step size s. The algorithm outputs the updated  $\delta$  and 2s control bits c for s divsteps. For generating the control bits for the s divsteps, the algorithm uses only s bits from each input polynomial instead of the full coefficients. Note, however, the algorithm is a sequential process where the control bits of iteration i depends on the results of the previous iterations.

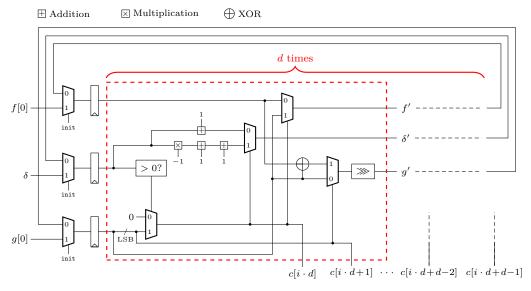

Our hardware design for get\_control\_bits() incorporates this characteristic such that we aim to fully utilize the computational capacity and hence execute d iterations of the loop shown in Algorithm 5 in one clock cycle. Therefore, Figure 5 shows a schematic draft of this approach where one iteration is highlighted by the red dashed border. For larger step sizes s, however, unrolling the whole loop in a hardware implementation would result in a long critical path. Hence, we introduce a round-based circuit that is executed  $\left\lceil \frac{s}{d} \right\rceil$  times since  $d \cdot \left\lceil \frac{s}{d} \right\rceil \geq s$ . We store the generated control bits in registers to use them immediately for updating the polynomials (f,g) and (v,w) by update\_fg\_or\_vw().

**Updating Polynomials.** We summarize the details of update\_fg\_or\_vw() in Algorithm 6. The algorithm expects as inputs the control bits c, two 2b-bit chunks of the polynomials (f,g) or (v,w), the step size s, and one bit specifying whether the input chunks originating

#### Algorithm 6: update\_fg\_or\_vw()

```

Input: Control bits c, two 2b-bit chunks of f and g, and the step size s.

Output: Updated b-bit chunks r_0 and r_1

1 for i = 0 to s - 1 do

\begin{array}{l} f,g \leftarrow (c[i \cdot 2] ? g : f), (c[i \cdot 2 + 1] ? g \oplus f : g); \\ \textbf{if} \quad \textbf{is\_updating\_fg then} \\ \mid g \leftarrow g/2 ; \\ \textbf{else} \\ \mid f \leftarrow f \cdot 2 ; \\ \textbf{end} \end{array} // \textbf{Shift } \textbf{f}

// Shift right, i.e., dividing by X

5

// Shift left, i.e., multiplying by X

6

7

s end

9 if is_updating_fg then

r_0, r_1 \leftarrow f[0:b], g[0:b];

// lower b bits

r_0, r_1 \leftarrow f[b:2b], g[b:2b];

// higher b bits

13 end

14 return r_0, r_1;

```

from the pairs (f,g) or (v,w). The algorithm updates the given chunks for s divsteps according to the control bits c. Since (f,g) and (v,w) are multiplied by the same transition matrix in the same divstep, the arithmetic for updating the polynomials is identical. The different formats of storing polynomials (see Section 2.4) cause the difference of the two operating modes, which shift polynomials in different directions and output different chunks of polynomials.

Figure 6 shows our hardware design for updating the polynomials (f,g). The basic block (highlighted by the red dashed border) updates the polynomials for one divstep, consisting of simple shifts, an addition (xor), and multiplexing operations. The whole submodule can finish the computation with s consecutive basic blocks which, however, would result in a long critical path without any further modifications. Therefore, to control the length of the critical path, we introduce pipeline registers after u basic blocks. Hence, there are  $\left\lfloor \frac{s}{u} \right\rfloor$  pipeline stages in the module. Note, we implement a similar module to update (v,w).

Although, Figure 6 depicts two full b-bit chunks for each input associated with the different polynomials, the algorithm actually only requires b+s bits of data from the input polynomials. The algorithm inputs the 2b-bit chunks because it accesses polynomials in chunks of b bits from the memory. However, the module only instantiates logic for processing s+b data such that no area overhead occurs.

Overall Design of the Polynomial Inversion. The entire polynomial inversion module consists of two counters controlling the reversion of the bits and the final right shift (cf. Algorithm 4). Additionally, we instantiate  $\mathtt{get\_control\_bits}()$  and two versions of  $\mathtt{update\_fg\_or\_vw}()$  (updating (f,g) and (u,w) in parallel) as described above. Since the algorithm works on four temporary polynomials, the inversion module utilizes eight Block-RAMs (BRAMs) allowing to read and write the intermediate results in the same clock cycle. Nevertheless, the latency of the proposed design depends on several parameters, i.e., r, b, s, d, and u. It is determined by

$$L_{\text{inv}}(s, d, u) = \underbrace{\lambda \cdot \left(3 + \left\lceil \frac{s}{d} \right\rceil + \left\lceil \frac{s}{u} \right\rceil + \left\lceil \frac{r}{b} \right\rceil\right)}_{\text{main computation}} + \underbrace{\rho + \left\lceil \frac{s}{d} \right\rceil + \left\lceil \frac{r}{b} \right\rceil}_{\text{remainder}} + \underbrace{3 \cdot \left\lceil \frac{r}{b} \right\rceil + 13}_{\text{bitreverse & shift}}$$

(3)

Figure 6: Hardware implementation of the update process for the f and g polynomial.

where  $\lambda = \left\lfloor \frac{2 \cdot r - 1}{s} \right\rfloor$  and  $\rho = \left\lceil \frac{2 \cdot r - 1 - \lambda \cdot s}{u} \right\rceil$ . Note, our design for s = 1 does not follow Equation 3 since it is a handcrafted and optimized design which achieves a slightly smaller latency and requires only seven BRAMs instead of eight.

#### 3.5 United Hardware Design

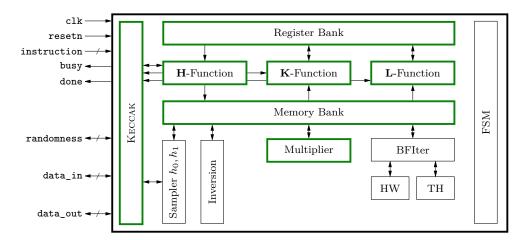

Given the optimized modules for the polynomial arithmetic and the modifications for the random oracles, we now present an united hardware design of BIKE consolidating the key generation, encapsulation and decapsulation in one module. Such a design allows to share resources between the different KEM operations. For example, we only instantiate one single multiplier, one Keccak core with the corresponding wrappers described in Section 3.2, and a limited number of BRAM modules. The number of required BRAMs is given by the decapsulation since its implementation utilizes the most memories (cf. [RBMG21]). However, this design decision implies that only one of the three KEM algorithms of BIKE can be executed at the same time. Therefore, we implement a control interface that allows to enable the desired algorithm by a three bit instruction, load and read data (polynomials and 256-bit strings), and request randomness used as seed for the PRNG. A top-level draft of this implementation is shown in Figure 7. While all building blocks that are used by more than one KEM algorithms are marked by a green border, the black modules are only required for a single KEM operation (the inversion module and sampler are used only in the key generation, and the BFIter module together with the Hamming weight and threshold computation only in the decapsulation).

The Finite-State Machine (FSM) on the right side manages all input/output operations and the control flow of the three KEM algorithms. The input interface expects a six-bit instruction identifying which data should be loaded. For the key generation no initial data is required. The encapsulation requires the public key h which needs to be loaded to a BRAM before the computation can be started. To perform a decapsulation, the implementation assumes that the user load the two parts of the cryptogram  $(c_0, c_1)$ , the two polynomials of the private key  $(h_0, h_1)$ , and  $\sigma$ . The output interface returns the same data and additionally the shared key K. After the required data has been accessed, all memories are reset by overwriting the content with zero.

# 4 Implementation Results

In this chapter, we evaluate the proposed optimizations and modifications for a hardware implementation of BIKE. First, we show that the modifications of the random oracles are

Figure 7: Top-level view of the united hardware design.

beneficial for a hardware design of BIKE. Second, we report implementation results for the proposed sparse multipliers and compare them to designs from the literature. Third, we demonstrate the scalability of our inversion module by presenting implementation results for different configurations. Fourth, since both – the multiplication and inversion – influence the footprint and performance of the key generation, we provide dedicated implementation results for a stand-alone key generation design. Fifth, we present the implementation results of the united hardware design and compare it to other implementations of code-based PQC schemes. We generate all results for an Artix-7 XC7A200T FPGA manufactured by Xilinx.

#### 4.1 New Random Oracles

As described in Section 3.2, BIKE's new specification [ABB<sup>+</sup>21] updates the random oracles from AES-256 and SHA2 to an unified Keccak core. To test how the design choice of cryptographic primitives effects the performance of hardware implementations, we compare the implementations of the original VHDL code<sup>2</sup> from [RBMG21] with our adapted version applying the new specification with a replaced Keccak core. We performed no other optimizations for a fair comparison.

Table 2 reports the comparisons for the encapsulation and decapsulation. For both KEM algorithms and all hardware configurations, the adapted versions achieve slightly better results in terms of area and latency. Especially the number of required registers decreases by roughly 880 in the adapted implementation for all designs. To this end, these implementation results show that the modifications of the random oracles are indeed beneficial for hardware implementations of BIKE.

#### 4.2 Multiplier

Table 3 shows the implementation results for our two multiplier designs configured for the lowest security level of BIKE, i.e., for  $r=12\,323$ . The first design is the general sparse multiplier where the sparse polynomial always has a fixed Hamming weight, i.e., the Hamming weight is determined before synthesis. In BIKE, such cases occur in the key generation and decapsulation where  $|p_{\rm sparse}|=w/2$ . The second design reads the Hamming weight of the sparse polynomial via an input interface. Hence, it can be used for all multiplications required in BIKE. Additionally, the design performs the encoding

$<sup>{}^2{\</sup>rm The \ authors \ published \ their \ code \ at \ https://github.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.com/Chair-for-Security-Engineering/BIKE/pithub.$

|                        |              | $\mathbf{R}$ | lesourc  | $\mathbf{e}\mathbf{s}$ |          | $\mathbf{Pe}$ | rforman     | ce      |

|------------------------|--------------|--------------|----------|------------------------|----------|---------------|-------------|---------|

|                        | Logi         | ic           | Men      | nory                   | Area     | Cycles        | Freq.       | Latency |

| b                      | LUT          | DSP          | FF       | BRAM                   | Slices   | Cycles        | $_{ m MHz}$ | ms      |

| Encapsula              | ation with   | adap         | ted rand | dom ora                | acles    |               |             |         |

| $32\mathrm{bit}$       | 6604         | 0            | 2409     | 3                      | 1906     | 151587        | 121.95      | 1.24    |

| $64\mathrm{bit}$       | 8388         | 0            | 2444     | 5                      | 2408     | 39264         | 121.95      | 0.32    |

| $128\mathrm{bit}$      | 15135        | 0            | 2625     | 10                     | 4268     | 11136         | 119.05      | 0.094   |

| Encapsula              | ation of the | he pre       | vious sp | ecificat               | ion fron | n [RBMG21     | ]           |         |

| $32\mathrm{bit}$       | 6730         | 0            | 3298     | 3                      | 2143     | 152694        | 121.95      | 1.25    |

| $64\mathrm{bit}$       | 8253         | 0            | 3327     | 5                      | 2538     | 40368         | 121.95      | 0.33    |

| $128\mathrm{bit}$      | 14829        | 0            | 3471     | 10                     | 4540     | 12240         | 121.95      | 0.10    |

| $\overline{Decapsula}$ | tion with    | adap         | ted rand | dom ora                | cles     |               |             |         |

| $32\mathrm{bit}$       | 9070         | 7            | 3055     | 10                     | 2570     | 1624402       | 125         | 13      |

| $64\mathrm{bit}$       | 14011        | 9            | 3415     | 15                     | 3933     | 515823        | 116.28      | 4.44    |

| $128\mathrm{bit}$      | 29697        | 13           | 4170     | 29                     | 8234     | 186364        | 100         | 1.86    |

| $\overline{Decapsula}$ | tion of th   | he pre       | vious sp | ecificati              | ion from | n [RBMG21     | 1           |         |

| $32\mathrm{bit}$       | 9380         | 7            | 3943     | 10                     | 2971     | 1626674       | 125         | 13.01   |

| $64\mathrm{bit}$       | 16140        | 9            | 4307     | 15                     | 4942     | 518105        | 116.28      | 4.46    |

| $128\mathrm{bit}$      | 30430        | 13           | 5063     | 29                     | 8785     | 188646        | 100         | 1.89    |

in the encapsulation in constant time. To this end, the hardware utilization is slightly higher as for the general sparse multiplier. Note, for the second multiplier design, we report performance numbers for the multiplication performed in the encapsulation, i.e.,  $|p_{\rm sparse}|=t=134$ . The number of clock cycles for different Hamming weights follows Equation 1.

Table 3 also lists the results of the schoolbook-based (dense) multiplier from [RBMG21] and of the sparse multiplier design from [HWCW19]. Since the authors of [RBMG21] only reported implementation results for  $r=10\,163$ , we extracted the multiplier from their code and synthesized it for  $r=12\,323$ . As expected, the sparse multiplier clearly outperforms the schoolbook-based design with respect to area. For a fixed Hamming weight of 71, the sparse multiplier also achieves better performance results. However, for b=128 the schoolbook multiplier achieves slightly better performance results than the tailored sparse multiplier which it trades with a huge area footprint. Therefore, the sparse multiplier is clearly superior with respect to the Area-Time (AT) product.

Compared to the multiplier from [HWCW19], our design achieves a considerably lower latency albeit our results were generated for a larger parameter set. Our design mainly differentiates from their implementation in two parts. First, we decided to instantiate two memories to store the intermediate results of the multiplication's product. This allows us to perform a read and write access in the same clock cycle while the implementation by Hu et al. requires two clock cycles. Note, for Xilinx FPGAs one could exploit the read-then-write option allowing to perform a read and write access in the same clock cycle to the same address reducing the amount of required BRAM modules. However, we decided not to use this option but rather instantiate two memories since it is a more generic approach which is universally applicable to other hardware devices as well. Second, our rotation unit performs the whole rotation within one clock cycle while the design by [HWCW19] requires  $\lceil \log b \rceil$  clock cycles. Even though our multiplier architectures consume slightly more slices, it clearly improves the AT product.

We also tried to compare our results to the design proposed in [BFG<sup>+</sup>19] but we were

|          |            | $\mathbf{Reso}$ | urces            |                   | Performance        |                |         |  |

|----------|------------|-----------------|------------------|-------------------|--------------------|----------------|---------|--|

|          | Logic      | Mei             | mory             | Area              | Cycles             | Frequency      | Latency |  |

| b        | LUT        | FF              | BRAM             | Slices            | Cycles             | $\mathrm{MHz}$ | μs      |  |

| General  | sparse m   | ultiplier       | $( p_{sparse} )$ | =w/2 =            | = 71)              |                |         |  |

| 32       | 319        | 127             | $\dot{2}$        | 132               | 27691              | 234.36         | 118.16  |  |

| 64       | 549        | 190             | 4                | 197               | 13988              | 222.22         | 62.94   |  |

| 128      | 1136       | 381             | 8                | 378               | 7172               | 184.95         | 38.78   |  |

| Tailored | sparse m   | ultiplier       | for BIK          | $E ( p_{spars} )$ | $ s_e  = t = 13$   | 4)             |         |  |

| 32       | 349        | 135             | 2                | 151               | 52261              | 238.15         | 219.5   |  |

| 64       | 629        | 204             | 4                | 245               | 26399              | 222.52         | 118.8   |  |

| 128      | 1249       | 386             | 8                | 437               | 13535              | 184.3          | 73.44   |  |

| Sparse n | nultiplier | from [H         | WCW19            | r = 10            | $163,  p_{spars} $ | $ e_e  = 71$   |         |  |

| 32       | _          | _               | 2                | 100               | 158614             | 240            | 660.89  |  |

| 64       | _          | _               | 3                | 157               | 90880              | 220            | 413.09  |  |

| 128      | _          | _               | 5                | 292               | 51688              | 210            | 246.13  |  |

| Dense pe | olynomial  | multipl         | lier from        | /RBMG2            | 21/                |                |         |  |

| 32       | 697        | 105             | 1.5              | 220               | 150 155            | 201.37         | 745.67  |  |

| 64       | 2595       | 137             | 3                | 864               | 37829              | 173.82         | 230.91  |  |

| 128      | 9539       | 293             | 6                | 3332              | 9701               | 183.66         | 52.82   |  |

Table 3: Comparison of sparse polynomial multipliers for r = 12323.

not able to figure out which value the authors applied for the parameter BW (corresponds to our bandwidth parameter b) so that a fair comparison is difficult. However, we assume that their design is similar to our multiplier design which uses fixed Hamming weights.

#### 4.3 Inversion Module

In this section, we first evaluate the polynomial inversion module described in Section 3.4 for  $b \in \mathcal{B}$  and for  $r=12\,323$  and compare our approach afterwards to the design from [RBMG21] which is based on Fermat's little theorem. Note, in all experiments we fix the maximum number of basic blocks instantiated between two register stages for the updating process of (f,g), and (v,w) to u=8 achieving a critical path that is smaller than 10 ns. Additionally, we generate all results in this subsection for a target frequency of 100 MHz.

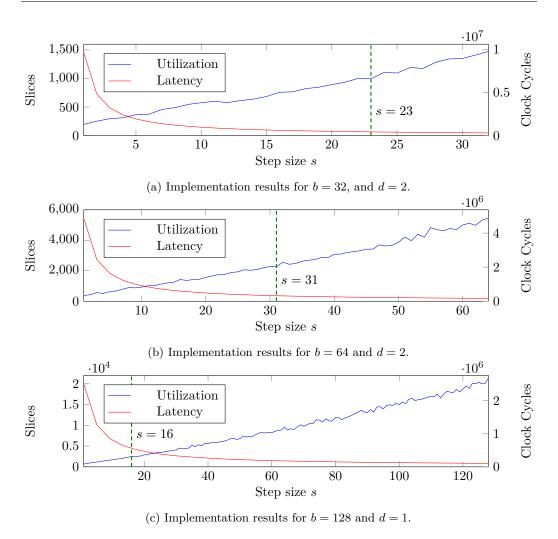

**Detailed Evaluation of the Inversion Module** Figure 8a shows the number of required slices and the latency in clock cycles for  $b=32,\ 1\le s\le 32,\$ and d=2. The area footprint linearly increases with the step size parameter s while the number of clock cycles follows Equation 3. Moreover, we include the configuration for the best AT product (slices  $\times$  cycles/10<sup>6</sup>) visualized by the green dashed line. The configuration for s=23 achieves the best result with an AT product of 432. A more detailed evaluation of the implementations can be found in the appendix in Table 7.

Figure 8b shows the implementations results for different step sizes s for b=64. The trends for the required clock cycles and for the area utilization are very similar to the configurations for b=32. The smallest configuration requires  $4\,880\,299$  clock cycles but only consumes 377 slices while the fastest design performs one inversion within 91 678 clock cycles by consuming  $5\,457$  slices. The design with the best AT product is obtained for s=31 (a detailed evaluation can be found in the appendix in Table 8).

Figure 8: Implementation results for the polynomial inversion for a Xilinx Artix-7 FPGA and a target frequency of  $100\,\mathrm{MHz}$  setting  $r=12\,323$ . The green dashed lines indicate the configurations with the best area-time product.

The implementation results for b=128 are plotted in Figure 8c where the best AT product is obtained for s=16. To achieve reasonable critical paths (maximum possible frequency larger than  $100\,\mathrm{MHz}$ ), we reduce the number of unrolled rounds to compute the control bits c to d=1. With s=128 we can instantiate our fastest inversion module which finishes one polynomial inversion in only 47 386 clock cycles. However, the implementation costs drastically increase to 21 435 slices. Again, a detailed evaluation is given in the appendix in Table 9 and Table 10.

**Comparison to Related Work.** We compare our inversion module to the approach presented in [RBMG21] which is based on Fermat's little theorem in Table 4. The corresponding numbers are extracted from their implementation of the key generation.

With Fermat's little theorem, given a  $g \in \mathcal{R}$ , [RBMG21] computes the inverse as  $g^{2^{r-1}-1}$ . To efficiently raise the degree of g, they used a square-and-multiply chain from the Itoh-Tsujii Algorithm (ITA) [IT88] achieving a latency of

$$L_{\text{inv-Fermat}} \approx \log(r) \cdot (r + L_{\text{school}}) + |r_{\text{bin}}| \cdot \left( \left\lceil \frac{r}{b} \right\rceil + L_{\text{school}} \right)$$

(4)

where  $r_{\text{bin}} = r - 2$  and  $L_{\text{school}} = \left\lceil \frac{r}{b} \right\rceil \cdot \left( \left\lceil \frac{r}{b} \right\rceil + 3 \right) + 1$ . Note, Equation 4 describes just an approximation of the required clock cycles since the implementation from [RBMG21] is highly optimized to the use-case of BIKE. However, compared to the dominant term  $\left\lfloor \frac{2\cdot r-1}{s} \right\rfloor \cdot \left\lceil \frac{r}{b} \right\rceil$  from Equation 3, our inversion module has an extra parameter s, allowing to achieve more optimized configurations.

In Table 4, we present results for the light-weight (s=1) and high-speed (s=b) configuration as well as the design with the best area-time product. For comparison with the area cost, we report a configuration targeting the number of clock cycles of the approach from [RBMG21]. While finishing the inversion with the same amount of clock cycles, Table 4 shows that the inversion module based on the extGCD achieves a smaller footprint. This implies that the extGCD implementation results in a better area-time product. We note that the inversion based on Fermat's little theorem always requires a dense polynomial multiplier, which increases the area cost notably. For the design with the best area-time product, our approach consumes roughly twice the amount of logic but finishes the inversion with only one sixth clock cycles setting b=32.

While writing this article, Deshpande et al. [DdPM<sup>+</sup>21] presented a hardware implementation of Bernstein and Yang's inversion algorithm for computing the modular inverse for integers. Their implementation targets integer sizes of 255 bits to 2048 bits which requires units for integer additions with carry logic. Since we compute the inverse of bit polynomials of at least 12 323 bits and perform carry-less additions, i.e., the XOR operation, the two implementations target different applications, and a comparison of performance numbers would be misleading.

Additionally, referring to the sequential design of [DdPM $^+$ 21], they always compute the control bits for only one divstep and update the integers with one divstep. This corresponds to the configuration of s=1 in our design introduced in Section 3.4. Hence, our inversion module provides more configurations allowing to finely adapt to various circumstances.

#### 4.4 Key Generation

We report implementation results for stand-alone key generation modules in Table 5 and compare them to the key generation module from [RBMG21]. We evaluate our designs only on the key generation because the polynomial inversion module is used solely in this KEM operation. Because our design is based on the extGCD instead on Fermat's little theorem, we do not install a dense polynomial multiplier that is required for the inversion with Fermat's little theorem. Instead, we use a sparse multiplier which is far more efficient (in both area and latency) than the dense multiplier in the key generation (cf. Table 3). Although the module of key generation consists of various components, including the PRNG based on SHAKE256, the main operations occur in the inversion module and the multiplier.

As described before, both designs perfectly scale with the bandwidth parameter b while the inversion module provides an additional configuration via the step size s. Nevertheless, for each  $b \in \mathcal{B}$ , we only pick two configurations for the inversion: (1) setting s = b which results in the fastest configurations we can achieve, and (2) instantiating the inversion module with the lowest AT product determined in Section 4.3.

The fastest key generation, that we can implement with our approaches, is obtained for b=s=128. The key generation only takes 484 µs but requires over 25 000 slices. The maximum frequencies for the designs with b=128 are slightly higher than for b=64 because the parameter d is decreased to d=1. We decided to synthesize these designs for d=1 since otherwise the critical path for the computation of the control bits would drastically increase. Note, the results for b=64 and b=128 for the designs adjusted to the best AT product achieves roughly the same performance because b is doubled while s is halved. Therefore, the design for b=64 is more efficient due to the lower footprint.

|           |              | Resou        | irces     |             | ]               | Performance |         |

|-----------|--------------|--------------|-----------|-------------|-----------------|-------------|---------|

|           | Logic        | Mem          | ory       | Area        | Cycles          | Frequency   | Latency |

| b         | LUT          | FF           | BRAM      | Slices      | Cycles          | MHz         | $\mu$ s |

| Our ligh  | t-weight d   | esigns (s =  | = 1)      |             |                 |             |         |

| 32        | 580          | 117          | 7         | 196         | 9637363         | 100         | 96637   |

| 64        | 1020         | 183          | 7         | 377         | 4880299         | 100         | 48803   |

| 128       | 1805         | 247          | 14        | 671         | 2514091         | 100         | 25141   |

| Our high  | n-speed des  | sign (s = b) | ,)        |             |                 |             |         |

| 32        | 5038         | 943          | 8         | 1473        | 316504          | 100         | 3165    |

| 64        | 18610        | 3563         | 8         | 5457        | 91678           | 100         | 917     |

| 128       | 75269        | 14028        | 16        | 21435       | 47386           | 100         | 474     |

| Our desi  | ign with th  | ne best area | a-time pr | roduct (s = | 23, s = 31, s   | s = 16)     |         |

| 32        | 3359         | 643          | 8         | 995         | 434255          | 100         | 4343    |

| 64        | 7801         | 1473         | 8         | 2269        | 172522          | 100         | 1725    |

| 128       | 8322         | 1245         | 16        | 2560        | 182138          | 100         | 1821    |

| Our desi  | ign targetis | ng the cloc  | ek cycles | of  RBMG    | [21] (s = 4, s) | =7, s=11)   |         |

| 32        | 905          | 179          | 8         | 313         | 2416672         | 100         | 24167   |

| 64        | 2391         | 334          | 8         | 786         | 708310          | 100         | 7083    |

| 128       | 5615         | 1157         | 16        | 1807        | 253533          | 100         | 2535    |

| Inversion | n Module     | used in /R   | BMG21     |             |                 |             |         |

| 32        | 1721         | 343          | 5         | 495         | 2670881         | 131.58      | 20299   |

| 64        | 3597         | 419          | 5         | 994         | 748769          | 113.64      | 6589    |

| 128       | 11878        | 722          | 10        | 3352        | 258555          | 96.15       | 2689    |

Since our proposed inversion module is highly scalable, there are many other possible configurations. An estimation of the expected footprint and clock cycles can be obtained by using the results provided in the appendix.

Unfortunately, the authors of [RBMG21] did not implement a PRNG to provide randomness to the sampler which makes a comparison more difficult. Therefore, we determined the hardware utilization of our Keccak core which consumes roughly 800 slices. Considering these additional costs, our design adjusted to the AT products of the inversion modules is roughly 5.5 times faster while it only consumes 3.6 more number of slices for b=32.

#### 4.5 United Design

We present the implementation results of the united hardware design of BIKE, introduced in Section 3.5, in Table 6 for the lowest security level. Results for Level 3 and Level 5 can be found in the appendix in Table 11. We created three different implementations where the first one is a light-weight design (b=32), the second one is a design with a trade-off between hardware resources and performance (b=64), and the last one is a high-speed design with b=128. The instantiations of the inversion module are the designs with the best AT product identified in Section 4.3.

Table 6 also contains the estimated implementation results for a united hardware design of BIKE from [RBMG21]. For the light-weight configuration, our design clearly outperforms the previous design with respect to the hardware resources and performance. This improvement is mainly due to the new multiplier design and inversion module.

For the high-speed design, our proposed implementation consumes only half the amount

|        |        |       |           |           | $\mathbf{Utiliz}$ | ation  |        | F       | Performance    | е       |

|--------|--------|-------|-----------|-----------|-------------------|--------|--------|---------|----------------|---------|

| C      | onfig  | gura  | tion      | Logic     | Men               | Memory |        | Cycles  | Frequency      | Latency |

| b      | s      | d     | PRNG*     | LUT       | FF                | BRAM   | Slices | Cycles  | $\mathrm{MHz}$ | ms      |

| This u | vork - | Hi    | gh Speed  | (s=b)     |                   |        |        |         |                |         |

| 32     | 32     | 2     | ✓         | 9880      | 3321              | 5      | 3070   | 344777  | 130.91         | 2.63    |

| 64     | 64     | 2     | ✓         | 24564     | 6255              | 10     | 7776   | 106243  | 104.65         | 1.02    |

| 128    | 128    | 1     | ✓         | 82457     | 17510             | 19     | 25009  | 55135   | 113.95         | 0.484   |

| This u | vork - | - Be  | st AT pro | oduct for | inversio          | n      |        |         |                |         |

| 32     | 23     | 2     | ✓         | 7791      | 3004              | 5      | 2179   | 462533  | 125            | 3.7     |

| 64     | 31     | 2     | ✓         | 12741     | 4169              | 10     | 3694   | 187097  | 98.04          | 1.91    |

| 128    | 16     | 1     | ✓         | 14705     | 4709              | 19     | 4121   | 189897  | 113.64         | 1.67    |

| KeyGe  | en fro | m / I | RBMG21    | 1         |                   |        |        |         |                |         |

| 32     | -      | _     | X         | 2074      | 659               | 4      | 649    | 2671076 | 131.58         | 20.30   |

| 64     | _      | _     | X         | 4432      | 1285              | 5      | 1285   | 748964  | 113.64         | 6.59    |

| 128    | _      | -     | X         | 12654     | 3554              | 10     | 3554   | 258750  | 96.15          | 2.69    |

Table 5: Comparison of stand-alone key generation modules for r = 12323.

of slices while achieving comparable performance results. Particularly, the latency of the key generation is significantly improved due to the inversion module. However, the number of clock cycles for the encapsulation and decapsulation slightly increased. This slight increase is due to the sparse polynomial multiplier.