# MIRACLE: MIcRo-ArChitectural Leakage Evaluation

A study of micro-architectural power leakage across many devices, and implications for evaluation of masking schemes and leakage modelling

Ben Marshall<sup>1,2</sup>, Dan Page<sup>1</sup> and James Webb<sup>1</sup>

<sup>1</sup> Department of Computer Science, University of Bristol, Merchant Venturers Building, Woodland Road, Bristol, BS8 1UB, UK. {ben.marshall,daniel.page,james.webb}@bristol.ac.uk <sup>2</sup> PQShield Ltd, Oxford, UK. ben.marshall@pqshield.com

**Abstract.** In this paper, we describe an extensible experimental infrastructure and methodology for evaluating the micro-architectural leakage, based on power consumption, which stems from a physical device. Building on existing literature, we use it to systematically study 14 different devices, which span 4 different instruction set architectures and 4 different vendors. The study allows a characterisation of each device with respect to any leakage effects stemming from sources within the micro-architectural implementation; we use it, for example, to identify and document several novel leakage effects (e.g., due to speculative instruction execution), and scenarios where an assumption about leakage is non-portable between different yet compatible devices.

Ours is the widest study of its kind we are aware of, and highlights a range of challenges with respect to 1) the design, implementation, and evaluation of masking schemes, 2) construction of accurate fine-grained leakage models, and 3) selection of suitable devices for experimental research. For example, in relation to 1), we cast further doubt on whether a given device can or does uphold the assumptions required by a given masking scheme; in relation to 2), we ultimately conclude that real-world leakage models (either statistical or formal) *must* include information about the micro-architecture of the device being modelled; in relation to 3), we claim the near mono-culture of devices that dominates existing literature is insufficient to support general claims regarding security. This is particularly important in the context of the FIPS 140-3 standard for non-invasive side-channel evaluation.

Keywords: side-channel attack, micro-architectural leakage, leakage modelling

# 1 Introduction

(Micro-)architecture as a concept. In the context of processor design, the term architecture<sup>1</sup> is understood as describing the interface between hardware and software. It defines how hardware and software interact, i.e., what is "visible" to the programmer, and so will typically include a definition of 1) state, 2) instructions that act on said state, and 3) an execution model for said instructions. The term Instruction Set Architecture (ISA) is often used synonymously, with micro-architecture<sup>2</sup> describing an implementation of the

$<sup>^{1}</sup>$ The term architecture seems to stem from the IBM System/360 design, which considered it as capturing "the attributes of a system as seen by the programmer" [ABB64, Page 84]; before this, the more nebulous term organisation was typical.

<sup>&</sup>lt;sup>2</sup>It seems likely the term micro-architecture stems from use of micro-coded implementations, where it can be read as the architecture controlled by a micro-program (cf. architecture controlled by a program

associated ISA, i.e., as a specific processor core. As such, the ISA represents a logical abstraction of an underlying, physical micro-architectural implementation.

Beyond pure definitional precision, this abstraction enables an important property that we now, to some extent, expect and even rely on. Principally, it is responsible for allowing behavioural diversity while ensuring functional compatibility, or, put another way, maximising flexibility with respect to implementation while retaining consistency with respect to usage: a by-design disconnection between behavioural and functional semantics of instruction execution means different micro-architectures can realise the same ISA, but, in doing so, employ features that differ in their design and/or implementation. By harnessing this fact, specific<sup>3</sup> micro-architectures can, for example, aggressively optimise instruction execution to suit a given market or use-case, without placing a burden on the programmer. Doing so often acts within a broader strategy to address limitations on scaling (e.g., clock frequency) that stem from Moore's Law.

(Micro-)architecture as an attack vector. Viewed from a different perspective, however, the same property *can* be problematic. For example, consider that development of high-assurance software typically requires both detailed knowledge of, and control over both functional and behavioural semantics of instruction execution. When met, such requirements permit 1) formal reasoning and guarantees about functional correctness, and 2) management of the associated (implementation) attack surface, e.g., by instrumenting suitable countermeasures. The abstraction of a micro-architecture by an ISA necessarily limits the degree to which this is true, however, so means the requirements are often *not* met (or at least not sufficiently so).

The way in which micro-architectural side-channel attack techniques (see, e.g., [Sze19, Section 4] and [GYCH18, Section 4]) are enabled and/or exacerbated offers an pertinent example of this problem. At a high level, such techniques harness leakage that stems from sources in a particular micro-architecture: one can classify leakage as either

- 1. *discrete* (or *digital*), meaning it relates to logical, or functional characteristics, e.g., data-dependent instruction execution latency (i.e., number of cycles) caused by micro-architectural state and execution model, or

- 2. *analogue*, meaning it relates to physical, or behavioural characteristics, e.g., datadependant power consumption [KJJ99, MOP07] or EM [GMO01, AARR02] emission caused by the behaviour of CMOS transistors which constitute the micro-architecture.

In a sense, the latter acts as a superset of the former: because analogue leakage can capture fine-grained, potentially sub-cycle features, discrete forms of leakage will typically be captured by it indirectly. Either way, however, micro-architectural abstraction implies 1) the security properties of software are difficult to reason about, and may even differ depending on the micro-architecture it is executed on, and therefore 2) development of robust software-based countermeasures is a significant challenge. Such implications have led to arguments (see, e.g., [GYH18]) for migration of traditionally opaque ISAs toward more (semi-)transparent alternatives in which (selected) micro-architectural features are visible. Likewise, they have motivated hardened micro-architectural designs (see, e.g., [KGBR19, MGH19]) which mitigate the lack of such transparency.

**Remit and organisation.** The *majority* of existing micro-architectural side-channel attacks harness some form of discrete leakage. Equally, however, there is an increasing body of work which explores analogue forms of leakage. To a significant degree, such work has been

written using the ISA).

<sup>&</sup>lt;sup>3</sup>For example, modulo trifurcation into mobile, application, and real-time profiles, the same ISA has been harnessed across a wide range of low(er)-end (e.g., ARMv7-M ISA, ARM Cortex-M3 micro-architecture), mid-range (e.g., ARMv7-A ISA, ARM Cortex-A17 micro-architecture), and high(er)-end (e.g., ARMv7-A ISA, Qualcomm Krait micro-architecture) micro-architectural implementations.

motivated by observations about the security of software-based masked implementations of cryptography: an exemplar is the "gap" between a theoretically, *provably* secure masking scheme proposed by Rivain and Prouff [RP10], versus attacks on a practical implementation thereof by Balasch et al. [BGG<sup>+</sup>14].

Set within the associated literature, we position this paper as contributing in the following ways. First, versus the Rosita framework of Shelton et al.  $[SSB^+20]$ , for example, we deliberately attempt to broaden the scope by 1) focusing on multiple, physical (vs. single, emulated) processor cores, and 2) increasing the diversity and complexity of microarchitectural features considered. Second, we place explicit value on increasing the extent to which "folk-law" observations are explainable. To a greater degree than previously, doing so provides a formal basis for the topic. Third, we place explicit value on the reusability of associated artefacts. We posit, for example, that the infrastructure and data sets stemming from our work can support forms of leakage-aware verification, such as that of Barthe et al. [BGG<sup>+</sup>20], which demand accurate, fine-grained leakage models. More specifically then, the paper is organised as follows:

- Section 2 surveys existing literature related to micro-architectural leakage. Based on this, Section 3 then attempts to define a precise, unified terminology. This allows development of a structured classification for leakage sources and effects, and so clearer discussion and evaluation of associated work.

- Section 4 describes an extensible experimental infrastructure and methodology for evaluating the micro-architectural leakage, based on power consumption, which stems from a processor core: we dub this MIRACLE, which is a backronym for MIcRo-ArChitectural Leakage Evaluation.

- Section 5 analyses specific data sets produced by the infrastructure, in order to document several novel, low-level leakage effects, and to explore some overarching high-level hypotheses. These include 1) to what extent common assumptions, such as Only Computation Leaks (OCL) [MR04] and Independent Leakage Assumption (ILA) [RSVC<sup>+</sup>11, Section 2.2], hold in practice, and 2) whether and how identical instruction sequences leak on different but compatible devices, and therefore how "portable" some forms of countermeasure are.

- Section 6 then, finally, attempts to summarise the implications for situations when consideration of micro-architectural leakage is important; we pitch this as a limited set of design or implementation guidelines for digital design and cryptographic engineers.

We carefully limit the remit of constituent work in the following ways. First, we focus exclusively on analogue micro-architectural leakage related to power consumption. We use the term micro-architectural leakage synonymously from here on, but stress that most of our results are more general, e.g., apply to instances such as EM emission. Second, we focus exclusively on identifying and documenting micro-architectural leakage; this means we deem exploitation of, and countermeasures based on leakage effects out of scope.

# 2 Background

In this section, we survey existing literature related to micro-architectural leakage: in however limited a sense, the goal is to 1) organise and summarise relevant work, which spans different research fields and focuses, and 2) clarify the relationship between this paper, and relevant work which we either build on and/or produce implications for. Due to space constraints we focus on a minimal survey of the *most* recent and/or relevant work only, deferring more comprehensive coverage to Appendix A.

(Micro-)architectural leakage effects. There have been many efforts to study particular micro-architectural sources of power leakage, and how they can undermine masking

based countermeasures. In [BGG<sup>+</sup>14], the authors discuss how physical effects in a hardware device ("glitches and transition-based leakages") can halve the security order of a masked implementation. This was followed by [PV17], which details several *specific* micro-architectural effects which can be repeatedly demonstrated as undermining a masked software implementation. This includes the "overwrite-effect" where registers are overwritten with sensitive values, the "memory remnant" effect where values written or read from memory are buffered unexpectedly and the "neighbour-leakage" effect, where explicit accesses to one register can cause implicit accesses to an adjacent register. Subsequent works such as [CGD18] and [SSB<sup>+</sup>20] replicate some or all of these effects in different devices, and introduce either new variants, or more specific cases of known variants. In [MMT20], the authors survey four devices and explicitly build on the work of [PV17]. We consider [MMT20] the work most similar to this one, in that it also surveys a wider range of effects and devices, confirming (as discussed later) that leakage effects vary widely between devices.

Other works have examined particular processor cores in great detail from a microarchitectural perspective [CGMA<sup>+</sup>15, BP18, DAK19], but have not looked more widely at families of cores, such as all ARM Cortex-M devices.

(Micro-)architectural leakage modelling and tooling. In [MWO16], the authors build a statistical leakage model of ARM Cortex-M0 and Cortex-M4 cores by examining tuples of adjacent instructions, and using statistical regression to model the resulting information leakage. This successfully captures even very esoteric kinds of leakage in instructions which are executed very closely together. However, as explored in [SSB<sup>+</sup>20], it can fail to capture cases where instructions which are executed far apart in time can induce leakage in one another. The best example being load and store instructions, which is discussed in [SSB<sup>+</sup>20, Section IV(C)], and examined in detail in Section 5.1 of this work. Another limitation of statistical modelling techniques is ensuring that a representative sample of instruction executions and sequences are used to build the model. The authors of [MWO16] found it was possible to group instructions into similarly leaking groups to minimise the problem space, but the problem of generating large amounts of initial stimulus remains.

Complementing statistical approaches to leakage modelling are formal modelling approaches. These have mostly been applied to masked *hardware* implementations, as with the **maskVerif** [BBC<sup>+</sup>19] and REBECCA [BGI<sup>+</sup>18] tools, or more recently, SILVER [KSM20].

Such techniques have also been applied to software masking. In  $[BGG^+20]$ , the authors use a Domain Specific Language (DSL) to describe the individual instructions of a processor core, and the state elements they update. This model of the micro-architecture is supplied by the user, and may need to be reverse engineered from an existing device. Assuming the accuracy of the micro-architecture model, this is a compelling approach. The TORNADO tool  $[BDM^+20]$  is another similar approach, which combines the Usuba bitslicing compiler [MDLG18] and the tightProve [BGR18] tools to generate C programs with formal side-channel security assurance in the register probing model.

In [GHP<sup>+</sup>20], the authors describe techniques for co-design and formal verification of hardware and side-channel resistant software using the REBECCA tool [BGI<sup>+</sup>18]. They give a worked example of their tool using the Ibex RISC-V core, and the parts of the hardware which gave rise to various micro-architectural sources of leakage. Their work is an excellent guide to explaining why certain leakages might be visible in the black-box processor cores analysed in this work.

# 3 Terminology

Per Section 2, study of micro-architectural leakage exists at the intersection of several different research fields, and so, in part as a result of this, associated terminology has

evolved which is imprecise or inconsistent. This can, for example, make it difficult to clearly discuss and evaluate associated work. Before any technical contributions we attempt to address this issue, doing so in two steps, i.e., first addressing architectural then microarchitectural concepts. In each such step, we use a model for instruction execution to classify associated leakage sources. Doing so allows one to reason about how and why leakage occurs, and thus how it may be avoided (or not).

It is important to note that *none* of this will be deemed innovative to digital design engineer. As well as supporting the remainder of this paper, however, we posit that shared terminology and understanding is a necessary starting point to enable 1) digital design engineers (cf. [BMT16]) to reason about the impact of leakage from their (hardware) designs and implementations, and 2) cryptographic engineers to develop useful leakage models, and thus leakage-free (software) designs and implementations.

# 3.1 Notation

Let  $\mathsf{MEM}[i]$  denote the *i*-th element of memory:  $\mathsf{MEM}[i]^j$  is used to specify an access granularity of *j* bytes where appropriate, with j = 1 (implying memory is byte addressed) assumed if/when omitted. Let  $\mathsf{GPR}[i]$  denote the *i*-th General Purpose Register (GPR); we refer to a given Special Purpose Register (SPR) by name, including an optional field where appropriate. Within the specific context of ARMv7-M, for example,  $\mathsf{PC} \equiv \mathsf{GPR}[15]$ might denote the Program Counter (PC), whereas  $\mathsf{CPSR}[C] \equiv \mathsf{CPSR}_{29}$  might be used to denote the carry flag within the Current Program Status Register (CPSR).

Let  $\mathbb{E}_i$  and  $\mathbb{C}_i$  denote some *i*-th execution and clock cycle respectively. We describe  $\mathbb{E}_i$ and  $\mathbb{E}_j$  (resp.  $\mathbb{C}_i$  and  $\mathbb{C}_j$ ) as being separated by a distance of *n* if |i - j| = n, noting that the specific case where n = 1 implies they are consecutive.

# 3.2 Architectural leakage

## 3.2.1 Model

We assume an ISA will include a definition of (at least)

- a set of architectural state, namely storage elements such as GPRs, SPRs, and memory,

- a set of architectural instruction semantics: any given instruction may read values from state elements, performs computation, and write values to state elements, and

- an instruction execution model.

An ISA will usually adopt a in-order execution model, wherein each execution cycle will atomically and independently fetch, decode, then execute a single instruction; only architectural state is guaranteed to be preserved between execution cycles.

#### 3.2.2 Leakage

**Definition 1. Architectural leakage** can be inferred from the architectural definition of instruction execution, meaning it stems *purely* from architecturally visible detail (and is thus micro-architecture agnostic).

**Definition 2. Intra-instruction leakage** can be reasoned about with within the context of 1 execution cycle (i.e., execution of 1 instruction). This contrasts with **inter-instruction leakage**, which cannot: it occurs, and thus must be reasoned about over n > 1 execution cycles (i.e., execution of n instructions).

Note that inter-instruction leakage is not limited to adjacent instructions, (i.e., those executed in  $\mathbb{E}_i$  and  $\mathbb{E}_{i\pm 1}$ ). As we explore later, interaction between and thus leakage from *non*-adjacent instructions (i.e., those executed in  $\mathbb{E}_i$  and  $\mathbb{E}_{i\pm j}$  for some j > 1) is also plausible.

Given an instruction sequence, the definitions above imply that associated architectural leakage can be inferred abstractly, i.e., *without* using a concrete implementation of the ISA: viable approaches include the use of an instruction set simulator, or even static analysis. For example, consider the following 3-instruction sequence:

```

add a0, a1, a2 // HW(a1) + HW(a2) + HW(a1 + a2) + HD(a0, a1 + a2)

add t0, t0, t2 // HW(t0) + HW(t2) + HW(t0 + t2) + HD(t0, t0 + t2)

slsl t0, t0, #4 // HW(t0) + HW(t0 << 4) + HD(t0, t0 << 4)

```

Based on an assumed leakage model for register access and bus activity, the annotation captures inferred architectural leakage, i.e., 1) Hamming weight leakage for each operand related to each read from the GPRs, 2) Hamming weight leakage related to each result computed, and 3) Hamming distance leakage related to each write to the GPRs. It is trivial to identify instances of inter- and intra-instruction leakage: the former occurs when an instruction reads operands from the GPRs or performs computation, whereas the latter occurs when an instruction writes results to the GPRs and thereby *over*writes a value already there (as written by a previous instruction, and therefore implying the required interaction).

As an aside, certain sources of architectural leakage are closely related to features in the ISA design. A given compressed instruction format, such as the RISC-V standard C extension [RV:19, Section 16] or ARMv7-M Thumb [ARM18, Chapter A5], will often employ destructive, e.g.,

add r1, r2

$$\mapsto$$

GPR[1]  $\leftarrow$  GPR[1] + GPR[2],

versus non-destructive, e.g.,

add r0, r1, r2

$$\mapsto$$

GPR[0]  $\leftarrow$  GPR[1] + GPR[2].

semantics with respect to the destination register: use of the former forces Hamming distance leakage between GPR[1] and GPR[1] + GPR[2] which can be avoided in (careful) use of the latter. There is an increasingly accepted argument (see, e.g., [RKL<sup>+</sup>04, RRKH04]) that security should be considered as a first-class metric at design-time, and, as such, one *could* argue this and similar examples should be considered within the ISA design process.

# 3.3 Micro-architectural leakage

#### 3.3.1 Model

Existing literature (see, e.g., [PV17, CGD18, SSB<sup>+</sup>20, MMT20]) has now clearly demonstrated that architectural leakage cannot accurately capture every pertinent leakage source or, therefore, effect. To do so, one *must* consider leakage which stems from the implementation of an ISA, i.e., the micro-architecture. We address this fact by extending our original model in Section 3.2: specifically, we

- extend the architectural state with a set of micro-architectural state plus a and a mapping function between architectural and micro-architectural state elements, and

- extend the architectural instruction semantics with a set of micro-architectural instruction semantics.

One could define micro-architectural state elements as being those implicitly supporting execution of instructions (by maintaining any associated values while execution occurs); this contrasts with architectural state elements, which are those explicitly used by instructions. Likewise, micro-architectural semantics describe execution of an instruction in terms of micro-architectural state elements; this contrasts with architectural semantics, which do so in terms of architectural state elements.

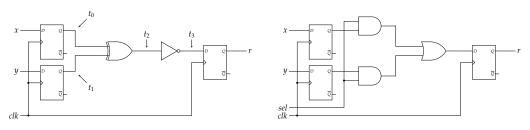

(a) Non-glitching combinatorial leakage. (b) Glitching combinatorial leakage.

Figure 1: Two example designs, illustrating the difference between non-glitching combinatorial leakage and glitching combinatorial leakage. In the left design, only combinatorial leakage is evident, based on how the signals  $t_0$  and  $t_1$  change on each clock cycle; subsequent signals, e.g.,  $t_2$  and  $t_3$ , change only once per clock cycle. Note this ignores the effect of wire delay on  $t_0$  and  $t_1$ . In the right design (a multiplexer), if the *sel*, *x*, and *y* signals all change, then the delayed *sel* signal will cause Hamming distance leakage on *r*: this causes it to glitch, i.e., change multiple times per clock cycle.

In contrast with architectural state, micro-architectural state may or may not be preserved across either execution or clock cycles. As such, the micro-architectural state mapping function and the instruction semantics must be considered, to some extent, with respect to an execution context which includes 1) the current micro-architectural state, 2) the "current" instruction (i.e., that executed in  $\mathbb{E}_i$ ), and 3) the "surrounding" instructions (i.e., those executed in  $\mathbb{E}_{i\pm j}$  for  $1 \leq j < m$  given some m). For example: where pipelining is employed, instructions following a branch may or may not be (completely) executed depending whether the branch is taken or not; where pipelining is employed, the (concrete) state element corresponding to an (abstract, architectural) register may be part of the forwarding logic versus the register file; where register renaming is employed, the (concrete) state element corresponding to an (abstract, architectural) register may differ for each write to that register.

## 3.3.2 Leakage

**Definition 3.** Micro-architectural leakage cannot be inferred from the architectural definition of instruction execution, meaning it stems *purely* from architecturally invisible detail (and is thus micro-architecture specific).

**Definition 4. Intra-cycle leakage** can be reasoned about with within the context of 1 clock cycle. This contrasts with **inter-cycle leakage**, which cannot: it occurs, and thus must be reasoned about over n > 1 clock cycles.

**Definition 5. Sequential micro-architectural leakage** occurs when the value of a state element changes.

We specifically use the term sequential leakage, because it stems from the sequential logic elements, flip-flops and registers constructed from them, used within a design. A specific instance of sequential micro-architectural leakage is necessarily classified as inter-cycle, because it occurs at the boundaries of clock cycles. However, it may be classified as *either* intra-instruction, because it can stem from isolated execution of 1 instruction (e.g., during iterative computation of a multiplication), *or* inter-instruction, because it can stem from interaction between execution of n > 1 instructions (e.g., a specific state element is updated by different instructions respectively executed in  $\mathbb{E}_i$  and  $\mathbb{E}_{i\pm j}$  for  $j \neq 0$ ).

Definition 6. Non-glitching combinatorial micro-architectural leakage occurs when the output of a combinatorial logic element toggles; glitching combinatorial micro-architectural leakage occurs when the output of a combinatorial logic element toggles more than once per clock cycle.

In existing literature, it is common for the catch-all term "glitching" to be used for either case. We carefully distinguish between the cases, observing that all leakage caused by glitching is combinatorial leakage but not all combinatorial leakage is caused by glitching. The designs in Figure 1 represent (simple) instances of the non-glitching and glitching cases respectively. Various other instances are arguably more subtle, in the sense they relate more to the physical properties of an implementation than logical properties of a design. For example, it is common to observe combinatorial leakage stemming from an inverter chain: these structures are used, for example, to mitigate issues due to 1) the standard cell library (e.g., to allow a high degree of fan-out), and/or 2) place-and-route (e.g., to drive signals over long wires).

Beyond some niche exceptions (e.g., multi-cycle paths) we deem out of scope, a specific instance of combinatorial micro-architectural leakage is necessarily classified as intra-cycle and therefore intra-instruction. This is because, within the context of a sequential logic design, the value produced by a combinatorial logic element must settle before the next clock cycle (otherwise a violation of the critical path occurs).

# 3.4 Summary

Definition 7. A given leakage source can be classified as being either

| 1) | architectural                                   | ≡        | A-class    |

|----|-------------------------------------------------|----------|------------|

| 2) | sequential micro-architectural                  | $\equiv$ | SMA-class  |

| 3) | non-glitching combinatorial micro-architectural | $\equiv$ | NCMA-class |

| 4) | glitching combinatorial micro-architectural     | $\equiv$ | GCMA-class |

and further qualified as manifesting on an a) **intra-instruction**, b) **inter-instruction**, c) **intra-cycle**, or d) **inter-cycle**, basis. A leakage source is therefore defined as the design or implementation feature that enables leakage to occur.

We stress that, due to our focus on the architectural and micro-architectural levels within what is a larger stack of abstractions, this classification should be viewed as necessary but not sufficient: it cannot and thus does not capture *every* leakage source. A pertinent example is that of capacitive coupling between wires (see, e.g., [CBG<sup>+</sup>17, CEM18, LBS19]), which, although important to model, we regard as a separate problem. Our justification is that there is no architecture or micro-architecture at that level of abstraction, only standard cells are wires: capacitive coupling leakage can therefore be regarded as at best indirectly related to any particular instruction sequence and execution of it, versus architectural or micro-architectural leakage where the same relationship is more direct.

**Definition 8.** A **leakage effect** is the form of information observable whenever a leakage source causes leakage due to execution of an instruction sequence we term a **leakage trigger**.

The term micro-benchmark<sup>4</sup> refers to a well established concept: it is a short, self-contained instruction sequence specifically designed to analyse (e.g., evaluate) some feature in the processor core that executes it. For example, the performance counter based nanoBench framework of Abel and Reineke [AR19] was used to determine (or reverse engineer) the latency, throughput, and port usage of x86 instructions, and cache architecture of x86 processor cores. We adapt the term as follows:

8

<sup>&</sup>lt;sup>4</sup>Different, context-specific terms are sometimes used for what is essentially the same concept. For example, the term litmus test is common within the context of concurrent hardware or software.

Definition 9. A leakage micro-benchmark is a specific instruction sequence constructed to prove or disprove a hypothesis about, e.g., the existence of a leakage source (and hence associated leakage effect).

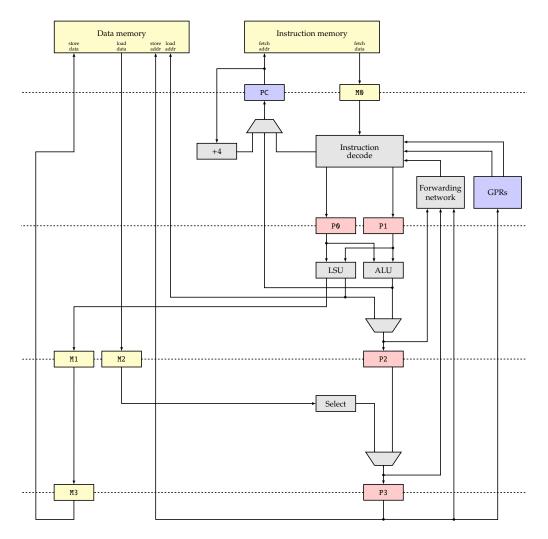

#### 4 Infrastructure

Fundamentally, we are interested in evaluating the (micro-)architectural leakage stemming from a given processor core. In this section we describe the components of MIRACLE, our experimental infrastructure and methodology for doing so. We start by introducing highlevel terminology related to the components and processes involved, then, in subsequent subsections, offer more, lower-level detail.

We refer to the physical integrated circuit containing some System on Chip (SoC) as a device; such a device will contain one or more  $cores^5$ . Most devices cannot be used in a stand-alone manner, because, for example, they require surrounding infrastructure for power delivery. We refer to this infrastructure as the host **platform**, noting that both general-purpose (i.e., support multiple devices), and special-purpose (i.e., be specific to, and even integrated with a device) instances are possible. As a result, the target of evaluation is defined by a 3-tuple of core, device, and platform. An evaluation, which we refer to as an experiment, is coordinated by a controller (i.e., a workstation) in two steps: it 1) acquires a set of power consumption traces during execution of some micro-benchmark by the target, then 2) subjects the traces to some form(s) of analysis, attempting to prove or disprove an associated **hypothesis**. We refer to the power consumption traces as the trace data set and results of analysis as the analysis data set.

Note that we avoid direct comparison of data sets stemming from different targets and therefore devices. For example, a conclusion such as "leakage is stronger in target X than target Y" is not possible. However, we do compare targets with respect to the associated hypothesis with a particular micro-benchmark. For example, a conclusion such as "target X and Y both exhibit leakage effect Z" is possible.

#### 4.1 Devices

Let  $f_i^d$  denote a device where f is the family identifier (e.g., ARM), d is the core identifier (i.e., the specific processor core), and *i* is the instance number (where more than one exits). Where necessary, we permit further annotation st.

$\implies \text{ an ASIC-based (or "hard") device} \\ \implies \text{ an FPGA-based (or "soft") device}$  $\overline{f}_i^d$  $\widetilde{f}_i^d$  $f_i^d[xMHz] \implies$  a device operating at a specific clock frequency (of xMHz)

We use this notation in Table 1, which describes the entire set of 14 different devices (currently) supported by MIRACLE. Note that each FPGA-based device is synthesised using Xilinx Vivado 2019.1; default synthesis settings are used, with no effort invested in synthesis or post-implementation optimisation.

#### 4.2 Platforms

Each device is supported by and so situated within a specific platform. MIRACLE (currently) supports 3 different platforms, described in detail by the following:

• SCALE describes a platform based on the SCALE<sup>6</sup> host board; it supports a range of interchangeable target boards, and thus devices. The trace acquisition pipeline includes

$<sup>{}^{5}</sup>$ In our case these are processor cores, but note that the terminology could be extended to accommodate, e.g., hardware accelerators. <sup>6</sup>https://github.com/danpage/scale-hw

Table 1: Pertinent technical detail for each device (currently) included in the MIRACLE study. Note that we use a short-hand for vendors: NXP denotes NXP, STM denotes STMicroelectronics, XLNX denotes Xilinx.

| $\mathbf{T}_{\mathbf{a}}$ |  |

|---------------------------|--|

| Table                     |  |

| ÷                         |  |

| _                         |  |

|                       |                                    |                                          |                                          |                            |                                                     | 1                                                   |                                                  |                                                  |                                          |                            |                                                  |                                          |                                                    |                      |

|-----------------------|------------------------------------|------------------------------------------|------------------------------------------|----------------------------|-----------------------------------------------------|-----------------------------------------------------|--------------------------------------------------|--------------------------------------------------|------------------------------------------|----------------------------|--------------------------------------------------|------------------------------------------|----------------------------------------------------|----------------------|

| RV <sup>PRV</sup>     | $\overset{\sim}{MB}_{X2}^{\times}$ | MB<br>1 MB<br>1 NB                       | - MB<br>- B<br>                          | ARM <sup>S5</sup>          | $\overline{\text{ARM}}^{\text{S4}}$                 | $\overline{\text{ARM}}^{\text{S3}}$                 | ARM <sup>S2</sup>                                | ~ 1                                              | ARM <sup>S0</sup>                        | ARM <sup>N3</sup>          | ARM <sup>N2</sup>                                | ARM <sup>N1</sup>                        | ARM                                                | Identifier Instances |

| 1                     | 1                                  |                                          | -<br>-<br>                               | ω                          | ·<br> <br>  14                                      | ·<br>                                               | 1                                                | 1                                                | <br>                                     | ω                          | 1                                                | <br>                                     | 1                                                  | Instances            |

| SASEBO-GIII           | SASEBO-GIII                        | SASEBO-GIII                              | SASEBO-GIII                              | CW308                      | CW308                                               | CW308                                               | CW308                                            | CW308                                            | CW308                                    | CW308                      | SCALE                                            | SCALE                                    |                                                    | ; Platform           |

|                       | XLNX                               | XLNX                                     | XLNX                                     | STM                        | STM                                                 | STM                                                 | STM                                              | STM                                              | STM                                      | NXP                        | NXP                                              | NXP                                      | NXP                                                | Vendor               |

|                       |                                    |                                          |                                          | STM32F051C8T6              | STM32F405RGT6                                       | STM32F303RCT7                                       | STM32F215RET6                                    | STM32F100RBT6B                                   | STM32F071RBT6                            | LPC1115FBD48/303           | NXP LPC1313FBD48/151 LQFP-48                     | LPC1114FN28/102                          | LPC812M101JDH16 TSSOP-16                           | Device               |

|                       |                                    |                                          | <br> <br> <br> <br>                      | LQFP-48                    | TQFP-64                                             | TQFP-64                                             | TQFP-64                                          | 3 TQFP-64                                        | TQFP-64                                  | 3 LQFP-48                  | 1 LQFP-48                                        | 2 DIP-28                                 | 6 TSSOP-16                                         | Package              |

| PicoRV32              | MicroBlaze v10.0                   | MicroBlaze v10.0                         | MicroBlaze v10.0                         | ARM Cortex-M0              | ARM Cortex-M4                                       | ARM Cortex-M4                                       | ARM Cort                                         | ARM Cortex-M3                                    | ARM Cortex-M0                            | ARM Cortex-M0              | ×                                                | ARM Cortex-M0                            | - M                                                | Core                 |

| 32-bit<br>multi-cycle | 32-bit<br>8-stage pipeline         | <u>32-bit</u><br><u>5-stage_pipeline</u> | <u>32-bit</u><br><u>3-stage_pipeline</u> | 32-bit<br>3-stage pipeline | 32-bit<br>3-stage pipeline<br>_ 1_cycle multiplier_ | 32-bit<br>3-stage pipeline<br>_ 1_cycle multiplier_ | 32-bit<br>3-stage pipeline<br>1-cycle multiplier | 32-bit<br>3-stage pipeline<br>1-cycle multiplier | <u>32-bit</u><br><u>3-stage_pipeline</u> | 32-bit<br>3-stage pipeline | 32-bit<br>3-stage pipeline<br>1-cycle multiplier | <u>32-bit</u><br><u>3-stage_pipeline</u> | 32-bit<br>2-stage pipeline<br>_1_cycle multiplier_ | Micro-architecture   |

| RV32IMC               | MicroBlaze                         | MicroBlaze                               | MicroBlaze                               | ARM6-M                     | ARMv7E-M<br>                                        | ARMv7-M                                             |                                                  | ARMv7-M                                          | ARM6-M                                   | ARM6-M                     | ARMv7-M                                          | ARM6-M                                   |                                                    | ISA                  |

|                       |                                    | -<br> <br> <br> <br> <br>                | <br> <br> <br> <br> <br>                 | 64 kB 8                    | 1 MB 192                                            | 256 kB 40 kB                                        | 512 kB 128                                       | 128 kB 8 kE                                      | .28 kB                                   | 64 kB 8 kB                 |                                                  |                                          | 16 kB 4                                            | Flash SRAM           |

| [Wol]                 | [Xila]                             | [Xila]                                   | [Xila]                                   | [ARMc, Mef]                | [ARMe, Mee, New]                                    | [ARMe, Med, New]                                    | Mec, N                                           | [AR.Md, Meb, New]                                | [ARMc, Mea, New]                         | [ARMc, NXPb]               | [ARMd, NXPc]                                     | [ARMc, NXPb]                             | NXPa]                                              | References           |

```

1 extern volatile void payload( word_t* inputs );

2

3 void driver( ctx_t* ctx ) {

4 word_t* inputs = ctx->receive_inputs();

5 ctx->device_set_trigger();

6 payload( inputs );

7 ctx->device_clear_trigger();

8 }

```

(a) The goal-agnostic, high-level driver (implemented in C).

```

1 .global payload

payload: push { r4, r5, r6, r7, lr } // Preserve callee save GPRs

3

<clear callee save registers>

4

<load inputs>

\mathbf{5}

<execute kernel>

6

kernel:

<clear used registers>

7

{ r4, r5, r6, r7, pc } // Restore

callee save GPRs

σοσ

8

```

(b) The goal-specific, low-level payload (implemented in assembly language).

Figure 2: The 2-part structure of each micro-benchmark.

an on-board NXP BGA2801 amplifier (with  $22\,\mathrm{dB}$  gain), and an on-board  $2.6\,\mathrm{MHz}$  low-pass filter.

- CW308 describes a platform based on the ChipWhisperer CW308 (or UFO)<sup>7</sup> host board; it supports a range of interchangeable target boards, and thus devices. The trace acquisition pipeline includes an off-board Agilent 8447D amplifier (with 25 dB gain), and an off-board MiniCircuits SLP-30+ 32 MHz low-pass filter.

- SASEBO-GIII describes a platform based on the SASEBO-GIII [HKSS12] side-channel analysis platform; it houses two FPGAs, a Xilinx Kintex-7 (model xc7k160tfbg676) target FPGA, and a Xilinx Spartan-6 (model xc6s1x45) support FPGA, and thus can be reconfigured to support a range of devices. The trace acquisition pipeline includes an off-board MiniCircuits BLK+89 D/C blocker, an off-board Agilent 8447D amplifier (with 25 dB gain), and an off-board MiniCircuits SLP-30+ 32 MHz low-pass filter.

The trace acquisition process is coordinated by a controller, which is connected to and so communicates with both the platform and a PicoScope 5000 series oscilloscope which terminates the trace acquisition pipeline. Although a platform- and/or device-specific approach to configuration and programming is required (e.g., via a Xilinx Platform Cable USB II for the SASEBO-GIII platform, or a Segger J-Link and OpenOCD for ARM-based devices), communication between the controller and platform is supported in a more uniform manner: each platform uses an FTDI-based FT232 USB-to-UART bridge then exposed to the device, which is on-board for the SCALE platform and off-board for the CW308 and SASEBO-GIII platforms.

#### 4.3 Micro-benchmarks

**Notation.** MIRACLE (currently) supports 23 different micro-benchmarks, each of which we refer to using MAJOR/MINOR as a short-hand: MAJOR is the major micro-benchmark identifier (or class), and MINOR is the minor micro-benchmark identifier (i.e., instance

<sup>&</sup>lt;sup>7</sup>https://wiki.newae.com/CW308\_UF0\_Target

within said class). Where clear from the context, we use the minor micro-benchmark identifier alone.

Each micro-benchmark must be implemented for each device, or, rather, for each unique ISA. The 7 different cores (currently) supported by MIRACLE span 4 different ISAs, however, which presents a challenge with respect to how to describe them. We use one of two approaches, depending on who or what the user of such a description is. First, our human-readable "on paper" description uses the combination of 1) a written explanation of the underlying goal, plus 2) an illustrative, pseudo-code example implementation modelled on the use of ARMv7-M; in some instances, we employ stylistic alterations<sup>8</sup> to improve their readability. On one hand, we use ARMv7-M because we expect this to be the most familiar of those ISAs support (and so add most value with respect to illustrating the underlying goal). On the other hand, although concrete ARMv7-M assembly language syntax and instruction mnemonics are used, for example, we opt for abstract, symbolic notation for values, register identifiers, etc. More specifically, we use the following notation:

- A through H represent variables; note these are not hexadecimal literals, which would be prefixed by #. Unless otherwise noted or self-evident, any two variables, say A and B, are always allocated different architectural registers.

- rA, for example, denotes a register which contains some variable A which is relevant to the associated experiment.

- rX and rY denote registers which contain an address or variable which is irrelevant to the associated experiment.

- rZ denotes a register which contains zero.

Second, our machine-readable "as source code" description is then of course a functionally equivalent but ISA-specific realisation of the pseudo-code; in doing so there is need to cope with differences between ISAs (e.g., the availability of a specific instruction type, or addressing mode), but, in all cases, we carefully avoid impact on the underlying hypothesis. Beyond formulation of the micro-benchmark goal, we found this to be the most fragile and therefore challenging aspect of the development process.

**Structure.** Each micro-benchmark is implemented using the 2-part structure described in Figure 2: the goal-agnostic, high-level micro-benchmark **driver** (Figure 2a) is implemented using C, whereas the goal-specific, low-level micro-benchmark **payload** (Figure 2b) is implemented using assembly language for the appropriate ISA. The driver part is identical for all devices, but specific to a given micro-benchmark: it is responsible, e.g., for 1) receiving a set of inputs, which are generated uniformly at random then communicated by the controller, 2) managing aspects of trace acquisition (e.g., the trigger signal), and 3) invoking the associated payload. Note that word\_t is typedef'ed to reflect the word size, e.g., to uint32\_t or uint64\_t. The payload part is responsible for realising the micro-benchmark itself; the micro-benchmark kernel is surrounded by additional instructions, which, for example, 1) clear callee-save registers before execution to ensure a fixed architectural state and prevent interaction with the input, and 2) clear all registers used by the kernel after one execution to prevent interaction with subsequent executions.

**Analysis.** For a given device, we execute each each micro-benchmark n times and so acquire n associated traces of power consumption; these, along with the input variables that allows us to completely all intermediate values, constitute the trace data set for a given experiment. Unless otherwise stated, and without loss of generality, we fix n = 20,000 for ASIC-based devices and n = 30,000 for FPGA-based devices; the traces are padded or truncated appropriately so each one contains m samples.

$<sup>^8\</sup>mathrm{Examples}$  include additional space or indentation, or labels which are either shorter or more meaningful given the associated description.

MIRACLE (currently) supports 14 devices and 23 benchmarks, meaning a total of 322 such trace data sets. We subject each one to Hamming weight and Hamming distance based correlation analysis, opting for this approach over techniques such as Test Vector Leakage Assessment (TVLA) [GJJR11] or Welch's t-test [Wel47] because it allows more confidence in a qualitative assessment of 1) whether or not there was *an* interaction between variables, and 2) exactly *which* interactions take place if so. Finally, the analysis data set that results is manually used to reason about a conclusion to the hypothesis associated with the experiment.

# 4.4 Artifacts

Among the goals of MIRACLE, we view accessibility, reproducibility, and extensibility as important<sup>9</sup> and so in need of explicit consideration: other researchers should, as far as possible, be able to access all the associated artefacts (i.e., source code and data sets), reproduce (and/or contest!) our conclusions, and develop and use, for example, additional micro-benchmarks for their own platforms and/or devices.

Similar goals are now best practice for research in general, but, within the context of MIRACLE specifically, we address them in two ways. First, all source code for MIRACLE is available online at

https://github.com/scarv/miracle

Second, we developed a web-based interface at

## https://miracle.scarv.org

which offers a straightforward way to 1) inspect the binary or disassembled form of each micro-benchmark, and 2) view and compare the associated analysis data sets. Note, however, that we do *not* (currently) retain any trace data sets. These (currently) represent more than 1 TB, which means the monetary cost and logistics of long-term storage and access are (currently) problematic. We hope to find a way to resolve this in the future.

# 5 Case studies

Note that *all* devices (currently) supported by MIRACLE, per Table 1, have a 32-bit data-path and could be described as micro-controller class. Although MIRACLE is general-purpose, this (initial) selection was intended to facilitate an exploration of (micro-)architectural leakage stemming from ostensibly similar (i.e., from the same class, and so designed to satisfy similar use-cases) devices commonly used in existing literature.

Using the MIRACLE infrastructure outlined in Section 4, this section presents said exploration via a set of case studies: each has the same structure, in the sense it 1) describes the set of micro-benchmarks used, 2) summarises the resulting analysis data sets, then 3) discusses those results, e.g., attempting to explain their occurrence, relevance, and/or implication. Some case studies replicate and generalise results in existing literature, while others, to the best of our knowledge, are novel (either in terms of the leakage effect and/or associated source).

# 5.1 Memory: hidden state

This case study focuses on the so-called *memory remnant effect*, as observed, for example, by Papagiannopoulos and Veshchikov [PV17, Section 3.2] who describe it as relating to "leakage originating from consecutive SRAM accesses". In short, it captures the

<sup>&</sup>lt;sup>9</sup>We point, for example, to the TCHES artifact evaluation process at https://ches.iacr.org/2021/ artifacts.php as evidence for this claim.

```

.text

.text

1

1

<sup>2</sup> kernel: ldr rA, [rC, #0]

<sup>2</sup> kernel: ldr rA, [rC, #0]

eor rE, rE, rE

eor rE, rE, rE

3

3

ldr rB, [rD, #0]

str rB, [rD, #0]

4

4

(a) MEMORY-BUS/LD-LD: load-after-load.

(b) MEMORY-BUS/LD-ST: store-after-load.

.text

.text

1

kernel: str rA, [rC, #0]

2 kernel: str rZ, [rA, #0]

2

eor rE, rE, rE

eor rE, rE ,rE

3

3

ldr rB, [rD, #0]

str rZ, [rB, #0]

4

4

(c) MEMORY-BUS/ST-LD: load-after-store.

(d) MEMORY-BUS/ST-ST-1: store-after-store,

overwrite with zero value.

.text

.text

1

1

2 kernel: str rA, [rC, #0]

2 kernel: str rA, [rD, #0]

eor rE, rE ,rE

str rB, [rE, #0]

3

3

str rC, [rD, #0]

str rB, [rD, #0]

4

4

(e) MEMORY-BUS/ST-ST-2: store-after-store,

(f) MEMORY-BUS/ST-ST-3: store-after-store,

overwrite with security-critical value.

with intermediate flush.

```

Figure 3: Pseudo-code for micro-benchmarks described in Section 5.1.1, i.e., those related to the case study on hidden state in the memory access path.

Table 2: A summary of results stemming from the micro-benchmarks in Figure 3, i.e., cases which explore Hamming distance leakage from combinations of ldr and str instructions. Note that AC, for example, indicates that the Hamming distance between A and C was leaked.

| Device            | LD-LD | LD-ST | ST-LD | st-st-1 | st-st-2 | ST-ST-3 |

|-------------------|-------|-------|-------|---------|---------|---------|

| ARM <sup>N0</sup> | AB    |       |       |         | AB      |         |

| ARM <sup>N1</sup> | AB    |       |       |         | AB      |         |

| ARM <sup>N2</sup> | AB    | AB    | AB    |         | AB      |         |

| ARM <sup>N3</sup> | AB    | AB    |       |         | AB      |         |

| ARM <sup>S0</sup> | AB    | AB    | AB    |         | AB      |         |

| ARM <sup>S1</sup> | AB    | AB    | AB    |         | AB      |         |

| ARM <sup>S2</sup> | AB    |       |       |         |         |         |

| ARM <sup>S3</sup> | AB    | AB    | AB    |         | AB      |         |

| ARM <sup>S4</sup> | AB    |       |       |         | AB      |         |

| ARM <sup>S5</sup> | AB    | AB    | AB    |         | AB      |         |

| MB <sup>X0</sup>  | AB    | AB    | AB    |         | AB      |         |

| $MB^{X1}$         |       |       |       |         |         |         |

| MB <sup>X2</sup>  |       |       |       |         | AB      |         |

| RVPRV             |       |       |       |         |         |         |

fact consecutive memory accesses may interact even if those accesses involve different architectural state This can be a challenging effect to identify and resolve, because 1) intermediate (e.g., ALU) instructions may not prevent leakage, and thus 2) leakage may occur due to instructions which occur far apart.

#### 5.1.1 Micro-benchmarks

Figure 3 includes pseudo-code for the micro-benchmarks used, which can be described as follows:

- 1. MEMORY-BUS/LD-LD (Figure 3a): an ldr instruction, followed by an intermediate eor (i.e., ALU) instruction, followed by an ldr instruction, none of which access the same architectural state (i.e., general-purpose registers, nor addresses in memory). The aim is to answer the question is there Hamming distance leakage between the values loaded, i.e., is there hidden state in the memory access path for ldr instructions (implying a possibility they interact)?

- 2. MEMORY-BUS/LD-ST (Figure 3b): as MEMORY-BUS/LD-LD, except with the second ldr instruction replaced by a str instruction. The aim is to answer the question is there Hamming distance leakage between the values loaded and stored, i.e., is there hidden state in the memory access path for ldr and str instructions (implying a possibility they interact)?

- 3. MEMORY-BUS/ST-LD (Figure 3c): as MEMORY-BUS/LD-ST, but with the order of ldr and str instructions swapped.

- 4. MEMORY-BUS/ST-ST-1 (Figure 3d): an str instruction, followed by an intermediate eor (i.e., ALU) instruction, followed by an str instruction, none of which access the same architectural state (i.e., general-purpose registers, nor addresses in memory). The aim is to answer the question *if a security-critical value is stored in memory, is the Hamming weight leaked by overwriting it with zero*?

- 5. MEMORY-BUS/ST-ST-2 (Figure 3e): as MEMORY-BUS/ST-ST-1, but with the str instructions storing a non-zero value. The aim is to answer the question is there Hamming distance leakage between the values stored, i.e., is there hidden state in the memory access path for str instructions (implying a possibility they interact)?

- 6. MEMORY-BUS/ST-ST-3 (Figure 3f): as MEMORY-BUS/ST-ST-2, but with 1) the str instructions accessing the same address, and 2) the intermediate instruction replaced with another str, which stores a zero value. The aim is to answer the question does the intermediate str instruction flush hidden state in the memory access path, i.e., is any Hamming weight leakage due to hidden state, or to the memory access itself.

# 5.1.2 Results

Each micro-benchmark in this case study is functionally equivalent across the set of devices used, and, where permitted by the ISA, *identical*. Despite this fact, we observe markedly different leakage behaviour across those targets. For example, from Table 2 one can identify various classes of difference:

- 1. equivalent instruction sequences executed on different cores that use different ISAs, e.g., Xilinx MicroBlaze versus ARM,

- 2. identical instruction sequences executed on different cores (from the same vendor) that use the same ISA, e.g., Xilinx MicroBlaze,

- 3. identical instruction sequences executed on different cores (from different vendors in different SoCs), that use the same ISA, e.g., NXP- versus ST-based ARM Cortex-M3, and

- 4. identical instruction sequences executed on the same core (from the same vendor in

different SoCs), e.g., ST-based ARM Cortex-M3.

Some experiments show very consistent behaviour across *architectures*. For example, all of the ARM cores behave identically for the MEMORY-BUS/LD-LD experiment. This result is widely reported in the literature. However, when looking at interactions between load and store instructions (such as might occur when spilling registers to the stack) separated by an ALU instruction (MEMORY-BUS/LD-ST and MEMORY-BUS/ST-LD) we see very different results not only between different CPU cores, but even between the same CPU core implemented by the same manufacturer but in different devices. For example, loaded and stored values interact in the ARM<sup>S1</sup> and ARM<sup>S3</sup> devices, both manufactured by ST Microelectronics. However, the ARM<sup>S2</sup> and ARM<sup>S4</sup> devices when running exactly the same code, do not leak in the same way, despite the underlying CPU core, and ISA (and hence program binary) being identical. Closer inspection of the data-sheets for these devices reveals that the ARM<sup>S2</sup> and ARM<sup>S4</sup> are high performance variants, with higher maximum operating frequencies.

A similar comparison can be made between the Xilinx MicroBlaze cores, where the 3-stage  $MB^{X0}$  had clear interactions between loaded and stored values, but in the longer pipelined  $MB^{X1}$  and  $MB^{X2}$ , the loaded and stored values do not interact.

For the store-store experiments, we see no Hamming distance leakage between the MEMORY-BUS/ST-ST-1 and MEMORY-BUS/ST-ST-3 variants. From this, we conclude that (for the number of traces we collected), leakage originates exclusively from *registers* in either the CPU core or the memory hierarchy, not from *inside the SRAM*. Indeed, only the MEMORY-BUS/ST-ST-2 experiment causes Hamming distance leakage between the values being stored. This suggests that in some cases, so long as there is an intervening store to another address (thus flushing the store data-path), values with the same mask may be safely overwritten in memory without causing leakage. This avoids the need for expensive countermeasures (some of which are well described in [SSB<sup>+</sup>20]), but we urge developers to verify that this holds on their own platforms themselves.

## 5.1.3 Discussion

In explaining some of the differences between targets with the same core but different leakage behaviours ( $ARM^{S2}$  and  $ARM^{S4}$ ), we hypothesise that the need to meet tighter timing requirements drove various design decisions regarding the core and memory interconnect, which apparently have led to totally separate load and store data-paths. Regardless of the actual reason for this difference in behaviour, from a leakage perspective, this is a critical difference between cores which must be accounted for.

Based on our observations, we extend the notion of adjacent instructions to describe different types of instruction:

Definition 10. Two distinct instructions can be described as

- **program-adjacent** if they are executed in consecutive execution cycles (i.e., they appear consecutively in program order),

- **memory-adjacent** if they are both load or store instructions, and no intermediate load or store instructions are executed between them,

- **load-adjacent** if they are both load instructions, and no intermediate load instructions are executed between them,

- **store-adjacent** if they are both store instructions, and no intermediate store instructions are executed between them.

It should be clear that *store-adjacent* and *load-adjacent* instructions are mutually exclusive, and are both subsets of *memory-adjacent* instructions. We can now say that for some cores, *memory-adjacent* instructions will leak the Hamming distance between values written or read from memory, e.g. the ARM<sup>N2</sup>. However, in the case of the ARM<sup>S2</sup>, only *load-adjacent*

.data .data 1 .align 4 .align 4 2 2 Χ: .byte 0,0,0,A,0,0,0,0 Χ: .byte 0,0,0,A,0,0,0,0 3 3 4 .text .text 5 rX, =Xkernel: ldr kernel: = X ldr rX. 6 ldrb rA, [rX, I] strb rZ, [rX, I]

(a) MEMORY-BUS/WIDTH-LD-BYTE: load from byte array.

(b) MEMORY-BUS/WIDTH-ST-BYTE: store zero into byte array.

| 1         | .data            | 1         | .data                       |

|-----------|------------------|-----------|-----------------------------|

| 2         | .align 4         | 2         | .align 4                    |

| з Х:      | .hword 0,A,O,O   | з Х:      | .hword 0,A,0,0              |

| 4         |                  | 4         |                             |

| 5         | .text            | 5         | .text                       |

| 6 kernel: | ldr rX, =X       | 6 kernel: | ldr rX, =X                  |

| 7         | ldrh rA, [rX, I] | 7         | <pre>strh rZ, [rX, I]</pre> |

(c) MEMORY-BUS/WIDTH-LD-HALF: load from half-word array.

(d) MEMORY-BUS/WIDTH-ST-HALF: store zero into half-word array.

Figure 4: Pseudo-code for micro-benchmarks described in Section 5.2.1, i.e., those related to the case study on width of the memory access path. Note that for both of these experiments I is a parameter rather than a variable: the micro-benchmark is executed 8 separate times (i.e., for  $I \in \{0, 1, ..., 7\}$ ) for the byte cases, and 4 separate times (i.e., for  $I \in \{0, 1, ..., 7\}$ ) for the half-word cases.

and *store-adjacent* instructions will leak as such. We believe that tagging instructions as such will make formal modelling of memory hierarchy related leakage much easier to reason about. There are also obvious similarities between memory consistency models and ordering constraints or fences in various ISAs. We hope that these rules can be easily added to static program checkers, and be used as extra information when looking for interactions between variables.

Based on the leakage taxonomy developed in Section 3, we classify these effects as *sequential, inter-instruction micro-architectural* leakage. Per target device, we can now explain concisely whether, e.g. load-adjacent instructions suffer from inter-instruction sequential micro-architectural leakage, or not.

For the ARM devices, we believe that the range of observed behaviours are much less surprising given a thorough reading of the AMBA-AHB bus standard [ARMa]. This bus standard is used by all of the ARM micro-controllers in the study. It is *explicitly* described as a pipelined bus architecture. Hence, the existence of *some* micro-architectural state should be expected. Observing [ARMa, Figure 1-1], the AHB block diagram, it is clear that there are *opportunities* for registers to be placed in several places, with only a finite number of sensible design choices for engineers to follow. This is shown in our results, because although different cores from the same manufacturer do differ, given that they differ, they differ consistently. This suggests it is possible to separate the leakage modelling of CPUs from the modelling of the memory interconnect.

# 5.2 Memory: data bus widths

This case study focuses on the interaction between data-type width (e.g., uint8\_t, uint16\_t, and uint32\_t) and memory bus width. The central question is how does

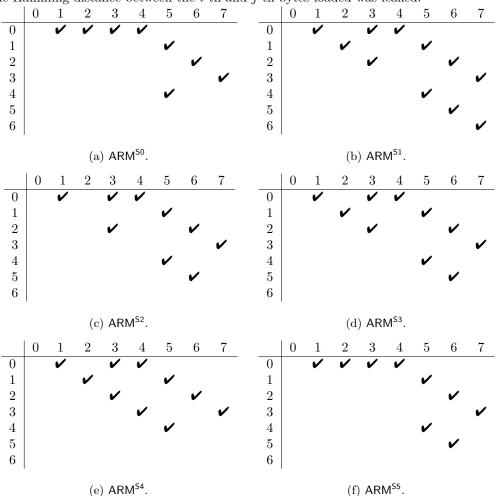

Table 3: A summary of results stemming from the micro-benchmarks in Figure 4a and Figure 4c i.e., cases which explore Hamming distance leakage from 8-bit, byte load (ldrb) instructions and 16-bit, half-word load (ldrh) instructions respectively. Note that each numbered column refers to the offset I into the array X, with a bold number used to highlight the offset for A; a  $\checkmark$  in the *i*-th column indicates that the Hamming weight of A was leaked.

| Device            |   |   |   | 1 | drb |   |   |   |   | ld | rh |   |

|-------------------|---|---|---|---|-----|---|---|---|---|----|----|---|

|                   | 0 | 1 | 2 | 3 | 4   | 5 | 6 | 7 | 0 | 1  | 2  | 3 |

| ARM <sup>N0</sup> |   |   |   | ~ | ~   | ~ | ~ |   |   | ~  | ~  |   |

| ARM <sup>N1</sup> |   |   |   | ~ | ~   | ~ | ~ |   |   | ~  | ~  |   |

| ARM <sup>N2</sup> |   |   |   | ~ | ~   | ~ | ~ |   |   | ~  | ~  |   |

| ARM <sup>N3</sup> |   |   |   | ~ | ~   | ~ | ~ |   |   | ~  | ~  |   |

| ARM <sup>S0</sup> |   |   |   | ~ | ~   | ~ | ~ |   |   | ~  | ~  |   |

| ARM <sup>S1</sup> |   |   |   | ~ | ~   | ~ | ~ |   |   | ~  | ~  |   |

| ARM <sup>S2</sup> |   |   |   | ~ | ~   | ~ | ~ |   |   | ~  | ~  |   |

| ARM <sup>S3</sup> |   |   |   | ~ | ~   | ~ | ~ |   |   | ~  | ~  |   |

| ARM <sup>S4</sup> |   |   |   | ~ | ~   | ~ | ~ |   |   | ~  | ~  |   |

| ARM <sup>S5</sup> |   |   |   | ~ | ~   | ~ | ~ |   |   | ~  | ~  |   |

| MB <sup>X0</sup>  |   |   |   | ~ | ~   | ~ | ~ |   |   | ~  | ~  |   |

| $MB^{X1}$         |   |   |   | ~ | ~   |   | ~ | ~ |   | ~  |    |   |

| MB <sup>X2</sup>  |   |   |   | ~ | ~   | V |   |   |   | ~  |    |   |

| RV <sup>PRV</sup> |   |   |   | ~ | ~   | ~ | ~ |   |   | •  | ~  |   |

Table 4: A summary of results stemming from the micro-benchmarks in Figure 4b and Figure 4d, i.e., cases which explore Hamming distance leakage from 8-bit, byte store (strb) instructions and 16-bit, half-word store (strh) instructions respectively. Note that each numbered column refers to the offset I into the array X, with a bold number used to highlight the offset for A; a  $\checkmark$  in the *i*-th column indicates that the Hamming weight of A was leaked.

| Device            |   |   |   | st | rb |   |   |   |   | st | rh |   |

|-------------------|---|---|---|----|----|---|---|---|---|----|----|---|

|                   | 0 | 1 | 2 | 3  | 4  | 5 | 6 | 7 | 0 | 1  | 2  | 3 |

| ARM <sup>N0</sup> |   |   |   |    |    |   |   |   |   |    |    |   |

| ARM <sup>N1</sup> |   |   |   |    |    |   |   |   |   |    |    |   |

| ARM <sup>N2</sup> |   |   |   |    |    |   |   |   |   |    |    |   |

| ARM <sup>N3</sup> |   |   |   |    |    |   |   |   |   |    |    |   |

| ARM <sup>S0</sup> |   |   |   | V  |    | ~ | V |   |   |    | ~  |   |

| ARM <sup>S1</sup> |   |   |   | ~  |    | ~ | ~ |   |   |    | ~  |   |

| ARM <sup>S2</sup> |   |   |   |    |    |   |   |   |   |    |    |   |

| ARM <sup>S3</sup> |   |   |   | ~  |    | ~ | ~ |   |   |    | ~  |   |

| ARM <sup>S4</sup> |   |   |   |    |    |   |   |   |   |    |    |   |

| ARM <sup>S5</sup> |   |   |   | V  |    |   | V |   |   |    | ~  |   |

| MB <sup>X0</sup>  |   |   |   | ~  |    | ~ |   |   |   |    |    |   |

| MB <sup>X1</sup>  |   |   |   |    |    |   |   |   |   |    |    |   |

| MB <sup>X2</sup>  |   |   |   | V  |    |   |   |   |   |    |    |   |

| RV <sup>PRV</sup> |   |   |   | •  |    |   |   |   |   |    |    |   |

the memory sub-system satisfy an n-byte memory access, e.g., are exactly n bytes loaded, or are m > n bytes loaded and then m - n discarded? The answer is important, because there are different approaches possible and each (potentially) has a different implication for associated leakage. Shelton et al. [SSB<sup>+</sup>20, Section IV.E] note that such leakage is evident on an ST-based ARM Cortex-M0 and in the ELMO [MWO16] power model: based on their observations as a starting point, our aim is to then 1) evaluate whether the same leakage effect is evident on other devices, and 2) explain the underlying leakage source(s).

## 5.2.1 Micro-benchmarks

Figure 4 includes pseudo-code for the micro-benchmarks used; both cases uses an 8-byte, word-aligned array X. Each element of X is initialised to zero, bar one which is instead initialised to a security-critical value A.

For the load (Figure 4a) case, the micro-benchmark loads an 8-bit (ldrb) or 16-bit (ldrh) value from a given offset I within X. If only those bytes required are accessed, we expect leakage only for an offset which implies access to the security-critical value; if leakage is observed at other offsets, we infer that bytes *other* than those required are also accessed. For the store (Figure 4b) case, the micro-benchmark stores an 8-bit (strb) or 16-bit (strh) zero value at a given offset I within X. Again, the presence (resp. absence) of leakage for a given offset allows us to infer which bytes are accessed.

#### 5.2.2 Results

Table 3 shows consistent sub-word load behaviour for all of the ARM cores in the study. Again, this effect has been noted in the literature, and we are unsurprised to confirm it across multiple devices and manufacturers. We note however the mixed results for MicroBlaze devices.

For stores, Table 4 shows differing behaviour between different cores, and even the same core implemented in different devices when adjacent bytes in memory are overwritten with zeros. We note that results for ARM<sup>S1</sup>, ARM<sup>S3</sup>, ARM<sup>S2</sup>, and ARM<sup>S4</sup> appear to mirror the results observed in Table 2. Comparatively few devices showed any leakage in this case and it is not immediately clear why Hamming weight leakage should be visible for a byte *in memory* when the word is being written too, but that exact byte is not changing value.

For the store experiments, we also note the clear divide between ARM based targets manufactured by ST-Microelectronics, which show various sources of leakage, and those built by NXP, which show no leakage at all for the same experiments. Recall again that where possible, the binary code running on each device is *identical*, yet still yields very different leakage behaviour.

## 5.2.3 Discussion

For the differing results of the MicroBlaze devices, we hypothesise this is a side effect of how FPGA BRAMs are grouped together to form different word sizes. The Xilinx 7-Series FPGA BRAMS have port widths<sup>10</sup> of 18, 36, and 72 bits [Xilb][Chapter 1]. Hence two BRAMs must be grouped together to create a 32-bit word. There is no guarantee from the Xilinx IP descriptions, or the synthesis tools, on how sub-word accesses to grouped BRAMs will behave. This is evident from the somewhat inconsistent results for the MicroBlaze cores when loading bytes and half-words. We ran all of the experiments through the Local Memory Bus (LMB) [Xila][Chapter 3, P155] used by the MicroBlaze core "primarily to access on-chip block RAM."

<sup>&</sup>lt;sup>10</sup>Note that for some power-of-two n, use of an (n + m)-bit (e.g., 18) port width is intended to support n bits (e.g.,  $2^4 = 16$ ) of data plus m bits (e.g., 2) of error correction meta-data in hardware.

```

.data

.data

.align 4

.align 4

2

2

Χ:

.byte A, B, C, D, E, F, G, H

з Х:

.byte 0.0.0.0.0.0.0.0

3

4

4

.text

.text

5

5

kernel: ldr

rX, =X

6 kernel: ldr

= X

rX.

6

ldrb rA, [rX, #0]

strb rA, [rX,

#0]

7

7

#1]

ldrb rB, [rX, #1]

strb rB, [rX,

8

8

ldrb rC, [rX, #2]

strb rC, [rX,

#2]

9

9

ldrb rD,

[rX, #3]

strb rD,

[rX,

#3]

10

10

ldrb rE, [rX, #4]

strb rE,

[rX,

#4]

11

11

strb rF,

ldrb rF, [rX, #5]

[rX, #5]

12

12

ldrb rG, [rX, #6]

strb rG, [rX, #6]

13

13

ldrb rH, [rX, #7]

strb rH, [rX,

#7]

14

14

```

(a) MEMORY-BUS/SEQ-LD: sequential load (b) bytes from array.

(b) MEMORY-BUS/SEQ-ST: sequential store bytes into array.

Figure 5: Pseudo-code for micro-benchmarks described in Section 5.3.1, i.e., those related to the case study on sequential use of the memory access path.

For the stores case, we hypothesise that leakage behaviour here is heavily dependent on the behaviour of the hardened RAMs. For example, it is possible that even when only a single byte is being explicitly accessed, the entire word is implicitly accessed (i.e. it's value is read out of the cell array) within the RAM, whether it is for a load or a store. We note that we *never* see Hamming weight leakage when the value in memory is explicitly overwritten with zeros. This might imply forwarding behaviour inside the RAMs, where the RAM *always* reads the word being accessed (regardless of whether it is a load or store), and where the word being read is being written in the same cycle, the written value is forwarded to the RAMs read data register.

As to the difference in stored value leakage behaviour between manufacturers, again we hypothesise this is down to differences in manufacturing approach for the hardened RAMs. We do not believe it is reasonable to conclude that NXP devices are on the whole *less leaky*, but note that this starkly illustrates how families of devices can behave very differently under leakage analysis.

Again, we classify these effects as load/store-adjacent, inter-instruction, sequential micro-architectural.

# 5.3 Memory: sequential accesses

This case study focuses on the behaviour of sequential accesses (i.e., loads or stores) to memory. Such an access patter can arise, for example, when the nature data-type is uint8\_t, or when accessing regions of (e.g., an array in) memory with unknown alignment. The central question is *if one loads (resp. stores) bytes from (resp. into) different addresses in memory into (resp. from) different architectural registers, is it possible they interact?* From an architectural perspective the answer should clearly be no, and so any leakage must stem from (micro-architectural) state within the memory sub-system.

#### 5.3.1 Micro-benchmarks

Figure 5 includes pseudo-code for the micro-benchmarks used; both cases uses an 8-byte, word-aligned array X.

For the load (Figure 5a) case, the micro-benchmark loads a sequence of bytes from

Table 5: A summary of results stemming from the micro-benchmarks in Figure 5a, i.e., cases which explore Hamming distance leakage from 8-bit, byte load (ldrb) instructions using different, consecutive addresses and different architectural registers; the results focus on ST-based devices only. Note that a  $\checkmark$  in the *i*-th column and *j*-th row indicates that the Hamming distance between the *i*-th and *j*-th bytes loaded was leaked.

different, consecutive addresses in memory into different architectural registers: note that ldr rA, [rX, #0] should be read as "load the 0-th element of X, i.e., the variable A, into register rA". Any Hamming distance leakage between the bytes loaded allows us to infer the presence of shared state, e.g., within 1) the memory sub-system, and/or 2) the pipeline stages used by the core (i.e., between a value being received from memory by the core, and being written into a GPR). For the load (Figure 5a) case, the micro-benchmark stores a sequence of bytes from different architectural registers into different, consecutive addresses in memory: note that str A, [rX, #0] should be read as "store register rA, i.e., the variable A, into the 0-th element of X". Any Hamming distance leakage allows similar inferences to the load case, but could *also* indicate that additional pipeline register(s) exist between the register file and the memory write-port.

## 5.3.2 Results

The results for a representative subset of the MEMORY-BUS/SEQ-LD experiment can be found in Table 5. We can see two main effects, namely 1) bytes within a word *can* interact but *may* not, and 2) the *i*-th byte of the array will *often* interact with the (i + 4)-th byte of the array.

#### 5.3.3 Discussion

We believe the first effect is due to the necessary multiplexing to select any byte of a loaded memory word, and to place it in the least significant byte of an architectural register. Clearly this multiplexing does not always cause visible leakage for the number of traces used in these experiments.

For the second effect, we believe this is because (as established in prior experiments), even when a byte of memory is requested, in reality, an entire word is loaded. Hence, when we load the first four bytes of the array, we are really repeatedly loading the entire first word. When we load byte 4 of the array, an entire new word is loaded into some micro-architectural state, and we see Hamming distance leakage between all corresponding bytes. Again, none of the instructions shared architectural destination registers, meaning all of the interactions are due to the micro-architectural leakage.