# Hardening Circuit-Design IP Against Reverse-Engineering Attacks

Animesh Chhotaray and Thomas Shrimpton

University of Florida

**Abstract.** Design-hiding techniques are a central piece of academic and industrial efforts to protect electronic circuits from being reverse-engineered. However, these techniques have lacked a principled foundation to guide their design and security evaluation, leading to a long line of broken schemes. In this paper, we begin to lay this missing foundation.

We establish formal syntax for *design-hiding (DH) schemes*, a cryptographic primitive that encompasses all known design-stage methods to hide the circuit that is handed to a (potentially adversarial) foundry for fabrication. We give two security notions for this primitive: function recovery (FR) and key recovery (KR). The former is the ostensible goal of design-hiding methods to prevent reverse-engineering the functionality of the circuit, but most prior work has focused on the latter. We then present the first provably (FR,KR)-secure DH scheme, *OneChaff*<sub>h-d</sub>.

A side-benefit of our security proof is a framework for analyzing a broad class of new DH schemes. We finish by unpacking our main security result, to provide parameter-setting guidance.

**Keywords:**  $\cdot$  cryptography  $\cdot$  provable security  $\cdot$  design hiding  $\cdot$  hardware obfuscation  $\cdot$  logic locking  $\cdot$  logic encryption  $\cdot$  IC camouflaging

#### 1 Introduction

Modern integrated-circuits (ICs, or "chips") are the product of a globally distributed supply-chain [TI19]. Much of this is driven by economics: the cost of building and operating a chip fabrication facility is exorbitant, so circuit designers are forced to send their digital intellectual property (IP) to external foundries for fabrication. In 2018, just ten foundries accounted for more than 95% of the chip-fabrication market [Tre18].

Given the lack of choice they have concerning who will fabricate and package their IP into chips, IP authors are motivated to protect their high-value circuit designs from being reverse-engineered and stolen by untrusted foundries. Along with IP theft, inserting difficult-to-detect malicious implants (or *trojans*) into ICs and producing out-of-contract, counterfeit ICs are the three major security issues in the IC supply chain.

We focus on the threat of IP theft because (intuitively) successful trojan insertion and IC counterfeiting are more difficult tasks when the adversary is denied access to the original circuit design. What's more, there are reports that estimate the cost of IP theft, and subsequent counterfeiting to be more than a hundred billion dollars in 2011 alone [Cou12, GHD+14]. Note that while there are legal restrictions for the foundries to not steal the circuit design of IP authors, the fact that they can steal and sell counterfeit chips in the black market without getting caught gives them incentive to fabricate counterfeit chips.

IP theft by the foundry is enabled when it obtains (effectively) the gate-and-wire layout for the circuit to be fabricated. Thus, the last decade has seen a surge in research on methods to "hide" the circuit IP [SPJ19]. We refer to such methods as *design-hiding* (DH) schemes. An important constraint on DH schemes is that the IP author still needs the foundry to fabricate something

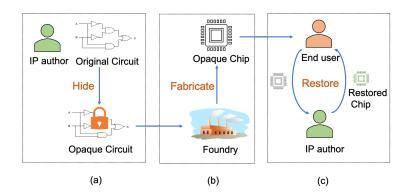

Figure 1: Simplified view of the setting for Design-Hiding schemes. The IP author is involved in hiding (a) and restoring (c) chips. The (potentially malicious) foundry controls fabrication (b) of chips.

useful; simply applying traditional encryption to the gate-and-wire layout and handing the resulting ciphertext to the foundry does not suffice. (We discuss relation to other cryptographic primitives like program obfuscation, multi-party computation and function secret-sharing in Section A.2.)

**Framing the problem.** Figure 1 gives a simplified picture of the setting in which DH techniques are typically deployed. An IP author attempts to hide (Figure 1(a)) the underlying functionality F that its plaintext circuit computes by presenting the foundry with an *opaque* version of the circuit. Upon receiving the opaque circuit, the foundry is meant to fabricate it (Figure 1(b)) into physical chips that compute whatever the opaque circuit does. These chips will likely not compute F, but this functionality can be restored (Figure 1(c)) by the IP author. Intuitively, the IP author's security goal is that only they can produce a chip that correctly computes F, i.e., the IP author's restoration mechanism is required, and only they can execute it properly. Chips that have been restored may enter the market and are available for purchase by the end-user.

Characterizing prior approaches. Broadly speaking, prior work on DH schemes falls into three categories: logic locking [RKM08, ZAMKHS19, SLP+19], IC camouflaging [RSSK13, VPH+16, SLP+19], and split manufacturing [RSK13, SAFT16]. Logic-locking¹ techniques are employed when an IP author must outsource the entire fabrication process to an untrusted, third-party foundry. Here, the foundry is provided a complete circuit description (modulo, perhaps, a small block of uninitialized write-once, tamper-resistant memory) to fabricate. This is the setting most commonly considered in the literature on circuit-design hiding. Split manufacturing primarily aims to prevent an untrusted foundry from inserting hardware-trojans into the IP author's circuit [DFS16]; as the name suggests, the fabrication of chips is spread across multiple parties, one of which is (typically) the IP author or a trusted proxy. When the trust model is altered, so that the IP author trusts the foundry but not the end user, IC camouflaging methods [CBWC12, VPH+16] can be employed. Here, the foundry fabricates an opaque circuit that contains several "camouflaged" logic cells. An end user that purchases fabricated chips from the market does not know the functionality of these camouflaged cells and hence will fail to recover the hidden design.

Our focus will be on adversarial foundries. As such, IC camouflaging is out of scope. Split manufacturing targets adversarial foundries, but it requires (effectively) that the IP author has fabrication capabilities. This is most often not the case, in practice.

Thus, we drill down on the logic-locking approach to hiding IP from untrusted foundries, and building DH schemes that are provably secure in the attack model assumed by logic-locking

<sup>&</sup>lt;sup>1</sup>This is one of several monikers used in the hardware community, others include hardware obfuscation, logic encryption, design withholding and encryption.

schemes. Here, the foundry has *unrestricted* access<sup>2</sup> to the opaque circuit and full control over the entire fabrication process, making this a challenging setting. We note that the foundry may also play the role of an end-user by purchasing packaged (restored) chips from the market. By running the chips on inputs of its choosing, it may learn the value of the original circuit design on a subset of inputs. Finally, we note that although our focus is on the logic-locking setting, our syntax also covers IC camouflaging and split manufacturing techniques. Please see Section A.1 to get a historical context of logic-locking schemes.

**Advancing the state of the art.** The design of logic-locking schemes (2008–2021) yielded schemes that were efficient, in terms of power, performance and area overhead of the opaque circuit, but ultimately insecure. We attribute this to a myopic view of what it means for a scheme to be secure, combined with a natural eagerness to focus upon efficiency. We are not alone in this belief: in their 2019 paper that broke the "provably secure" SFLL-HD scheme [YSN<sup>+</sup>17], Sirone and Subramanyan state

"Our results reinforce the observation that all logic locking schemes appear to be vulnerable to attack. We assert this is because the logic locking community has not adopted notions of provable security from cryptography." [SS19]

Indeed, the paper that presented SFLL-HD claimed provable security because it (provably) resisted *three* prominent attacks; but not Sirone and Subramanyan's FALL attack. This provides a clear reminder that a scheme should claim security —explicitly scoped by a principled and well defined security notion— only if it provably thwarts *all* (suitably efficient) attacks that are admitted by that notion.

In response to this state of affairs, we give a principled, provable-security foundation to the area. Our main contributions are as follows:

- 1. First, we formalize DH schemes as an abstract, syntactic object, i.e., a definition of what a DH scheme *is*. A DH scheme will be defined by two component algorithms, *Hide* and *Restore*, that correspond to the hiding and restoration phases discussed, above. In addition, we elevate the fabrication step, of turning circuit descriptions (necessarily visible to the foundry) into fully packaged chips (which require considerable resources and expertise to "open" and analyze), to an explicit algorithm *Fab*. This has important implications for security that have not previously been surfaced.

- 2. We establish two security notions that capture the capabilities, and goals (KR and FR), of an adversarial foundry. These notions make formal the attack model considered in prior works, and attends to details that have sometimes been quietly elided, e.g., a priori knowledge about the hidden function *F* that the foundry may have.

- We note that the SAT attack [SRM15], and other key-recovery attacks [SRM15, XSTF17, SZ17, SRZ18, YMSR17a, SLM<sup>+</sup>17a, SLR<sup>+</sup>19, ZJK17, Che18, SS19, YTS19], are admitted by our formal KR-security notion. (Some of these attacks are against DH schemes [XS16, YMRS16, YSS<sup>+</sup>17, SLM<sup>+</sup>17b, YSN<sup>+</sup>17, RMKS18, KAHS19] that were designed (post 2015) to thwart SAT attack.) The KR-security notion and our formal FR-security notion share the same abstract attack model, and Theorem 1 shows that KR *insecurity* immediately implies FR *insecurity*. Thus, the existence of these attacks implies that prior logic-locking schemes cannot achieve our notion of FR security.

- 3. We give the first DH scheme,  $OneChaff_{\rm hd}$ , that provably protects a broad class of functions (or their circuit representation) against reverse-engineering attacks. Along the way, we observe that certain types of "simple" functions (e.g., functions with small domain) cannot be protected by any DH scheme.

<sup>&</sup>lt;sup>2</sup>We use the racially neutral term "unrestricted access" instead of "whitebox access" to a circuit/function. Similarly, we use "oracle access" instead of "blackbox access."

In Section 2 we will discuss our contributions in more detail; but, before that, let us mention some of the immediate next steps that future work might take.

**Next Steps.** Our work *initiates* a provable-security exploration of DH schemes, putting the goals of prior work on a solid foundation, and showing that these goals are achievable. As such, it completes an important first step towards the ultimate goal of providing IP authors with efficient schemes that provably protect broad classes of practically relevant circuit designs. But there is much to be done between here and there, and the following list captures some of the research challenges that our results suggest.

- 1. HIDING MORE REALISTIC CIRCUITS. We consider DH schemes for stateless circuits, as these were the target of most prior work. However, many real-world circuits are stateful, and comprised of multiple stateless sub-circuits. There are very few DH schemes [CB09, AKP07, DHW+13, DY17] for stateful circuits and all of them have been shown to be broken by a recent attack [FWD+18]. Thus, extending our formalisms to such circuits is an important next step. One may treat each stateless sub-circuit as an independent circuit, and try to use *OneChaff*<sub>hd</sub> to prevent FR-attacks on each of these. For reasons that we give in Section 2, *OneChaff*<sub>hd</sub> focuses on hiding Boolean circuits, i.e., those with a single output bit. As we will explain, extending *OneChaff*<sub>hd</sub> to stateless circuits with multiple output bits requires some care. Intuitively, one can take the transitive fan-in cone<sup>3</sup> (TFC) of any output bit and use *OneChaff*<sub>hd</sub> to hide the Boolean (sub)circuit that is the indicated TFC. But determining which TFC(s) to hide may not be straightforward, as we will see.

- 2. MORE PRACTICAL SECURITY GOALS. Capturing the security goals of prior work, our FR-security notion demands that the foundry recover the *full* input-output behavior of the hidden function. But in practice, this is likely too strong. In particular, it discounts attacks that recover a "good enough" approximation of the hidden function. There are many potential ways to address this. For example, one might modify our FR-security experiment to demand input-output correctness on a subset of the function's domain; but how should this subset be determined, and how large should it be? Perhaps better, one could add an explicit *Test* algorithm the syntax of a DH scheme, and then modify the FR-security experiment to declare an attack successful only if it fools the *Test* algorithm into saying that the foundry's dishonestly produced chip (not circuit) is functionally correct. This would allow the IP author (via the DH scheme) to specify what counts as a "win" for the adversarial foundry, rather than having the security notion assert it.

- 3. EXPLORING THE EFFECTS OF A PRIORI KNOWLEDGE. Earlier works implicitly assumed that the adversary has *no* a priori information about the hidden function. Our FR-notion addresses this shortcoming, by restricting the to-be-hidden function to come from a specified set (which is a parameter of the notion); intuitively, this set captures the ability of the foundry to narrow the search space. In our analysis of *OneChaff*<sub>hd</sub>, we assume that the adversary knows the exact hamming weight of the hidden function, and we will justify this choice. But a thorough exploration of the effects of a priori knowledge, on *OneChaff*<sub>hd</sub> or any other realization of a DH scheme, is likely to be illuminating.

- 4. EMPIRICAL EVALUATIONS. We prove that our *OneChaff*<sub>hd</sub> construction is FR-secure for a wide range of functions. Still, a "head-to-head" empirical evaluation of published attacks against *OneChaff*<sub>hd</sub> and existing schemes, for a range of parameter settings and families of circuits, would be interesting. Among other things, this would help to establish the tightness of our security results, and aid in guiding security-sensitive choices in practice. Another dimension for such an empirical evaluation is to explore the power, performance and area overhead of the opaque circuits created by *OneChaff*<sub>hd</sub> vs. those produced existing DH schemes. For reasons of scope and focus, we do not explore this evaluation in the current work.

<sup>&</sup>lt;sup>3</sup>The transitive fan-in cone of an output bit in a function is the smallest subgraph in the DAG (circuit) representation that connects the primary inputs to the output bit.

# 2 Overview of Contributions

We now provide a more detailed overview of our contributions, before engaging with the technical core of the paper.

**Formal foundations for DH schemes: Syntax.** Notably absent from the area is a provable-security foundation for the design and analysis of DH schemes. Very few papers in the area offer anything along these lines. The works that do [YSN+17, MZGT17, LSM+16, SPJ19, SLP+19] fall short of what is needed, e.g., by giving syntactic descriptions that are imprecise or clearly mismatch existing schemes.

Such a foundation begins with a precise definition of a DH scheme as a syntactic object, i.e., what are the component algorithms that must be realized in a concrete scheme.

So, we begin by providing a formal syntax (in Section 4) for DH schemes, and our formalization captures all currently known methods of design-stage circuit hiding. Specifically, a DH scheme is a pair of algorithms (Hide, Restore) that abstract the portions (a) and (c) of Figure 1, respectively. Loosely, the design-hiding algorithm Hide takes as input a circuit  $C_F$  (and some design parameters  $\theta$ ), and it returns an opaque circuit  $C_L$ , along with the associated hiding key  $K_O$ . The design-restoring algorithm Restore takes an opaque  $chip \ \mathbb{C}_L$ , a hiding key  $K_O$  and design parameters  $\theta$  as inputs; it returns either a restored  $chip \ \mathbb{C}_F$  or an error symbol  $\bot$ , i.e, an indication that restoring has failed.

The opaque circuit is transformed into a chip by a separate chip-fabrication algorithm Fab that takes a circuit  $C_L$  and design parameters as inputs and returns a chip  $\mathbb{C}_L$ . Notice that we use the heavy typeface in  $\mathbb{C}_L$  to distinguish between unrestricted access to circuits (e.g.  $C_L$ ) and oracle access to chips. This is necessary as otherwise the foundry can purchase a restored chip and use invasive attacks [EHP19] to read the hiding key from (tamperproof) memory. In this work, we consider such attacks to be out of scope as protecting against invasive attacks will likely require design of special hardware like active shields [CDG<sup>+</sup>14] and are hence, orthogonal to the development of DH schemes. We note that no prior work considered the fabrication process, which turns circuits into chips, as a first-class syntactic primitive. The effect is that fabrication-specific security issues could not be cleanly surfaced. We will see that making the fabrication process explicit uncovers an important connection between the security of DH schemes, and detecting stealthy hardware trojans (in packaged chips). More on this in a moment.

Formal foundations: Security notions. Given a precise description of what a DH scheme is, we next define formal notions of what it means for a DH scheme (however it is realized) to be secure. An intuitive definition of reverse-engineering the opaque circuit is to recover from it, the hidden IP F by any means. But literature has tended to focus on attacks (and countermeasures) that attempt to recover the secret hiding key  $K_O$ . Thus, we give two formal notions of security (in Section 5): function recovery (FR) and key recovery (KR). In both notions, the adversary is provided unrestricted access to the opaque circuit, and various oracles that abstractly capture the powers of a foundry.

In the KR notion, the adversary's goal is to return a key K that is equivalent to  $K_O$ , in the sense that when one restores the functionality of an honestly fabricated chip using either K or  $K_O$ , we get restored chips with identical functionalities.

The FR notion captures a stronger attack model. In it, the adversary's goal is to find *any* chip that is functionally equivalent to F. As one expects, KR-insecurity implies FR-insecurity: if you can recover a key K equivalent to  $K_O$ , then you can win the FR game by returning an honestly fabricated chip restored with K. The converse is not necessarily true, i.e., reverse-engineering the hidden functionality of the opaque circuit does not necessarily require recovering something equivalent to the hiding key.

We note that certain kinds of functions cannot be protected by *any* DH scheme in the logic-locking setting, where the foundry may purchase honest chips and thereby learn input-output pairs of its choosing. For example, if the domain of the chip is small, the functionality of the chip can be recovered by querying the chip on its entire domain. In the case of Boolean functions, those whose

decision-tree representations have small depth/size cannot be hidden [KM93], nor can those whose Fourier spectra contain relatively few significant components [GOS+11]. So, while our security notions are agnostic to structural characteristics of the function(s) one wishes to hide, our security results will surface this concern.

We also note that our security notions allow for fully malicious foundries that may fabricate arbitrary, "dishonest" chips, and submit these to be restored with the secret hiding-key  $K_O$ . The chip may have been fabricated from the opaque circuit, but (say) with an embedded hardware trojan that outputs  $K_O$  when triggered on a particular input. Unless knowledge of the secret  $K_O$  suffices to allow the *Restore* algorithm to detect such a trojan (and alert the IP author not to proceed), the restored chip can be run by the foundry (acting as user), leaking  $K_O$  and allowing it to win the FR game. Given the state of the art in trojan detection, we know of *no remotely practical* DH scheme that can be FR-secure against fully malicious foundries. Thus, we restrict our attention to designing DH schemes that are secure against honest-but-curious foundries, i.e., ones that will try to reverse-engineer the functionality of the IP, but will only fabricate chips that adhere to the IP author's opaque circuit. This is in keeping with all prior work on DH schemes.

A new family of DH schemes: One Chaff. We introduce a family of DH schemes that we call One Chaff (see Section 6), and analyze a particular scheme One Chaff in this family. In One Chaff had, the Hide algorithm takes inspiration from SFLL-flex [YSN+17] as it encodes a single n-input-bit Boolean function H (one "chaff" function) and an uninitialized lookup table Tab in the opaque circuit. While SFLL-flex allows arbitrary H, in our One Chaff had scheme, the chaff H matches the hidden function F, except on  $\Delta \in \mathbb{N}$  uniformly chosen inputs. These are the so-called distinguishing inputs (DIs) for the pair (H, F). The hiding key  $K_O$  encodes the correct input-output behaviors on the DIs. (Practical Hide algorithms will have  $\Delta \ll 2^n$ .) On input of a key K, chip  $\mathbb{C}_L$ , and design parameters  $\theta$ , the Restore algorithm in One Chaff had loads the key K into the (write-once, tamper-resistant) uninitialized lookup table of the chip. Under honest operation, key K is equal to  $K_O$ .

**Proving security of** *OneChaff* for Boolean functions. After giving our foundations for DH schemes and introducing the *OneChaff* family of schemes, the remainder of this work is spent showing that  $OneChaff_{hd}$  provably prevents full recovery of *Boolean* functions in the presence of honest-but-curious adversarial foundries. While most real-world circuits do not compute functions returning a single bit, several prominent logic-locking schemes [XS16, YMRS16, YSS+17, YSN+17] only aim to hide Boolean functions. Moreover, no provably secure scheme exists for circuits implementing functions from this "base" class. We note that for circuits with multiple output bits, one can attempt to hide Boolean sub-functions that are determined by the transitive fan-in cone (TFC) of individual output bits.

Our main security result (Theorem 3) gives an upperbound on the probability that a computationally bounded, honest-but-curious foundry manages to win the FR game against *OneChaff*<sub>hd</sub>. To the best of our knowledge, this is *the first positive provable-security result* on DH schemes.

Security holds for Boolean functions that are not "simple" in the sense we mentioned earlier (no DH scheme can hide those) under some assumptions about the *a priori* knowledge that the adversary has about F. All prior schemes assume that the adversary has *no* a priori knowledge of F. Such an assumption is unrealistic and also makes the adversary weak as the initial "guess" space of the adversary is the set of all Boolean functions. In our FR analysis of  $OneChaff_{hd}$ , we assume that the adversary knows a priori the hamming weight h, i.e., the number of inputs that cause F to output one. This narrows the initial "guess space" to Boolean functions that have hamming weight of h. Also, the hamming-weight parameter allows us to capture the fact that the number of functions in the guess space of the adversary increases exponentially in h. Hence, functions with hamming weight close to  $2^{n-1}$  will be more secure compared to functions with hamming weights close to zero or  $2^n$ . This is also intuitive and in agreement to a result from learning theory that states that a random Boolean function (with sufficiently large domain) will not be simple, as it will lack the highly concentrated Fourier spectral structure that is typically needed for a function to be

learnable. Note that a random Boolean function will have expected hamming weight close to  $2^{n-1}$ .

Our analysis essentially bounds the number of functions that remain in the adversary's guess space after some number of true input-output observations  $(X_1, F(X_1)), \ldots, (X_q, F(X_q))$  are (adaptively) obtained. Intuitively, if a large number of functions remain in the guess space, then the probability of winning the FR-game will be small, and conversely if the adversary is able to eliminate all but a few functions, the adversary's winning probability will be close to one.

From Theorem 3, and the analysis leading to it, we can glean some useful observations. In particular, the IP author should use  $OneChaff_{\mathrm{hd}}$  to protect Boolean functions (or Boolean subfunctions) that have large domains, and hamming weights not too close to 0 or  $2^n$ . Functions with small domains cannot be hidden by any DH scheme, at least not without severely restrictive assumptions on the adversary. When the hamming weight tends towards 0 or  $2^n$ , the function tends towards a constant function. Intuitively, as the (known) hamming weight of the hidden function moves away from  $2^{n-1}$  towards either 0 or  $2^n$ , the number of possible functions decreases. This makes it more likely, although not necessarily "likely", that the hidden function can be guessed after seeing the opaque circuit and some true (X, F(X)) pairs. Finally, the IP author should choose to make  $\Delta$  as large as is feasible. Intuitively, if  $\Delta$  is small, the number of functions that remain in the adversary's guess space after it gets access to the opaque circuit (that encodes chaff H and a lookup table Tab) will also be small compared to large  $\Delta$ . Note that the new guess space will contain only functions that have a hamming weight of h (due to its a priori knowledge of the hamming weight of F) and that also differ from H on  $\Delta$  DIs (by construction).

# 3 Preliminaries

**Basic notation.** When X, Y are strings, we establish the following notations. We write  $X \parallel Y$  to denote the concatenation of X and Y; X[i] for the i-th element of X; and |X| to denote the length of X. We extend the last two notations to ordered objects (e.g., a sequence, list, table).

When T is any ordered object, we write T[i] for the i-th element, and |T| to denote the number of elements in T. In pseudocode, our convention will be: all such T are initialized to  $T[i] = \bot$  for all values of i, where  $\bot$  is a distinguished symbol. Likewise, all sets will be initially empty. We use the notation  $\langle V \rangle$  to denote the encoding of object V as a bit string. The method of encoding is left implicit, and it is silently overloaded to accommodate whatever is the type of V.

When m is an integer, we use the standard notation [m] to denote the set  $\{1,2,\ldots,m\}$ . We write  $v_1,v_2,\ldots,v_r \leftarrow V$  to denote sampling (with replacement) r>0 uniform elements of V, where V is some non-empty set. An unembellished  $\leftarrow$  denotes deterministic assignment. This notation is also used for randomized algorithms, i.e.,  $x \leftarrow A(\cdots)$  means that algorithm A runs on its indicated inputs, and halts with an output that is assigned to x. (In this case, the distribution on output values is determined by A, and is not necessarily uniform.)

We write  $A^{\mathcal{O}_1,\mathcal{O}_2,\cdots}$  to denote that algorithm A has oracle access to the superscripted oracles. For randomized algorithms X that may return a distinguished symbol  $\bot$ , the support of the algorithm  $\operatorname{Sup}(X)$  is defined only over non- $\bot$  outputs. An *adversary* is a randomized algorithm.

Functions and their representations. When  $\mathcal{D}, \mathcal{R}$  are non-empty sets, we write  $\operatorname{Func}(\mathcal{D}, \mathcal{R})$  for the set of all functions  $F \colon \mathcal{D} \to \mathcal{R}$ . We write  $\operatorname{Func}(n,m)$  as shorthand for functions with  $\mathcal{D} = \{0,1\}^n$  and  $\mathcal{R} = \{0,1\}^m$ . When m=1,  $\operatorname{Func}(n,1)$  is the set of all Boolean functions. We will use three representations of functions in this work:  $\operatorname{circuits}$ ,  $\operatorname{chips}$  and  $\operatorname{lookup}$  tables. While circuits and chips will be used to describe the design phase of the IC supply chain and are important to denote the type of access (oracle or unrestricted) to a circuit that an adversary gets as part of the threat model, lookup tables will be used primarily for functional analyses.

Formally, a *circuit*  $C_F$  is a directed acyclic graph that implements some mapping  $F \in \operatorname{Func}(\mathcal{D}, \mathcal{R})$ . Access to circuits will always be unrestricted. This captures a reality of our setting, in which the foundry is handed a description of a circuit to be fabricated. Once a circuit  $C_F$  is fabricated, we will refer to it as a *chip* and use the heavy typeface  $\mathbb{C}_F$  to make this distinction clear.

Crucially, access to  $\mathbb{C}_F$  is *not* unrestricted; rather an adversary can only use  $\mathbb{C}_F$  to make *oracle* queries. This syntactic choice is to make invasive attacks [EHP19] on chips (to leak secrets) out of scope as they are orthogonal to the (algorithmic) development of design-hiding schemes — the central primitive in our work.

The lookup-table representation of a function F with domain  $\mathcal{D}$  and range  $\mathcal{R}$  is a table  $T_F = \langle (X_1, Y_1), (X_2, Y_2), \ldots \rangle$ , where  $X_i \in \mathcal{D}$  and  $Y_i = F(X_i)$ .

In all representations of functions, when the underlying mapping is implicit/understood, we will omit the subscript.

When F,G are two n-bit to m-bit functions, the *hamming distance* between F and G is the number of inputs  $X_i$  on which the value of the functions differ. We use  $\mathcal{I}^{\neq}(F,G)$  to denote the set of such *distinguishing inputs*, i.e.,  $\mathcal{I}^{\neq}(F,G) = \mathcal{I}^{\neq}(G,F) = \{x \in \{0,1\}^n \mid F(x) \neq G(x)\}$ . Formally,  $\mathrm{hd}(F,G) = |\mathcal{I}^{\neq}(F,G)|$ . We write  $F \equiv G$  whenever  $\mathrm{hd}(F,G) = 0$ .

We will also find it useful to define the *hamming weight* of Boolean functions. When  $F \in \operatorname{Func}(n,1)$ , the *hamming weight* of F is defined as the number of inputs that map to one, i.e.,  $\operatorname{hw}(F) = |\{X \in \{0,1\}^n \mid F(X) = 1\}|$ . Also, for Boolean functions, we will use sets  $\mathcal{X}_i(F) = \{X \mid F(X) = i\}$ , where i = 0 or 1, to denote the set of inputs for which F map to 1 or 0. Notice that these two sets fully define F as we can construct the truth table of F using  $\mathcal{X}_0(F)$  and  $\mathcal{X}_1(F)$ .

We define the  $\Delta$ -neighborhood of F as  $N_{\Delta}(F) = \{H \in \operatorname{Func}(n,m) \mid \operatorname{hd}(F,H) = \Delta\}$  for any  $F \in \operatorname{Func}(n,m)$ .

#### 4 DH Schemes

We begin by defining design-hiding scheme as a syntactic object. Loosely speaking, the syntax describes the inputs and outputs of the core algorithms that any DH scheme must realize, as well as what it means for a DH scheme to operate correctly.

**Definition 1.** Fix integers n, m > 0. A design-hiding (DH) scheme  $\Pi = (Hide, Restore)$  for Func(n, m), with key length  $k_o : \{0, 1\}^* \to \mathbb{N}$  is a tuple of algorithms with the following syntax.

- The randomized design-hiding algorithm Hide:

Inputs: a circuit  $C_F$  implementing  $F \in \operatorname{Func}(n,m)$ , and a string of design parameters  $\theta$ .

Outputs: the distinguished symbol  $\bot$  ("error"), or a tuple consisting of (1) a secret key  $K_O \in \{0,1\}^{k_o(\theta)}$ , (2) and an opaque circuit  $C_L$ , where  $L \in \operatorname{Func}(n+k_o(\theta),m)$ .

Requirements: for every input  $(F,\theta)$ , either  $\Pr[Hide(C_F,\theta)=\bot]=1$  or  $\Pr[Hide(C_F,\theta)=\bot]=0$ .

- The deterministic design-restoring algorithm Restore:

Inputs: a key  $K \in \{0,1\}^{k_o(\theta)}$ , a string of design parameters  $\theta$ , and a chip  $\mathbb{C}_L$ .

Outputs: a restored chip  $\mathbb{C}_F$  or  $\bot$ . When  $K_O$  the key that is used by Hide to produce  $C_L$  is the key input to Restore, we refer to the resulting chip  $\mathbb{C}_F$  as an honestly-restored chip. Requirements: for every input  $(K, \theta, \mathbb{C}_L)$ , it must be that  $\mathbb{C}_F \leftarrow Restore(K, \theta, \mathbb{C}_L) \neq \bot$  implies that  $\overline{F} \in Func(n, m)$ .

We assume that if an algorithm is called on a point outside of its domain, in particular if any of its inputs are  $\bot$ , then the algorithm returns  $\bot$ .

The syntax that we have just established is fashioned to capture the techniques — logic locking, IC camouflaging, and split manufacturing — that an IP author uses to (a) protect the "privacy" of its high-value circuit-design  $C_F$  from adversarial entities in the post-design phase of the IC supply chain, and (b) make functionally-correct chips available to the end user. Let us elaborate using the logic-locking setting.

The IP author often outsources the fabrication of  $C_F$  into physical chips  $\mathbb{C}_F$  to third-party foundries. (We will formalize this transformation in the next section.) The foundries are potentially malicious entities. Hence, the IP author cannot give the foundries the circuit design  $C_F$  (in

$\Diamond$

plaintext). The design-hiding algorithm Hide abstracts the mechanism by which the IP author turns  $C_F$  into an opaque circuit  $C_L$  that "hides" the functionality F using a secret key  $K_O$ . The circuit  $C_L$  takes  $k_o(\theta) + n$  bits of input, where n is the length of the input to F. Here, the additional  $k_o(\theta)$  bits encode the key  $K_O$ , which will be used to restore the functionality of the chips (that the foundry produces) to the original, intended functionality F. Specific instantiations of Hide include the locking process in logic-locking schemes like random logic-locking (RLL) [RKM08] and its variants [RPSK12a, RPSK12b, DBDN+14, PM14], SAT-attack-resistant schemes [YSN+17, XS16, YMRS16, YSS+17, KAHS19], etc. We insist that for a given pair  $(F,\theta)$ , either Hide works always (returns valid  $K_O$  and L) or it always fails (returns  $\bot$ ).

The meaning of the parameter string  $\theta$  depends heavily on the particular instantiation of the design-hiding scheme. For example, it may encode the number of "key gates" to be inserted in an RLL scheme [RKM08], or the target hamming distance in SFLL-HD [YSN+17]. It may also encode other design constraints, such as the maximum size and depth of a locked circuit, restrictions on gate types, and so on.

We envision that the IP author will securely store the key  $K_O$ , and send the opaque circuit  $C_L$  to the foundry, instead of the (plaintext) circuit  $C_F$ . The foundry will fabricate and package one or more opaque chips; if the foundry is *honest*, then each chip will implement L. We formalize this in a moment.

Intuitively, the design-restoring algorithm *Restore* abstracts the mechanism by which a fabricated and packaged chip  $\mathbb{C}_L$  is restored to its original, intended functionality F. Loosely, this entails fixing the  $k_o(\theta)$  "key bits" in the input to  $\mathbb{C}_L$  to  $K_O$ . In logic locking, the opaque chips are restored by (at least) having a key installed in some tamper-proof, one-time writable memory unit within the chip.

**Fabrication and DH-scheme correctness.** In order to define the correctness for a DH scheme, we need some mechanism for turning an opaque circuit into a chip. This is exactly the role of the fabrication process that the foundry is meant to provide. Thus, let Fab be a randomized *chip-fabrication algorithm*: it takes as inputs a circuit  $C_L$  and a string of design parameters  $\theta$ , and it outputs either a chip  $\mathbb{C}_L$ , or the error symbol  $\bot$ .

**Definition 2.** A DH scheme  $\Pi = (Hide, Restore)$  is *correct* with respect to chip fabrication Fab if, for any  $(F, \theta)$  and any  $(K_O, C_L) \in \operatorname{Supp}(Hide(C_F, \theta))$ , we have

$$\Pr[\mathbb{C}_G \leftarrow \text{$\circ$ Restore}(K_O, \theta, Fab(C_L, \theta)) : (\mathbb{C}_G \neq \bot) \Rightarrow (G \equiv F)] = 1,$$

where, the probability is over the coins of Fab.

In words, this requirement asserts that whenever  $(F, \theta)$  is a pair that results in an opaque circuit  $C_L$  with associated key  $K_O$ , it must be the case that an honestly-restored chip computes F exactly.

We will find it useful to define an *honest* chip-fabrication algorithm. Loosely, we say that a chip-fabrication algorithm Fab is honest if the chip that it produces computes exactly what it is supposed to compute. Formally, this requires that for any circuit  $C_L$ , and design-parameters  $\theta$ ,  $\Pr\left[\mathbb{C}_{\hat{L}} \leftarrow Fab(C_L, \theta) : (\mathbb{C}_{\hat{L}} \neq \bot) \Rightarrow (\hat{L} \equiv L)\right] = 1$ , where the probability is over the coins of Fab. We note that the correctness of a DH scheme does not require honest Fab; indeed,  $Fab(C_L, \theta)$  may produce a chip  $\mathbb{C}_{\hat{L}}$  such that for some  $Y \in \mathrm{Dom}(F)$ ,  $\hat{L}(K, Y) \neq L(K, Y)$  for (say) a small set of keys  $K \neq K_O$ . For example, a hardware trojan [CB11] can be embedded in the description of Fab such that a fabricated opaque chip  $\mathbb{C}_{\hat{L}}$  implements  $L(K_O, \cdot)$  honestly; on keys  $\hat{K} \neq K_O$ ,  $\hat{L}$  may leak information about  $K_O$ .

# 5 Security Notions

We consider two notions of security for DH schemes. Both notions deal with an adversarial foundry that attempts to recover the original functionality that the opaque circuit hides. The adversary gets

```

Experiment \mathbf{Exp}^{\mathrm{FR}}_{(\Pi,\theta),\mathit{Fab}}(\mathcal{F},A)

Experiment \mathbf{Exp}^{\mathrm{KR}}_{(\Pi,\theta),\mathit{Fab}}(\mathcal{F},A)

F \leftarrow \mathcal{F}; i \leftarrow 0

F \leftarrow \mathcal{F}; i \leftarrow 0

\begin{array}{l} (K_O,C_L) \leftarrow ^{\mathrm{s}} \mathit{Hide}(C_F,\theta) \\ K \leftarrow ^{\mathrm{s}} A^{\mathrm{FAB},\mathrm{RESTORE},\mathrm{RUN}}(C_L,\theta) \end{array}

(K_O, C_L) \leftarrow \$ Hide(C_F, \theta)

\mathbb{C}_G \leftarrow A^{\mathsf{FAB},\mathsf{RESTORE},\mathsf{RUN}}(C_L,\theta)

Ret [G \equiv F]

\mathbb{C}_G \leftarrow Restore(K, \theta, Fab(C_L, \theta))

Ret [G \equiv F]

oracle FAB(Z):

oracle RESTORE(\mathbb{C}_{\hat{L}}):

oracle RUN(j, X):

\mathbb{C}_P \leftarrow \mathcal{U}[j]

if Z = \varepsilon then //make intended chip

if \mathbb{C}_{\hat{L}} \notin \mathcal{H} \cup \mathcal{N} then Ret \perp

Ret P(X)

\mathbb{C}_L \leftarrow \$ Fab(C_L, \theta)

\mathbb{C}_P \leftarrow Restore(K_O, \theta, \mathbb{C}_{\hat{L}})

\mathcal{H} \leftarrow \mathcal{H} \cup \{\mathbb{C}_L\}

if \mathbb{C}_P \neq \bot then

Ret \mathbb{C}_L

i \leftarrow i + 1; \mathcal{U}[i] \leftarrow \mathbb{C}_P

else //make arbitary chip

Return i

\langle C_N, \gamma \rangle \leftarrow Z

\mathbb{C}_N \leftarrow \$ Fab(C_N, \gamma)

\mathcal{N} \leftarrow \mathcal{N} \cup \{\mathbb{C}_N\}

Ret \mathbb{C}

```

Figure 2: Experiments for function-recovery (FR) and key-recovery (KR) notions for DH scheme  $\Pi = (Hide, Restore)$ , given  $\mathcal{F} \subseteq \operatorname{Func}(n, m)$  and design parameters  $\theta$ , when chips are fabricated according to Fab.

unrestricted access to the opaque circuit, as this is something that a real foundry would receive in order to carry out fabrication. It is also given oracles that capture various capabilities that a foundry is likely to have.

Function recovery. We begin with a notion of function recovery for a design-hiding scheme  $\Pi = (Hide, Restore)$ . The pseudocode for the FR experiment is given in Figure 2. The experiment is parameterized by the DH scheme  $\Pi$ , some design parameters  $\theta$  that  $\Pi$  uses, and an honest chip-fabrication algorithm Fab. It takes as inputs: an adversary's attack algorithm A, and a set  $\mathcal{F} \subseteq \operatorname{Func}(n,m)$ . Intuitively, the set  $\mathcal{F}$  captures the a priori uncertainty/knowledge that the adversary has about the function F that the DH scheme  $\Pi$  is used to protect. Clearly, there must be some uncertainty, since otherwise, the adversary already knows the functionality of the IP author's circuit design. Note that the design of  $\Pi$  does not depend on  $\mathcal{F}$ .

The experiment begins by sampling F uniformly from  $\mathcal{F}$ . A circuit  $C_F$  (that implements F) and the design parameters  $\theta$  are inputs to the hiding algorithm  $\mathit{Hide}$ , which returns the key  $K_O$ , and the opaque circuit  $C_L$ . The adversary is given  $C_L$  and  $\theta$  as inputs, and it is provided oracles named FAB, RESTORE, and RUN. These oracles model processes that an adversarial foundry can employ while trying to recover F.

When the foundry is *honest-but-curious*, it will *only* produce chips that are fabricated from the opaque circuit that the IP author generates using the DH scheme  $\Pi$ , and the design parameters  $\theta$ . In the *fully-malicious* setting, the adversary can produce any *arbitrary* chip using arbitrary circuits and arbitrary design parameters.

For our security experiments, we define an honest-but-curious adversary as one that *always* queries FAB with zero arguments, i.e.,  $Z = \varepsilon$ . On the other hand, a fully-malicious adversary can call FAB with any circuit  $C_N$ , and any design parameters  $\gamma$  of its choice, i.e.,  $Z = (C_N, \gamma)$ .

When  $Z=\varepsilon$ , the FAB oracle runs Fab with  $C_L$  (generated in the FR experiment) and  $\theta$  as inputs to get an honest chip  $\mathbb{C}_L$ . Otherwise, FAB parses Z to get  $(C_N,\gamma)$  and runs the Fab algorithm on  $(C_N,\gamma)$  to get an arbitrary chip  $\mathbb{C}_N$  of the adversary's choice. We use the sets  $\mathcal{H}$  and  $\mathcal{N}$  to keep track of the honest and arbitrary chips, respectively.

The RESTORE oracle models the adversary's ability to obtain honestly-restored chips, i.e., chips that are restored with the secret key  $K_O$ . We allow the adversary to query RESTORE on any chip that it obtained from FAB, i.e., chips in set  $\mathcal{H} \cup \mathcal{N}$ . We use  $\mathcal{U}$  to keep track of honestly-restored

chips. The RESTORE oracle does not return the restored chips in order to prevent the adversary from reading the secret key from the description of the chip. Instead, we return the index of the restored chip in  $\mathcal{U}$ . Notice that we do not restrict the adversary to run the deterministic *Restore* algorithm *locally* on any triple  $(K, \gamma, \mathbb{C}_N)$  of its choice.

The RUN oracle captures the foundry's ability to see the output of any honestly-restored chip  $\mathbb{C}_P$  (that is stored in  $\mathcal{U}$ ) on any input of its choice. The oracle takes as input the index j of  $\mathbb{C}_P$  in  $\mathcal{U}$  and  $X \in \{0,1\}^n$ , and returns the value P(X). (By notation,  $\mathbb{C}_P$  implements function P.)

The goal of the adversary in the FR experiment is to output a chip  $\mathbb{C}_G$  as its guess for F. The adversary is said to win the FR experiment if  $F \equiv G$ . Notice that we prevent trivial wins — by returning honestly-restored (honestly-fabricated) chips — by not allowing the adversary direct access to chips that are restored by the RESTORE oracle.

We define the FR advantage of the pair  $(\mathcal{F}, A)$  against DH scheme  $\Pi$ , design parameters  $\theta$ , and honest-fabrication algorithm Fab to be

$$\mathbf{Adv}^{\mathrm{FR}}_{(\Pi,\theta),\mathit{Fab}}(\mathcal{F},A) = \Pr\Big[ \operatorname{\mathbf{Exp}}^{\mathrm{FR}}_{(\Pi,\theta),\mathit{Fab}}(\mathcal{F},A) = 1 \, \Big],$$

where the probability is over the indicated experiment. We say A is  $(t,q_f,q_s,q_r)$ -resource when its time complexity is t, and it makes  $q_f$  queries to the FAB oracle,  $q_s$  queries to the RUN oracle. By convention, an FR adversary does not make pointless queries to any oracle, i.e. queries that cannot increase its advantage.

**Key recovery.** The notion of key recovery (KR) is similar to the FR notion, except the adversary's goal is to recover a key K, and the key is then used to get an honestly restored chip  $\mathbb{C}_G$  that is obtained by running the honest Fab algorithm on  $(C_L, \theta)$ . In the final step of the KR notion, we check whether the function G that the chip  $\mathbb{C}_G$  implements is functionally equivalent to F. We define the KR advantage of A as

$$\mathbf{Adv}^{KR}_{(\Pi,\theta),\mathit{Fab}}(\mathcal{F},A) = \Pr\Big[ \operatorname{\mathbf{Exp}}^{KR}_{(\Pi,\theta),\mathit{Fab}}(\mathcal{F},A) = 1 \, \Big],$$

where the probability is over the indicated experiment. The resources are the same as those for the FR advantage.

Note that one might think it more natural to define key recovery as determining *the* secret key  $K_O$ . We define it as we do because some of the existing DH schemes, including RLL [RKM08] and strong logic obfuscation (SLO) [RPSK12a], admit multiple keys  $K \in \{0,1\}^{k_o(\theta)}$  that map to the hidden function F, i.e.,  $F \equiv Restore(K_O, \theta, \mathbb{C}_L) \equiv Restore(K, \theta, \mathbb{C}_L)$ . (These keys are said to constitute an equivalence class of the hidden function.) Thus, our KR notion captures (for example) the SAT attack of Subramanyan et. al [SRM15], which recovers some key in the equivalence class of the hidden function. It also captures other key-recovery attacks [XSTF17, YMSR17a, SS19] that exploit structural and functional characteristics of the opaque circuit.

It is intuitively clear that FR security implies KR security for any design-hiding scheme. We formalize this relation in Theorem 1.

**Theorem 1.** Fix integers n, m > 0,  $\mathcal{F} \subseteq \operatorname{Func}(n, m)$ , and design parameters  $\theta$  for a DH scheme  $\Pi = (\operatorname{Hide}, \operatorname{Restore})$ . Let Fab be honest. For any KR-adversary A, there is an FR-adversary B such that

$$\mathbf{Adv}^{\mathrm{KR}}_{(\Pi,\theta),\mathit{Fab}}(\mathcal{F},A) \leq \mathbf{Adv}^{\mathrm{FR}}_{(\Pi,\theta),\mathit{Fab}}(\mathcal{F},B).$$

Here, A is

$$(t, q_f, q_s, q_r)$$

-resource where  $t = O(q_f + q_s + q_r)$ , and B is  $(O(t), O(q_f), O(q_s), O(q_r))$  resource.

The proof of this theorem is straightforward. Given the KR-adversary A guesses K, the FR adversary B can generate  $\mathbb{C}_G$  by fixing the  $k_o(\theta)$  input bits in the opaque circuit  $C_L$  with K (using the deterministic algorithm Restore), and then using Fab to fabricate the restored circuit. With  $\mathbb{C}_G$ , B wins the FR experiment with probability no less than the probability with which A wins the KR experiment.

| Experiment $\widetilde{\mathbf{FR}}_{(\Pi,\theta)}(\mathcal{F},B)$ | oracle $TRUE(X)$ : |

|--------------------------------------------------------------------|--------------------|

| $F \leftarrow \mathcal{F}$                                         | Ret $F(X)$         |

| $(K_O, C_L) \leftarrow \$ Hide(C_F, \theta)$                       |                    |

| $C_G \leftarrow B^{TRUE}(C_L, \theta)$                             |                    |

| $Ret [G \equiv F]$                                                 |                    |

Figure 3: FR-game in the honest-but-curious setting. All three oracles in the original FR-security experiment are replaced with TRUE.

The converse, i.e., KR security implies FR security, is not true. Consider that the opaque circuit that the hiding algorithm outputs is an encoding of the original circuit, and the secret key is sampled uniformly at random from  $\{0,1\}^{128}$ . While admittedly pathological, this example suffices to make the point.

Simplified FR-notion in the honest-but-curious setting. Recall that in the security experiments, the goal of the adversary is to recover the full-functionality of F. In the honest-but-curious setting, the foundry effectively will have oracle access to F and unrestricted access to F. (We discuss the fully-malicious setting in Section A.3.) Let's see this in the context of the FR-security definition.

Let  $C_L$  be the opaque circuit that the IP author generates using  $\mathit{Hide}$ . In the honest-but-curious setting, the foundry uses  $\mathit{Fab}$  honestly. By definition of honest  $\mathit{Fab}$ , any opaque chip that  $\mathit{Fab}$  produces will implement L. Thus, running (the deterministic)  $\mathit{Restore}$  algorithm on the honestly-fabricated opaque chips with  $K_O$  will result in chips with identical functionalities. Since the adversary gains no additional information about F from multiple queries to the oracles FAB and RESTORE, we can fix  $q_f = 1$  and  $q_s = 1$ , where the only (useful) query that A makes to FAB is  $\hat{Z} = \langle C_L, \theta \rangle$ , and the only (useful) query that A makes to RESTORE is  $\widehat{\mathbb{C}}_L = \mathit{Fab}(\hat{Z})$ . Notice that this results in  $\mathcal{U}$  to store a single restored chip  $\mathbb{C}_F = \mathit{Restore}(K_O, \theta, \widehat{\mathbb{C}}_L)$  at index one. Using its  $q_r$  queries  $(1, X_i)$  to RUN oracle, the adversary will learn  $q_r$  pairs  $(X_i, F(X_i))$ . Thus, in the honest-but-curious setting, we can replace all the oracles with a single TRUE oracle, that takes  $X_i$  as input and returns  $F(X_i)$ . We show these changes in the security experiment  $\widehat{FR}_{(\Pi,\theta)}(\mathcal{F},B)$ ; See Figure 3.

Notice that the changes are all either syntactic (i.e., no change to the advantage) or conservative (i.e., cannot decrease advantage) with respect to the original FR experiment. This observation gives rise to the following simple, but useful lemma.

**Lemma 1.** Fix DH scheme  $\Pi$  and parameters  $\theta$ . For every honest-but-curious FR-adversary A that is  $(t, q_f, q_s, q)$ -resource, there exists a closely related adversary B such that

$$\Pr\left[\mathbf{Exp}_{(\Pi,\theta),\mathit{Fab}}^{\mathrm{FR}}(\mathcal{F},A) = 1\right] \leq \Pr\left[\widetilde{\mathbf{FR}}_{\Pi,\theta}(\mathcal{F},B) = 1\right]$$

where B makes at most q queries to TRUE (see Figure 3), and runs in time O(t).

As discussed in Section A.2, almost all existing DH schemes [RKM08, BTZ10, RPSK12a, RPSK12b, DBDN<sup>+</sup>14, XS16, YMRS16, YSS<sup>+</sup>17, SLM<sup>+</sup>17b, YSN<sup>+</sup>17] have been shown to be KR-insecure, i.e., these schemes have large (close to one) KR advantage due to various key-recovery attacks [SRM15, XSTF17, SZ17, SRZ18, YMSR17a, SLM<sup>+</sup>17a, SLR<sup>+</sup>19, ZJK17, Che18, SS19, YTS19]. Per our Theorem 1, if a DH scheme is KR-insecure, then it is also FR-insecure, i.e., large FR advantage. The few (recent) schemes [RMKS18, KAHS19] that have not been shown to be broken were designed specifically to thwart SAT attack. In order to prove FR-security, we need to show that a DH scheme thwarts *all* FR-attacks — not specific KR-attacks. In the next section, we will construct an FR-secure DH scheme.

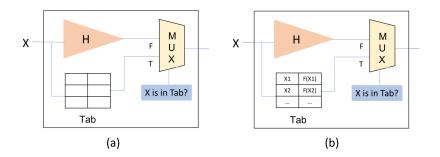

Figure 4: a) An opaque circuit generated by any OneChaff scheme. b) An honestly-fabricated-and-restored chip. Adversary gets unrestricted access to (a) and oracle access to (b).

# 6 A Framework for Designing FR-Secure DH Schemes

In the FR-security experiment as well as in  $\widehat{FR}$ , the adversary's guess space is the set  $\mathcal{F} \subseteq \operatorname{Func}(n,m)$  before it gets full access to the opaque circuit. As the adversary learns new information via its unrestricted access to the opaque circuit  $C_L$  and oracle access to F, it can prune its guess space to a smaller set  $\mathcal{M}_1 \subseteq \mathcal{F}$  of functions. Let  $\mathcal{D}_1$  be the probability distribution of  $\mathcal{M}_1$ . Then, the probability that B wins  $\widehat{FR}$  will be upperbounded by  $2^{-H_\infty(\mathcal{D}_1)}$ , where  $H_\infty(\mathcal{D}_1)$  is the min-entropy of  $\mathcal{D}_1$ . In this section, we will describe a framework that an IP author can use to build a DH scheme (with formal descriptions of Hide and Restore) such that it can concretely define the distribution  $\mathcal{D}_1$ , and find concrete FR-security guarantees of its construction.

Abstractly, the opaque chip  $\mathbb{C}_L$  can be viewed as a circuit that encodes a set  $\mathcal{R}_L\subseteq \operatorname{Func}(n,m)$  of n-bit to m-bit functions (not necessarily distinct) that are selected by  $\operatorname{Hide}$  (either implicitly or explicitly), and each key K in set  $K=\{0,1\}^{k_o(\theta)}$  is associated with some function in  $\mathcal{R}_L$ . Minimally, correctness will require that the hiding key  $K_O$  is associated with the true function F. We define a chaff function  $H\in\operatorname{Func}(n,m)$  as one that is not functionally equivalent to F; we refer to the inputs on which H differs (in output) from F as "distinguishing" inputs.

In our framework, we insist that the set  $\mathcal{R}_L$  be "extractable" from the opaque circuit, i.e., given  $C_L$  and the description of Hide, the IP author knows the full-functionality of each function in  $\mathcal{R}_L$ . This is a reasonable assumption as during the design of circuit, the functionality of a circuit is fixed first as part of the system specification and architectural design, and then the topology of the circuit is decided. In RLL [RKM08] and its variants [RPSK12a, RPSK12b, DBDN+14, KAHS19, RMKS18], the functionality of the chaff functions is *not* decided during the design of Hide. Rather, the chaff functions are an artifact of random structural modifications — the positions of key gates in the original circuit. So, for a non-pathological circuit, i.e., circuits with sufficiently complex functionality and reasonably large domain, it is almost impossible to extract the functionality of the chaff functions. Consequently, it is difficult to evaluate the FR security of such schemes in our framework. As mentioned earlier, RLL and its variants (designed before SAT attack) as well as SAT-attack-resistant schemes [XS16, YMRS16, YSS+17, SLM+17b, YSN+17] (designed post SAT attack) are FR-insecure due to various key-recovery attacks [SRM15, XSTF17, SZ17, SRZ18, YMSR17a, SLM+17a, SLR+19, ZJK17, Che18, SS19, YTS19].

#### 6.1 OneChaff: a family of DH schemes

We present a family of DH schemes called *OneChaff* with the following common features:

• the design-hiding algorithm returns an opaque circuit that contains the circuit of a single *chaff* H with  $\Delta \in \mathbb{N}$  distinguishing inputs and an uninitialized lookup table (see Figure 4(a)) that is used for restoring the functionality of the hidden function;

- the hiding key encodes the set of distinguishing inputs and the correct value of the hidden function on the distinguishing inputs;

- the design-restoring algorithm, in an honest run, initializes the lookup table with the hiding key (see Figure 4(b)).

Notice that the description of OneChaff leaves H unspecified; specific OneChaff schemes will define H explicitly.

The opaque circuit that OneChaff generates consists of: the circuit of a single Boolean function, and a lookup table that is effectively a restore unit. Structurally, this is similar to the opaque circuits that SAT-attack-resistant DH schemes [XS16, YMRS16, YSS+17, YSN+17] generate. However, the functionalities of the Boolean function and the restore unit are different across schemes. In SFLL-HD [YSN+17] and TTLock [YSS+17], the encoded Boolean function H is such that its functionality differs from F only on non-key inputs  $X_i$  that are at a hamming-distance of h (in SFLL-HD,  $0 \le h \le 2^n$ ; in TTLock, h = 0) from the correct key  $K_O$ ; on the remaining inputs, H and H have identical functionalities. In AntiSAT [XS16] and SARLock [YMRS16], the original function H is encoded in the opaque circuit with the assumption that the circuit-synthesis tools will "meld" the functionalities of H and the restore unit —a comparator that checks whether the key-input to the opaque circuit is identical to the hard-coded correct key H0- in such a way that the adversary will not be able to locate H1.

Several key-recovery attacks [SS19, YMSR17a, YTS19, YMSR17b] have exploited structural as well as functional weaknesses in the opaque circuits that the SAT-attack-resistant DH schemes [XS16, YMRS16, YSS+17, YSN+17] generate to recover the correct key (and hence the entire functionality of the original circuit). In our construction *OneChaff*<sub>hd</sub>, which we describe next, we chose the functionality of the Boolean function and the restore unit in such a way that we can prove its security for a wide class of functions against all attacks admissible in the standard threat model of logic-locking.

Let

$$\theta = (n, m, \Delta)$$

, where  $n, m > 0$ , and  $\Delta \in [2^n - 1]$ .

**Description of Hide.** Given F, the Hide algorithm in  $OneChaff_{\mathrm{hd}}$  selects F as the anchor function and samples a single chaff uniformly from its  $\Delta$ -neighborhood, i.e.,  $H \leftarrow N_{\Delta}(F)$ . Equivalently, the chaff H is initialized to F and then, on a random subset  $\mathcal{I}^{\neq}(F,H) = \{X_1,X_2,\ldots,X_{\Delta}\}$  of the domain of F, the value of  $H(X_i) \leftarrow \{0,1\}^m \setminus \{F(X_i)\}$ ; when M = 1,  $M(X_i) \leftarrow P(X_i)$ .

Formally, the opaque circuit  $C_L$  returned by *Hide* computes the function  $L: (\{0,1\}^n \cup \{\{\}\})^\Delta \times (\{0,1\}^m \cup \{\{\}\})^\Delta \times \{0,1\}^n \to \{0,1\}^m$  defined by

$$L\left(\left((U_1,V_1),(U_2,V_2),\ldots,(U_{\Delta},V_{\Delta})\right),X\right) = \begin{cases} V_i & \text{if } \exists U_i = X \\ H(X) & \text{otherwise} \end{cases}$$

where the distinguished (non-string) symbol  $\xi$  is understood to mean "uninitialized". We implicitly assume that all string-valued  $U_i$  are distinct so that L is well defined, and that if any  $U_i = \xi$ , then all  $U_i = \xi$ . Thus, L computes H and a family of functions  $\mathcal{R}_L = N_\Delta(H)$ , one of which is F.

In practice, we envision  $C_L$  to be a circuit that encodes H and an uninitialized table Tab, whose gate-and-wire representation allows for a sub-circuit  $C_H$  (computing H) to be easily parsed out; overloading the  $\langle \cdot \rangle$  notation, we will sometimes write  $C_L = \langle H, \operatorname{Tab} \rangle$  to reflect this. This way, one can evaluate  $C_H$  given  $C_L$  and, by loading  $\operatorname{Tab}$  in  $C_L$  with a list of  $\Delta$  pairs in  $\{0,1\}^n \times \{0,1\}^m$ , any of the functions in  $N_{\Delta}(H)$ .

**Description of** *Restore*. The *Restore* algorithm parses the input (design) parameters  $\theta$  to determine  $n, m, \Delta$ . It then expects a key  $K = \langle (U_1, V_1), \ldots, (U_\Delta, V_\Delta) \rangle$  where each  $(U_i, V_i) \in \{0, 1\}^n \times \{0, 1\}^m$ , and a chip  $\mathbb{C}_L$  that was fabricated from a circuit  $C_L = \langle H, \widetilde{\text{Tab}} \rangle$ . When these expectations are met, *Restore* loads the pairs  $(U_i, V_i)$  into the uninitialized lookup table. (When not, it returns  $\bot$ .) We write  $\mathbb{C}_L \uparrow K$  for this, the notation suggesting that K is "uploaded" into  $\mathbb{C}_L$ .

Thus, when provided with an honestly fabricated chip from the opaque circuit  $C_L$  returned by  $Hide(F,\theta)$ , and the corresponding key  $K_O$ , the restored chip  $\mathbb{C}_L \uparrow K_O$  properly computes the hidden function F. Note that, we abstract away the physical mechanism by which uploading the  $(U_i,V_i)$  is implemented, and assume that if this mechanism is able to detect upload failure, *Restore* returns  $\bot$ .

# 6.2 OneChaff $_{\rm hd}$ is efficient

*Hide* is efficient. Note that *Hide* in *OneChaff* $_{hd}$  is abstracting the process by which an IP author goes from the "idea" (i.e., informal specification) of a functionality F to an opaque circuit described in some format that is suitable for fabrication (e.g., a GDSII file). This process typically involves writing a program for the desired functionality in some high-level language like Verilog, and then converting the program to a circuit description by an EDA tool. In  $OneChaff_{hd}$ , this process can be augmented to sample  $\Delta$  random domain points, and incorporate these to yield a program (hence a circuit) for the chaff function H. More specifically, the IP author can follow a two-step approach in order to create H from F. Let m=1. In the first step, it creates a set of  $\Delta$  random n-bit inputs and finds the value of F on those inputs. Next, it sets the value of H on the  $\Delta$  inputs  $X_i$  to  $\neg F(X_i)$ ; on the remaining inputs H and F have identical values. Hence, runtime of Hide to create H will be  $O(n\Delta) + T(H)$ , where T(H) is the time needed to create the circuit for H. Note that the IP author would have anyways spent T(F) time to build the circuit for F in the honest setting. So, effectively, the additional runtime of *Hide* in  $OneChaff_{hd}$  is  $O(n\Delta) + T(H) - T(F)$ . (Time to create  $K_O$  will also be  $O(n\Delta)$  as  $|K_O| = n\Delta$ .) When  $\Delta \ll 2^n$ , T(H) will be roughly same as T(F). Thus, the efficiency of *Hide* should be roughly same as that of the original process, at least when  $\Delta \ll 2^n$ .

Also, note that such an implementation does not leak any additional information about F apart from H when the adversary gets full view of the opaque circuit  $\langle H, \widetilde{\mathrm{Tab}} \rangle$ .

**Restore** is efficient. Since *Restore* involves uploading the  $n\Delta$ -bits hiding key  $K_O$  to Tab, it's runtime will be  $O(n\Delta)$ .

# 6.3 FR security of OneChaff<sub>hd</sub>

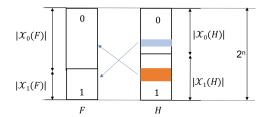

In  $\widetilde{\mathbf{FR}}$ , given unrestricted access to  $C_L = \langle H, \widetilde{\mathrm{Tab}} \rangle$ , the IP author knows that the foundry can (at best) extract the set  $\mathcal{R}_L = N_\Delta(H)$  and compute  $\mathcal{M}_0 = \mathcal{F} \cap N_\Delta(H)$  to reduce the size of its original guess space  $\mathcal{F}$ . Using queries to TRUE, the foundry can further reduce the guess space to  $\mathcal{M}_1 \subseteq \mathcal{M}_0$  by removing functions in  $\mathcal{M}_0$  whose distinguishing-input sets contain query inputs.

In practice, the IP author will not know the set  $\mathcal{F}$  because that captures the foundry's initial guess at the set of possible functions F that may be what the IP author intends to hide. (Recall that the FR-notion samples  $F \leftarrow \mathcal{F}$ , suggesting that the foundry's initial set is the correct set.) More plausibly, the author may assume that the foundry's initial guess is based upon knowledge of likely "properties" of F. These properties may be gleaned from discussions with the IP author, statements in fabrication contracts, historical and market information, etc. The IP author may use these assumed-known properties in its description of Hide, Restore, or into the parameters  $\theta$ . In particular, it can use these assume-known properties to compute its estimates of the sets  $\mathcal{M}_0$  and  $\mathcal{M}_1$  that can help the foundry reduce the guess space. We will use these observations in our upcoming analysis.

Scoping the set  $\mathcal{F}$ . In what follows, we will focus on the case that m=1, i.e.,  $\mathcal{F}\subset \operatorname{Func}(n,1)$ . We focus on Boolean functions for a few reasons. First, even if the circuit representation of the hidden function has  $n'\geq n$  bits of input and m>1 bits of output, we can take as a first consideration whether or not one can securely hide the transitive fan-in cone (TFC) of any particular output bit. For a collection of output bits that have disjoint transitive fan-in cones, one can consider hiding these in parallel.

Second, focusing on Boolean functions makes the analysis less complicated. In particular, for all distinguishing inputs  $U_i \in \mathcal{I}^{\neq}(F,H), V_i = \neg F(U_i)$ ; otherwise  $V_i \leftarrow \mathfrak{s} U_m \setminus F(U_i)$ . Note that when m>1, the TFCs of different output bits may not be disjoint. In such a case, the adversary can potentially use information it learns about one TFC to learn about the functionality of a different TFC

Third, barring SFLL-flex [YSN<sup>+</sup>17], in the remaining SAT-attack-resistant DH schemes (Anti-SAT [XS16], SARLock [YMRS16], TTLock [YSS<sup>+</sup>17] and SFLL-HD [YSN<sup>+</sup>17]), F is Boolean.

Simple functions cannot be hidden. We borrow the definition of "simple" functions from learning theory; simple functions are those that can be efficiently learned via a reasonably small number of input-output values of F. Now, if  $\mathcal{F}$  consists predominantly of simple functions, then *no* DH scheme will be secure<sup>4</sup> in hiding functions sampled from  $\mathcal{F}$ . For example, functions that have a small domain can be learned by brute force. In addition, results from computational learning theory tell us that functions whose decision-tree representation have small depth/size can be learned via the Kushilevitz-Mansour algorithm [KM93]. More generally, methods exist to (approximately) learn Boolean functions whose Fourier spectra are sparse (e.g., dominated by relatively few Fourier coefficients) [GOS<sup>+</sup>11].

To loosely capture a measure of the density of "simple" Boolean functions within a given set  $\mathcal{F}$ , we give the following definition.

**Definition 3.** ["Simple" functions in  $\mathcal{F}$ .] Let  $\mathcal{F} \subseteq \operatorname{Func}(n,1)$  be a set of Boolean functions. Let  $t,q\geq 0$  be integers, and let  $\delta\in[0,1]$  be a real number. Let  $\mathcal{F}_{t,q,\delta}\subseteq\mathcal{F}$  be a subset such that the following holds:  $\exists$  a q-query, t-time adversary A such that,  $\forall f\in\mathcal{F}_{t,q,\delta}$ , when  $g\leftarrow A^{f(\cdot)}$  we have  $\Pr[x\leftarrow \{0,1\}^n:g(x)=f(x)]\geq \delta$ . Furthermore, define  $\epsilon_{t,q,\delta}=|\mathcal{F}_{t,q,\delta}|/|\mathcal{F}|$ . In particular,  $\epsilon_{t,q,1}$  is the fraction of  $\mathcal{F}$  that can be exactly learned (by some A) with q input-output values and time-complexity t.

Our security bounds for  $\mathit{OneChaff}_{hd}$  will reflect the term  $\epsilon_{t,q,1}$ , although we stress that corresponding bounds for any DH scheme would also have to reflect this term (perhaps not explicitly) because any "simple" function will not be hideable.

In general, specifying a set  $\mathcal{F}$  for which  $\epsilon_{t,q,1}$  is small enough for practically meaningful security statements (for reasonable t,q) is challenging, as this would require results of the following kind: There exist no adversary that can learn any function in  $\mathcal{F} \setminus \mathcal{F}_{t,q,1}$  with q queries in time t. We are not aware of any such results. Also, note that it is not sufficient for  $\mathcal{F}$  to be large (although it is necessary to avoid simply guessing F), as one can specify large sets of functions with sparse Fourier spectra.

We conjecture that if  $\mathcal F$  is sufficiently "unstructured", then  $\epsilon_{t,q,1}$  will be small enough to not dominate the FR-security bounds we will prove, for practically reasonable t,q. For example, a random Boolean function lacks the highly concentrated spectral structure — the number of non-zero Fourier coefficients is  $(1-o(1))2^n$  [DW08] — that leads to efficient learnability from input-output pairs.

Under the above conjecture, we will focus on  $\mathcal{F}=\mathcal{F}_{[h_0,h_1]}\subseteq \mathsf{Func}(n,1)$  that consists of all Boolean functions with hamming weight at least  $h_0$  and at most  $h_1$ . Recall that the set  $\mathcal{F}$  in our FR experiment is meant to reflect the adversary's a priori "knowledge" about the function hidden in the opaque circuit, and that our FR-notion samples F uniformly from  $\mathcal{F}$ . At the extremes, setting  $h_0=0, h_1=2^n$  considers the case that the adversary has no a priori knowledge; setting  $h_0=h_1$  considers an adversary that knows exactly the hamming weight of the hidden function F. In our analysis of  $OneChaff_{\mathrm{hd}}$ , we will conservatively assume the latter.

A random Boolean function has an expected hamming weight close to  $2^{n-1}$ . Hence, when  $\mathcal{F}$  comprises functions with hamming weights close to  $2^{n-1}$ , then a randomly sampled function from  $\mathcal{F}$  is unlikely to be easily learned (i.e., "simple") given the current state of the art, and will have very

<sup>&</sup>lt;sup>4</sup>Shamsi et al. [SPJ19] made a similar observation and gave impossibility results on logic locking when  $\mathcal{F}$  consists of entirely simple functions. Our security experiments are more generic as they allow  $\mathcal{F}$  to contain functions of varying degrees of "simplicity".

small  $\epsilon_{t,q,1}$ . We conjecture this based on the fact that a random Boolean function almost certainly does not have a concentrated Fourier spectrum [DW08] thereby making efficient learning-theoretic attacks out-of-scope.

A practical warm-up: FR security with  $\mathbf{q}=\mathbf{0}$ . Chips that are used in critical infrastructure (e.g., military devices) will most likely require considerable effort to obtain. In this case, we can assume that the foundry cannot get access to honestly restored chips, and thereby learn the true input-output behavior of F on inputs of its choice. Thus, we begin our analysis of  $OneChaff_{hd}$  for  $\mathcal{F}_{[h,h]}$  in the q=0 case.

Given Lemma 1, recall that we were left to find an upper bound on  $\Pr\left[\widetilde{\mathbf{FR}}(B) = 1\right]$ , where B has some time-complexity t and asks q queries to its TRUE oracle. Let us fix q = 0, and consider an arbitrary adversary  $B_0$  with these resource bounds.

Recalling the notation that  $\mathcal{R}_L$  is the set of functions realizable by the opaque circuit  $L=\langle H, \mathrm{Tab} \rangle$ , we have  $\mathcal{R}_L=N_\Delta(H); F\in \mathcal{R}_L$ . The adversary  $B_0$  knows a priori that  $F\in \mathcal{F}_{[h,h]}$ . Hence, for all  $\hat{F}\in \mathcal{R}_L$ ,  $\mathrm{hw}(\hat{F})\in [\mathrm{hw}(H)-\Delta,\mathrm{hw}(H)+\Delta]$ . To get an intuition of the claim on  $\mathrm{hw}(\hat{F})$ , consider two cases:  $\mathrm{hw}(H)=0$  and  $\mathrm{hw}(H)=2^n$ . When  $\mathrm{hw}(H)=0$ ,  $\mathrm{hw}(\hat{F})=\mathrm{hw}(H)+\Delta=\Delta$ ; when  $\mathrm{hw}(H)=2^n$ ,  $\mathrm{hw}(\hat{F})=\mathrm{hw}(H)-\Delta=2^n-\Delta$ .

While attacking  $\mathit{OneChaff}_{\mathrm{hd}}$ , the optimal strategy for  $B_0$  is to return the circuit implementation of the most-likely function in  $\mathcal{F}_{[h,h]} \cap \mathcal{R}_L$ . (We will use  $\mathcal{F}_{[h,h]}^j$ ,  $\mathcal{R}_L^j$  to denote the subset of functions in  $\mathcal{F}_{[h,h]}$  and  $\mathcal{R}_L$ , respectively, that have correct values on some  $0 \leq j \leq q$  inputs.) But as sampling is done in a uniform and independent fashion in  $\widetilde{\mathbf{FR}}$ , all functions in  $\mathcal{M}_0 = \left(\mathcal{F}_{[h,h]}^0 \cap \mathcal{R}_L^0\right)$  are equally likely. Then,  $\Pr\left[\widetilde{\mathbf{FR}}(B_0) = 1\right] = |\mathcal{M}_0|^{-1}$ . We will proceed to give a lowerbound on  $|\mathcal{M}_0|$  in the q = 0 case.

**Claim 1.** Let  $hw(H) = h + \alpha$ , where  $\alpha < (2^{n-1} - h)$ , and  $\Delta < h$ . Then,

$$|\mathcal{M}_0| = \left| \left( \mathcal{F}^0_{[h,h]} \cap \mathcal{R}^0_L \right) \right| = \binom{h+\alpha}{(\Delta+\alpha)/2} \binom{2^n-h-\alpha}{(\Delta-\alpha)/2}.$$

When  $\Delta < h$  and  $\operatorname{hw}(H) < 2^{n-1}$ , we found (in the proof of Claim 1) that *more than half*  $(\Delta/2 + \alpha/2)$  of the distinguishing inputs will belong to  $\mathcal{X}_1(H)$ . Hence, we can assume, without any loss in the FR advantage of the adversary, that the adversary will make all of its queries from  $\mathcal{X}_1(H)$  until it finds all  $(\Delta + \alpha)/2$  distinguishing inputs in  $\mathcal{X}_1(H)$ . (Later, we will show that when  $q < \min(\operatorname{hw}(H)/4, \Delta^2/64 \ln n)$ , the adversary can find *at most* half of the distinguishing inputs in  $\mathcal{X}_1(H)$ , without loss.)

The lower bound on  $|\mathcal{M}_0|$  in Claim 1, a function of hw(H) as  $\alpha = (h - hw(H))$ , gives us an upper bound on the FR advantage of adversary that attacks  $OneChaff_{hd}$  without making any queries to any of the three oracles. But, hw(H) is not a parameter of the FR-security experiment. In the next claim, we give a lower bound on the hamming weight of H using the Hoeffding lemma; the bound is a function of h,  $\Delta$  and n and all three are parameters of the FR experiment.

**Claim 2.** Let

$$\Delta < h$$

and  $0 < (\Delta + h) < 2^{n-1}$ . Then,  $hw(H) \ge h + \Delta(1 - h/2^{n-1})$ , with probability at least  $(1 - 1/\Delta^2)$ .

We will assume that the bound on  $\mathrm{hw}(H)$  is tight and we will reflect the uncertainty in the claim/theorem statements.

Now, we are ready to give the upper bound on the FR advantage of adversary A in the zero-query setting. We use the standard relation  $\binom{p}{r} \geq (p/r)^r$  in the bound in Claim 1 to make the final bound in Theorem 2 easier to interpret. We also use the weaker bound  $\mathrm{hw}(H) > h$  (instead of the tighter bound in Claim 2) to make the final bound even more interpretable. Note that practical  $\mathit{OneChaff}_{\mathrm{hd}}$  schemes will have  $\Delta \ll 2^{n-1}$  as the run time of  $\mathit{Hide}$  as well as  $\mathit{Restore}$  will be linear

٠

in  $\Delta$ . Thus, the loss in using hw(H) > h instead of  $hw(H) \ge h + \Delta(1 - h/2^{(n-1)})$  will not be significantly large.

**Theorem 2.** Fix m=1 and integers  $n,h,\Delta>0$  such that  $\Delta< h$ , and  $\Delta+h<2^{(n-1)}$ . Let  $\epsilon_{t,0,1}$  be as defined in Definition 3. When an honest-but-curious adversary A attacks the FR security of  $\Pi=OneChaff_{hd}$  without making any queries to any oracle, then, it achieves

$$\mathbf{Adv}^{\mathrm{FR}}_{(\Pi,\theta),\mathit{Fab}}(\mathcal{F}_{[h,h]},A) \leq \left(\frac{\Delta^2}{2^n h}\right)^{\Delta/2} + \epsilon_{t,0,1},$$

with probability at least  $(1 - 1/\Delta^2)$ .

In the next section, we will see that when we account for the adversary's access to the oracles, more specifically, the TRUE oracle, the upper bound on the FR advantage will be  $\left(\frac{\Delta^2}{2^n \cdot (h-q)}\right)^{\Delta/4} + \epsilon_{t,q,1}$ . Observe that the queries to TRUE increase the FR advantage of an adversary significantly (compared to the zero-query setting) as the exponent  $\Delta/2$  decreases to  $\Delta/4$ ; the denominator also is smaller compared to the zero-query setting. Since the first term is very similar to the bound in Theorem 3, we defer the unpacking of Theorem 2 to the next section.

FR analysis of OneChaff $_{\mathrm{hd}}$  with  $\mathbf{q}>\mathbf{0}$ . The ability to learn true input-output pairs, via queries to TRUE, provide a way for the adversary to verify guesses at portions of the key  $K_O$ . Recall that the key encodes  $(X_1,F(X_1)),\ldots,(X_\Delta,F(X_\Delta))$  for  $X_i\in\mathcal{I}^{\neq}(F,H)$ , and the opaque circuit  $C_L$  allows for local computation of H(X). Thus, as a first step in analyzing the FR security of  $\mathit{OneChaff}_{\mathrm{hd}}$  in the q>0 case, we derive a bound on the number of points in  $\mathcal{I}^{\neq}(F,H)$  that an adversary uncovers in its q queries to the TRUE oracle.

Let  $\mathcal{Q}_j = \{x_1, x_2, \dots, x_j\}$  be the first j queries to TRUE, and let random variable  $\mathcal{Q}_j^{\text{key}} = \mathcal{Q}_j \cap \mathcal{I}^{\neq}(F, H)$  denote the queries in  $\mathcal{Q}_j$  that uncover a portion of the distinguishing inputs. Observe that  $|\mathcal{Q}_0^{\text{key}}| = 0$ , and for j > 0 the value of  $|\mathcal{Q}_j^{\text{key}}|$  depends only upon  $|\mathcal{Q}_{j-1}^{\text{key}}|$  and the query  $x_j$ ; in particular that  $|\mathcal{Q}_j^{\text{key}}| = |\mathcal{Q}_{j-1}^{\text{key}}| + 1$  if  $x_j \in \mathcal{I}^{\neq}(F, H)$ , and  $|\mathcal{Q}_j^{\text{key}}| = |\mathcal{Q}_{j-1}^{\text{key}}|$  if not.

Let  $I_j$  be the indicator random variable indicating that the event  $x_j \in \mathcal{Q}_j^{\text{key}}$  occurs. We claim that  $\Pr[I_j = 1] = (\Delta - |\mathcal{Q}_{j-1}^{\text{key}}|) / (\text{hw}(H) - (j-1))$ . To see this, observe that the number of uncovered points in  $\mathcal{I}^{\neq}(F,H)$  is precisely  $(\Delta - |\mathcal{Q}_{j-1}^{\text{key}}|)$  and, given how those points were sampled, any of the remaining, unqueried points in  $\mathcal{X}_1(H)$  are equally likely to be in  $\mathcal{I}^{\neq}(F,H)$ . Given this, we can prove the following lemma.

**Lemma 2.** Let

$$\Delta < h$$

and  $(\Delta + h) < 2^{n-1}$ . Then, we have  $\mathbb{E}\left[|\mathcal{Q}_q^{\text{key}}|\right] = \frac{q\Delta}{hw(H)}$ , and,  $|\mathcal{Q}_q^{\text{key}}| < \mathbb{E}\left[|\mathcal{Q}_q^{\text{key}}|\right] + \sqrt{4q\ln\Delta}$  with probability at least  $1 - (2/\Delta^2)$ .

Notice that when  $q<\Delta^2/(256\ln\Delta),\,\sqrt{4q\ln\Delta}<\Delta/8;$  when  $q<\mathrm{hw}(H)/8,\,q\Delta/\mathrm{hw}(H)<\Delta/8.$  Thus, with probability  $1-(2/\Delta^2)$ , the adversary will uncover *no more than* quarter of the distinguishing inputs in  $\mathcal{I}^{\neq}(F,H)$  when  $q<\min(\mathrm{hw}(H)/8,\Delta^2/(256ln\Delta)).$

The adversary can increase its FR advantage by removing functions from  $\left(\mathcal{F}_{[h,h]}^0\cap\mathcal{R}_L^0\right)$  that are not correct on any input in  $\mathcal{Q}_q^{\text{key}}$ . In fact, it can remove all functions that do not agree with F on any point in the query set  $\mathcal{Q}_q$ .