## Polynomial multiplication on embedded vector architectures

Hanno Becker<sup>1</sup>, Jose Maria Bermudo Mera<sup>2</sup>, Angshuman Karmakar<sup>2</sup>, Joseph Yiu<sup>1</sup> and Ingrid Verbauwhede<sup>2</sup>

Arm Ltd, Cambridge, UK, {firstname.lastname}@arm.com

imec-COSIC, KU Leuven Kasteelpark Arenberg 10, Bus 2452, B-3001 Leuven-Heverlee, Belgium {firstname.lastname}@esat.kuleuven.be

Abstract. High-degree, low-precision polynomial arithmetic is a fundamental computational primitive underlying structured lattice based cryptography. Its algorithmic properties and suitability for implementation on different compute platforms is an active area of research, and this article contributes to this line of work: Firstly, we present memory-efficiency and performance improvements for the Toom-Cook/Karatsuba polynomial multiplication strategy. Secondly, we provide implementations of those improvements on Arm<sup>®</sup> Cortex<sup>®</sup>-M4 CPU, as well as the newer Cortex-M55 processor, the first M-profile core implementing the M-profile Vector Extension (MVE), also known as Arm<sup>®</sup> Helium<sup>™</sup> technology. We also implement the Number Theoretic Transform (NTT) on the Cortex-M55 processor. We show that despite being singleissue, in-order and offering only 8 vector registers compared to 32 on A-profile SIMD architectures like Arm<sup>®</sup> Neon<sup>™</sup> technology and the Scalable Vector Extension (SVE), by careful register management and instruction scheduling, we can obtain a 3× to 5× performance improvement over already highly optimized implementations on Cortex-M4, while maintaining a low area and energy profile necessary for use in embedded market. Finally, as a real-world application we integrate our multiplication techniques to post-quantum key-encapsulation mechanism Saber.

**Keywords:** Post-Quantum Cryptography · Polynomial multiplication · IoT · Cortex-M55 · Cortex-M4 · M-profile Vector Extension (MVE) · Helium vector extension · Number Theoretic Transform (NTT) · Toom-Cook · Karatsuba

## 1 Introduction

The rapidly expanding Internet of things (IoT) has an unprecedented impact on our digital ecosystem, so much that it is often termed the fourth industrial revolution. However, it also poses significant challenges. Firstly (sadly, often rather lastly), security: Absence or insufficient quality of security measures on IoT devices is a frequent headline. Secondly, performance: Embedded devices have much less compute resources than high-end consumer devices such as mobile phones or desktops. The dichotomy of the situation is that tight resource constraints need to be imposed on these devices to allow them to be cost-effective, but equally they limit performance and, importantly, often impede incorporating secure cryptographic protocols. Both aspects are in fact closely tied because (public-key) cryptography is computationally demanding. It is therefore a constant tussle of cryptographers and embedded engineers alike to fit secure and most advanced cryptographic protocols into constrained devices, and to have them perform sufficiently well to enable a wide range of applications. Unsurprisingly, an important criterion to assess a new cryptographic protocol is to evaluate its suitability for constrained devices.

The rise of Post-Quantum Cryptography (PQC) exacerbates the problem. Recalling the context first: Large-scale quantum computers are a threat to our current digital security infrastructure, especially public-key cryptography (PKC). The reason is that the security of today's predominant public-key cryptography – RSA and Elliptic Curve Cryptography (ECC) – rests on the hardness of computational problems which are known [Sho97, PZ03] to be solvable in polynomial time using a large quantum computer. Therefore, the National Institute of Standards and Technology (NIST) started a standardization procedure [NIS] aimed at the standardization of key-encapsulation mechanisms (KEM), public-key encryption (PKE) and signature schemes which resist the increased computational abilities of quantum computers – those schemes form the field of Post-Quantum Cryptography (PQC). These schemes will eventually replace their counterparts RSA and ECC used in our current public-key infrastructure. We refer to [NIS, Arm20] for more detailed introductions.

Post-Quantum Cryptography is highly relevant to the problem of balancing cost, performance and security in the IoT since it tends to have a higher resource footprint than classical public key cryptography. It is thus vital to understand the demands and performance of PQC on embedded devices. Reflecting this, the Cortex-M4 processor has been designated by NIST as the reference platform for PQC on embedded systems.

The most prominent class of PQC is that of schemes based on structured lattices, and the underlying computational workload is the multiplication of polynomials of large degree and low coefficient precision. This problem has been studied extensively, and two approaches prevailed: Multiplication via the Toom-Cook-Karatsuba algorithms [Too63, Coo66, KO62], and multiplication via the Number Theoretic Transform (NTT). We are thus interested in the constraints and performance of these algorithms on embedded systems. Structurally, both approaches are very similar and amenable to the same tradeoffs [KMRV18, KRS19, MKV20]. The main benefit of Toom-Cook is the absence of modular arithmetic, which the NTT heavily relies on. Its main drawback, and the primary factor determing its memory-usage, is that it expands the input both before ("evaluation") and during ("point multiplication") the core of the multiplication routine, while the NTT operates in-place.

On high-end processors, performance improvements can often be obtained by leveraging Single Instruction Multiple Data (SIMD) instruction set extensions, such as Arm's Neon instruction set on the R- and A-profiles of the Arm architecture, or the Intel® Advanced Vector Extension (AVX). On embedded systems, however, SIMD instruction extensions are challenging within the usually tight power, cost and area constraints. The M-profile Vector Extension (MVE), or Helium vector extension, is a rather recent addition to the M-profile of the Arm architecture which promises to introduce the performance benefits of vector extensions to embedded systems while maintaining a low gate and power profile. The Cortex-M55 processor is the first implementation of the Helium instruction set. The primary motivation of this work is to evaluate how this future generation of low-cost and low-energy processors fare in the context of next generation of public key cryptography.

**Contributions** We contribute to the study of viability and performance of PQC on embedded devices. We study two themes: Firstly, how to reduce the resource demands of PQC for low-end embedded devices such as the Cortex-M4 CPU. Secondly, how to leverage the Helium instruction set on embedded devices implementing the Helium vector extension, focusing on the Cortex-M55 processor. Our specific contributions are as follows:

• We revive a known but little used variant of Toom-Cook and Karatsuba called *striding Toom-Cook/Karatsuba* to reduce the memory-usage of polynomial multiplication. In a nutshell, while expansion during evaluation remains, a suitable input reordering allows to avoid size-doubling on the point-multiplication, thereby saving almost 50% in memory and also accelerating the interpolation step. See Table 1. We implement the striding variant of Toom-Cook/Karatsuba on the Cortex-M4 processor.

• We implement the striding Toom-Cook/Karatsuba and a 32-bit degree-256 negacyclic NTT on the Cortex-M55 processor, based on the Helium instruction set. We report an  $\approx 5 \times$  speedup of our striding Toom-Cook/Karatsuba implementation compared to previous Cortex-M4 implementations, and an  $\approx 3.5 \times$  speedup of our implementation of the NTT compared to the fastest NTT on Cortex-M4 [CHK<sup>+</sup>21].

We provide an introduction to the M-profile Vector Extension and to the Cortex-M55 processor, highlight its similarities and differences compared to other vector extensions, and share our experience on what to look out for to get the most out of the instructions. We hope that this will enable researchers to build on our work and study the use of the Helium vector extension for other workloads, esp. PQC schemes.

|                                          | NTT [CHK <sup>+</sup> 21] | Toom-Cook    |

|------------------------------------------|---------------------------|--------------|

| Lazy interpolation                       | ✓                         | ✓ [MKV20]    |

| No expansion during evaluation           | <b>√</b>                  | Х            |

| No expansion during inner multiplication | ✓                         | ✓[This work] |

Table 1 Comparing features of multiplication based on FFT/NTT and Toom-Cook

**Code** The code generation tooling and resulting Helium assembly for Cortex-M55 are available at <a href="https://gitlab.com/arm-research/security/pqmx">https://gitlab.com/arm-research/security/pqmx</a>. The repository also contains detailed instructions for how to explore Helium using a freely available functional model of the Cortex-M55. The Cortex-M4 code will be made available on the Saber repository <a href="https://github.com/KULeuven-COSIC/SABER">https://github.com/KULeuven-COSIC/SABER</a>.

## 2 Preliminaries

We denote  $\mathbb{Z}_n$  the ring of integers modulo  $n \in \mathbb{Z}$ . If n = q is a prime, we also write  $\mathbb{F}_q$ . Unless stated otherwise, R denotes a any commutative ring. We denote R[X] the polynomial ring over R, and for a monic polynomial  $P \in R[X]$  we denote R[X]/(P) the quotient of R[X] obtained by identifying polynomials with the same remainder modulo P. We will mostly work with  $\mathbb{F}_q[X]/(X^n+1)$  or  $\mathbb{Z}_{2^k}[X]/(X^n+1)$ .

#### 2.1 Polynomial multiplication

In this section we survey the most prominent sub-quadratic polynomial multiplication strategies: Toom-Cook/Karatsuba and the Number Theoretic Transform (NTT). Good expositions exist in the literature, so we will be brief. See e.g. the excellent [Ber01].

## 2.2 Multiplication by evaluation

The idea behind Toom-Cook/Karatsuba and NTT-based multiplication is the same: Multiplication via evaluation. Given a ring R, two polynomials  $f, g \in R[X]$  and fixed elements  $\alpha_1, \ldots, \alpha_n \in R$ , we have  $(fg)(\alpha_i) = f(\alpha_i)g(\alpha_i)$ . Each equation puts a constraint on fg, and by choosing n large enough, we hope to be able to recover fg from  $(fg)(\alpha_i)$ .

Formally, consider the evaluation homomorphism

$$\widetilde{\operatorname{ev}}_{\alpha}: R[X] \xrightarrow{f \longmapsto (f(\alpha_1), \dots, f(\alpha_n))} R \times R \times \dots \times R.$$

It factors through the quotient  $R[X]/\prod_i (X-\alpha_i)$ , which as a set is canonically identified with  $R[X]^{< n}$ , the set of polynomials of degree < n. Depending on the context, we

can view the evaluation homomorphism either as  $\operatorname{ev}_{\alpha}: R[X]/\prod_{i}(X-\alpha_{i}) \to R^{n}$ , or as  $\operatorname{ev}_{\alpha}: R[X]^{\leq n} \to R^{n}$ . It is an isomorphism if and only if for all  $i \neq j$ ,  $\alpha_{i} - \alpha_{j}$  is invertible in R. For example, this holds if R is a field and the  $\alpha_{i}$  are pairwise distinct. If  $\operatorname{ev}_{\alpha}$  is bijective, we can thus fully recover a polynomial  $f \in R[X]^{\leq n}$  of degree  $\leq n$  from its evaluations  $f(\alpha_{i})$ ; equally, we can recover the residue of  $f \in R[X]$  modulo  $\prod_{i}(X-\alpha_{i})$  from  $f(\alpha_{i})$ .

This technique can be used to calculate products fg if  $f,g \in R[X]/\prod_i (X-\alpha_i)$  or if  $f \in R[X]^{\leq a}, g \in R[X]^{\leq b}$  with a+b < n: In both cases, we first compute  $f(\alpha_i), g(\alpha_i)$  – the "evaluation step" – then the products  $f(\alpha_i)g(\alpha_i)$  – the "point multiplication step" – and finally recover fg from its evaluations at the  $\alpha_i$  – the "interpolation step".

It is common to add the "evaluation at  $\infty$ ", giving  $\operatorname{ev}_{\alpha}^{\infty}: R[X]^{\leq n} \to R^{n+1}$  defined by  $f \mapsto (f(\alpha_1), \ldots, f(\alpha_n), f(\infty))$ , where  $f(\infty)$  is the coefficient of  $X^n$ . This extended evaluation  $\operatorname{ev}_{\alpha}^{\infty}$  is bijective if and only if  $\operatorname{ev}_{\alpha}$  is. In this case, we can therefore a polynomial of degree  $\leq n$  from its evaluations at  $\alpha_1, \ldots, \alpha_n$  plus its n-th coefficient.

#### 2.2.1 Toom-Cook/Karatsuba

Karatsuba's algorithm instantiates the "multiplication by evaluation" blueprint with  $\alpha_0 = 0, \alpha_1 = 1, \alpha_2 = \infty$ , thereby allowing to compute the product of two degree-1 polynomials f = a + bX and g = c + dX in terms of their evaluations at  $0, 1, \infty$ . Concretely,

$$f(0) = a, f(1) = a + b, f(\infty) = b, g(0) = c, g(1) = c + d, g(\infty) = d,$$

and we recover fg from the point multiplications f(0)g(0), f(1)g(1), and  $f(\infty)g(\infty)$  via

$$fg = (a+bX)(c+dX) = ac + (ad+bc)X + bdX^{2}$$

=  $f(0)g(0) + (f(1)g(1) - f(0)g(0) - f(\infty)g(\infty))X + f(\infty)g(\infty)X^{2}$ .

This works for any ring R since  $\alpha_0 - \alpha_1 = -1$  is invertible.

The Toom-Cook algorithm generalizes Karatsuba's. Concretely, we are interested in 4-way Toom-Cook defined by the points  $0, \infty, \pm 1, \pm \frac{1}{2}, 2$  and applied over a ring R where  $2^k = 0$  for some k – we will mainly be looking at  $\mathbb{Z}_{2^{13}}$ . This setting has been introduced and studied in [KMRV18], and a few subtle points should be noted – see [KMRV18] for details: Firstly, to make sense of the fractional evaluations  $\mathbb{Z}$ , one scales by  $\alpha^{\deg(f)}$ , so that for  $f = a_0 + a_1 X + a_2 X^2 + a_3 X^3$  we have  $f\left(\frac{1}{2}\right) := 8a_0 + 4a_1 + 2a_2 + a_3$ . Secondly, ev<sub>\alpha</sub> is not an isomorphism: In fact, if  $2^k = 0$  in R but  $2^{k-1} \neq 0$ , the polynomial  $f := 2^{k-1} X(X+1)$  satisfies  $f(\alpha) = 0$  for all  $\alpha \in \{0, \infty, \pm 1, \pm \frac{1}{2}, 2\}$ . However, [KMRV18] explains that multiplication by evaluation still works if we temporarily operate with k+3 bits of precision – that is, we lift representatives from  $\mathbb{Z}_{2^k}$  to  $\mathbb{Z}_{2^{k+3}}$  below  $2^k$ , compute evaluation, multiplication and interpolation in  $\mathbb{Z}_{2^{k+3}}$ , and reduce to  $\mathbb{Z}_{2^k}$  in the end.

#### 2.2.2 Iterating Toom-Cook/Karatsuba

Toom-Cook/Karatsuba multiplication is usually applied iteratively, with R being a polynomial rings itself, transforming a product of two polynomials of large degree into numerous products of polynomials of smaller degree, which can then be computed by more direct means such as schoolbook multiplication. We explain this for k-way Toom-Cook.

Given a polynomial  $f \in R[X]^{< n}$  with n = kr, we can group its monomials into the blocks  $\{\frac{in}{k}, \frac{in}{k} + 1, \dots \frac{(i+1)n}{k} - 1\}, i = 0, \dots, r - 1$ , and thereby express f as

$$\tilde{f} = f_0(X) + f_1(X)Y + \dots + f_{k-1}(X)Y^{k-1}, \quad \deg_X(f_i) < n/k, \quad Y = X^{\frac{n}{k}}.$$

Formally, we consider lifts under  $R[X]^{< n/k}[Y]^{< k} \to R[X]^{< n}, Y \mapsto X^{n/k}$ . Treating R' := R[X] as the coefficient ring, we then apply Toom-Cook to compute  $R'[Y]^{< k} \times R'[Y]^{< k} \to R[X]$

$R'[Y]^{\leq 2k-1}$  via 2k-1 multiplications of elements in R' and substitute  $Y=X^{n/k}$  afterwards. Ultimately, this computes a degree-n product via 2k-1 products of degree n/k.

Toom-Cook and Karatsuba can be combined. E.g., one layer of 4-way Toom-Cook and two layers of Karatsuba reduce a degree-16n product to 63 degree-n products.

#### 2.2.3 Number Theoretic Transform

The Number Theoretic Transform (NTT) instantiates the "multiplication by evaluation" blueprint with  $R = \mathbb{F}_q$  for a prime q with n|q-1. Then, it is known that  $\mathbb{F}_q$  has a primitive n-th root of unity  $\zeta_n$ , and that  $X^n - 1 = \prod_i (X - \zeta_n^i)$ , and  $\operatorname{ev}_{\alpha}$  is an isomorphism

$$\operatorname{NTT}: \mathbb{F}_q[X]/(X^n-1) \xrightarrow{f \mapsto (f(1),f(\zeta),\dots,f(\zeta^{n-1}))} \mathbb{F}_q^n.$$

If  $n=2^k$ , then NTT can be computed iteratively as indicated in the following figure:

$$\mathbb{F}_{q}[X]/(X^{n}-\zeta_{n}^{n})\underbrace{\qquad\qquad} \mathbb{F}_{q}[X]/(X^{n/2}-\zeta_{n}^{0(n/2)})$$

$$\mathbb{F}_{q}[X]/(X^{n/4}-\zeta_{n}^{0(n/4)}) \quad \mathbb{F}_{q}[X]/(X^{n/4}-\zeta_{n}^{0(n/4)})$$

$$\mathbb{F}_{q}[X]/(X^{n/4}-\zeta_{n}^{0(n/4)}) \quad \mathbb{F}_{q}[X]/(X^{n/4}-\zeta_{n}^{0(n/4)})$$

Here, the k-th entry from the right in the i-th layer is  $\mathbb{F}_q[X]/(X^{n/2^i}-\zeta_n^{\mathrm{rev}_i(k)(n/2^i)})$ , where  $\mathrm{rev}_i$  is the bit-reversal on i+1 bits. For example,  $\mathrm{rev}_1(1)=\mathrm{rev}_1(0\mathrm{b01})=0\mathrm{b10}=2$ .

This strategy is akin to the Cooley-Tukey algorithm for the FFT and achieves complexity  $n \log_2(n)$ . Since NTT is a ring isomorphism, we can compute the product of  $a, b \in \mathbb{F}_q[X]/(X^n-1)$  as NTT<sup>-1</sup>(NTT(a)  $\circ$  NTT(b)), where  $\circ$  is pointwise multiplication in  $\mathbb{F}_q^n$ . We consider the NTT from an implementation view. Every transition is of the form

$$R[X]/(X^{2n} - \alpha^2) \to R[X]/(X^n - \alpha) \times R[X]/(X^n + \alpha).$$

In terms of the standard monomial basis,  $R[X]/(X^{2n}-\alpha^2)\to R[X]/(X^n-\alpha)$  is given by  $f_0+X^nf_1\mapsto f_0+\alpha f_1$ , while  $R[X]/(X^{2n}-\alpha^2)\to R[X]/(X^n-\alpha)$  is given by  $f_0+X^nf_1\mapsto f_0-\alpha f_1$ . The transformation  $(a,b)\mapsto (a+\zeta b,a-\zeta b)$  is called a *Cooley-Tukey* (CT) butterfly. The *Gentleman-Shande* (GS) butterfly  $(a,b)\mapsto (a+b,\zeta^{-1}(a-b))$  reverses the Cooley-Tukey butterfly up to  $\frac{1}{2}$ . The CT and GS are central primitives to implement for an NTT-based polynomial multiplication; the third is point-wise multiplication in  $\mathbb{F}_q$ .

## 2.3 Modular Arithmetic in $\mathbb{F}_q$

We briefly recall two prominent algorithms in the context of modular multiplication: Barrett reduction and Montgomery multiplication.

The central problem is as follows: Given a modulus  $n \in \mathbb{Z}$  and a "large"  $a \in \mathbb{Z}$ , find "small" representatives of a modulo n. Two choices stand out: Firstly, the canonical unsigned representative a mod<sup>+</sup> n is the unique representative of a modulo n in the interval  $\{0,1,\ldots,n-1\}$ . Secondly, the canonical signed representative a mod<sup>+</sup> n is the unique representative of a modulo n in the interval  $\{-\lceil \frac{n}{2} \rceil, -\lceil \frac{n}{2} \rceil + 1, \ldots, \lfloor \frac{n}{2} \rfloor\}$ . These can naïvely be calculated as a mod<sup>+</sup>  $n = a - n \lfloor \frac{a}{n} \rfloor$  and a mod  $n = a - n \lfloor \frac{a}{n} \rfloor$ , but such an approach is inacceptable from a performance perspective since division by n is expensive in general. Barrett and Montgomery reduction are two ways around this by trading the division by n for a division by a 2-power, which can implemented cheaply as a bitshift.

#### 2.3.1 Barrett reduction

The idea behind Barrett reduction is to pick  $\ell$  such that  $2^{\ell} > n$  and approximate  $\left\lfloor \frac{a}{n} \right\rceil = \left\lfloor a \frac{2^{\ell}}{n} / 2^{\ell} \right\rceil \approx \left\lfloor a \left\lfloor \frac{2^{\ell}}{n} \right\rfloor / 2^{\ell} \right\rceil$ , where  $C := \left\lfloor \frac{2^{\ell}}{n} \right\rfloor$  can be precomputed. See Algorithm 1. For  $a < 2^{\ell}$  and  $\ell$  bounded by the machine word size, the resulting modular reduction  $a - n \cdot \left\lfloor \frac{aC}{2^{\ell}} \right\rfloor$  is amenable for direct mapping to many instruction set architectures: It is a combination of a high-multiply with rounding for  $x \mapsto \left\lfloor \frac{x \cdot C}{2^{\ell}} \right\rfloor$  and a low-multiply-accumulate for  $x, a \mapsto a - n \cdot x$ . We will discuss the details in the case of the Helium vector extension in Section 6.4.1.

#### 2.3.2 Montgomery reduction and multiplication

Montgomery reduction is a way to compute a representative a' s.t.  $2^{\ell}a' \equiv a \mod n$  if n is odd; in other words, a' is a small representative of the quotient  $\frac{a}{2^{\ell}}$  computed in  $\mathbb{Z}_n$  – note that the latter expression always makes sense because n is odd, and hence  $2^{\ell}$  is invertible modulo n.

If a is already divisible by  $2^{\ell}$  in  $\mathbb{Z}$ , we can set  $a' := \frac{a}{2^{\ell}}$ , computed in  $\mathbb{Z}$ . Otherwise, if we pick  $k := a \cdot n^{-1} \mod^{\pm} 2^{\ell}$ , where  $a \cdot n^{-1}$  is computed in  $\mathbb{Z}_{2^{\ell}}$ , we have  $n \cdot k \equiv a$  modulo  $2^{\ell}$  by construction, and so  $a - n \cdot k$  is divisible by  $2^{\ell}$ . We can thus set  $a' := (a - n \cdot k)/2^{\ell}$ .

We are interested in Montgomery reduction for  $\ell$  bounded by the machine word size, and  $a < 2^{2\ell}$  a product of two single-width values  $x, y < 2^{\ell}$ . In this case, it can be expressed in single-width operations: two high-multiplications  $x, y \mapsto \frac{xy}{2^{\ell}}, \ k \mapsto \frac{n \cdot k}{2^{\ell}}$ , and two low multiplications  $x, y \mapsto xy \mod^+ 2^{\ell}, \ a \mapsto a \cdot n^{-1}$  in  $\mathbb{Z}_{2^{\ell}}$ . See Algorithm 2 for both the double-width and the single-width descripton of Montgomery multiplication. We will discuss the details in the case of the Helium vector extension in Section 6.4.1.

| Algorithm 1: Barrett reduc-                                                     | Algorithm 2: Montgomery multiplication                    |                                                                                      |  |  |

|---------------------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|

| tion                                                                            | In: $n$ odd modulus, $2^{\ell} > n$ , $a, b < 2^{\ell}$ . |                                                                                      |  |  |

| In: $n \text{ modulus}$ , $2^{\ell} > n$ , $z < 2^{\ell}$ .                     | In: $\omega$ modular inver                                |                                                                                      |  |  |

| <b>Out:</b> Barrett reduction of $z$ w.r.t.                                     | r.t. $n$ . Out: Montgomery multiplication of $a, b$ w     |                                                                                      |  |  |

| 1: $t \leftarrow \left  z \left  \frac{2^{\ell}}{n} \right  / 2^{\ell} \right $ | 1: $h \leftarrow ab$                                      | $h \leftarrow \lfloor \frac{ab}{2^{\ell}} \rfloor, l \leftarrow ab \bmod^+ 2^{\ell}$ |  |  |

| $2: c \leftarrow nt$                                                            | 2: $r \leftarrow h\omega \mod^{\pm} 2^{\ell}$             | $r \leftarrow l\omega \mod^{\pm} 2^{\ell}$                                           |  |  |

| 3: <b>return</b> $z-c$                                                          | $3: c \leftarrow r \cdot n$                               |                                                                                      |  |  |

|                                                                                 | 4: $\mathbf{return} \ \frac{h-c}{2^{\ell}}$               | return $h-c$                                                                         |  |  |

## 3 M-profile Vector Extension (MVE)

In this section we give an introduction to the M-profile Vector Extension (MVE), also referred to as  $\operatorname{Arm}^{\otimes}$  Helium Technology. We will focus on aspects of MVE that are relevant to the algorithms studied in this paper, and refer to [Arme, Mar21] more exhaustive introductions to the Helium instruction set, as well as to [Armb] for the full reference. We also found the blog series [Armc, Part 1-4] very useful.

#### 3.1 Introduction to MVE

The M-Profile Vector Extension (MVE) is a feature of the Armv8.1-M architecture [Armb, Arme], primarily for signal processing and machine learning applications. MVE is also referred to as the Helium vector extension, in alignment with the  $\text{Arm}^{\oplus}$  Neon<sup>TM</sup> Technology architecture extension for A-profile processors [Arma, Section C.3.5]. However, while there are similarities between the Helium instruction set and the Neon instruction set, the

Helium vector extension is a new ground-up architecture design specifically tailored for the extreme area and energy efficiency required in typical Cortex-M applications.

**SIMD basics** The Helium instruction set is primarily an architectural extension for Single Instruction Multiple Data (SIMD) operations: It adds a set of 128-bit registers viewed as vectors of equal-sized blocks called lanes, and instructions operate on the lanes in parallel. For example, a 128-bit vector register can be viewed as a length-8 vector of unsigned 16-bit elements, and a 16-bit vector add VADD.u16 adds the lanes of two such vectors, storing the results in the lanes of a third vector – thus the term "Single Instruction, Multiple Data".

The vector file Like the Neon instruction set, the Helium vector extension uses 128-bit vector registers. There are 8 vector registers, compared to 32 in the Neon instruction set, a design choice which can be approached from multiple angles: Firstly, it results in a lower gate count and power profile. Secondly, the lower vector count is compensated for by multiple features, including the presence of numerous instructions utilizing both vector and scalar registers. The suitability of scalar-vector operations is a main difference between M- and A-profile: On A-profile implementations, the physical distance between vector and scalar register file is too large to allow for low-latency scalar-vector operations. The smaller scale of M-profile CPUs means that these operations become feasible.

**Implication: Algorithm design** A common technique for vectorization of computational workloads is batching, whereby multiple instances of a higher-level construct are computed in parallel, rather than the computation of a single instance of the construction being vectorized and accelerated.

Since batching tends to use a large number of vector registers but a low number of general purpose registers (GPR), we found it not suitable for use with the Helium vector extension except for very small computations. Instead, we found that the Helium instruction set works well for single-instance speedup, using a mix of vector and GPR file. We will see this in the example of schoolbook multiplications below.

**Instruction Overlapping** The idea of overlapping the execution of instructions is fundamental to CPU microarchitecture and at the heart of the concept of a pipeline. However, it is commonly hidden from the programmers. The Helium architecture extension deviates from this by making instruction overlapping part of the *architecture*.

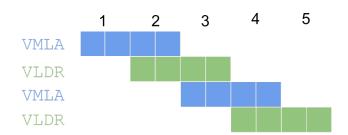

The execution of each vector instruction is architecturally subdivided into four 32-bit parts called *beats*. The operation of each beat may affect multiple lanes: For example, the VADD.u16 operation operates on two 16-bit lanes per beat. The Helium architecture extension requires that each beat of an instruction is executed in-order, but it allows implementations to execute beats from the following instruction whilst still executing beats from the previous instruction [Armb]. For example, a vector load VLDR instruction can be overlapped with a vector multiply accumulate VMLA as shown in Figure 1.

Because the load/store units and arithmetic units can both be kept busy at the same time, even on a single issue CPU, the architected instruction overlap can significantly improve performance at minimal area overheads. Moreover, implementations benefit from the fact that instruction overlapping is architectural because they don't need logic to maintain the illusion of atomic execution: The Helium architecture extension allows instructions to be interrupted between architectural beats.

Implication: Instruction design Support for instruction overlapping has to be built into the design of the architecture: For example, consider a data dependency between two consecutive instructions A, B on a dual-beat system. In this case, beats BO, BI of B can only commence if the inputs (produced by beats AO, AI of A) are available. Generally, this

Figure 1 Illustration of instruction overlapping on a dualbeat implementation of the Helium instruction set

is supported by instructions whose beats describe the same amount of work and operate on lanes independently, and from right to left. This explains why there is a 128-bit left shift Helium instruction VSHLC, but no 128-bit right shift. Long multiplies are another example: The inputs to VMULL in the Neon instruction set are lower and upper halves of 128-bit vectors. This would not fare well with beat-wise execution, and instead there are instructions VMULL{B,T} in Helium operating on even or odd parts of the inputs, which is beat-friendly. We again refer to [Armc, Part 1] for details and more examples.

Implication: Programming discipline There are three main ways to develop code for the Helium instruction set: Auto-vectorization, intrinsics and handwritten assembly. In the former cases, the compiler has the responsibility of instruction scheduling. When handwriting Helium instructions, however, it important to carefully study the ordering of instructions in order to make optimal use of instruction overlapping and the available computational resources. For example, the sequence in Figure 1 would run 50% slower on a system with 64-bit data paths if we'd batch the multiplies and load operations. Generally, alternating instructions of different nature (load/store, add/sub, multiply) is preferred.

Low overhead loops Armv8.1-M adds the Low Overhead Branch Extension, allowing software to indicate how many iterations of a loop are going to be executed and let the hardware take care of counter modification and branching. Most importantly, the loop-end instruction LE permits to cache details of the loop and allow processors to optimize future iterations, skipping subsequent LE instructions and overlapping instructions across loop iterations. The following iterations of the loop can therefore perform as if the loop had been unrolled at compile-time. See [Armc, Part 4] for details.

Interleaving memory operations The Helium instruction set adds support for deinter-leaving data during loads via the instructions VLD2{0-1} and VLD4{0-3}, and interleaving data during stores via the VST2{0-1} and VST4{0-3}. Logically, those instructions correspond to a load/store of 64 byte of data, combined with  $2 \times \_ \leftrightarrow \_ \times 2$  and  $4 \times \_ \leftrightarrow \_ \times 4$  transpositions. It should be noted that the feasibility of such instructions in an embedded architecture is a non-trivial question, as the required interleaving logic has to be implementable at low cost. We refer to [Armc, Part 2] for details on how this is achieved.

### 3.2 Cortex-M55

The Cortex-M55 processor is the first implementation of the Arm v8.1-M architecture, including optional support for the Helium vector extension. Cortex-M55r1 is the most recent revision of the Cortex-M55 processor, providing additional features and performance optimizations. We give a very brief introduction here and refer to [Armd] for details.

Pipeline and memory The Cortex-M55 processor has a 5-stage in-order pipeline when Helium is included, and instruction scheduling is single-issue with a few exceptions. In addition to cache-able main memory, the Cortex-M55 processor supports tightly coupled memory (TCM) interfaces for instructions and data, allowing fast and deterministic memory access which is useful for real-time or performance critical applications. The total D-TCM bandwidth is 128-bit/cycle, allowing 64-bit/cycle bandwidth for processing such as vector processing, plus 64-bit/cycle for DMA transfers to/from TCM running in the background. We locate all our code and data in TCM for our measurements.

**Vector processing** The Cortex-M55 processor is a dual-beat implementation of the Helium instruction set which supports instruction overlapping. This means that it takes two cycles to perform the work of a vector instruction, and that parallel execution of the next instruction can commence in the second cycle, computing resources permitting. Figure 1 shows how a sequence of alternating VMLA, VLDR would perform on the Cortex-M55 processor, absent of other hazards and assuming data and code in TCM.

Our experiments suggest that the Cortex-M55 processor has separate units for load/store (e.g. VLDR, VSTR), additive integer operations (e.g. VADD, VSUB), and multiplicative integer as well as floating point operations (e.g. VMUL). When optimizing assembly for the Cortex-M55 processor, we therefore tried to achieve an alternation of those three kinds of operations as a first step towards good instruction overlapping. The assembly snippets below reflect the different instruction types through their color.

## 4 Memory efficient striding Toom-Cook

In this section, we describe "striding" Toom-Cook multiplication. While not new – see e.g. [Ber01] – it doesn't appear to have been used in lattice-based cryptography before.

Recall from Section 2.2.2 that using classical Toom-Cook k-way for large-degree multiplication, the inputs in R[X] are lifted to the isomorphic ring  $R[X][Y]/(X^k - Y)$  via

$$a_0 + a_1 X + \dots + a_{n-2} X^{n-2} + a_{n-1} X^{n-1}$$

$$= (a_0 \dots + a_{k-1} X^{k-1}) + (a_k \dots + a_{2k-1} X^{k-1}) Y \dots + (a_{n-k} \dots + a_{n-1} X^{k-1}) Y^{r-1}$$

where  $r:=\frac{n}{k}$ , before k-way Toom-Cook is applied to  $R'[Y]^{< r}$  over the base ring R'=R[X]. The problem with this approach is that even if, ultimately, we care about size-preserving multiplication in  $R[X]/(X^n+1)$ , the base multiplication in  $R[X]^{< k}$  is length-doubling: The polynomial degree is too small for wraparound. This size-doubling during point multiplication in turn raises the memory usage.

This can be improved by using a different ring isomorphism, effectively changing the arrangement of X and Y: We lift the polynomials from R[X] to  $R[Y][X]/(X^k - Y)$  as

$$(a_0 + a_k Y + \dots + a_{(r-1)k} Y^{r-1}) X^0 + (a_1 + a_{k+1} Y + \dots + a_{(r-1)k+1} Y^{r-1}) X^1 + \dots$$

$$= \sum_{i < k} (a_i + a_{k+i} Y + \dots + a_{(r-1)k+i} Y^{r-1}) X^i$$

and apply k-way Toom-Cook to  $R'[X]^{< k}$  and base ring  $R' = R[Y]^{< r}$ . The point is: If our target ring is  $R[X]/(X^n+1) = R[X]/(X^{rk}+1)$ , then because  $Y = X^k$ , our new base R' = R[Y] is in fact  $R[Y]/(X^r+1)$ , another negacyclic polynomial ring with size-preserving multiplication. In this way, the polynomial reduction can be moved to the point multiplication, significantly reducing memory usage of Toom-Cook multiplication. Another advantage is that the interpolation operates on smaller polynomials and is thus faster.

**Difference in evaluation:** Striding Toom-Cook/Karatsuba evaluation differs from classical evaluation only through the memory access pattern, which is no longer contiguous but at stride k. In Section 5 and Section 6 we discuss how to overcome this with low performance-penalty on the Cortex-M4 and Cortex-M55 processors. Alternatively, one can permute the input upfront and thereby reduce striding evaluation to classical evaluation. It depends on the context whether this is feasible – we comment on the case of Saber below.

**Differences in interpolation:** While classical interpolation gives  $ab = \sum_{i < 2k-1} c_i(X)Y^k$  with  $\deg_X(c_i) < 2(n/k)$  and  $Y = X^{n/k}$ , striding interpolation gives  $ab = \sum_{i < 2k-1} c_i(Y)X^k$  with  $\deg_Y(c_i) < n/k$  and  $Y = X^k$ . Resolving the substitution  $Y = X^{n/k}$  in the classical context means overlapping the upper half of  $c_i$  with the lower half of  $c_{i+1}$ . Resolving the substitution  $Y = X^k$  in the striding context gives  $ab = \sum_{i < k} (c_i(X^k) + X^k c_{k+i}(X^k))X^i$  computing this thus involves a negacyclic rotation of  $c_{k+i}$  and addition onto  $c_k$ .

## 4.1 Application: Saber

Our primary interest in striding Toom-Cook/Karatsuba multiplication lies in its use for the Saber PQC scheme. We refer to [BMD+20] or the section pertaining to Toom-Cook multiplication in the supplementary material for details, but the important point is that the ring  $\mathbb{Z}_{2^{13}}[X]/(X^{256}+1)$  underlying Saber is amenable to iterated application of the striding method. Concretely, a striding Toom-Cook/Karatsuba based multiplication for Saber would use a hybrid of one layer of 4-way Toom-Cook to reduce from  $\mathbb{Z}_{2^{13}}[X]/(X^{256}+1)$  to  $\mathbb{Z}_{2^{13}}[X]/(X^{64}+1)$ , one or two layers of Karatsuba to reduce from  $\mathbb{Z}_{2^{13}}[X]/(X^{64}+1)$  to  $\mathbb{Z}_{2^{13}}[X]/(X^{16,32}+1)$ , and schoolbook multiplication.

The polynomials used in Saber are generated from packed data on a per-coefficients level. We expect that it possible to merge the upfront permutation of the input into the key generation process with small negligible penalty, thereby reducing the evaluation step to classical Toom-Cook/Karatsuba, but leave exploring the details for future work.

## 5 Implementation: Cortex-M4

In this section, we describe the implementation aspects of the striding version of Toom-Cook and Karatsuba on Cortex-M4 processors.

## 5.1 Toom-Cook/Karatsuba

As explained in Section 4, there are two fundamental differences between the classical and the striding variants of Toom-Cook multiplication, the access pattern to the coefficients of the operands, and the memory expansion of the products. The sequence of arithmetic operations that are performed during evaluation and interpolation once the polynomial coefficients are loaded from memory is the same for both variants.

The read accesses occur during the evaluation and are performed with a 64 offset for the classical Toom-Cook whereas 4 consecutive coefficients at a time are required for the striding version. Although the access pattern of the striding variant is more regular, this is an issue for exploiting the DSP extensions to carry out two operations on halfword registers in parallel. To circumvent this problem, the polynomials can be stored with a custom memory layout, in which case the complexity is moved to the packing operation, or the coefficients of the polynomial can be packed with an offset of 4 after being loaded into the register. Since we implement the entire multiplication we opt for the latter. The instruction overhead is equal to the number of word loads, effectively as if we only performed halfword loads.

The write operations happen during the interpolation, when the result is computed from the weighted polynomials. Here, the striding version has an advantage since it iterates half the times of the classical due to the non expansion of the products. Additionally, since the coefficients of the result are generated consecutively, the write operations can be simplified to 4 per iteration instead of 7. In addition to this simplification of the interpolation, the non expansion of the products in the striding version allows for a halving in the memory requirements to store all the weighted polynomials, i.e., a saving of 896 bytes.

The differences in the implementation of the striding version of Karatsuba with respect to the classical Karatsuba are equivalent to Toom-Cook. There is an overhead in the instruction count due to the sequential access pattern to the coefficients of the polynomial during evaluation, and the counterpart during interpolation if one wants to exploit the single instruction multiple data capabilities of Cortex-M4 processors. However, the non expansion of the polynomial degree after the multiplication is more beneficial than in the case of Toom-Cook. In particular, if Karatsuba is applied recursively the memory utilization can be kept constant by re-utilizing the memory allocated to store the operands after the evaluation is performed.

### 5.2 Schoolbook

It has been shown in [KMRV18] and later in [KRS19] that the schoolbook has the highest impact in the performance of the polynomial multiplication. We follow the divide and conquer approach of [KRS19] to decompose the schoolbook into smaller multiplications that can be performed without fetching extra coefficients from memory and aiming to use the multiply and accumulate instructions. However, in this case the multiplication has to avoid the length doubling of the resulting polynomial, i.e., the negacyclic convolution must be performed in-place. This is a challenge because the DSP extensions of Cortex-M4 processors offer a wide range of multiply and accumulate instructions but not their multiply and subtract counterparts. Additionally, there are extra load instructions required due to the negatively wrapped accumulation of the result which increases further the register pressure, which is the key for a high performance schoolbook [KMRV18, KRS19]. To circumvent this issue, we create a custom memory layout where both operands are in consecutive addresses and, therefore, only one pointer needs to be kept in a register while coefficients of different operands can be loaded using immediate offsets.

The other implementation decision for the polynomial multiplication is how to select the cut-off from which Karatsuba is not applied anymore and the multiplication is performed using the schoolbook algorithm. Due to the availability of registers to pre-load coefficients and the absence of multiply and subtract instructions, we find that the optimal cut-off for schoolbook is degree 16. For higher cut-offs, the performance will be determined by the dominant term between the extra load operations required in the striding version of Karatsuba and the overhead introduced by the negacyclic convolution in the schoolbook. We have verified that the optimal choice is for 16 coefficients multiplication for which a full 256 coefficient polynomial multiplication can be performed in 34,884 clock cycles, while for 32 coefficients the execution time increases to 36,340 clock cycles. This choice was expected since 16 was also the optimal cut-off for other multiplications combining Toom-Cook and Karatsuba [KMRV18, KRS19].

In Section 7 we discuss the performance and memory figures of our proposed multiplication and compare the impact on the full Saber operation to other implementations in Cortex-M4 processors as well as in the new Cortex-M55 processor.

## 6 Implementation: Cortex-M55

In this section, we describe our implementations of large-degree, low-precision polynomial multiplication on the Cortex-M55 CPU, leveraging the Helium vector extension.

## 6.1 NTT vs. Toom-Cook/Karatsuba on vector architectures

[CHK<sup>+</sup>21] demonstrates that for Cortex-M4, polynomial multiplication via NTTs can outperform multiplication via Toom-Cook even for coefficient rings not tailored to the NTT, such as  $\mathbb{Z}_{2^{13}}$ . For vectorized implementations, however, the passage to the NTT comes at a larger cost than for non-vectorized implementations. We provide some details.

Setting expectations Since the Helium vector extension operates on 128-bit vectors, we consider a  $4\times$  speedup a theoretical limit for a vectorized 32-bit NTT. However, we don't expect to meet this limit, because the NTT relies on long multiplications for modular arithmetic, and few Helium instructions can perform more than two  $32\times32\to64$  long multiplications. For Toom-Cook/Karatsuba based multiplication, we operate on 16-bit lanes, hence get a theoretical speedup of  $8\times$  compared to scalar code. However, optimized implementations on the Cortex-M4 processor already leverage the DSP extension to treat 32-bit registers as  $2\times16$ -bit vectors and thus operate on two 16-bit values at once, if possible. We therefore expect a speedup somewhere between  $4\times$  and  $8\times$ . Considering that NTT-based polynomial and matrix-vector multiplication for the Saber rings is around  $2\times$  as fast as Toom-Cook/Karatsuba based routines [CHK+21, Table 5], it is not entirely clear which approach will be faster when implemented based on the Helium vector extension.

## 6.2 Vectorizing striding Toom-Cook/Karatsuba

Recall that 4-way Toom-Cook evaluation is a matrix-vector multiplication

$$R^{7\times4} \times R^{4\times(n/4)} \longrightarrow R^{7\times(n/4)}, \quad R = \mathbb{Z}_{2^{16}},$$

with every sub-matrix-vector multiplication  $R^{7\times 4}\times R^4\to R^7$  corresponding to one evaluation transformation. We vectorize this by computing one sub-matrix-matrix multiplication  $R^{7\times 4}\times R^{4\times \ell}\to R^{7\times \ell}$  a time, storing the four rows of the input  $R^{4\times \ell}$  and the 7 rows of the output  $R^{7\times \ell}$  in one vector register each. We find that by overwriting input registers as soon as they are no longer needed, the 8 vector registers available are sufficient for the transformation. With 128-bit vectors, we compute  $\ell=\frac{128}{16}=8$  evaluations at once.

The above vectorization approach works for both classical and striding Toom-Cook. However, in the case of striding Toom-Cook, we need to de-interleave the input at stride 4 first, for which we leverage the de-interleaving load instruction VLD4{0-3}.

The interleaving of memory operations and arithmetic is crucial to leverage instruction overlapping. We achieve this by optimizing the evaluation across loops, using preloading and late storing of input and results. The preloading becomes more challenging for striding Toom-Cook, where we can use VLD4{0-3} only once we have four free vector registers available. Listing 1 shows one loop of our vectorized Toom-Cook evaluation.

We turn to the implementation of Toom-Cook interpolation: As for evaluation, we vectorize interpolation by computing 8 interpolations at once, keeping the 7 input/output rows in one vector each and leveraging the interleaving-store VST4{0-3} for the striding. We're using the interpolation sequence from [KMRV18].

At the end of the interpolation, we have  $f_0, \dots f_6 \in \mathbb{Z}_{2^{13}}[X^4]/(X^n+1)$  such that

$$\sum_{i} f_i X^i = (f_0 + X^4 f_4) + (f_1 + X^4 f_5) X + (f_2 + X^4 f_5) X^2 + (f_3 + X^4 f_6) X^3$$

```

1 vld43.u16 {Q0,Q1,Q2,Q3}, [r0]

1 ldrd r9, r7, [r1, #48]

2 vadd.u16 Q7, Q0, Q2

2 vmla.u16 Q3, Q6, r10

3 vstrw.u32 Q6, [r14,#(-32)]

3 vshlc Q2, r12, #16

4 vadd.u16 Q6, Q1, Q3

4 vmla.u16 Q2, Q4, r5

5 vstrw.u32 Q5, [r0,#(-32)]

5 vshlc Q3, r12, #16

6 vsub.u16 Q5, Q7, Q6

6 vmla.u16 Q3, Q4, r7

7 vstrw.u32 Q4, [r0,#(-48)]

7 vshlc Q5, r12, #16

8 \text{ vmla.u16 Q7, Q0, } \text{r10}

8 vmla.u16 Q2, Q7, r7

9 vstrw.u32 Q5, [r0,#(48)]

9 ldrd r10, r8, [r1, #8]

10 vmla.u16 Q5, Q6, r11

10 vmla.u16 Q3, Q6, r5

11 vstrw.u32 Q0, [r0], #64

11 vshlc Q2, r12, #16

12 vmla.u16 Q6, Q1, r10

12 vmla.u16 Q2, Q4, r6

13 vstrw.u32 Q3, [r14,#(32)]

13 vshlc Q3, r12, #16

14 vadd.u16 Q4, Q5, Q1

14 vmla.u16 Q3, Q4, r9

15 vstrw.u32 Q5, [r14],

15 vshlc Q5, r12, #16

_{\rm 16} vmla.u16 Q4, Q2, r10

16 vmla.u16 Q2, Q7, r9

17 vmla.u16 Q4, Q3, r9

```

Listing 1 Striding Toom-Cook evaluation

Listing 2 Schoolbook multiplication

is the polynomial we're looking for. Each  $X^4 \cdot f_{4+k}$  amounts to a negacyclic rotation of  $f_{4+k}$ , which we compute gradually within the interpolation loop, using VSHLC to shift one 128-bit block after each iteration, and remembering the carry-out as the carry-in for the next iteration. This requires the use of three more general purpose registers for carries.

The interpolation sequence from [KMRV18] is very add/sub-heavy, leading to inevitable stalls on a dual-beat system when implemented as written. We experimented with replacing VADD, VSUB by VMLA with constants  $\pm 1$ , but were limited by the pressure on the GPR file. It is left for future work to optimize this further.

#### 6.3 Schoolbook

We consider multiplication in  $\mathbb{Z}_{2^{16}}[X]/(X^k+1)$ . While previous vectorized implementations use batch-multiplication, our algorithm vectorizes a single schoolbook multiplication. To our knowledge, the approach is novel, and rests on the shift-with-carry instruction VSHLC.

**Outline** We outline the algorithm for k = 16. We can write

$$a = (a_0 + a_8 X^8) X^0 + (a_1 + a_9 X^8) X^1 + \ldots + (a_7 + a_{15} X^8) X^7 = \sum_{i} (a_i + a_{8+i} X^8) X^i,$$

hence  $ab = \sum_{i} [(a_i + a_{8+i}X^8)b] X^i$ . We will now separately discuss the following:

- How to efficiently compute one subproduct  $(a_i + a_{8+i}X^8)b$  in the sum. We will express this as an 8-fold batch multiplication over  $\mathbb{Z}_{2^{16}}[X]/(X^2+1)$ .

- How to shift + accumulate in the sum. We will express this as an iteration of addition and negacyclic rotation, similar to a linear feedback shift register.

**Subproduct computation** We write  $b = \sum_i (b_i + b_{8+i}X^8)X^i$  as before, and hence obtain  $(a_i + a_{8+i}X^8)b = \sum_j (a_i + a_{8+i}X^8)(b_j + b_{8+j}X^8)X^j$ . Now, note that  $\mathbb{Z}_{2^{16}}[X^8]/(X^{16} + 1)$  is a subring of  $\mathbb{Z}_{2^{16}}[X]/(X^{16} + 1)$  isomorphic to the "complex numbers"  $\mathbb{Z}_{2^{16}}[Y]/(Y^2 + 1)$  — we therefore have to compute a batch multiplication in  $\mathbb{Z}_{2^{16}}[Y]/(Y^2 + 1)$  of the fixed  $a_i + a_{8+i}Y$  with the varying  $b_i + b_{8+i}Y$ ,  $j = 0, 1, \ldots, 7$ .

This batch multiplication is easy to vectorize: If  $a_i$  and  $a_{8+i}$  are in GPRs  $a_0$ ,  $a_1$ , and  $b_0, \ldots, b_7$  and  $b_8, \ldots, b_{15}$  are in vectors  $b_0$  and  $b_1$ , we only have to calculate a scalar-vector  $2 \times 2$  schoolbook multiplication  $(a_0 + a_1 Y)(b_0 + b_1 Y) = (a_0 b_0 - a_1 b_1) + Y(a_0 b_1 + a_1 b_0)$ . This

uses 2 GPRs for the a, 2 vector registers for the b, and 2 vector registers for the output. Multiplication is done via VMUL.u16 / VMLA.u16. Since there is no multiply-subtract variant of VMLA.u16, the computation of  $-a_1b_1$  requires flipping the sign of  $a_0$  or  $b_1$ .

**Accumulation** We need to compute the sum  $ab = \sum_i \left[ (a_i + a_{8+i}X^8)b \right] X^i$ . and discussed how to compute an individual product  $(a_i + a_{8+i}X^8)b$ . We now consider how to sum them. Since  $\cdot X$  is a negacyclic shift, computing  $[(a_i + a_{8+i}X^8)b]X^i$  from  $(a_i + a_{8+i}X^8)b$  means a negacyclic shift of i positions. This doesn't map well to MVE because the maximum shift amount of VSHLC is 32 bits, hence two 16-bit coefficients. Instead, setting  $\mathbf{a}_i := a_i + a_{8+i}X^8$ , we can rewrite the sum as follows:

$$ab = \sum_{i} [\mathbf{a}_{i}b] X^{i} = \mathbf{a}_{0}b + (\mathbf{a}_{1}b + (\dots + (\mathbf{a}_{6}b + (\mathbf{a}_{7}b + 0)X) \dots X)X)$$

Here, we only shift by X, corresponding to a VSHLC Qd, Ra, #16. Moreover, we can handle the sum through multiply-accumulates in the schoolbook subroutine computing  $\mathbf{a}_i b + \underline{\phantom{a}}$ .

**Implementation considerations** We describe how to map the above algorithm to the Helium instruction set and the microarchitecture of the Cortex-M55 processor.

First, consider a rotation  $(b_0,\ldots,b_{15})\mapsto (-b_{15},b_0,\ldots,b_{14})$ , where b is stored in vector registers  $b_0=(b_0,\ldots,b_7)$  and  $b_1=(b_8,\ldots,b_{15})$ : To begin, two chained invocations of VSHLC with carry GPR c yield  $b_0'=(c_{\mathrm{old}},b_0,\ldots,b_6)$  and  $b_1'=(b_7,\ldots,b_{14})$ , with  $c_{\mathrm{new}}=b_{15}$  (in-carry and out-carry in VSHLC use the same GPR). After that,  $-c_{\mathrm{new}}=-b_{15}$  has to be fed back into  $b_0'$ . We implement this lazily by buffering  $c_{\mathrm{new}}$  in a vector  $C=(0,\ldots,0,c)$  and deferring correcting  $b_0'$ . If C is initially C0, we can simultaneously store C0 and clear it via VSHLC. We only need to correct  $c_0$ 0 once after the full loop.

A standalone implementation of the anticyclic shift would not perform well on a dual-beat system like the Cortex-M55 processor, because consecutive invocations of VSHLC would stall. We will revisit this after studying the nature of each subproduct computation.

Each subproduct involves the following: Firstly, loading of a-input in two GPRs, ideally using LDRD to load a pair of GPRs at once. Secondly,  $4 \times$  multiply via VMUL.u16 or VMLA.u16. Thirdly, a sign flip in a or b. The lowest instruction count is offered by storing  $-b_1$  in another vector throughout the loop. Flipping a adds a 1-instruction overhead, but releases pressure on the vector file. At best, we get  $1 \times LDRD$  and  $3 \times VMLA$  per subproduct.

As for the negacyclic shift, a naïve implementation would perform poorly on a dual-beat system because consecutive invocations of VMLA would stall. However, we found that interleaving subproduct and shift leads to good overlapping and resource utilization on the Cortex-M55 processor. We show an iteration of the core loop in Listing 2.

**Variants** There is a variant computing the rotation abX instead of ab: We write

$$aX = (a_0 + a_8 X^8) X^1 + (a_1 + a_9 X^8) X^2 + \dots + (a_7 + a_{15} X^8) X^8$$

=  $(-a_{15} + a_7 X^8) + (a_0 + a_8 X^8) X^1 + \dots + (a_6 + a_{14} X^8) X^7$

and apply the same multiply-accumulate strategy as before. The rotation in the a-input is easy to express through modified immediate offsets in the GPR loads.

Secondly, consider what happens when we accumulate onto the destination vector in the first iteration. Since the result of first iteration gets shifted 7 times subsequently, this computes  $ab + cX^7$ , where c is the polynomial previously stored in the destination vectors.

The previous points allow for efficient integration of  $16 \to 32$  Karatsuba interpolation with degree-16 schoolbook multiplication: Recall that we have to compute  $(f_{\rm e}g_{\rm e}+Xf_{\rm o}g_{\rm o})+X(f_{\rm s}g_{\rm s}-f_{\rm e}g_{\rm e}-f_{\rm o}g_{\rm o})$ . We avoid any manual shift of  $f_{\rm o}g_{\rm o}$  here by computing  $Xf_{\rm o}g_{\rm o}$  first, and then using the multiply-accumulate variant for  $f_{\rm s}g_{\rm s}-f_{\rm o}g_{\rm o}=f_{\rm s}g_{\rm s}+X^7(X^8\cdot(Xf_{\rm o}g_{\rm o}))$ : Here,  $Xf_{\rm o}g_{\rm o}$  is known, and  $\cdot X^8$  is a single sign-flip and some re-indexing.

#### 6.3.1 Integrating Toom-Cook, Karatsuba, and Schoolbook

We implement a degree 256 negacyclic polynomial through a combination of one layer of 4-way Toom-Cook for degree  $256 \rightarrow 64$  reduction, one layer of Karatsuba for degree  $32 \rightarrow 16$  reduction, and an integrated  $32 \leftrightarrow 16$  followed by  $16 \times 16$  schoolbook. We found this variant slightly more efficient than an implementation of degree-32 schoolbook.

#### 6.4 Number Theoretic Transform

| Algorithm 3: Barrett reduction – MVE                                                                                                                                                                                     | Algorithm 4: Montgomery multiplication – MVE                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| In: Modulus $n < 2^{32}$ , $ z  < 2^{31}$<br>Out: Barrett reduction of $z$ w.r.t. $n$ .<br>1: VQRDMULH.s32 $t$ , $z$ , $\left\lfloor \frac{2^{\ell}}{2n} \right\rfloor$<br>2: VMLA.s32 $z$ , $t$ , $-n$<br>3: return $z$ | In: $n < 2^{32}$ , $ a ,  b  < 2^{31}$ , $\omega \equiv n^{-1} \mod 2^{32}$<br>Out: Representative $h$ of $ab/2^{32}$ modulo $n$<br>1: V[QD] MULH. s32 $h$ , $a$ , $b$<br>2: VMUL. u32 $l$ , $a$ , $b$<br>3: VMUL. u32 $l$ , $l$ , $\omega$<br>4: V[QD] MULH. s32 $l$ , $l$ , $l$ |

#### 6.4.1 Modular Arithmetic

Montgomery multiplication Algorithm 4 shows two implementations of single-width Montgomery multiplication (Algorithm 2), one using the multiply-high instruction VMULH.s32, whose functional effect is  $a,b\mapsto \left\lfloor\frac{ab}{2^{32}}\right\rfloor$ , the other the doubling multiply-high instruction VQDMULH.s32 from fixed-point arithmetic, whose functional effect is  $a,b\mapsto \left\lfloor\frac{2ab}{2^{32}}\right\rfloor$ . In the latter case, the doubling can be corrected through a halving subtraction VHSUB.s32 in the last instruction. We mention the fixed-point variant for two reasons: Firstly, because VQDMULH has a scalar-vector variant where one vector is constant. This is useful for the VQDMULH.s32 c,l,n step, where n is a constant which we'd ideally store in a GPR rather than a vector. Secondly, the fixed-point variant can be improved to 4 and 3 instruction Montgomery multiplication variants, which we discuss now.

| Algorithm 5: Montgomery multi-                            | Algorithm 6: Montgomery multipli-                                |

|-----------------------------------------------------------|------------------------------------------------------------------|

| plication via rounding – MVE                              | cation via rounding, constant – $MVE$                            |

| In: Odd $n < 2^{32}$ , $ a ,  b  < 2^{31}$ , <u>b odd</u> | In: Odd $n < 2^{32}$ , $ a ,  b  < 2^{31}$ , $\underline{b}$ odd |

| In: $\omega \equiv -n^{-1} \mod 2^{32}$ precomputed       | In: $b' \equiv -bn^{-1} \mod 2^{32}$ precomputed                 |

| <b>Out:</b> Representative h of $ab/2^{31}$ modulo n      | <b>Out:</b> Representative h of $ab/2^{31}$ modulo n             |

| 1: VQRDMULH.s32 $h,\ a,\ b$                               | 1: VQRDMULH.s32 $h,\ a,\ b$                                      |

| $2$ : VMUL.u32 $l,\ a,\ b$                                | 2: VMUL.u32 $l, a, b'$                                           |

| 3: VMUL.u32 $l, l, \omega$                                | 3: VQRDMLAH.s32 $h, l, n$                                        |

| 4: VQRDMLAH.s32 $h, l, n$                                 |                                                                  |

Algorithm 5 shows a variant of Algorithm 4 where the subtraction step VHSUB has been merged with the high multiply VQDMULH.s32 into a single doubling multiply-high-rounding with accumulate instruction VQRDMLAH.s32, leveraging  $\frac{v+w}{2^l} = \left\lfloor \frac{v}{2^\ell} \right\rceil + \left\lfloor \frac{w}{2^\ell} \right\rceil$  for any two  $v, w < 2^\ell$  s.t.  $v \equiv -w \not\equiv 2^{\ell-1}$  modulo  $2^\ell$ , the case  $2^{\ell-1}$  being excluded by the important new assumption that b is odd. This variant of Montgomery multiplication has been communicated with the authors of [BHK<sup>+</sup>], and is explored in greater detail in loc.cit. alongside other improvements to modular arithmetic.

**Barrett reduction** Algorithm 3 implements Barrett reduction (Algorithm 1). Two things are noteworthy: Firstly, we have merged the multiplication  $c \leftarrow n \cdot t$  and the subtraction z-c into a single multiply-accumulate VMLA. Secondly, since VQRDMULH.s32 computes  $\left\lfloor \frac{2ab}{2^{32}}\right\rfloor$ , not  $\left\lfloor \frac{ab}{2^{32}}\right\rfloor$ , we use  $2\left\lfloor \frac{2^\ell}{2n}\right\rfloor$  as the approximation to  $\frac{2^\ell}{n}$  instead of  $\left\lfloor \frac{2^\ell}{n}\right\rfloor$  in Algorithm 1. The theoretical implications of this modification are studied in greater detail in [BHK<sup>+</sup>].

**Central reduction** After the inverse NTT, we need to normalize to signed canonical representatives in  $\{-\lfloor \frac{q}{2} \rfloor, \ldots, \lfloor \frac{q}{2} \rfloor\}$ . Assuming we are already given a signed representative in the range  $\{-q+1,\ldots,q-1\}$ , this can be achieved by two conditional additions of  $\pm q$ . In Helium, we implement central reduction using lane predication. See Algorithm 7.

#### 6.4.2 Forward NTT

We compute two layers of radix-2 butterflies at once, using 4 vectors for the butterfly and leaving 4 for intermediate results and loop optimization (pre-load, late-store). Merging three layers would require register spilling, so we have not implemented it. See Algorithm 8.

We implement Montgomery multiplication via the 3-instruction rounding strategy Algorithm 6, choosing odd representatives for the  $\zeta_i$  and their twists  $\zeta_i'$ . For NTT layers 0 to 5, we keep the modulus and root constants in 7 GPRs, reducing the pressure on the vector file and taking advantage of the scalar-vector instructions. For the last two NTT layers, where each size-4 butterfly operates on consecutive 32-bit elements, we use the de-interleaving load VLD4{0-3} and compute four size-4 butterflies at once. In this case, we require 6 vectors for the root constants, in addition to the 4 input vectors. However, we find that with careful register management, the total of 8 vector registers is sufficient.

```

Algorithm 8: Size-4 NTT Cooley-Tukey butterfly

In: a_0, a_1, a_2, a_3, \zeta_0, \zeta_1, \zeta_2 \in \mathbb{F}_q

Out: Radix-4 butterfly of (a_i) w.r.t. \zeta_j.

1: a_2 \leftarrow \zeta_0 a_2, a_3 \leftarrow \zeta_0 a_3

> Montgomery

2: (a_0, a_2) \leftarrow (a_0 + a_2, a_0 - a_2), (a_1, a_3) \leftarrow (a_1 + a_3, a_1 - a_3)

> Add-Sub

3: a_1 \leftarrow \zeta_1 a_1, a_3 \leftarrow \zeta_2 a_3

> Montgomery

4: (a_0, a_1) \leftarrow (a_0 + a_1, a_0 - a_1), (a_2, a_3) \leftarrow (a_2 + a_3, a_2 - a_3)

> Add-Sub

```

To leverage instruction overlapping, it is vital to interleave the Montgomery multiplications – consisting of multiplications only – and the add/sub steps – consisting of addition operations only. Moreover, since there are 6 multiplications but only 4 addition/subtraction operations, we also interleave loads/stores in order to achieve a stall-free execution.

#### 6.4.3 Point multiplication for full NTT

For the point multiplication in  $\mathbb{F}_q^n$ , our measured code uses Algorithm 4. We comment on the possibility of using the shorter Algorithm 5: This algorithm is only applicable if one of the inputs is odd. Here, the following trick can be applied:

**Proposition 1.** Assume a Montgomery multiplication routine for the NTT which produces only even representatives. Then, if  $(x_s)$  is an input vector to the NTT, all entries of its NTT transform have the same parity, which agrees with the parity of the representative  $x_0$ . In particular, if  $x_0$  is odd, then all entries in the NTT transform of  $(x_s)$  are odd.

*Proof.* Consider the first layer: If n is the size of the NTT, each pair  $(a = x_r, b = x_{r+n/2})$  of elements in the lower and upper half is transformed via  $(a, b) \mapsto (a + \zeta b, a - \zeta b)$ . By assumption,  $\zeta b$  is represented by an even integer, so at the end of layer 0, the parity of the elements in the lower half has not changed, and the parity of elements in the upper half is the same as the parity of the corresponding lower half element. Continue inductively.  $\Box$

As long we ensure that  $x_0$  is odd initially, we can therefore force all outputs of the NTT to have only odd entries, and thus be suitable for our accelerated point multiplication via Algorithm 5. We leave it for future work to explore the use of this trick further.

#### 6.4.4 Point multiplication for partial NTT

When implementing multiplication in  $\mathbb{F}_q[X]/(X^{256}+1)$  using a 6-layer incomplete NTT, the base multiplication is in  $\mathbb{F}_q[X]/(X^4-\zeta)$ . For this, [CHK<sup>+</sup>21] relies on UMLAL to reduce the number of Montgomery reductions by operating in double-width values as long as possible. The AVX2 code from [CHK<sup>+</sup>21] implements a batched version of this strategy.

As mentioned in Section 3.1, batched implementations are difficult to realize in the Helium instruction set due to the lower number of vectors. A batched multiplication in  $\mathbb{F}_q[X]/(X^4-\zeta)$  would need at least 4+4+4 vectors for the two inputs and the output. Instead, we vectorize a single multiplication in  $\mathbb{F}_q[X]/(X^4-\zeta)$  as follows: For inputs  $a=a_0+a_1X+a_2X^2+a_3X^3$  and  $b=b_0+b_1X+b_2X^2+b_3X^3$ , we first prepare the reversed and expanded array of 32-bit values  $b_3,b_2,b_1,b_0,\zeta b_3,\zeta b_2,\zeta b_1$  in memory. We can then compute the coefficients of ab as dot products of  $[a_0,a_1,a_2,a_3]$  with length-4 subvectors of the expanded array, each of which can be computed with a single invocation of the long-multiply-accumulate-across instruction VMLALDAV.s32. For example, the  $X^2$ -coefficient of ab is  $[a_0,a_1,a_2,a_3] \cdot [b_2,b_1,\zeta b_3,\zeta b_2]$ . Like UMLAL, VMLALDAV.s32 accumulates into a pair of GPRs. We compute all coefficients of ab in pairs of GPRs each, before moving them into a vector using VMOV Qx[i], Qx[j], Ra, Rb and applying a single Montgomery reduction.

The main drawbacks of this approach are the following: Firstly, we need four loads for b; a batched implementation would have only one load per input. This can be amortized by simultaneously computing multiple  $a_ib$ ; we have not yet implemented this approach, yet. Secondly, the cost of preparing  $b_3, b_2, b_1, b_0, \zeta b_3, \zeta b_2, \zeta b_1$ . Following an approach similar to [BHK<sup>+</sup>] and adapted to this context, this cost can be partly amortized in the application to matrix-vector multiplication, by precomputing  $b_3, b_2, b_1, b_0, \zeta b_3, \zeta b_2, \zeta b_1$  as part of the forward NTT for the vector entries. In Section 7 below, this size-doubling version of the NTT is called "expanded NTT". We find that the above schoolbook multiplication strategy offers a good mix of different kinds of operations which can be interleaved to leverage instruction overlapping.

### 6.4.5 Inverse NTT

We use Gentleman-Sande butterflies  $(a, b) \mapsto (a + b, \zeta(a - b))$ , which we compute using interleaved add/sub sequences and the 3-instruction Montgomery multiplication as in the forward-NTT. Overflow is prevented through the addition of selected Barrett reductions.

The GS butterflies are inverse to the CT butterflies only up to a factor of 2, which we need to compensate through a modular division in/after the inverse NTT. We also need to account for the Montgomery twist by  $2^{-31} \in \mathbb{F}_q$  in the point multiplication. We merge half of the required scalings with the multiplications in the last-layer GS butterflies. For the other half, we add explicit Montgomery multiplications. One could integrate the scalings

into the GS butterflies for all but the first coefficient with a trick similar to Proposition 1; however, we would need explicit Barrett reductions at the end of the last layer in this case, which would only be one instruction shorter than the Montgomery multiplications.

### 6.5 Hashing

We have not attempted to develop hashing implementations based on the Helium vector extension: Both the smaller scale nature of Cortex-M CPUs and the fact that software executes directly in the physical address space (without virtual to physical translation) mean that the overhead associated with offloading computation to accelerators is very low. As a result, many Cortex-M microcontrollers already include accelerators for symmetric cryptography and hashing. It is expected that these accelerators will be used for the hashing in PQC schemes, eliminating the need for high performance software-based hashing.

"90's versions" Numerous PQC schemes offer a "90's version" replacing the use of SHA-3 by AES and SHA-2, and it has been discussed whether NIST should standardize those versions. We support NIST standarizing "90's versions": Firstly, many existing MCUs already have hardware acceleration for AES and SHA-2. Secondly, AES and SHA-2 won't go away anytime soon, and limited gate budget may prevent vendors from shipping MCUs with both SHA-2 and SHA-3 acceleration. Finally, SHA-2 is a faster software-fallback for systems which do not have have any hardware acceleration for hashing.

|            |     | Onemation | Cor         |                         | Cortex-M55 |        |        |

|------------|-----|-----------|-------------|-------------------------|------------|--------|--------|

|            |     | Operation | NTT         | $\mathrm{TC}^{\dagger}$ | TC         | TC     | NTT    |

|            |     |           | $[CHK^+21]$ | 10,                     | [This]     | [This] | [This] |

|            |     | KeyGen    | 294k        | 377k                    | 367k       | 244k   | 232k   |

|            | CPA | Encaps    | 330k        | 440k                    | 425k       | 250k   | 233k   |

| LightSaber |     | Decaps    | 58k         | 101k                    | 96k        | 22k    | 20k    |

| Lightbaber |     | KeyGen    | 360k        | 443k                    | 433k       | 308k   | 296k   |

|            | CCA | Encaps    | 513k        | 622k                    | 607k       | 429k   | 412k   |

|            |     | Decaps    | 498k        | 631k                    | 612k       | 378k   | 358k   |

|            | CPA | KeyGen    | 554k        | 759k                    | 737k       | 466k   | 436k   |

|            |     | Encaps    | 606k        | 858k                    | 829k       | 480k   | 442k   |

| Saber      |     | Decaps    | 79k         | 142k                    | 135k       | 30k    | 27k    |

| Dabei      | CCA | KeyGen    | 658k        | 862k                    | 840k       | 568k   | 538k   |

|            |     | Encaps    | 864k        | 1115k                   | 1086k      | 735k   | 697k   |

|            |     | Decaps    | 835k        | 1128k                   | 1091k      | 655k   | 615k   |

|            |     | KeyGen    | 879k        | 1260k                   | 1222k      | 750k   | 693k   |

|            | CPA | Encaps    | 947k        | 1395k                   | 1346k      | 772k   | 706k   |

| Firesaber  |     | Decaps    | 101k        | 184k                    | 174k       | 40k    | 36k    |

| rnesabel   |     | KeyGen    | 1008k       | 1389k                   | 1350k      | 877k   | 820k   |

|            | CCA | Encaps    | 1255k       | 1703k                   | 1654k      | 1077k  | 1011k  |

|            |     | Decaps    | 1227k       | 1732k                   | 1674k      | 985k   | 914k   |

$\dagger$  Saber implementation from [KRSS] using Toom-Cook for polynomial multiplication instead of NTT.

Table 2 Comparison of Toom-Cook and NTT-based implementations of Ind-CPA and Ind-CCA versions of the NIST PQC finalist Saber. SW-based hashing waters down optimizations for polynomial multiplication, but is expected to be HW-accelerated in practice, see Section 6.5.

|                                    | NTT-based polynomial multiplication |         |        |                         |         |               |          |      |         |

|------------------------------------|-------------------------------------|---------|--------|-------------------------|---------|---------------|----------|------|---------|

|                                    | NTT                                 |         | inv    | NTT Base multiplication |         | ultiplication | Poly-Mul |      |         |

|                                    | Full                                | Partial | Expand | Full                    | Partial | Point         | deg-4    | Full | Partial |

| Cortex-M4<br>[CHK <sup>+</sup> 21] | _                                   | 5794    | -      | _                       | 7791    | _             | 3886     | -    | _       |

| Cortex-M55<br>[This work]          | 2027                                | 1473    | 1835   | 2559                    | 1940    | 569           | 1151     | 7194 | 6411    |

Table 3 Comparing different stages of NTT multiplication for Saber. "Expand" is the NTT-variant discussed in Section 6.4.4.

|             | Toom-Cook/Karatsuba based polynomial multiplication |                      |            |           |  |  |  |

|-------------|-----------------------------------------------------|----------------------|------------|-----------|--|--|--|

|             | Evaluation                                          | Interpolation        | Schoolbook | Poly-Mul  |  |  |  |

|             | $256 \rightarrow 32$                                | $32 \rightarrow 256$ | (32x32)    | roiy-wiii |  |  |  |

| Cortex-M55  | 289+330                                             | 370+531              | 267        | 7790      |  |  |  |

| [This work] | = 619                                               | = 901                | 207        | 1190      |  |  |  |

|             | Evaluation                                          | Interpolation        | Schoolbook | Poly-Mul  |  |  |  |

|             | $256 \rightarrow 16$                                | $16 \rightarrow 256$ | (16x16)    | rory-wrur |  |  |  |

| Cortex-M4   | 2188 + 7x(3x128 + 260)                              | 7x(3x91+179)+3187    | 302        | 34884     |  |  |  |

| [This work] | = 6696                                              | = 6351               | 302        | 34004     |  |  |  |

Table 4 Performance of polynomial multiplication based on Toom-Cook/Karatsuba. Sum-decompositions refer to shares of Toom-Cook/Karatsuba during interpolation/evaluation.

### 7 Results

## 7.1 Development setup

Benchmarking the Cortex-M4 processor We have developed our code based on the pqm4 framework [KRSS]. We have focused our development on polynomial multiplication only without optimizing other operations in Saber. To measure the performance, we have executed the benchmark environment provided by pqm4 on a STM32F4 Discovery board featuring a 32-bit Arm Cortex-M4 with FPU core, 1MB of Flash, and 192KB of RAM.

Benchmarking for the Cortex-M55 processor We have developed our code using the Fixed Virtual Platform (FVP) for the Arm® Corstone®-300 MPS2¹, containing a functional model of the Cortex-M55 CPU. To measure performance, we have used a cycle-accurate model of the Cortex-M55r1 CPU which can currently be obtained from Arm under license and NDA. An FPGA image including the Cortex-M55r1 CPU is expected to be publicly released by the end of 2021; an image including the Cortex-M55r0 CPU is already available².

Code generation We have developed most of our Helium as well as Cortex-M4 assembly with the help of a small Python-based code-generation framework, similar to [KRS19]. The main tasks the framework performs are register management and address offset calculations when loading contiguous or scattered buffers. While the final assembly can possibly be written by hand, we found the tool useful for quick experimentation with different approaches. For very simple code-sequences, such as the Karatsuba algorithm or NTT base multiplication, we have written the assembly by hand. The code-generation tool will be made available with the paper upon publication.

$<sup>^1</sup> Freely \ available \ at \ https://developer.arm.com/tools-and-software/open-source-software/arm-platforms-software/arm-ecosystem-fvps$

<sup>&</sup>lt;sup>2</sup>https://developer.arm.com/tools-and-software/development-boards/fpga-prototyping-boards contains more information on prototyping boards and FPGA images.

|       | Matrix-Vector Multiplication |              |         |           |                |         |

|-------|------------------------------|--------------|---------|-----------|----------------|---------|

|       |                              | NTT          |         | Toom      | -Cook + Karats | uba     |

| Dim   | Cortex-M4                    | Cortex-M55r1 | Chardyn | Cortex-M4 | Cortex-M55r1   | Speedup |

| DIIII | $[CHK^+21]$                  | (this work)  | Speedup | [MKV20]   | (this work)    | speedup |

| l=2   | 66k                          | 18.4k        | 3.5x    | 159k      | 28.1k          | 5.6x    |

| l=3   | 125k                         | 35.9k        | 3.4x    | 317k      | 61.6k          | 5.1x    |

| l=4   | 205k                         | 58.9k        | 3.4x    | 528k      | 107.7k         | 4.9x    |

Table 5 Comparison of different approaches for Matrix-Vector multiplication.

|            | NTT [CHK <sup>+</sup> 21] | TC classical <sup>†</sup> | TC striding [This]   |

|------------|---------------------------|---------------------------|----------------------|

|            | KeyGen/Encaps/Decaps      | KeyGen/Encaps/Decaps      | KeyGen/Encaps/Decaps |

| LightSaber | 5,3 / 5,3 / 5,3 KB        | 6,1 / 6,0 / 6,0 KB        | 4,3 / 4,3 / 4,3 KB   |

| Saber      | 6,4 / 6,3 / 6,3 KB        | 6,6 / 6,5 / 6,6 KB        | 4,8 / 4,8 / 4,8 KB   |

| FireSaber  | 7.4 / 7.3 / 7.4  KB       | 7,1 / 7,1 / 7,1 KB        | 5,3 / 5,3 / 5,3 KB   |

$<sup>\</sup>dagger$  Saber implementation from [KRSS] using Toom-Cook for polynomial multiplication instead of NTT.

Table 6 Comparison of the memory utilization of Saber on Cortex-M4 processor when implementing different polynomial multiplication algorithms.