# Rocca: An Efficient AES-based Encryption Scheme for Beyond 5G<sup>\*</sup>

Kosei Sakamoto<sup>1</sup> and Fukang Liu<sup>1</sup> and Yuto Nakano<sup>2</sup> and Shinsaku Kiyomoto<sup>2</sup> and Takanori Isobe<sup>1,3,4</sup>

<sup>1</sup> University of Hyogo, Kobe, Japan. takanori.isobe@ai.u-hyogo.ac.jp,

liufukangs@gmail.com, k.sakamoto0728@gmail.com

<sup>2</sup> KDDI Research, Fujimino, Japan. yuto@kddi-research.jp, kiyomoto@kddi-research.jp

<sup>3</sup> NICT, Tokyo, Japan

<sup>4</sup> PRESTO, Japan Science and Technology Agency, Tokyo, Japan

Abstract. In this paper, we present an AES-based authenticated-encryption with associated-data scheme called Rocca, with the purpose to reach the requirements on the speed and security in 6G systems. To achieve ultrafast software implementations, the basic design strategy is to take full advantage of the AES-NI and SIMD instructions as that of the AEGIS family and Tiaoxin-346. Although Jean and Nikolić have generalized the way to construct efficient round functions using only one round of AES (aesenc) and 128-bit XOR operation and have found several efficient candidates, there still seems to exist potential to further improve it regarding speed and state size. In order to minimize the critical path of one round, we remove the case of applying both aesenc and XOR in a cascade way for one round. By introducing a cost-free block permutation in the round function, we are able to search for candidates in a larger space without sacrificing the performance. Consequently, we obtain more efficient constructions with a smaller state size than candidates by Jean and Nikolić. Based on the newly-discovered round function, we carefully design the corresponding AEAD scheme with 256-bit security by taking several reported attacks on the AEGIS family and Tiaxion-346 into account. Our AEAD scheme can reach 150 Gbps which is almost 5 times faster than the AEAD scheme of SNOW-V. Rocca is also much faster than other efficient schemes with 256-bit key length, e.g. AEGIS-256 and AES-256-GCM. As far as we know, Rocca is the first dedicated cryptographic algorithm targeting 6G systems, i.e., 256-bit key length and the speed of more than 100 Gbps.

Keywords: AES-NI, Fast Software Implementation, 6G, AEAD

<sup>\*</sup> This is an updated and extended version from conference version [SLN<sup>+</sup>21].

### 1 Introduction

#### 1.1 Background

The fifth-generation mobile communication systems (5G) have been launched in several countries for commercial services since 2020. Besides, researches for beyond-5G or 6G have been already started in some research institutes. As the first white paper of 6G, [LaL19] was published by the 6Genesisi project in 2019, which is mainly organized by the University of Oulu in Finland. In the white paper, several requirements for 6G systems are raised. For the data transmission speed, it says that 6G achieves more than 100 Gbps, which is more than 10 times faster than that of 5G.

For the 4G system, as underlying cryptographic algorithms to ensure confidentiality and integrity, SNOW 3G [SAG06], AES [Nat01], and ZUC-128 [SAG11] are employed, which are specified as 128-EEA1 (EIA1), 128-EEA2 (EIA2), 128-EEA3 (EIA3), respectively, and these algorithms are also selected cryptographic algorithms for the 5G system as 128-NEA1 (NIA1), 128-NEA2 (NIA2), 128-NEA3 (NIA3). However, for the 5G system, the 3GPP standardization organization requires to increase the security level to 256-bit key lengths. In 2018, ZUC-256 [The18] was proposed as the 256-bit key version of ZUC-128. ZUC-256 was revised only in the initialization phase and in the MAC generation phase from ZUC-128. By this revise, ZUC-256 improves the security level against the keyrecovery attack to the 256-bit security from the 128-bit security. On the other hand, the performance of the encryption/decryption speed is not quite improved because the key-stream generation phase is the same as ZUC-128, and a structural weakness was found [YJM20]. In FSE 2020, Ekdahl et al. proposed SNOW-V that is the 256-bit key version of SNOW 3G, and they showed that SNOW-V achieves more than 38 Gbps at an AEAD (Authenticated Encryption with Associated Data) mode on OpenSSL [EJMY19]. The performances of SNOW-V are sufficient for them to be used in the 5G system.

However, when taking requirements in 6G systems into account, we have to tackle some challenges. The biggest one is the encryption/decryption speed. For 6G systems, as the data transmission speed is expected to reach more than 100 Gbps, we have to design a cryptographic algorithm with the encryption/decryption speed of more than 100 Gbps, which is at least three times faster than SNOW-V. Besides, achieving 256-bit security against key-recovery attacks is essential as in 5G systems [3GP18]. In addition, due to the increase of data transmissions in 6G systems, it is necessary to ensure at least 128-bit security against distinguishing attacks while SNOW-V only claims 64-bit security against distinguishing attacks. Therefore, there is no doubt that a new cryptographic algorithm is needed in 6G systems.

For symmetric-key primitives targeting high-performance applications, there are several interesting cryptographic algorithms. The most tempting ones are those employing AES-NI [Gue10, Corb], which is a new AES instruction set equipped on many modern CPUs from Intel and AMD. Some SoCs for mobile devices are also equipped with an instruction set for AES [arm21], and more

and more SoCs will support the instruction by the time 6G system is realized. Hence employing AES-NI seems reasonable in designing cryptographic algorithms for 6G systems. The AEGIS family and Tiaoxin-346 belongs to such a category, which are two submissions to the CAESAR competition [cae18] and AEGIS-128 has been selected in the final portfolio for high-performance applications. The round functions of the AEGIS family and Tiaoxin-346 are quite similar. Specifically, they are only based on the usage of one AES round and the 128-bit XOR operation, both of which have been realized with one instruction on SIMD (Single Instruction, Multiple Data) instructions. As a result, both the AEGIS family and Tiaoxin-346 are competitive in terms of encryption/decryption speed in a pure software environment, if compared with many primitives.

Jean and Nikolić generalized the method to design efficient round functions as that used in AEGIS and Tiaoxin-346 in [JN16]. After a thorough search, they discovered round functions that can achieve a faster speed than any of the round functions adopted in the AEGIS family and Tiaoxin-346 and provide the 128-bit security against forgery attacks. However, they did not propose a concrete AEAD scheme [JN16].

Obviously, AEGIS-128, AEGIS-128L and Tiaoxin-346 do not meet the security requirement of the 256-bit key length in 6G systems. In addition, according to our experiments, AEGIS-256 does not reach more than 100 Gbps (See Sect. 5). However, those researches leave us the potential of designing the faster cryptographic algorithm based on AES round functions for 6G.

### 1.2 Our Design

In this paper, we present an AES-based encryption scheme with a 256-bit key and 128-bit tag called Rocca, which provides both a raw encryption scheme and an AEAD scheme with a 128-bit tag. The goal of Rocca is to meet the requirement in 6G systems in terms of both performance and security. For performance, Rocca achieves an encryption/decryption speed of more than 100 Gbps in both raw encryption scheme and AEAD scheme. For security, Rocca can provide 256-bit and 128-bit security against key-recovery attacks and forgery attacks, respectively.

*Optimized AES-NI-Friendly Round Function* To achieve such a dramatically fast encryption/decryption speed, **Rocca** is designed for a pure software environment that can fully support both the AES-NI and SIMD instructions. The design of the round function of **Rocca** is inspired by the work of Jean and Nikolić [JN16]. To further increase its speed and reduce the state size, we explore a new class of AES-based structures. Specifically, we take the following different approaches.

- To minimize the critical path of the round function, we focus on the structure where each 128-bit block of the internal state is updated by either one AES round or XOR while Jean and Nikolić consider the case of applying both aesenc and XOR in a cascade way for one round, and most efficient structures in [JN16] are included in this class. - We introduce a permutation between the 128-bit state words of the internal state in order to increase the number of possible candidates while keeping efficiency as executing such a permutation is a cost-free operation in the target software, which was not taken into account in [JN16].

We search for round functions that can ensure 128-bit security against forgery attacks in a class of our general constructions as with [JN16]. Consequently, we succeed in discovering more efficient constructions with a smaller state size than those in [JN16]. The internal state of Rocca consists of eight 128-bit words and its round function is composed of 4 aesencs and 4 128-bit XOR operations, which is significantly faster than those of the AEGIS family, Tiaxion-346 and Jean and Nikolić's structure [JN16].

*Encryption and Authentication Scheme.* To resist against the statistical attack in [Min14], generating each 128-bit ciphertext block will additionally require one AES round, while it is generated with simple quadratic boolean functions in the AEGIS family and Tiaxion-346. However, such a way will have few overhead by AES-NI (See Sect. 3). Moreover, a study on the initialization phases for both reduced AEGIS-128 and Tiaoxin-346 has been reported recently [LIMS21]. To further increase the resistance against the reported attacks, how to place the nonce and the key at the initial state is carefully chosen in our scheme.

*Performance* The encryption/decryption speed of Rocca is dramatically improved compared with other AES-based encryption schemes. Rocca is more than three and four times faster than SNOW-V and SNOW-V-GCM, respectively, i.e. the speed reaches 215 and 178 Gbps, respectively. Compared to other schemes with 256-bit key, Rocca is more than five times faster than AEGIS-256 and more than three times faster than AES-256-GCM in our evaluations (See Sect. 5 and Appendix. A). Moreover, Rocca is also faster than AEGIS-128, AEGIS-128L, and Tiaoxin-346 even though Rocca provides a higher security level. To the best of our knowledge, Rocca is the first dedicated cryptographic algorithm targeting 6G systems and we hope it can inspire future designs.

#### 1.3 Version History

The difference from the conference version  $[SLN^+21]$  is that key feedforward is added in initialization and finalization to be secure against cryptanalysis on the first version of Rocca [HII<sup>+</sup>22]. Along with this change, we add the security evaluation against new attack in 4.6 and update software performance. Here, we would like to enhasize that there is no overhead in any environment due to this change.

The other changes from the conference version [SLN+21] are in the followings: (1) updated security claims of Rocca by taking consideration into the security requirements for 6G (See Sect. 2.3) (2) showed the limitation of the message length and the length of the associated data (See Sect. 2.3). (3) Added software performance results on Intel's CPUs and ARM-based SoCs (See Appendix A). (4) Modified typo in Algorithm 1 regarding the decryption.

#### 1.4 Organization

This paper is organized as follows. We first present the specification of Rocca in Sect. 2. Then, we describe the design rationale, such as the general construction based on AES-NI, criteria for performance and security, and how to find efficient round functions in Sect. 3. In Sect. 4, we provide the details of security evaluations against possible attacks on Rocca. Sect. 5 shows our software implementation results. Finally, we conclude this paper in Sect. 6.

#### 2 Preliminaries

In this section, the notations and the specification of our designs will be described.

#### 2.1 Notations

The following notations will be used in the paper. Throughout this paper, a block means a 16-byte value. For the constants  $Z_0$  and  $Z_1$ , we utilize the same ones as Tiaoxin-346 [Nik14].

- 1. S: The state of Rocca, which is composed of 8 blocks, i.e.  $S = (S[0], S[1], \ldots, S[7])$ , where S[i]  $(0 \le i \le 7)$  are blocks and S[0] is the first block.

- 2.  $Z_0$ : A constant block defined as  $Z_0 = 428a2f98d728ae227137449123ef65cd$ .

- 3.  $Z_1$ : A constant block defined as  $Z_1 = b5c0fbcfec4d3b2fe9b5dba58189dbbc.$

- 4. AES(X, Y): One AES round applied to the block X, where the round constant is Y, as defined below:

$\mathsf{AES}(X, Y) = (\mathsf{MixColumns} \circ \mathsf{ShiftRows} \circ \mathsf{SubBytes}(X)) \oplus Y,$

where MixColumns, ShiftRows and SubBytes are the same operations as defined in AES.

5. A(X): The AES round function without the constant addition operation, as defined below:

A(X) =MixColumns  $\circ$  ShiftRows  $\circ$  SubBytes(X),

- 6. |X|: The length of X in bits.

- 7.  $0^l$ : A zero string of length *l* bits.

- 8. X||Y: The concatenation of X and Y.

- 9.  $R(S, X_0, X_1)$ : The round function used to update the state S.

#### 2.2 The Round Update Function

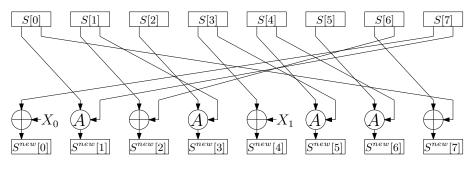

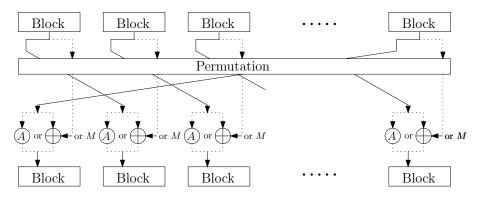

The input of the round function  $R(S, X_0, X_1)$  of Rocca consists of the state S and two blocks  $(X_0, X_1)$ . If denoting the output by  $S^{new}$ ,  $S^{new} \leftarrow R(S, X_0, X_1)$  can be defined as follows:

$$S^{new}[0] = S[7] \oplus X_0,$$

$$\begin{split} S^{new}[1] &= \mathsf{AES}(S[0], S[7]), \\ S^{new}[2] &= S[1] \oplus S[6], \\ S^{new}[3] &= \mathsf{AES}(S[2], S[1]), \\ S^{new}[4] &= S[3] \oplus X_1, \\ S^{new}[5] &= \mathsf{AES}(S[4], S[3]), \\ S^{new}[6] &= \mathsf{AES}(S[5], S[4]), \\ S^{new}[7] &= S[0] \oplus S[6]. \end{split}$$

The corresponding illustration can be referred to Figure 1.

Fig. 1: Illustration of the round function

#### 2.3 Specification of Rocca

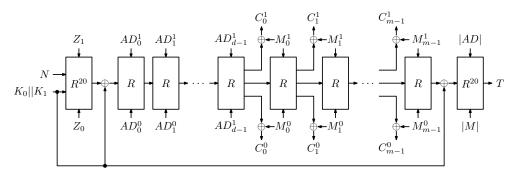

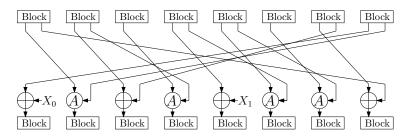

Rocca is an authenticated-encryption with associated-data scheme composed of four phases: initialization, processing the associated data, encryption and finalization. The input consists of a 256-bit key  $K_0||K_1 \in \mathbb{F}_2^{128} \times \mathbb{F}_2^{128}$ , a 128-bit nonce N, the associated data AD and the message M. The output is the corresponding ciphertext C and a 128-bit tag T. Define  $\overline{X} = X||0^l$  where l is the minimal non-negative integer such that  $|\overline{X}|$  is a multiple of 256. In addition, write X as  $X = X_0||X_1|| \dots ||X_{|X|-1}|$  with  $|X_i| = 256$ . Further,  $X_i$  is written as  $X_i = X_i^0||X_i^1|$  with  $|X_i^0| = |X_i^1| = 128$ .

Initialization. First,  $(N, K_0, K_1)$  is loaded into the state S in the following way:

$$S[0] = K_1, S[1] = N, S[2] = Z_0, S[3] = Z_1,$$

$$S[4] = N \oplus K_1, S[5] = 0, S[6] = K_0, S[7] = 0.$$

Here, two 128-bit constants  $Z_0$  and  $Z_1$  are encoded as 16-byte little endian words and loaded into S[2] and S[3] respectively. Then, 20 iterations of the round function  $R(S, Z_0, Z_1)$  is applied to the state S. After 20 iterations of the round function, two 128-bit keys are XORed with the state S in the following way;

$$S[0] = S[0] \oplus K_0,$$

$$S[4] = S[4] \oplus K_1.$$

Processing the associated data. If AD is empty, this phase will be skipped. Otherwise, AD is padded to  $\overline{AD}$  and the state is updated as follows:

for

$$i = 0$$

to  $d - 1$

$R(S, \overline{AD}_i^0, \overline{AD}_i^1)$ ,

end for

where  $d = \frac{|\overline{AD}|}{256}$ .

*Encryption.* The encryption phase is similar to the phase to process the associated data. If M is empty, the encryption phase will be skipped. Otherwise, M is first padded to  $\overline{M}$  and then  $\overline{M}$  will be absorbed with the round function. During this procedure, the ciphertext C is generated. If the last block of M is incomplete and its length is b bits, i.e. 0 < b < 256, the last block of C will be truncated to the first b bits. A detailed description is shown below:

$$\begin{split} &\text{for } i=0 \text{ to } m-1\\ &C_i^0=\mathsf{AES}(S[1],S[5])\oplus \overline{M}_i^0,\\ &C_i^1=\mathsf{AES}(S[0]\oplus S[4],S[2])\oplus \overline{M}_i^1,\\ &R(S,\overline{M}_i^0,\overline{M}_i^1),\\ &\text{end for} \end{split}$$

where  $m = \frac{|\overline{M}|}{256}$ .

Finalization. After the above three phases, two 128-bit keys  $K_0$  and  $K_1$  are first XORed with the state S in the following way;

$$S[0] = S[0] \oplus K_0,$$

$$S[4] = S[4] \oplus K_1.$$

Then, the state S will again pass through 20 iterations of the round function R(S, |AD|, |M|) and then the tag is computed in the following way:

$$T = \bigoplus_{i=0}^{7} S[i].$$

The length of associated data and message is encoded as 16-byte little endian word and stored into |AD| and |M|, respectively.

A formal description of Rocca can be seen in Algorithm 1 and the corresponding illustration is shown in Figure 2.

Algorithm 1 The specification of Rocca

1: procedure  $RoccaEncrypt(K_0, K_1, N, AD, M)$ 2:  $S \leftarrow \text{Initialization}(N, K_0, K_1)$ 3: if |AD| > 0 then  $S \leftarrow \texttt{ProcessAD}(S, \overline{AD})$ 4: if |M| > 0 then 5: $S \leftarrow \texttt{Encryption}(S, \overline{M}, C)$ 6: 7: Truncate C8:  $T \leftarrow \texttt{Finalization}(S, |AD|, |M|, K_0, K_1)$ return (C,T)9: 10: procedure RoccaDecrypt $(K_0, K_1, N, AD, C, T)$ 11: $S \leftarrow \text{Initialization}(N, K_0, K_1)$ 12:if |AD| > 0 then  $S \leftarrow \texttt{ProcessAD}(S, \overline{AD})$ 13:if |C| > 0 then 14:  $S \leftarrow \texttt{Decryption}(S, \overline{C}, M)$ 15:16:Truncate Mif  $T = \text{Finalization}(S, |AD|, |C|, K_0, K_1)$  then 17:18:return M19:else 20:return  $\perp$ procedure Initialization $(N, K_0, K_1)$ 21:22: $(S[0], S[1], S[2], S[3]) \leftarrow (K_1, N, Z_0, Z_1)$ 23: $(S[4], S[5], S[6], S[7]) \leftarrow (N \oplus K_1, 0, K_0, 0)$ for i = 0 to 19 do 24:25: $S \leftarrow R(S, Z_0, Z_1)$  $(S[0], S[4]) \leftarrow (S[0] \oplus K_0, S[4] \oplus K_1)$ 26:27:return Sprocedure ProcessAD(S, AD)28: $d \leftarrow \tfrac{|AD|}{256}$ 29:30: for i = 0 to d - 1 do  $S \leftarrow R(S, AD_i^0, AD_i^1)$ 31: 32: return S33: procedure Encryption(S, M, C) $m \leftarrow \frac{|M|}{256}$ 34: 35: for i = 0 to m - 1 do  $C_i^0 \leftarrow \mathsf{AES}(S[1], S[5]) \oplus M_i^0$ 36:  $C_i^1 \leftarrow \mathsf{AES}(S[0] \oplus S[4], S[2]) \oplus M_i^1$  $S \leftarrow R(S, M_i^0, M_i^1)$ 37: 38: 39: return S40: procedure Decryption(S, M, C) $c \leftarrow \frac{|C|}{256}$ 41: 42: for i = 0 to c - 1 do  $M_i^0 \leftarrow \mathsf{AES}(S[1], S[5]) \oplus C_i^0$ 43: 44:  $M_i^1 \leftarrow \mathsf{AES}(S[0] \oplus S[4], S[2]) \oplus C_i^1$ 45:  $S \leftarrow R(S, M_i^0, M_i^1)$ return S46: 47: procedure Finalization $(S, |AD|, |M|, K_0, K_1)$  $(S[0], S[4]) \leftarrow (S[0] \oplus K_0, S[4] \oplus K_1)$ 48:49:for i = 0 to 19 do  $S \leftarrow R(S, |AD|, |M|)$ 50: $T \leftarrow 0$ 51:52:for i = 0 to 7 do  $T \leftarrow T \oplus S[i]$ 53:54: return T

Fig. 2: The procedure of Rocca

A raw encryption scheme. If the phases of processing the associated data and finalization are removed, a raw encryption scheme is obtained.

Security claims. Rocca provides 256-bit security against key-recovery and 128bit security against distinguishing and forgery attacks in the nonce-respecting setting<sup>5</sup>. We do not claim its security in the related-key and known-key settings.

The message length for a fixed key is limited to at most  $2^{128}$  and we also limit the number of different messages that are produced for a fixed key to be at most  $2^{128}$ . The length of associated data of a fixed key is up to  $2^{64}$ .

### 3 Design Rationale

#### 3.1 General Construction

SIMD instruction. The prime design goal of Rocca is to meet the requirements of processing/transmission speed for 6G applications, namely more than 100 Gbps [LaL19]. In order to realize fast encryption/decryption speed (hereafter, we simply call "speed") on a pure software environment, we take full advantage of the SIMD instructions and the AES-NI, both of which are equipped on most of modern CPUs. The SIMD instructions contains some fundamental instructions such as XOR and AND, and can execute them by 32/64/128-bit units as one instruction, where the AES-NI is a special set of the SIMD instructions, which is first rolled out by Intel [Cora] and available on modern processors. The AES-NI can execute AES about 10 times faster than non-AES-NI in parallelizable modes

<sup>&</sup>lt;sup>5</sup> We updated the claimed security of distinguishing attacks from the ToSC version [SLN<sup>+</sup>21] for the following reasons. The most well-known and popular distinguishing attack on the keystream seems to be the linear attack. Such a distinguishing attack often requires a large number of plaintexts. If the data complexity exceeds the time complexity to find the key with Grover's algorithm, we view such an attack as invalid in the quantum setting. Therefore, regarding the distinguishing attack, we only claim 128-bit security in the quantum setting and a meaningful distinguishing attack in the classical setting should have data complexity below 2<sup>128</sup>.

such as CTR mode. In this paper, we utilize on aesenc, which is one of instruction sets of AES-NI, and performs one regular (not the last) round of AES on an input state S with a subkey K:

$\operatorname{aesenc}(S, K) = (\operatorname{MixColumns} \circ \operatorname{ShifRows} \circ \operatorname{SubBytes}(S)) \oplus K.$

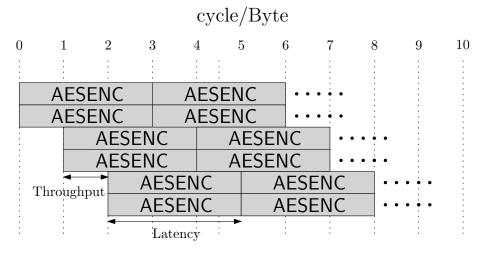

The execution speed of these instructions can be evaluated by *latency* and *throughput*, where latency is the number of clock cycles required to execute a single instruction and throughput is the required number of clock cycles before the same instruction to be executed. It is important when considering the parallel execution. Table 1 shows latency and throughput of aesenc [RTL] in each architecture. Among existing architectures, we focus the latest architecture Intel Ice-Lake series that has the fastest AES-NI whose latency and throughput of aesenc are 3 and 0.5, respectively. Figure 3 illustrates an example of the process in the parallel execution of aesenc for Intel Ice-lake whose latency and throughput are 3 and 0.5<sup>6</sup>, respectively.

Employing one AES round as an underlying component for future designs has a great merit for performance compared to employing other cryptographic primitives. Many software and libraries support AES-NI natively, e.g OpenSSL. Thus, it seems to be very reasonable that devices connected to 6G services will still support such instructions. SNOW-V also takes advantage of AES-NI for the same reason.

| Vendor | Architecture | Latency | Throughput |

|--------|--------------|---------|------------|

|        | Sky-lake     | 4       | 1          |

|        | Kaby-lake    | 4       | 1          |

| Intel  | Coffee-lake  | 4       | 1          |

| Intel  | Cannon-lake  | 4       | 0.5        |

|        | Cascade-lake | 4       | 1          |

|        | Comet-lake   | unknown | unknown    |

|        | Ice-lake     | 3       | 0.5        |

| AMD    | Zen +        | 4       | 0.5        |

| AWID   | Zen 2        | 4       | 0.5        |

**Table 1:** Latency and throughput of aesenc for some architectures by Intel andAMD referred by [RTL].

**Permutation-based Structure.** As a reference point, we consider a stream cipher SNOW-V, which is designed for 5G applications. SNOW-V is based on linear feedback shift register (LFSR) and Finite State Machine(FSM) with AES-based round functions. As discussed in Section 1, if we follow this design strategy, we need to accelerate the performance approximately at least three times faster than SNOW-V to achieve the required performance of 100 Gbps. Thus, we decide to choose other design strategies based on AES round functions.

$<sup>^{6}</sup>$  Throughput 0.5 means that there are two ports for **aesenc** with throughput 1.

Fig. 3: The process of aesenc for Intel Ice-lake.

Specifically, we focus on AEGIS family [WP13] and Tiaoxin-346 [Nik14], which are permutation-based authenticated encryption schemes using AES round functions and submitted to CAESAR competition [cae18]. These allow a full parallelization and can achieve the outstanding speed compared to AES-CTR.

However, as it has been pointed out that there exists a linear bias in the ciphertext blocks for AEGIS-256 [Min14], it seems insecure to adopt the similar quadratic boolean function to generate the ciphertexts, especially for the purpose to reach 256-bit security. This fact motivates us to design different ways to generate the ciphertext blocks and finally involving 1 AES round function into generating each ciphertext block is chosen. Such a way is efficient due to the parallel calls to AES-NI. Moreover, a study on the initialization phases for both reduced AEGIS-128 and Tiaoxin-346 has been reported recently [LIMS21]. To further increase the resistance against the reported attacks, how to place the nonce and the key at the initial state is carefully chosen in our scheme, which is little discussed in AEGIS and Tiaoxin-346.

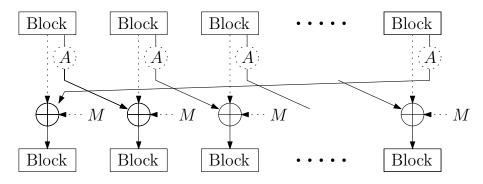

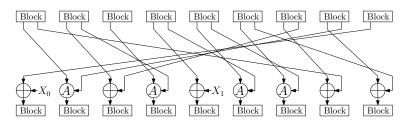

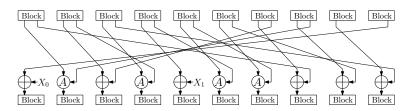

Efficient AES-Based Round Function. Round functions of AEGIS family [WP13] and Tiaoxin-346 [Nik14] consist of the 128-bit XOR operation and one AES round that is executed by the processor instruction aesenc. Jean and Nikolić have generalized the way to construct efficient round functions using only the one AES round (aesenc) and 128-bit XOR and have found several more efficient candidates [JN16]. Figure 4 shows the general construction of the round function considered in [JN16].

To push the limitation further of efficiency of their structures, we explore a new class of AES-based structures shown in Fig 5. Compared to the structures considered by Jean and Nikolić results [JN16], our constructions remove the case of applying both **aesenc** and XOR to each block in a cascade way for one round

**Fig. 4:** The general construction considered of the round function in [JN16]. Dash lines mean that it can be possible to be absent or present in the design.

to minimize the critical path of one round. Specifically, we only consider the case of applying only either **aesenc** or 128-bit XOR to each block in one round, where **aesenc** takes a state block or message block as input of AddRoundKey and 128-bit XOR takes state block or message block as inputs, respectively as shown in Figure 5.

Moreover, we apply a block permutation to state blocks, which was not considered by Jean and Nikolić (See Fig 4). This sufficiently increases the number of possible candidates. Indeed, as described in later section, it enables us to find more efficient constructions than Jean and Nikolić's results, which is not covered by their target classes. It should be emphasized that executing the block permutation in register size is a cost-free operation, that is, the permutation only changes the order of blocks. More strictly, a permutation needs some temporary registers. However, these registers almost do not affect the speed if the total number of registers used in process of the scheme is lower than 16, which is the total number of xmm-registers equipped in almost all modern CPUs. Hence, applying a block permutation does not affect the speed of the round function. For a block that will be inputted into **aesenc** or XOR, we use one-block right rotation as in [JN16].

#### 3.2 Criteria for Performance and Security

For designing efficient round functions, we need to choose several parameters such as the number of **aesencs**, the number of inserted message blocks, and a block permutation for our structure in Fig. 5. We clarify requirements of performance and security for target applications to choose these parameters.

*Requirements for Performance.* To theoretically estimate speed, we utilize a metric called *rate*, which is proposed by Jean and Nikolić [JN16].

**Definition 1 (Rate [JN16])** The rate p of a design is the number of AES rounds (calls to aesenc) used to process a 128-bit message.

Fig. 5: General construction of the round function. Dash lines mean that it can be possible to be absent or present in the design.

For our general construction of Fig 5, the *rate* p is estimated as a ratio of (# of aesencs)/( # of the inserted 128-bit messages) in one round. Since a smaller *rate* leads to more efficient design [JN16], we should design the round function that have as small *rate* as possible. The *rate* is the most important parameter for speed.

The number of **aesenc** in one round is also important factor to maximize the efficiency. Jean and Nikolić claim that the number of **aesenc** in one round should be close to (latency)/(throughput) ratio [JN16] for the efficient design, e.g. if the latency and throughput of **aesenc** are respectively 3 and 0.5, the number of **aesenc** should be 6 in one round. The reason is when the number of **aesencs** is less than a (latency)/(throughput) ratio, there are empty cycles in process of **aesenc**. On the other hand, if the number of **aesencs** is the same as (latency)/(throughput) ratio, there is no empty cycles as shown in Figure 3. Since our target architecture is Ice-lake, the number of **aesenc** in a round should be 6.

Another important factor related to speed is the number of blocks of round functions, namely the state size. Smaller state size significantly improves the efficiency because it can reduce registers used for encryption and makes a whole process of encryption easier. We experimentally confirmed that reducing the number of blocks leads to increasing speed when the *rate* is the same. Table 2 shows our experimental result that compares three types of round functions of the *rate* 2 with the number of blocks of 8, 9, and 10, each of which is measured on Intel(R) Core(TM) i7-1068NG7 CPU @ 2.30GHz with 16 GB RAMs. Details of these round functions are given in Appendix B. Besides, a smaller state size is a preferable feature to be deployed in wider classes of devices with keeping the efficiency. It is because this, that some CPUs, such as ones from AMD, do not support the large size register like AVX512, and the process requiring the use of many registers tends to become more complicated on these CPUs. Since the number of blocks of SNOW-V, which is our reference point, is 7, the state size should be competitive.

**Table 2:** Comparison of the performance of the round function having different number of blocks at the same *rate*.

| # of blocks | Speed (in cycle/Byte) | rate |

|-------------|-----------------------|------|

| 8           | 0.126717              | 2    |

| 9           | 0.147397              | 2    |

| 10          | 0.155584              | 2    |

Requirements for Security. Since evaluating the resistance to all possible attacks for all possible candidates is practically infeasible, we focus on the security against the forgery attack by the internal collision as a criteria of security when finding candidates, as with [JN16]. Especially, we impose the 128-bit security against the forgery attack on our design, i.e. our security requirement is that there are no internal collisions with a probability more than  $2^{-128}$ . Through this paper, "forgery attacks" is meant to be a universal forgery in the nonce-respecting setting.

To evaluate the probability of the internal collision, we search the lower bound for the number of active S-boxes by a Mixed Integer Linear Programming (MILP) solver [MWGP11]. Since the maximum probability of an S-box is  $2^{-6}$ , it is sufficient to guarantee the security against internal collisions if there are 22 active S-boxes, as it gives  $2^{(-6\times22)} < 2^{-128}$  as an estimate of differential probability. For the security against other possible attacks, we evaluate after designing a whole design, and it will be described in Sect. 4.

*Summary of Our Criteria.* Requirements for AES-based round function are as follows.

For speed.

**Requirement 1.** The lowest *rate* round function as possible that leads to faster speed.

Requirement 2. The number of aesencs in one round is close to 6.

**Requirement 3.** A round function with a smaller number of blocks (around 7).

For security.

**Requirement 4.** 128-bit security to the forgery attack by internal collision, i.e. the lower bound of active S-boxes is 22.

For comparison, Table 3 shows parameters of the round function in the AEGIS [WP13] family, Tiaoxin-346 [Nik14] and structure by Jean and Nikolić [JN16].

### 3.3 Finding Efficient Structures

We choose several parameters such as the number of **aesencs**, the number of inserted message blocks, and a block permutation to meet requirements given

Table 3: Round functions of AEGIS family and Tiaoxin-346

| Primitive   | #  of aesenc | # of blocks | # of inserted message blocks | rate |

|-------------|--------------|-------------|------------------------------|------|

| AEGIS-128   | 5            | 5           | 1                            | 5    |

| AEGIS-256   | 6            | 6           | 1                            | 6    |

| AEGIS-128L  | 8            | 8           | 2                            | 4    |

| Tiaoxin-346 | 6            | 13          | 2                            | 3    |

| [JN16]      | 6            | 12          | 3                            | 2    |

in Sect. 3.2. The number of possible candidates is estimated as  $s! \times {\binom{s}{a}} \times {\binom{s}{m}}$  candidates where s, a, and m are # of blocks, # of **aesenc**, and # of message blocks, respectively. For example, it reaches  $2^{35.00}$  candidates when s = 10, a = 4, and m = 2.

*Our Approach.* According to Table 3, the most efficient design is Jean and Nikolić's structure whose *rate* is 2. However, their state size is quite large for our requirement. In our experiments, the round functions with a smaller *rate* require a larger number of blocks to meet the security requirement. Indeed, we cannot find any structure of *rate* 2 and less than 12 internal blocks by Jean and Nikolić's constructions (Fig.4) [JN16]. To address it, our approach is as follow.

- To expand possible candidates while keeping efficiency, we introduce a block permutation to state blocks in the round function, while Jean and Nikolić did not consider any permutation. It should be emphasized that executing the block permutation in register size is a cost-free operation.

- To further improve the efficiency, we focus on the structure in which each block in one round is applied only either aesenc or XOR to minimized the critical path of the round function.

Search Targets. When the number of inserted message blocks is m, the number of aesencs in one round should be (6 - m) to satisfy requirement 2 as m aesenc is used for generating ciphertext blocks for our design to the resistance to the linear bias (details in Section 3.5). Considering requirement 1 (rate = 2), the only choice of m is 2, thus the number of aesences is 4. Following requirement 3, we consider the case where # of blocks are from 6 to 8. Besides, we consider the case where rate = 1.5 that can not satisfy requirement 2, because the low rate round function might be possible to more efficient even if it does not meet requirement 2. Table 4 shows our candidates of the round function.

We evaluate the lower bounds for the number of active S-boxes for Candidate-1, 2, 3, 4, 5, and 6 by a MILP solver. We can conduct exhaustive searches for Candidates-1, 2, 4, and 5 while exhaustive searches for Candidates-3 and 6 are infeasible due to too large candidates that reach  $2^{26.23}$  and  $2^{25.91}$  for Candidates-3 and 6, respectively. Thus, we randomly search  $2^{19.93}$  candidates for both Candidate-3 and 6.

Table 4: Candidates of round functions which we search.

| Round function | # of aesenc | # of blocks | # of message blocks | rate | # of candidates | # of searched candidates |

|----------------|-------------|-------------|---------------------|------|-----------------|--------------------------|

| Candidates-1   | 4           | 6           | 2                   | 2    | $2^{17.30}$     | ALL                      |

| Candidates-2   | 4           | 7           | 2                   | 2    | $2^{21.82}$     | ALL                      |

| Candidates-3   | 4           | 8           | 2                   | 2    | $2^{26.23}$     | $2^{19.93}$              |

| Candidates-4   | 3           | 6           | 2                   | 1.5  | $2^{17.72}$     | ALL                      |

| Candidates-5   | 3           | 7           | 2                   | 1.5  | $2^{21.82}$     | ALL                      |

| Candidates-6   | 3           | 8           | 2                   | 1.5  | $2^{25.91}$     | 2 <sup>19.93</sup>       |

*Results.* As a result of an exhaustive search over Candidates-1, 2, 4, and 5, there are no round functions that satisfy the requirement 4. For candidates-6, we could not find round functions meeting requirement 4 either. For Candidates-3, we found that 100 out of  $2^{19.93}$  candidates ensure active S-boxes of  $\geq 22$ . We then evaluate a diffusion property for these 100 candidates. Then we find 22 out of 100 candidates achieve the full diffusion after 7 rounds in nibble-wise while round functions of AEGIS-128, AEGIS-256, AEGIS-128L, and [JN16] require 7, 8, 10, and 12 rounds for the full diffusion, respectively, and the one of Tiaoxin-346 never achieve the full diffusion as the state consists of three independent chucks.

We finally choose the round function shown in Fig 1 as the one of Rocca, which ensures active S-boxes of 24 that is the largest number of active S-boxes among 22 candidates. This evaluation requires about 23 days on three computers equipped with 48/64/64 cores and 256/256/256 GB RAMs.

Table 5 compares the speed of round functions of Rocca and other primitives, where speed is estimated as the average value of the round function executed 1000000 times with 64kB messages on Intel(R) Core(TM) i7-1068NG7 CPU @ 2.30GHz with 16 GB RAMs. Our round function is the fastest one and the number of blocks is smaller than ones whose *rate* is 2 or 3.

It should be mentioned that the comparison of the speed of round functions does not always reflect directly to the speed of the whole design. This is because that the overhead of the ciphertext generation depends on the structure of the round function, especially the empty cycle in process of XOR/aesenc.

| Primitive   | Speed (in cycles / Byte) | # of blocks | rate |

|-------------|--------------------------|-------------|------|

| AEGIS-128   | 0.384482                 | 5           | 5    |

| AEGIS-256   | 0.388125                 | 6           | 6    |

| AEGIS-128L  | 0.191072                 | 8           | 4    |

| Tiaoxin-346 | 0.192413                 | 13          | 3    |

| [JN16]      | 0.140433                 | 12          | 2    |

| Rocca       | 0.124609                 | 8           | 2    |

Table 5: Speed (in cycles / Byte) of round functions of Rocca, AEGIS-128, AEGIS-128L, AEGIS-256, Tiaxion-346, and JN16 (not include a generation part of a ciphertext).

#### 3.4 Loading the Nonce and Key

It has been pointed by Liu et al. that there is one useless round in Tiaoxin-346 by expressing the internal states in terms of the nonce and the key at the initialization phase [LIMS21]. The main reason is that the nonce and the key are not well diffused, i.e. after a certain number of rounds, the internal state can be expressed in terms of A(N) and the key. To avoid it in Rocca, we carefully investigate how to place the nonce and the key.

In Rocca, the initial state is loaded as follows:

$$S[0] = K_1, S[1] = N, S[2] = Z_0, S[3] = Z_1,$$

$$S[4] = N \oplus K_1, S[5] = 0, S[6] = K_0, S[7] = 0.$$

After one-round update, the state  $(S[0], \ldots, S[7])$  becomes:

$$S[0] = Z_0, S[1] = A(K_1), S[2] = \underline{N \oplus K_0}, S[3] = \underline{N \oplus A(Z_0)},$$

$$S[4] = 0, S[5] = A(N \oplus K_1) \oplus Z_1, S[6] = N \oplus K_1, S[7] = K_0 \oplus K_1.$$

It can be observed that N is xored with  $K_0$  and  $K_1$ , respectively. Moreover, N is involved in the expressions of each state block in a very different way, which can avoid the useless rounds and, at the same time, strengthen the resistance against the key-recovery attacks applied to round-reduced AEGIS-128 and Tiaoxin-346 as described in [LIMS21]. Further evidence can be seen from the expressions of the state blocks after 3 rounds of update, as shown below:

$$\begin{split} S[0] &= \underline{N \oplus K_1}, \\ S[1] &= A(K_0 \oplus K_1 \oplus Z_0) \oplus Z_0 \oplus N \oplus K_1, \\ S[2] &= A(Z_0) \oplus K_0 \oplus K_1 \oplus A(A(\underline{N \oplus K_1}) \oplus Z_1), \\ S[3] &= A(\underline{A(K_1) \oplus N \oplus K_1}) \oplus A(Z_0) \oplus K_0 \oplus K_1, \\ S[4] &= A(\underline{N \oplus K_0}) \oplus A(K_1) \oplus Z_1, \\ S[5] &= A(\underline{N \oplus A(Z_0) \oplus Z_1}) \oplus A(\underline{N \oplus K_0}) \oplus A(K_1), \\ S[6] &= A(\underline{N \oplus A(Z_0)}) \oplus N \oplus A(Z_0) \oplus Z_1, \\ S[7] &= K_0 \oplus K_1 \oplus Z_0 \oplus A(A(\underline{N \oplus K_1}) \oplus Z_1). \end{split}$$

#### 3.5 Generating the Ciphertext Blocks

In both AEGIS and Tiaoxin-346, each ciphertext block is computed based on a simple quadratic boolean function in terms of the several internal state blocks where the number of AND operations is 1. However, such a way to generate the output seems to be insecure against the statistical attack proposed by [Min14], especially for the scheme targeting 256-bit security.

At the initial design phase, we tried many possible combinations to compute each ciphertext block with a similar quadratic boolean function. However, with the MILP-based method [ENP19] to automatically evaluate the security against this statistical attack, the lower bound for the time complexity is always below  $2^{128}$ , which is far smaller than  $2^{256}$ . Therefore, new strategies are essential for Rocca.

The basic idea is to utilize a complex nonlinear function and finally the AES round function is chosen as the only nonlinear function. Due to the parallel way to perform the AES round function, such a way is indeed rather efficient and can simultaneously strengthen the security of our scheme. To reduce the overall overheads, computing each ciphertext block only utilizes 1 aesenc.

The basic principle to choose the state blocks to compute the ciphertext is that the state blocks (S[0], S[2], S[4], S[5]) passing through the AES round function in the round updated function should be involved, which can increase the number of active S-boxes in the first round. In addition, we expect that they should be processed in a different way from that in the round update function. Intuitively, this can prevent the ciphertext blocks from being related to the updated internal state blocks.

Moreover, as (S[4], S[5]) passes through the AES round function in the round update function and the two state blocks are next to each other, considering the fact that several rounds are needed, it is better to choose additional state blocks from (S[0], S[1], S[2], S[3], S[4]), which will be shifted to (S[4], S[5]) after some rounds. A detailed study of the security of our choice can be found in the following section.

We emphasize that the overhead of executing these two **aesencs** is few since we can assign them into empty cycles of **aesenc** in the round function.

### 4 Security Evaluation

#### 4.1 Differential Attack

The differential attack is one of the possible attacks on the initialization phase of Rocca. Specifically, the differences in the *nonce* (and key) can propagate to the ciphertext. If there is a differential characteristic with a high probability, it can be exploited for the differential attack. Hence, we can compute the lower bound for the number of active S-boxes in the initialization phase to evaluate the resistance against the differential attack. To compute the lower bound, we utilize a MILP-aided method proposed by Mouha et al. [MWGP11] and focus on the byte-wise truncated differences. We evaluate it in both the single-key setting where differences can only be injected into the *nonce* and the related-key setting where differences can be injected into the key and *nonce*.

Table 6 shows the lower bounds for the number of active S-boxes up to 14 rounds in the single-key setting and up to 11 rounds in the related-key setting in the initialization phase. Since the maximal differential probability of the S-box of AES is  $2^{-6}$ , it is sufficient to guarantee the security against differential attacks if there are 43 active S-boxes, as it gives  $2^{(-6\times43)} < 2^{-256}$  as an estimate of the differential probability. As shown in Table 6, there are 54 active S-boxes over 6 rounds in the single-key setting and 44 active S-boxes over 7 rounds in the

related-key setting in the initialization phase. It should be emphasized that we do not claim the security in the related-key setting, although we evaluated the number of active S-boxes in the related-key setting.

Since there is a large security margin, we expect that Rocca can resist against differential attacks in the initialization phase.

Table 6: The lower bound for the number of active S-boxes in the initialization phase where  $AS_{sk}$  and  $AS_{rk}$  mean an active S-box in the single-key setting and in the related-key setting, respectively.

| Rounds                   | 1 | 2 | 3 | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 |

|--------------------------|---|---|---|----|----|----|----|----|----|----|----|----|----|----|

| $\# \text{ of } AS_{sk}$ |   |   |   |    |    |    |    |    |    |    |    |    |    |    |

| $\#$ of $AS_{rk}$        | 0 | 1 | 2 | 11 | 21 | 36 | 44 | 48 | 68 | 73 | 79 | -  | -  | -  |

#### 4.2 Forgery Attack

It has been shown in [Nik14] that the forgery attack is a main threat to the constructions like Tiaoxin-346 and AEGIS as only one-round update is used to absorb each block of associated data and message. Such a concern has been taken into account in our design phase, as reported in Sect. 3.

Specifically, in the forgery attack, the aim is to find a differential trail where the attackers can arbitrarily choose differences at the associated data and expect that such a choice of difference can lead to a collision in the internal state after several number of rounds. The resistance against this attack vector can be efficiently evaluated with an automatic method [MWGP11]. As Rocca is based on the AES round function, it suffices to prove that the number of active S-boxes in such a trail is larger than 22 as the length of the tag is 128 bits. With the MILP-based method, it is found that the lower bound is 24. Consequently, Rocca can provide 128-bit security against the forgery attack.

#### 4.3 Integral Attack

One of the most efficient attacks on round-reduced AES is integral attacks. Recently, Liu et al. presented some attacks [LIMS21] on round-reduced AEGIS-128 and Tiaoxin-346 based on the integral distinguisher on 4-round AES. To understand the security of our construction, it is necessary to evaluate the resistance against integral attacks. Similar to [LIMS21], the internal state will be first expressed in terms of the initial state and then we study the expressions.

For simplicity, denote the state after r iterations of the round function at the initialization phase by  $S_r$ . In addition, when writing the expressions, we omit the constants and use A(X) to represent that X passes through one AES round.

i.e. A(X) can represent  $A(X \oplus \epsilon)$  where  $\epsilon$  is a 128-bit constant. In this way, the internal state  $S_4$  can be expressed as follows:

$$S_4[0] = A(A(N)), S_4[1] = A(N) \oplus A(A(N)),$$

$$S_4[2] = A(N), S_4[3] = A(A(A(N))) \oplus N,$$

$$S_4[4] = A(N), S_4[5] = A(A(N)) \oplus A(N),$$

$$S_4[6] = A(A(N) \oplus A(N)) \oplus A(N), S_4[7] = A(N)$$

As our construction can provide 256-bit security, it is necessary to evaluate the case when N traverses all the  $2^{128}$  possible values under the same 256-bit key. According to [LIMS21], some terms in the expressions can be eliminated by adding proper conditions and the expressions can be simplified. However, according to the expression of  $S_4[3]$ , when N takes all the possible values, it is impossible that  $S_4[3]$  will also take all the  $2^{128}$  possible values. In other words, the multiset of  $S_4[3]$  tends to be unstructured. Therefore, by considering the propagation of  $S_4[3]$  and the way to compute the ciphertext, we believe that 20 rounds are sufficient to resist against integral attacks.

On the other hand, consider the expressions for  $S_6$ , as shown below:

$$\begin{split} S_6[0] &= A(A(N)) \oplus A(A(N) \oplus A(N)) \oplus A(N), \\ S_6[1] &= A(A(N)) \oplus A(A(N)) \oplus A(A(N)) \oplus A(A(N)) \oplus A(N)) \oplus A(N), \\ S_6[2] &= A(A(A(N))) \oplus A(N) \oplus A(A(A(N)) \oplus A(N)) \oplus A(N), \\ S_6[3] &= A(A(N) \oplus A(A(N)) \oplus A(A(N)) \oplus A(N)) \oplus A(N)) \oplus A(N)) \\ & \oplus A(A(A(N))) \oplus A(N), \\ S_6[4] &= A(A(N)) \oplus A(N) \oplus A(A(N)), \\ S_6[5] &= A(A(A(A(N))) \oplus N) \oplus A(A(N)) \oplus A(N) \oplus A(A(N)), \\ S_6[6] &= A(A(A(N)) \oplus A(A(A(N))) \oplus N) \oplus A(A(A(N))) \oplus N, \\ S_6[7] &= A(N) \oplus A(A(A(N)) \oplus A(N)) \oplus A(N). \end{split}$$

As

~ [-]

$$S_8[0] \oplus S_8[4] = S_6[0] \oplus S_6[6] \oplus A(S_6[2]) \oplus S_6[1] \oplus Z_0 \oplus Z_1,$$

$$S_8[1] = A(S_6[7] \oplus Z_0) \oplus S_6[0] \oplus S_6[7],$$

it can be found that in the expressions of  $A(S_8[1])$  and  $A(S_8[0] \oplus S_8[4])$ , N will pass through 5 AES rounds and there seems to be no way to add proper conditions to prevent N from passing through 5 AES rounds. Moreover, as N passes through 5 AES rounds in very different ways in  $A(S_8[1])$  and  $A(S_8[0] \oplus S_8[4])$ , it is also impossible to prevent it by considering the sum  $A(S_8[1]) \oplus A(S_8[0] \oplus S_8[4])$ . Consequently, we further believe that 20 rounds are secure against integral attacks.

#### **4.4** State-recovery Attack

Different from AEGIS and Tiaoxin-346, the output in our construction only involves a few state blocks, i.e. the attackers are able to know  $A(S[1]) \oplus S[5]$  and

$A(S[0] \oplus S[4]) \oplus S[2]$ . As the internal state consists of 8 blocks and the output in each round only leaks 256-bit information, the attackers at least need to consider 4 consecutive rounds in order to recover the whole secret internal state.

Guess-and-determine attack. The guess-and-determine attack is a common tool to achieve state recovery. Consider four consecutive rounds at the encryption phase and denote the 4 internal states used to generate the ciphertexts by  $S_t$ ,  $S_{t+1}$ ,  $S_{t+2}$  and  $S_{t+3}$ , respectively. In this case, the attackers can compute

$$A(S_i[1]) \oplus S_i[5], A(S_i[0] \oplus S_i[4]) \oplus S_i[2],$$

where  $t \leq i \leq t+3$ .

Assuming the message blocks are all zero, we thus have

$$\begin{split} A(S_{t+1}[1]) &= A(A(S_t[0]) \oplus S_t[7]), \\ S_{t+1}[5] &= A(S_t[4]) \oplus S_t[3], \\ A(S_{t+1}[0] \oplus S_{t+1}[4]) &= A(S_t[7] \oplus S_t[3]), \\ S_{t+1}[2] &= S_t[1] \oplus S_t[6], \\ \\ A(S_{t+2}[1]) &= A(A(S_{t+1}[0]) \oplus S_{t+1}[7]) \\ &= A(A(S_t[7]) \oplus S_t[0] \oplus S_t[6]), \\ S_{t+2}[5] &= A(S_{t+1}[4]) \oplus S_{t+1}[3] \\ &= A(S_t[3]) \oplus A(S_t[2]) \oplus S_t[1], \\ A(S_{t+2}[0] \oplus S_{t+2}[4]) &= A(S_{t+1}[7] \oplus S_{t+1}[3]) \\ &= A(S_t[0] \oplus S_t[6] \oplus A(S_t[2]) \oplus S_t[1]), \\ S_{t+2}[2] &= S_{t+1}[1] \oplus S_{t+1}[6] \\ &= A(S_t[0]) \oplus S_t[7] \oplus A(S_t[5]) \oplus S_t[4], \\ \\ A(S_{t+3}[1]) &= A(A(S_{t+1}[7]) \oplus S_{t+1}[0] \oplus S_{t+1}[6]) \\ &= A(A(S_t[0]) \oplus S_t[6]) \oplus S_t[7] \oplus A(S_t[5]) \oplus S_t[4]), \\ S_{t+3}[5] &= A(S_{t+1}[3]) \oplus A(S_{t+1}[2]) \oplus S_{t+1}[1], \\ &= A(A(S_t[2]) \oplus S_t[1]) \oplus A(S_t[1] \oplus S_t(6]) \oplus A(S_t[0]) \oplus S_t[7], \\ A(S_{t+3}[0] \oplus S_{t+3}[4]) &= A(S_{t+1}[0] \oplus S_{t+1}[6] \oplus A(S_{t+1}[2]) \oplus S_{t+1}[1]), \\ &= A(A(S_t[5]) \oplus S_t[4] \oplus S_t[1] \oplus S_t[6] \oplus A(S_t[0])), \\ S_{t+3}[2] &= A(S_{t+1}[0]) \oplus S_{t+1}[7] \oplus A(S_{t+1}[5]) \oplus S_{t+1}[4], \\ &= A(S_t[7]) \oplus S_t[0] \oplus S_t[6] \oplus A(S_t[4]) \oplus S_t[3]) \oplus S_t[3]. \\ \end{split}$$

Therefore, the attackers at least need to consider the following 1024 nonlinear boolean equations in terms of 1024 boolean variables  $(S_t[0], \ldots, S_t[7])$  in order to recover the secret state:

$\alpha_0 = A(S_t[1]) \oplus S_t[5],$

$$\begin{split} &\alpha_1 = A(S_t[0] \oplus S_t[4]) \oplus S_t[2], \\ &\alpha_2 = A(A(S_t[0]) \oplus S_t[7]) \oplus A(S_t[4]) \oplus S_t[3], \\ &\alpha_3 = A(S_t[7] \oplus S_t[3]) \oplus S_t[1] \oplus S_t[6], \\ &\alpha_4 = A(A(S_t[7]) \oplus S_t[0] \oplus S_t[6]) \oplus A(S_t[3]) \oplus A(S_t[2]) \oplus S_t[1], \\ &\alpha_5 = A(S_t[0] \oplus S_t[6] \oplus A(S_t[2]) \oplus S_t[1]) \oplus A(S_t[0]) \oplus S_t[7] \oplus A(S_t[5]) \oplus S_t[4], \\ &\alpha_6 = A(A(S_t[0] \oplus S_t[6]) \oplus S_t[7] \oplus A(S_t[5]) \oplus S_t[4]) \\ & \oplus A(A(S_t[2]) \oplus S_t[1]) \oplus A(S_t[1] \oplus S_t[6]) \oplus A(S_t[0]) \oplus S_t[7], \\ &\alpha_7 = A(A(S_t[5]) \oplus S_t[4] \oplus S_t[1] \oplus S_t[6] \oplus A(S_t[4]) \\ & \oplus A(S_t[7]) \oplus S_t[0] \oplus S_t[6] \oplus A(A(S_t[4]) \oplus S_t[3]) \oplus S_t[3], \end{split}$$

where  $\alpha_i \in \mathbb{F}_2^{128}$   $(0 \le i \le 7)$  are known constants. It is obvious that the attackers should not completely guess 2 state blocks as the time complexity of guess will be  $2^{256}$ . A clever way is to guess a column and a diagonal of the state blocks, which fits well with the form of the outputs. Such a strategy will allow attackers to guess at most 8 columns and diagonals. However, only in the conditions imposed by  $(\alpha_0, \alpha_1, \alpha_3)$ , one AES round is involved, i.e. the clever way is only applicable to these conditions. For the remaining conditions, two AES rounds are involved, which implies that the attackers at least need to guess a complete 128-bit block due to the full diffusion. For such reasons, we believe the time complexity of the guess-and-determine attack cannot be lower than  $2^{256}$ .

Algebraic attack. It is well-known that the S-box of AES can be expressed as a set of quadratic boolean equations if the input zero is discarded. Therefore, the above equation system can be described as quadratic boolean equations by introducing extra intermediate variables to represent the outputs of the S-box for each AES round function. Notice that for different ciphertext blocks ( $\alpha_0, ..., \alpha_7$ ), the attackers have to introduce different variables due to the big difference between the equations. Although the system of equations is overdefined, the number of equations is only slightly larger than the number of variables and the number of variables is much larger than 256. As far as we know, such a system of equations can not be solved with time complexity  $2^{256}$ .

#### 4.5 The Linear Bias

Exploiting the fact that the output (keystream) of AEGIS is quadratic in terms of several state blocks and only one-round update is used to process each message block, Minaud proposed a statistical attack [Min14] on the keystream of AEGIS-256. Such an attack was improved in [ENP19] with an automatic search method based on [SSS<sup>+</sup>19]. Specifically, the authors first utilized a simple truncated model and evaluated the minimal number of active S-boxes. It is found that for AEGIS-128, AEGIS-128L and AEGIS-256, all the results obtained in the simple truncated model suggest they are insecure against such a statistical attack. However, when searching for compatible linear trails in the bit level, almost all of them are

incompatible. In addition, the results obtained in the refined model is far larger than that obtained in the simple truncated model.

To evaluate the resistance of our construction against such a statistical attack, we also adopted the simple truncated model as in [ENP19]. According to our results, the best case is to consider 4 consecutive rounds and the minimal number of active S-boxes is 38, which suggests that the time complexity of the distinguishing attack is at least  $2^{228}$ . Achieving 42 active S-boxes is ambitious without affecting the performance and we believe 38 is enough to resist against such an attack considering the big gap between the truncated model and bitwise model as reported in [ENP19]. To further verify whether there is a compatible linear trail to the best solution obtained with the truncated model, we also implemented the bitwise model where there is no additional constraint on the input mask and output mask of the S-box except the trivial infeasible pairs caused by the zero input mask or zero output mask. When searching for a compatible linear trail based on the truncated pattern, it is soon shown to be infeasible. One main reason is that compared with the attack on AEGIS-256 requiring 2 consecutive rounds, this statistical attack on Rocca requires 4 consecutive rounds, which makes the contradictions in the solutions obtained with the simple truncated model occur more easily if verified with the bitwise model. Taking this fact into account, we further believe **Rocca** is secure against this attack vector.

#### 4.6 The State-recovery Attack Using the Decryption Oracle

In a recent work [HII<sup>+</sup>22], by using a trivial decryption oracle, it is possible to recover the full internal state after the initialization phase with time complexity  $2^{128}$ . Indeed, such a state-recovery attack has been observed by the designers of AEGIS-256 and it is inavoidable if the tag size is small. However, what we need to care is to prevent the further key-recovery attacks after the internal state is recovered in such a way. In AEGIS-256, this is ensured by using a keyed permutation for the initialization phase. In this revised version, we simply use a key feed-foward operation to prevent the further key-recobery attack because the attackers cannot invert the initialization phase without knowing the key even if the state after this phase is fully known. Moreover, although the finalization phase of AEGIS-256 does not involve the key, i.e. it is a public permutation, as suggested by [HII<sup>+</sup>22], we feel it is reasonable to involve the key addition at the very beginning of this phase to prevent further forgery attacks.

#### 4.7 Other Attacks

While there are many attack vectors for block ciphers, their application to Rocca is restrictive as the attackers can only know partial information of the internal state from the ciphertext blocks. In other words, reversing the round update function is impossible in Rocca without guessing many secret state blocks. For this reason, only the above potential attacks vectors are taken into account. In addition, due to the usage of the constant  $(Z_0, Z_1)$  at the initialization phase,

the attack based on the similarity in the four columns of the  $\mathsf{AES}$  state is also excluded.

### 4.8 No Claims

We do not claim the security of our scheme in the nonce-misuse setting and it seems trivial to achieve the state recovery in this setting as the output is computed with only one-round update function at the encryption phase. In addition, we do not claim the security of our scheme in the related-key and known-key setting, which is far from meaningful in real-world applications. For the attacks on the initialization phase, we emphasize that the attackers can only derive information from the restricted outputs and cannot know the full secret internal state.

### 5 Software Implementation

According to [ITU17], target peak data rates for 5G communication are 10 Gbps for uplink and 20 Gbps for downlink. SNOW-V [EJMY19] is a new version of SNOW-family designed for 5G communication with 256-bit key support and achieves 58.25 Gbps on Intel(R) Core(TM) i7 8650U CPU @1.90GHz in encryption only mode. In the next generation (*i.e.* 6G), the target peak data rate is further increased to 100 Gbps to 1 Tbps [LaL19]. In order to realize this high peak data rate, a new encryption algorithm is required.

We evaluate the performance of Rocca and show that Rocca can achieve 160 Gbps when encrypting data of large size. Modern CPUs are equipped with a dedicated instructions set for AES called AES New Instructions (AES-NI). As Rocca has the AES round function as its component, we can optimize the implementation by utilizing AES-NI. Specifically, we use \_mm\_aesenc\_si128() for AES's round function. For XORing two 128-bit values, we use mm xor si128() We also compare the performance with existing algorithms and demonstrate Rocca's advantage in terms of the performance. All evaluations were performed on a PC with Intel(R) Core(TM) i7-1068NG7 CPU @ 2.30GHz with 32GB RAM. For the fair comparison, we included Rocca as well as SNOW-V. Tiaoxin and AEGIS to Openssl (3.1.0-dev) and measured their performances. We used SNOW-V reference implementation with SIMD, which was given in [EJMY19]. For Tiaoxin-346 and AEGIS, we used implementations available at https:// github.com/floodyberry/supercop. The results are given in Table 7, and all performance results are given in Gbps. In TLS, data will be divided into chunks of  $2^{14} = 16384$  bytes or less before it is encrypted, the values in Table 7 are close to what we expect in practice. As shown, Rocca is 4.16 times faster than SNOW-V, and 3.10 times faster than AES-256-CTR in processing 16384 bytes message. It also outperforms both 128-bit algorithms which we tested. In encryption only mode, the initialization is performed once and only the encryption is iterated. While in AEAD mode, the initialization, associated data addition, encryption, tag generation and finalization are iterated. Here, the size of associated data is fixed to 13 bytes. In case of Rocca, the round function is iterated 20 times in

the initialization and finalization, respectively, which is equivalent to processing 1280 bytes of input. As a result, we expect  $1280/16384 \approx 8\%$  overhead to the encryption mode for 16384 bytes input. Additional overhead will be incurred by calling functions for the initialization, tag generation and finalization. The performance results on other CPUs are given in Appendix A, and Rocca achieves the best performance in other CPUs as well.

Size of input (bytes) Algorithms Key length 16384 2568192 64 1024 Encryption only 28.94 Gbps AEGIS-128 64.60 Gbps 63.43 Gbps 57.53 Gbps43.44 Gbps AEGIS-128L 128-bit 104.91 Gbps 102.71 Gbps 66.28 Gbps31.30 Gbps14.10 Gbps 13.61 Gbps Tiaoxin-346 v2 127.55 Gbps 126.73 Gbps 81.27 Gbps 33.78 Gbps AEGIS-256 66.02 Gbps 64.39 Gbps 59.09 Gbps 40.59 Gbps 26.28 Gbps 9.26 Gbps AES-256-CB0 9.35 Gbps 9.34 Gbps 9.51 Gbps 9.23 Gbps AES-256-CTR 58.19 Gbps 56.83 Gbps  $48.77 \mathrm{~Gbps}$ 38.90 Gbps 19.54 Gbps 11.40 Gbps ChaCha20 256-bit 11.49 Gbps 11.38 Gbps 10.63 Gbps 4.8 Gbps 43.39 Gbps 41.47 Gbps 41.59 Gbps 36.29 Gbps SNOW-V 25.78 Gbps Rocca 80.55 Gbps 1 77.71 Gbps 151.22 Gbps 98.30 Gbps 33.74 Gbps AEAD AEGIS-128 60.03 Gbps 55.16 Gbps 30.13 Gbps11.88 Gbps 3.62 Gbps AEGIS-128L 128-bit 97.55 Gbps 85.41 Gbps 31.14 Gbps9.96 Gbps 2.95 Gbps 2.54 Gbps 114.61 Gbps 31.67 Gbps Tiaoxin-346 v2 97.52 Gbps 9.16 Gbps AEGIS-256 61.16 Gbps  $57.51 \mathrm{~Gbps}$  $30.43 \mathrm{~Gbps}$ 11.26 Gbps3.37 Gbps 29.08 Gbps 18.78 Gbps AES-256-GCM 27.90 Gbps 8.41 Gbps 2.57 Gbps ChaCha20-Poly1305 7.60 Gbps 7.32 Gbps 5.98 Gbps 3.61 Gbps 1.24 Gbps 256-bit SNOW-V-GCM 30.20 Gbps 29.31 Gbps 19.14 Gbps 8.84 Gbps 2.73 Gbps 150.95 Gbps 131.41 Gbps 42.39 Gbps 12.75 Gbps 3.29 Gbps Rocca

Table 7: Performance Evaluation

The performance can be further improved by using new instructions set and/or optimizing the implementation. The new instructions set AVX512 contains \_mm512\_aesenc\_epi128(), which runs four 128-bit AES round functions in parallel. As Rocca uses four AES round functions in one state update, using \_mm512\_aesenc\_epi128() instead of four \_mm\_aesenc\_epi128()s can be improved by up-to 4 times.

### 6 Conclusions

To fulfill the basic requirements on the speed and security in 6G systems, i.e. 100 Gbps and 256-bit security, we are motivated to further study the generalized method to construct round functions based on the parallel calls to the AES round function, which was first studied by Jean and Nikolić in FSE 2016. As a result, an efficient AES-based AEAD scheme called Rocca is proposed, whose construction is only based on the AES round function and the 128-bit XOR operation supported by the SIMD instructions on model CPUs. In addition, we have performed a thorough study to understand the security of Rocca. According to the software implementation, Rocca can reach 150 Gbps in the AEAD mode, which is more than four times faster than SNOW-V designed for 5G systems. To the best of our

knowledge, Rocca is the first dedicated scheme targeting 6G systems and it also shows the potential to reach the basic requirements in such systems.

As future work, a parallelizable mode of Rocca would be interesting and beneficial for both environments equipped with multiple cores and not supported AES-NI.

#### Acknowledgments

The authors would like to thank Stefan Kölbl and the anonymous ToSC reviewers for the valuable comments and suggestions. Takanori Isobe is supported by JST, PRESTO Grant Number JPMJPR2031, Grant-in-Aid for Scientific Research (B)(KAKENHI 19H02141) and SECOM science and technology foundation. Fukang Liu is supported by Invitation Programs for Foreigner-based Researchers of NICT. Kosei Sakamoto is supported by Grant-in-Aid for JSPS Fellows (KAK-ENHI 20J23526) for Japan Society for the Promotion of Science. This research was in part conducted under a contract of "Research and development on new generation cryptography for secure wireless communication services" among "Research and Development for Expansion of Radio Wave Resources (JPJ000254)", which was supported by the Ministry of Internal Affairs and Communications, Japan.

### References

| [3GP18]  | 3GPP SA3. Study on the support of 256-bit algorithms                    |

|----------|-------------------------------------------------------------------------|

|          | for 5G. https://portal.3gpp.org/desktopmodules/Specifications/          |

|          | <pre>SpecificationDetails.aspx?specificationId=3422, 2018.</pre>        |

| [arm 21] | arm. Arm® architecture reference manual armv8, for armv8-a architecture |

|          | profile, 2021.                                                          |

| [cae18]  | CAESAR: Competition for Authenticated Encryption: Security, Applica-    |

|          | bility, and Robustness, https://competitions.cr.yp.to/caesar.html,      |

|          | 2018.                                                                   |

| [Cora]   | Intel Corporation. Intel Advanced Encryption Stan-                      |

|          | dard (AES) New Instructions Set. Official webpage,                      |

|          | https://www.intel.com/content/dam/doc/white-paper/                      |

|          | advanced-encryption-standard-new-instructions-set-paper.pdf.            |

| [Corb]   | Intel Corporation. Intel intrinsics guide. Official webpage,            |

|          | https://software.intel.com/sites/landingpage/                           |

|          | IntrinsicsGuide/.                                                       |

| [EJMY19] | Patrik Ekdahl, Thomas Johansson, Alexander Maximov, and Jing Yang.      |

|          | A new SNOW stream cipher called SNOW-V. IACR Trans. Symmetric           |

|          | Cryptol., 2019(3):1-42, 2019. doi:10.13154/tosc.v2019.i3.1-42.          |

| [ENP19]  | Maria Eichlseder, Marcel Nageler, and Robert Primas. Analyzing the      |

|          | linear keystream biases in AEGIS. IACR Trans. Symmetric Cryptol.,       |

|          | 2019(4):348-368, 2019. doi:10.13154/tosc.v2019.i4.348-368.              |

| [Gue 10] | Shay Gueron. Intel advanced encryption standard (aes) new instructions  |

|          | set, 2010.                                                              |

- [HII<sup>+</sup>22] Akinori Hosoyamada, Akiko Inoue, Ryoma Ito, Tetsu Iwata, Kazuhiko Mimematsu, Ferdinand Sibleyras, and Yosuke Todo. Cryptanalysis of rocca and feasibility of its security claim. *IACR Transactions* on Symmetric Cryptology, 2022(3):123–151, Sep. 2022. URL: https: //tosc.iacr.org/index.php/ToSC/article/view/9852, doi:10.46586/ tosc.v2022.i3.123-151.

- [ITU17] ITU. Minimum requirements related to technical performance for IMT-2020 radio interface(s), 2017. URL: https://www.itu.int/pub/R-REP-M. 2410-2017.

- [JN16] Jérémy Jean and Ivica Nikolic. Efficient design strategies based on the AES round function. In Thomas Peyrin, editor, Fast Software Encryption - 23rd International Conference, FSE 2016, Bochum, Germany, March 20-23, 2016, Revised Selected Papers, volume 9783 of Lecture Notes in Computer Science, pages 334–353. Springer, 2016. doi:10.1007/978-3-662-52993-5\\_17.

- [LaL19] Matti Latva-aho and Kari Leppänen. Key drivers and research challenges for 6G ubiquitous wireless intelligence, 2019. URL: http://jultika.oulu. fi/files/isbn9789526223544.pdf.

- [LIMS21] Fukang Liu, Takanori Isobe, Willi Meier, and Kosei Sakamoto. Weak keys in reduced aegis and tiaoxin. Cryptology ePrint Archive, Report 2021/187, 2021. https://eprint.iacr.org/2021/187.

- [Min14] Brice Minaud. Linear biases in AEGIS keystream. In Antoine Joux and Amr M. Youssef, editors, Selected Areas in Cryptography - SAC 2014 - 21st International Conference, Montreal, QC, Canada, August 14-15, 2014, Revised Selected Papers, volume 8781 of Lecture Notes in Computer Science, pages 290–305. Springer, 2014. doi:10.1007/978-3-319-13051-4\\_18.

- [MWGP11] Nicky Mouha, Qingju Wang, Dawu Gu, and Bart Preneel. Differential and linear cryptanalysis using mixed-integer linear programming. In Chuankun Wu, Moti Yung, and Dongdai Lin, editors, Information Security and Cryptology - 7th International Conference, Inscrypt 2011, Beijing, China, November 30 - December 3, 2011. Revised Selected Papers, volume 7537 of Lecture Notes in Computer Science, pages 57–76. Springer, 2011. doi:10.1007/978-3-642-34704-7\\_5.

- [Nat01] National Institute of Standards and Technology. FIPS 197 Advanced encryption standard., 2001.

- [Nik14] Ivica Nikolić. Tiaoxin-346: Version 2.0. CAESAR Competition, 2014.

- [RTL] Real-Time and Embedded Sys Lab. uops.info. Official webpage, https: //www.uops.info/.

- [SAG06] SAGE. Specification of the 3GPP Confidentiality and Integrity Algorithms UEA2 & UIA2. Version 1.1, ETSI/SAGE, 2006. https://www.etsi.org/deliver/etsi\_ts/133500\_133599/133501/ 15.02.00\_60/ts\_133501v150200p.pdf, 2006.

- [SAG11] SAGE. Specification of the 3GPP Confidentiality and Integrity Algorithms 128-EEA3 & 128-EIA3. document 2: ZUC specification. Version 1.6, ETSI/SAGE, 2011. https://www.etsi.org/deliver/etsi\_ts/133500\_ 133599/133501/15.02.00\_60/ts\_133501v150200p.pdf, 2011.

- [SLN<sup>+</sup>21] Kosei Sakamoto, Fukang Liu, Yuto Nakano, Shinsaku Kiyomoto, and Takanori Isobe. Rocca: An efficient aes-based encryption scheme for beyond 5g. IACR Trans. Symmetric Cryptol., 2021(2):1–30, 2021. doi: 10.46586/tosc.v2021.i2.1–30.

- [SSS<sup>+</sup>19] Danping Shi, Siwei Sun, Yu Sasaki, Chaoyun Li, and Lei Hu. Correlation of quadratic boolean functions: Cryptanalysis of all versions of full \mathsf MORUS. In Alexandra Boldyreva and Daniele Micciancio, editors, Advances in Cryptology - CRYPTO 2019 - 39th Annual International Cryptology Conference, Santa Barbara, CA, USA, August 18-22, 2019, Proceedings, Part II, volume 11693 of Lecture Notes in Computer Science, pages 180–209. Springer, 2019. doi:10.1007/978-3-030-26951-7\\_7.

- [The18] The ZUC design team. The ZUC-256 Stream Cipher. http://www.is. cas.cn/ztzl2016/zouchongzhi/201801/W020180126529970733243.pdf, 2018.

- [WP13] Hongjun Wu and Bart Preneel. AEGIS: A fast authenticated encryption algorithm. In Tanja Lange, Kristin E. Lauter, and Petr Lisonek, editors, Selected Areas in Cryptography SAC 2013 20th International Conference, Burnaby, BC, Canada, August 14-16, 2013, Revised Selected Papers, volume 8282 of Lecture Notes in Computer Science, pages 185–201. Springer, 2013. doi:10.1007/978-3-662-43414-7\\_10.

- [YJM20] Jing Yang, Thomas Johansson, and Alexander Maximov. Spectral analysis of ZUC-256. IACR Trans. Symmetric Cryptol., 2020(1):266-288, 2020. doi:10.13154/tosc.v2020.i1.266-288.

## A Software Implementation Results on Other CPUs

We show software implementation results on other CPUs in Tables 8 to 10. The evaluations were performed on Windows 10 Pro 21H1 for Table 8, Windows 10 Pro 21H2 for Table 9 and macOS Big Sur 11.4 for Tables 10. The difference of the environments affects the performance of some algorithms (e.g. AESGIS-256, AES-256-CTR and ChaCha20), Rocca shows competitive performance on all environments.

Table 8: Performance on Intel(R) Core(TM) i9-12900K CPU with 64 GB RAMs.

|                   |            |                         | <u></u>                 | 6.1 . (1 .  | >           |            |  |  |  |

|-------------------|------------|-------------------------|-------------------------|-------------|-------------|------------|--|--|--|

| Algorithms        | Key length |                         | Size of input (bytes)   |             |             |            |  |  |  |

| 1 iigoritiiiiis   | ney length | 16384                   | 8192                    | 1024        | 256         | 64         |  |  |  |

| Encryption only   |            |                         |                         |             |             |            |  |  |  |

| AEGIS-128         |            | 101.50 Gbps             | 99.13 Gbps              | 84.44 Gbps  | 63.66 Gbps  | 23.46 Gbps |  |  |  |

| AEGIS-128L        | 128-bit    | 143.87 Gbps             | 142.70 Gbps             | 126.06 Gbps | 77.85 Gbps  | 20.08 Gbps |  |  |  |

| Tiaoxin-346 v2    |            | 192.64 Gbps             | 189.01 Gbps             | 148.12 Gbps | 78.02 Gbps  | 21.05 Gbps |  |  |  |

| AEGIS-256         |            | 47.27 Gbps              | 46.65 Gbps              | 45.82 Gbps  | 43.09 Gbps  | 26.55 Gbps |  |  |  |

| AES-256-CBC       |            | 13.62 Gbps              | 13.69 Gbps              | 13.65 Gbps  | 13.68 Gbps  | 13.44 Gbps |  |  |  |

| AES-256-CTR       |            | 77.82 Gbps              | 77.49 Gbps              | 68.58 Gbps  |             | 22.04 Gbps |  |  |  |

| ChaCha20          | 256-bit    | 32.98 Gbps              | 32.99 Gbps              | 31.19 Gbps  | 15.58 Gbps  | 7.67 Gbps  |  |  |  |

| SNOW-V            |            | 62.00 Gbps              | 62.06 Gbps              | 56.88 Gbps  | 54.66 Gbps  | 27.09 Gbps |  |  |  |

| Rocca             |            | 235.45 Gbps             | 232.81 Gbps             | 218.54 Gbps | 160.92 Gbps | 54.65 Gbps |  |  |  |

|                   |            |                         | AEAD                    |             |             |            |  |  |  |

| AEGIS-128         |            | 92.66 Gbps              | 84.70 Gbps              | 38.52 Gbps  | 13.77 Gbps  | 3.68 Gbps  |  |  |  |

| AEGIS-128L        | 128-bit    | 125.42 Gbps             | 110.38 Gbps             | 41.49 Gbps  | 12.74 Gbps  | 3.21 Gbps  |  |  |  |

| Tiaoxin-346 v2    |            | 163.23 Gbps             | 138.51 Gbps             | 46.23 Gbps  | 13.65 Gbps  | 3.55 Gbps  |  |  |  |

| AEGIS-256         |            | 44.82 Gbps              | 42.46 Gbps              | 27.98 Gbps  | 12.53 Gbps  | 3.64 Gbps  |  |  |  |

| AES-256-GCM       |            | 57.87 Gbps              | 54.47 Gbps              | 29.12 Gbps  | 11.45 Gbps  | 3.13 Gbps  |  |  |  |

| ChaCha20-Poly1305 | 256-bit    | 21.99 Gbps              | 21.33 Gbps              | 13.99 Gbps  | 5.38 Gbps   | 1.81 Gbps  |  |  |  |

| SNOW-V-GCM        | 200-DIt    | 36.10 Gbps              | 34.81 Gbps              | 23.63 Gbps  | 11.26 Gbps  | 3.54 Gbps  |  |  |  |

| Rocca             |            | $210.67 \mathrm{~Gbps}$ | $185.90  \mathrm{Gbps}$ | 70.40 Gbps  | 22.59 Gbps  | 6.07 Gbps  |  |  |  |

**Table 9:** Performance on Intel(R) Core(TM) i9-11900 CPU@2.50GHz with 64 GB RAMs.

|                   |            | Size of input (bytes)   |                         |                         |            |            |  |  |  |  |

|-------------------|------------|-------------------------|-------------------------|-------------------------|------------|------------|--|--|--|--|

| Algorithms        | Key length | 16384                   |                         | 1024                    |            | 64         |  |  |  |  |

| Encryption only   |            |                         |                         |                         |            |            |  |  |  |  |

| AEGIS-128         |            | 97.67 Gbps              | 95.76 Gbps              | 79.37 Gbps              | 53.05 Gbps | 23.53 Gbps |  |  |  |  |

| AEGIS-128L        | 128-bit    | 142.44 Gbps             | 140.26 Gbps             | 112.17 Gbps             | 62.09 Gbps | 17.07 Gbps |  |  |  |  |

| Tiaoxin-346 v2    | 1          | 178.69 Gbps             | 173.88 Gbps             | 120.69 Gbps             | 60.13 Gbps | 18.79 Gbps |  |  |  |  |

| AEGIS-256         |            | 34.90 Gbps              | 34.53 Gbps              |                         |            | 18.83 Gbps |  |  |  |  |

| AES-256-CBC       | 1          | 13.71 Gbps              |                         |                         |            | 13.26 Gbps |  |  |  |  |

| AES-256-CTR       | 256-bit    | 84.30 Gbps              |                         |                         | 48.46 Gbps | 21.28 Gbps |  |  |  |  |