# Cryptographic Protection of Random Access Memory: How Inconspicuous can Hardening Against the most Powerful Adversaries be?

Roberto Avanzi<sup>1</sup>, Ionuț Mihalcea<sup>2</sup>, David Schall<sup>3</sup>, and Andreas Sandberg<sup>2</sup>

<sup>1</sup>Arm Germany, GmbH — roberto.avanzi@arm.com, roberto.avanzi@gmail.com <sup>2</sup>Arm Limited, UK — ionut.mihalcea@arm.com, andreas.sandberg@arm.com <sup>3</sup>School of Informatics, University of Edinburgh, United Kingdom — david.schall@ed.ac.uk

October 28, 2022

#### Abstract

For both cloud and client applications, the protection of the confidentiality and integrity of remotely processed information is an increasingly common feature request. It is also a very challenging goal to achieve with reasonable costs in terms of memory overhead and performance penalty. In turn, this usually leads to security posture compromises in products.

In this paper we review the main technologies that have been proposed so far to address this problem, as well as some new techniques and combinations thereof. We systematise the treatment of protecting data in use by starting with models of the adversaries, thus allowing us to define different, yet consistent protection levels. We evaluate the storage and performance impacts and, as far as we are aware for the first time, we consider also the impact on performance when the measured benchmarks are the only running tasks or when they are just one task in an environment with heavy additional random traffic, thus simulating a cloud server under full load.

Using advanced techniques to compress counters can make it viable to store them on-chip – for instance by adding on-chip RAM that can be as small as to  $1/256^{\text{th}}$  of the off-chip RAM. This allows for implementations of memory protection providing full confidentiality, integrity and anti-replay protection with hitherto unattained penalties, especially in combination with the repurposing of ECC bits to store integrity tags. The performance penalty on a server with a saturated memory subsystem can thus be contained under 2% with a memory overhead of 1/256 and even under 1% with a memory overhead of 1/128.

**CCS Concepts:** Security and privacy  $\rightarrow$  Hardware-based security protocols.

Keywords: Memory Encryption, Memory Integrity.

# Contents

| 1 | Introduction                                                                                                                                                                                                                                                                    | 3                                                               |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| 2 | Systematisation of the problem      2.1    Definitions                                                                                                                                                                                                                          | <b>5</b><br>5<br>7<br>8<br>9                                    |

| 3 | 3.3    Modes of operation      3.4    Memory integrity structures                                                                                                                                                                                                               | 9<br>9<br>10<br>10<br>11<br>12                                  |

| 4 | 4.1Scope of the comparisons4.2Technologies used for each level4.3Choice of the cryptographic parameters4.4Benchmarking environment4.5The simulated system4.6Benchmarking suite and testing methodology4.7Description of the plan of simulations4.8ECC-memory vs. non-ECC memory | <b>13</b><br>13<br>14<br>15<br>15<br>16<br>16<br>16<br>19<br>19 |

| 5 | 5.1 Unloaded system                                                                                                                                                                                                                                                             | <b>19</b><br>20<br>23                                           |

| 6 | Conclusions                                                                                                                                                                                                                                                                     | 26                                                              |

|   | References                                                                                                                                                                                                                                                                      | 27                                                              |

| A | Selected full benchmark results                                                                                                                                                                                                                                                 | 36                                                              |

| в | B.1Memory encryption primitivesB.2Authentication primitivesB.3Modes of operationB.4Memory integrity structures                                                                                                                                                                  | <b>42</b><br>42<br>44<br>46<br>49<br>53                         |

# 1 Introduction

With the ever growing availability and use of *Computing as a Service* (a.k.a. Cloud Computing), the question of confidentiality and integrity of remotely processed information is becoming paramount. The first means to protect information entrusted to a process or a virtual machine is, classically, *Access Control (AC)*, which is configured by the operating system for the former and by the hypervisor for the latter.

Cloud tenants are becoming increasingly aware that their data can be compromised by various adversaries. The simplest class of adversaries consists in other tenants running unprivileged malicious software on the same hardware, using attacks that can circumvent AC, such as side channel attacks ranging from cache contention [Hu92, Koc96, Bero5a, OSTo6] to exploitation of micro-architectural features such as speculative execution. (Regarding the latter class of attacks, after the first seminal works on Meltdown [LSG<sup>+</sup>18] and Spectre [KHF<sup>+</sup>19] too many papers followed to reasonably cite, so we refer the reader to the surveys [CBS<sup>+</sup>19, XS21].) Insider operators running privileged software represent another serious threat. Tenant data may even be targeted by entities having access to the actual computing hardware with the capability to perform physical side-channel attacks (see for instance the surveys [FGM<sup>+</sup>10, CA16, LGG<sup>+</sup>21]), or to directly compromise the memory contents by means of cold-boot attacks [HSH<sup>+</sup>09, YADA17, WCJ<sup>+</sup>21] or even at run-time by chip interposition [Kuh98, LJF<sup>+</sup>20]. Hardening the operating system and the hypervisor to prevent privilege escalation attacks is no longer considered sufficient, especially in light of the extreme complexity of modern system software stacks, for which one cannot have absolute reliance on countermeasures against software exploitation.

The same threats apply to client devices, where the compromised party may be the provider of banking, digital IDs, or gaming services. For these use cases, a compromise can lead to economic losses for the device owner or service providers. In the case of gaming, adversaries may be device owners involved in cheating or piracy. Banking applications and digital IDs need to be protected also against adversaries with temporary access to a device (that may have been left unattended).

This implies that steps that go beyond AC need to be put in place to isolate processes, services, or virtual machines from each other *and* the host environment, including the physical environment. Apart from putting processing elements and memory in the same tamper-proof package, these technologies rely on cryptography. Depending on the adversaries that are considered during their development, they range from simple memory encryption [Bes80, LTM<sup>+</sup>00, KFM05] to more advanced techniques to guarantee integrity of memory contents [MVS00, SCG<sup>+</sup>03, GSC<sup>+</sup>03, SLGL04, YGZ05, YEP<sup>+</sup>06, SOD07, RCPS07, CL10, HS10, CRSP11, Gue16a, WUS<sup>+</sup>17, SNR<sup>+</sup>18, JLK<sup>+</sup>23]. The latter range from tables of hashes in memory, each entry associated with a memory region, to structures that can detect any memory manipulation. These structures can be roughly described as variations on the theme of Merkle trees [Mer87], with the root node protected on-chip.

During the last four decades these technologies have been steadily improved to the point that performance and memory space overheads have become sufficiently acceptable to justify commercial deployment. Still, some more expensive proposals such as SGX [MAB<sup>+</sup>13] ended up being deprecated on client CPUs because the above mentioned penalties quickly degenerated when used to protect large processes. Indeed, after Bastion [CL10], the development of cryptographic isolation methods nearly halted, ushering an era of research in AC based mechanisms, starting with H-SVM [JAS<sup>+</sup>15]

and Hyperwall  $[SL_{12}]$  – until the announcement of the cryptographic mechanisms to protect the SGX enclave page cache [Gue\_16a] set the research in motion once again.

Even restricting ourselves to cryptographic techniques, as we do in this paper, it is very difficult to compare different technologies since any two papers on the subject will almost never use the same benchmarking suite, memory subsystem, cache sizes, and overall system load. Furthermore, most benchmarks are performed on systems without memory bus contention. This is not realistic, as the main application for these technologies seems to be cloud computing, servers on which hundreds of processes can run concurrently and contend for shared resources.

In this paper we systematise the comparison between various techniques and their combinations, including also some new ideas. We focus solely on technologies that only require the implementation of components inside the security perimeter of the *System-on-a-Chip (SoC)*, using external untrusted memory. Our tests consider both unloaded and fully loaded memory subsystems, by running traffic generators alongside the chosen benchmarking suite. We give here a short summary of our results:

- (i) We systematise the treatment of protecting data in use by starting with models of the adversaries, thus allowing us to define different, yet consistent protection levels.

- (ii) We confirm that protection levels that provide temporal uniqueness and integrity can have a lower performance impact than simple full *Memory Encryption (ME)* methods (with or without integrity) because they can use counter modes for encryption, thus removing the cipher from the critical path. However, this may change as memory subsystem load increases. Using a lightweight cipher optimised for memory encryption like QARMA [Ava17] provides better performance than the AES [DR02a] in all situations.

- (iii) Even though using longer Cache Lines (CLs) (say, 128B instead of 64B) may slightly degrade performance, it is better suited for memory protection because, all other things being equal, storage for Metadata (MD) such as MACs for integrity and counters will be halved, easing the pressure on the memory bus and on any MD cache. Again, this clearly holds on unloaded systems but the situation can change with increased memory traffic.

- (iv) Asynchronous integrity verification brings only a minor performance improvement, so it can be omitted, keeping implementations simpler and thus less bug prone.

- (v) For encryption methods based on counters, advanced counter compression makes it viable to store them on-chip. This allows for implementations of memory protection with anti-replay (i.e. *full integrity*) with extremely low performance penalties, especially in combination with the repurposing of ECC bits to store integrity tags. Our simulations show performance penalties smaller than 1% with a memory overhead of 1/128 (and smaller than 2% with a memory overhead of 1/256) even under heavy bus contention.

- (vi) We detail various trade-offs of performance penalty vs. resources if ECC memory is not available or including RAM in the SoC is not feasible.

The structure of the paper is as follows: In Section 2 on the facing page we model the types of adversaries that want to compromise memory contents, and accordingly we define the levels of protection required to thwart these adversaries. Section 3 on page 9 contains background material (an extended treatment is given in Appendix B on page 42). In Section 4 on page 13 we describe the new technologies that we add to the state to the art, the benchmarking environment, how we select the techniques we test in order to produce a clearly represented and understandable comparison. The results are reported and discussed in Section 5 on page 19. In Section 6 on page 26 we make practical recommendations for cloud and client use cases.

# 2 Systematisation of the problem

# 2.1 Definitions

The software-accessible volatile memory attached to a memory controller is viewed as an array of CLs, i.e. equally sized and contiguous memory ranges adjacent to each other. A CL is the smallest unit that will be encrypted and possibly authenticated by the systems we consider in this study. By CL length we only consider that of a CL in the *Last Level Cache (LLC)*, usually a System Cache.

The integrity information computed on a CL's plaintext or ciphertext is called an *integrity tag.* It is a *Message Authentication Code (MAC)*.

If a scheme provides *integrity* it is understood that it simply associates an integrity tag to each CL. A scheme provides *full integrity* if it also prevents any form of replay attack.

An encryption or authentication function provides *spatial uniqueness* when, if computed on equal inputs, but written to different locations, it results in different outputs. This is achieved by including the *Physical Address* (PA) of the encrypted or authenticated CL in the computation.

An encryption or authentication function is said to provide *temporal uniqueness* (also known as *freshness*) when repeated writes of the same plaintext to the same location result in different outputs. This is achieved by associating a non-repeating nonce, such as a counter, to each CL and including it in the computation of the function.

In what follows by *mode (of operation)* we understand a general purpose encryption mode of operation, A ME *mode* is understood to be an encryption mode of operation that has fixed input lengths, plaintext and ciphertext having the same size as a CL, and no associated data.

We use the terminology *on-chip* to denote components that are either part of the same die as the processing cores, or in/on the same package with tamper detection or prevention hardening.

#### 2.2 Problem statement and adversarial models

First of all, we need to define what we mean by *memory protection* and get beyond the hype that is markets ME as the apparent solution to all security issues – even if they have not been formalised.

Our first observation is that we cannot define what we mean by protection of an asset without first establishing the adversaries against which we intend to defend the asset. A suitable way to characterise the adversaries is by *Adversarial Models* (AMs) that depend on their type of access to the target devices and their resources, i.e. essentially budget. A possible taxonomy is the following:

AM0 The adversary is capable of accessing data that is outside the security perimeter of the complete system that contains the target components and on commonly accessible channels, such as messages in transit or data in storage. This includes network access.

- 6 Roberto Avanzi, Ionuț Mihalcea, David Schall, and Andreas Sandberg

- AM1 In addition to the capabilities of AM0, this adversary can run software on the target. Beside the exploitation of software vulnerabilities, this adversary can mount Rowhammer attacks [KDK<sup>+</sup>14, Mut19, MK20]. Within scope are also any side channel attacks that rely on software-exposed built-in hardware features to perform physical measurements, including time, or give partial or full read access to memory contents. Access to software-exposed power management control interfaces may enable glitching attacks, similar to those that that exploit a hardware interface (for instance [CVM<sup>+</sup>21]). Integrity violation is only a partial concern, as some effects of memory corruption are arguably made less effective by deploying ME.

- AM2 This adversary has physical access to the complete system that contains the target components, including its internals. They can gain access to exposed interfaces and communication buses but they do not have the capabilities to access on-chip communication interfaces. This adversary will only perform passive attacks, such as:

- Side-channel analysis that requires close proximity, contact or connection with the target device, which includes also recording or measurements of any off-SoC signals;

- Eavesdropping the content of off-SoC memory, either at run-time via memory bus probing, chip or module interposition [Kuh98, LJF<sup>+</sup>20], abuse of DMA channels [Fri16] or by means of a cold-boot attack [HSH<sup>+</sup>09, YADA17, WCJ<sup>+</sup>21].

- AM3 This adversary has the same level of access as in the previous model. However, they will also perform *active* attacks, such as blocking memory transactions or signals, replaying them, corrupting them, injecting new ones [KLR<sup>+</sup>20], performing some form of fault attack. Because of the similarity of the involved technologies, there is little difference in the expertise required beyond the previous adversarial model, whereas resources may need to be have a higher level of precision. The difference in complexity and cost and of the *countermeasures* is also a key factor in distinguishing the two models. Furthermore, since active attacks are more easily detectable, especially if they need to perform several tries triggering repeated failures, an adversary may choose not to mount them even if possessing the required capabilities. Examples of threats mounted by this type of adversary are [BBKN12, BR12, ZDC<sup>+</sup>12, MDH<sup>+</sup>13, CVM<sup>+</sup>21].

Within AM3, following the industry we distinguish two cases:

- AM3.(i) Adversaries that limit themselves to corrupt individual memory locations; and

- AM3.(ii) Adversaries that replace a memory region together with any associated MD.

- AM4 This adversary, in addition to all of the above capabilities, can mount highly invasive attacks at the chip or package level that go far beyond the previous models and require considerable experience, resources, and time to succeed. The attacks this adversary can mount range from micro-probing attacks [Sko17] to actual chip reverse engineering and editing using a Focused Ion Beam Microscope [TJ09, SAFT16, HTLW21].

The question that we answer in this study is: What technologies are available to protect the contents of data-in-use in RAM against the five types of adversaries defined above, and what are their costs in terms of memory overhead and performance?

Before we establish the defences against each type of adversary, some observations are in order.

**Remark 2.1** Against adversaries of type AMO the usual consensus is that no memory protection is necessary, even though attacks like Nethammer  $[LSR^+20]$  can corrupt the memory of a target system without a single attacker-controlled line of code on it, and therefore it can be argued that this model should be subsumed into AM1.

Remark 2.2 AM4 is out of scope for the research described in this paper.

**Remark 2.3** In what follows we shall assume that appropriate AC policies are in place to prevent unauthorised agents within the SoC from accessing memory.

## 2.3 Protection levels

In light of the above adversarial models, we define the following basic memory protection levels:

- L1 A simple encryption of the entire memory to be protected is implemented to defeat adversaries AM1 and AM2, except for: AM1 adversaries with a ciphertext-revealing side channel, or AM2; and that exploit memory access patterns as a side channel. The encryption function provides spatial uniqueness to reduce detection of data patterns. Temporal uniqueness and integrity verification are not provided as they are not required against the considered adversaries.

- L2 In order to thwart adversaries of type AM3.(i), each CL is encrypted and augmented with an integrity tag. No freshness is provided. This is not sufficient against Adversary AM3.(ii), that calls for either the integrity tags or the freshness information be protected themselves.

- L2+ Same as L2 except that freshness information is provided and used as an additional input to the encryption and integrity functions. This serves as partial hardening against adversaries of type AM1 with a ciphertext-revealing side channel or type AM2, that exploit memory access patterns as a side channel.

- L3 Against adversaries of type AM3.(ii), additionally, full integrity is provided.

We combine the following types of technologies to implement the above protection levels:

- 1. ME primitives (Section 3.1 on page 9) and modes (Section 3.3 on page 10);

- 2. Authentication primitives (Section 3.2 on page 10);

- 3. Integrity and anti-replay structures (Section 3.4 on page 11) such as tables and trees; and

- 4. Physical mechanisms to protect memory from tampering, such as including memory on-chip.

The last solution would in principle work if applied to the entire RAM and without any performance penalty, but it is impractical: for instance, for server applications it is not reasonable to put, say, 512GiB of RAM in the SoC package, for both space and thermal reasons.

**Remark 2.4** In this paper, we only consider solutions that need the security perimeter to be no larger than the physical package of the SoC. Hence, out of scope are "smart memory" technologies as those introduced in  $[AN_{17}]$ . These have cryptographic logic in the memory chips to attest themselves to the memory controller – allowing them to communicate on a secured channel only with that memory controller, such as the CXL.memory Integrity and Data Encryption (IDE) scheme  $[CXL_{19}]$ .

In order to properly address the threats they are meant to defend against, such smart memories are very expensive. They require the implementation of mutual attestation with the memory controllers, and must duplicate cryptographic engines in each memory chip, as putting the engines only on an on-board controller of the DIMM would not completely remove the risk of interposition. But the countermeasures which are the subject of this paper require cryptographic engines only in the SoC.

However, smart memories are suitable for physically remote memories, to implement the communication between the local SoC and the remote storage. This way, the protected address space can be expanded beyond what the local MD would allow, esp. if the latter is on-chip.

We now discuss the protection levels offered by some state of the art solutions.

- (i) The Memory Encryption Engine (MEE) in Intel's SGX [Gue16a] is a L3 solution.

- (ii) Memory protection in Intel's TDX is provided by the Multi-Key Total Memory Engine with Integrity (MKTMEi) [Int21c, Section 2.A]. It provides encryption without freshness, and integrity with 28b tags. These tags are computed using SHA-3-256, and are stored together with the ciphertext in 28 repurposed ECC bits [Int21a, Section 16.2]. In our terminology the MKTMEi is a L2/MirE solution, where MirE means MACs in repurposed ECC bits.

- (iii) Amd's SEV [KPW16] uses AES-128 in a construction that gives spatial uniqueness. According to our classification, SEV is a L1 solution.

- (iv) SYNERGY [SNR<sup>+</sup>18] is a ECC memory specific proposal. It is a L3/MirE solution.

- (v) CSI:Rowhammer [JLK<sup>+</sup>23] improves on SYNERGY's usage of the ECC bits by shortening the data MACs to 56 bits to make room for parity bits. It implements a L2/MirE solution.

## 2.4 System level view of the technical solution

To answer the question posed in Section 2.2 on page 5 we introduce a set of HW components, of which the central one is called the *Memory Protection Engine (MPE)*. This is not a new concept: all cryptographic memory protection designs cited so far use such a component, usually called somewhat reductively a *Memory Encryption Engine (MEE)* even when it does more than encryption.

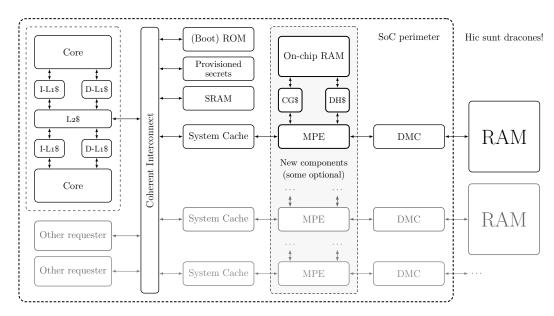

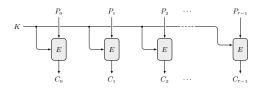

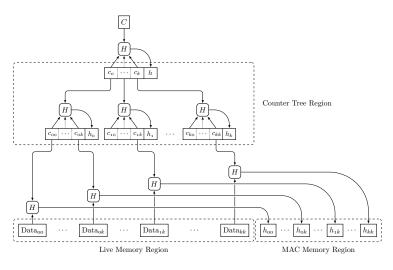

Its placement in a SoC system level view is depicted in Fig. 1 on the next page. A MPE sits between the interconnect or a System Cache that branches off the interconnect on one side, and a memory controller on the other side, which in turn is connected to RAM. The MPE can optionally have: caches, namely a *Counter Group (CG)* and a *Data Hash (DH)* cache; internal buffers (not depicted); and it may have access to a certain amount of on-chip RAM.

The memory protection technologies that we study in this paper are implemented in the MPE.

Figure 1: Simplified system level view of a SoC with Memory Protection Engine(s)

## 2.5 Cost indicators

It is not only important to know whether we have a solution to a problem: For real-world applications it is critical to know how *expensive* is the solution.

The two principal cost indicators are the performance penalty and the memory overhead. Area and power constraints restrict which solutions can be considered for viability, but relaxing these constraints can often be justified in the presence of a strong market requirement. On the other hand, a solution that impacts performance or memory availability too heavily will face major acceptance hurdles. For this reason, we focus mainly on performance penalty and memory overhead.

# 3 Background

Several technologies have been used to protect memory contents, and many have been cited in the introduction. This is a short summary of the techniques we considered in the development of this paper. An extended version of this summary is given as Appendix B on page 42.

#### **3.1** Memory encryption primitives

Block ciphers are the most common type of functions used to encrypt memory. In *direct encryption* they are applied block-wise to the plaintext to generate the ciphertext. In *One-Time Pad (OTP)* encryption, the encryptions of successive values of a counter are XOR-ed block-wise to the plaintext.

The most important block ciphers for ME are: The standard general purpose memory encryption block cipher AES [DR02a, DR02b]; The 64b block cipher PRINCE with design goals of low latency and low area [BCG<sup>+</sup>12] has been designed as a compact and fast ME cipher; and the *Tweakable*

Block Cipher (TBC) QARMA [Ava17] that has been designed specifically for the ME use case, and includes a third input beside text and key, called tweak, to select the function applied to the text in an agile way in order to facilitate the design of secure modes of operation.

Stream ciphers can also be used, but they lack parallelisability and have an initial high latency, and there are some newer designs like the block cipher SPEEDY [LMMR21], which is however difficult to use in some use cases because of its unusual block size of 192 bits.

In this paper therefore we shall use AES and QARMA. Note that the latter has been used in various papers on cryptographic memory protection  $[UWM_{19}, JLK^{+}2_{3}]$ .

#### **3.2** Authentication primitives

Standard hashing functions such as SHA-2 [NIS12] or SHA-3 [NIS15] can be turned into a MAC by means of established constructions such as NMAC or HMAC [BCK96] and used to verify memory integrity. However, the resulting schemes are very slow and not intrinsically parallelisable.

SipHash [AB12] is a cryptographically strong *Pseudo-Random Function (PRF)* that is used as MAC. We do not consider it here because it is based on 64b integer additions, which makes the latency of HW implementations too high, and it is not parallelisable.

Encrypted or hashed Universal Hash Functions (UHFs) [CW77, CW79] are a better choice. UHFs admit fully parallelisable constructions such as polynomial or multi-linear functions of the input, computed over a binary Galois field which allows for HW-friendly carry-less arithmetic. Intel uses an encrypted multi-linear hash over  $\mathbb{F}_{2^{64}}$  in SGX [Gue16b].

**Remark 3.1** The UHF-based MAC constructions always encrypt the universal hash because an adversary would be otherwise able to successfully manipulate it. However, a universal hash is assumed to be beyond the reach of the adversary if stored in MPE-private on-chip memory. Even though we do not use on-chip RAM for DHs (except for one single test run), this principle applies also to on-chip caches: The DHs are encrypted only when evicted from the latter, and the cached values can be verified more efficiently because an encryption or decryption operation is avoided. This approach also offers reliability and security advantages, as described in Remark 4.1 on page 13.

TBC-based *Parallel MACs (PMACs)* [Rogo4] can also be used. PMACs are slightly more expensive than encrypted UHFs because the text is first processed by encryptions instead of Galois multiplications, but they have the advantage that they can be used for error detection and correction beside integrity, as in IVEC [HS10], SYNERGY [SNR<sup>+</sup>18], and CSI:Rowhammer [JLK<sup>+</sup>23].

A checksum of the plaintext can also be used, as in Rogaway's *Offset Codebook mode (OCB)* mode [Rogo4] (cf. Fig. 41 on page 48), provided that the encryption offers freshness, block-wise spatial uniqueness, and good per-block diffusion properties. However, for protection levels that provide freshness we use OTP modes to reduce critical path length, and since in this case an encrypted checksum would leave the ciphertext malleable, we need to use a proper MAC.

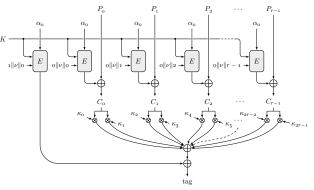

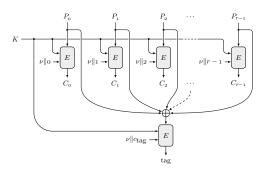

#### 3.3 Modes of operation

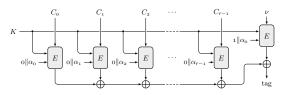

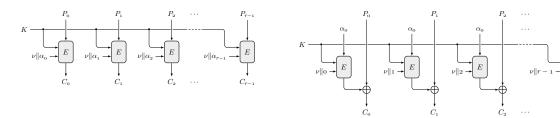

For direct encryption, spatial uniqueness is achieved by using the PA as the cipher's tweak. To achieve this with the AES, a non-tweakable block cipher, we use it in Rogaway's XOR, Encrypt, and

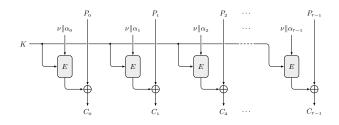

XOR (XEX) construction XEX construction [Rogo4]. XEX is defined as  $C_i = E_K(P_i \oplus M_i) \oplus M_i$ . In other words, a tweak-derived mask is added to the plaintext and to the ciphertext. The first mask  $M_0$  is derived by encrypting the tweak, and the successive masks  $M_i$  for  $i \ge 1$  are obtained by multiplying the first mask by a fixed sequence of values. Using a single finite field element  $\gamma$  we can put  $M_i = \gamma^i \cdot M_0$ . This results in a variant of Rogaway's OCB mode [Rogo4] and is represented graphically in Fig. 35 on page 47. With a TBC such as QARMA, the address of each block can be used directly in the tweak, cf. Fig. 36 on page 47, without the need for Galois multiplications.

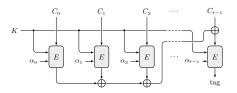

Let us now consider OTP encryption,. The AES is used in a counter mode as depicted in Fig. 34 on page 47. Intel's SGX uses a variant of the *Galois/Counter Mode (GCM)* mode, namely it uses a counter-based OTP encryption followed by a *multi-linear (ML)* Carter-Wegman UHF (in place of GCM's polynomial authenticator). QARMA is used in the *CounTeR in Tweak (CTRT)* mode [PS16], depicted in Fig. 37 on page 47. We use a ML UHF, except when we are repurposing the ECC bits to store the MACs, in which case we use a PMAC as mentioned earlier.

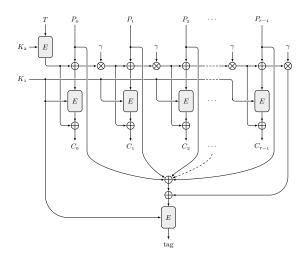

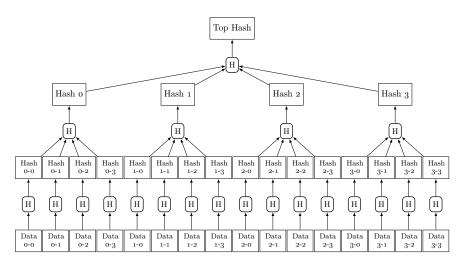

#### 3.4 Memory integrity structures

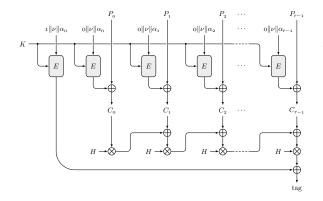

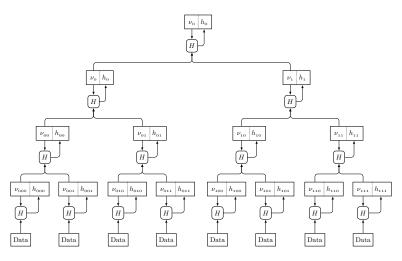

The technically simplest way to ensure full integrity of untrusted memory is to use a *Merkle Tree (MT)* [Mer80], depicted in Fig. 44 on page 49, MTs were used in one of the earliest architecture for memory protection, the XOM system [MVS00]. In [GSC<sup>+</sup>03] MT nodes are cached, whereby a cached node is treated as trusted, halting the tree verification traversal. This reduced the performance penalty from a factor 10 to just 22%.

In [RCPS07] it is observed that if a counter-based mode is used, the counters are often shorter than the hashes in a common MT (say, 64b vs. 128b). Then, it is proposed to build the MT on the memory region containing the counters, reducing the size of the MT. This smaller tree is called a *Bonsai Merkle Tree (BMT)*.

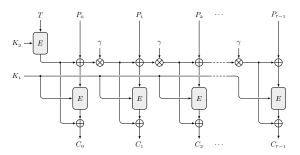

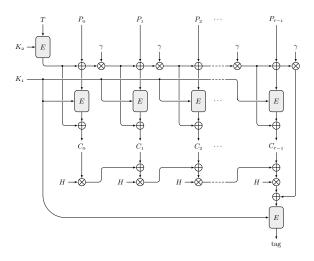

Hall and Jutla in [HJ05] build on this idea by repeatedly using a counter and a hash to protect a groups of counters, instead of just hashing them recursively into a MT. This way a new type of tree is constructed, the *Parallelisable Authentication Tree (PAT)*, where the nodes are *pairs*  $(\nu, h)$ consisting of a nonce  $\nu$  and a MAC h computed over the children nodes (cf. Fig. 45 on page 51).

Intel's [Gue16a], cf. Fig. 46 on page 51, reorganizes the PAT by grouping all the counters in a set of sibling PAT nodes together with the MAC that in the parent node of the PAT. The nodes of the new resulting *Counter Tree (CT)* are called CGs and in Intel's implementation contain eight 56b counters and a 56b MAC.

A different type of tree is the *Tamper-Evident Counter (TEC)* treen  $[ECL^+o_7]$  (cf. Fig. 47 on page 51). In the TEC tree a wide block cipher in a direct mode is used to encrypt data or counter blocks together with a copy of the parent counter and with the address of the block. The correct decryption of the address guarantees authenticity.

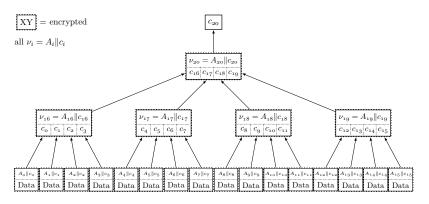

An important optimisation consists in using *split counters*. In [YEP<sup>+</sup>06] a group of *a* counters is replaced by a group composed of a *major counter* and a' > a smaller, *minor counters*, so that the two types of CGs have the same size. The freshness information associated to a child consists of the concatenation of the common major counter with the minor counter corresponding to the child. The increased arity (for instance, from a = 8 to a' = 64) reduces both storage overhead for counters and tree depth. When a minor counter overflows, the major counter in the same group is increased, all

|                                                                                 |             | Overhead     |                |  |

|---------------------------------------------------------------------------------|-------------|--------------|----------------|--|

| Type of Tree                                                                    | CL size:    | 64B          | 128B           |  |

| Merkle Tree $\ell_H = 128, a = 4$ , resp. 8                                     |             | $33\cdot3\%$ | 16.7%          |  |

| Monolithic CT with embedded MAC and $\ell_c = \ell_h = 56-64$                   |             |              |                |  |

| • $\ell_H = 64; n = 1; a = 8, \text{ resp. 16}$                                 |             | 26.8%        | 12.9%          |  |

| • $\ell_H = 32; n = 1; a = 8, \text{ resp. 16}$                                 |             | 20.5%        | 9.79%          |  |

| • $\ell_H = 32; n = 2; a = 8, \text{ resp. 16}$                                 |             | 17.4%        | 8.23%          |  |

| • $\ell_H = 32; n = 4; a = 8, \text{ resp. 16}$                                 |             | 15.8%        | $7{\cdot}45\%$ |  |

| BMT with $a = 8$ , resp. $a = 16$ , and $\ell_H = \ell_h =$                     | 64          | 29.2%        | 13.4 $\%$      |  |

| Split CT with embedded MAC and $\ell_c = \ell_h = 56-64$                        |             |              |                |  |

| • $\ell_H = 64; n = 1; \ell'_c = 6, \text{ resp. } 7; a = 64, \text{ resp. } 7$ | esp. 128    | 14.1 $\%$    | 7.04%          |  |

| • $\ell_H = 32; n = 1; \ell'_c = 6, \text{ resp. } 7; a = 64, \text{ resp. } 7$ | esp. 128    | 7.84%        | 3.91%          |  |

| • $\ell_H = 32; n = 2; \ell'_c = 6, \text{ resp. } 7; a = 64, \text{ resp. } 7$ | esp. 128    | 4.71%        | <b>2.34</b> %  |  |

| • $\ell_H = 32; n = 4; \ell'_c = 6, \text{ resp. } 7; a = 64, \text{ resp. } 7$ | esp. 128    | 3.15%        | 1.57%          |  |

| • $\ell_H = 32; n = 1; \ell'_c = 3; a = 128$ , resp. 25                         | 6           | 7.04%        | 3.52%          |  |

| • $\ell_H = 32; n = 2; \ell'_c = 3; a = 128, \text{ resp. } 25$                 | 6           | 3.91%        | 1.95%          |  |

| • $\ell_H = 32; n = 4; \ell'_c = 3; a = 128$ , resp. 25                         | 6           | 2.35%        | 1.17%          |  |

| PAT with $a = 8$ , resp. $a = 16$ , and $\ell_H = \ell_h = 6$                   | 64          | 28.6%        | 13.3%          |  |

| TEC tree with $a = 8$ , resp. $a = 16$ , and $\ell_H = \ell$                    | $_{h} = 64$ | 42.9%        | 20.0%          |  |

Table 1: Memory Overhead of Various Types of Integrity Trees at 32b and 64b security levels

**Legend:**  $\mathcal{L}_{CL}$ ,  $\ell_H$ ,  $\ell_h$ ,  $\ell_c$ , and  $\ell'_c$  are the bit lengths of a CL; a DH or MAC; of a hash value or MAC embedded in a CG; of a monolithic or major counter; and a minor counter, respectively. a is the arity of a CG, i.e. the number of its monolithic or minor counters; and n is the number of CLs a MAC covers.

minor counters in the group are reset to zero, and the memory blocks corresponding to the minor counters in the same group must be re-encrypted (for leaf nodes), or the hashes recomputed (for non-leaf nodes) in bulk with the updated freshness information. These *Read-Modify-Write (RMW)* operations may affect performance, but in general split counter trees represent a major performance improvement with respect to non-split, i.e. monolithic, counters.

## 3.5 Memory overhead of integrity trees

In Table 1 we compare the integrity trees we encountered here. We assume that CGs have the same size of a CL, also if tags are embedded, whereas a MAC can cover 1, 2, or 4 CLs.

**Remark 3.2** There are essentially only two ways of reducing memory overheads: (i) compressing the MD or (ii) move it somewhere else ("sweeping-under-the-rug"), for instance on-chip. The latter can improve performance, simplify memory management (no carveout has to be identified and no

special AC policies have to be configured and locked) but comes with a high hardware cost. The former approach has a lower hardware cost, but the impact on performance may be negative.

For counters, compression means the use of split counters. This improves performance. Sweepingunder-the-rug means storing the counters on-chip. The two approaches may be combined.

For MACs, compression means either to use shorter MACs or to compute a MAC on several CLs. The first option may adversely affect security. The second option may considerably worsen performance. Sweeping-under-the-rug can mean storing the MACs on on-chip memory or repurposing the ECC bits for MACs.

# 4 Setup and parameters of the study

## 4.1 Scope of the comparisons

Depending on the level, several variants of the involved technologies may be combined. These technologies are summarized in the following list, where the entries marked with  $\dagger$  contain technologies that are new contributions in this paper; and those marked with  $\star$  describe variations not hitherto compared to each other to the best of our knowledge:

- Use of the AES or QARMA ciphers;

- Size of the MACs (32b or 64b);\*

- Type of counter tree: monolithic, 2-way split or 3-way split;<sup>†</sup>

- Various choices for the size of CG\$ and DH\$.

- Use of on-chip memory for hashes and/or counters;<sup>†</sup>

- Repurposing of ECC bits for data MAC storage;

- Synchronous or asynchronous integrity checking;

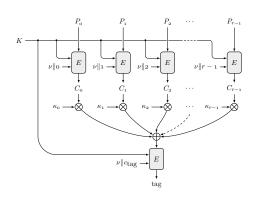

- Use of single MACs covering multiple CLs, with cached incremental hashing;<sup>†</sup>

- Arity variations in the CGs;

- We consider both 64B and 128B CLs;<sup>\*</sup> and, finally

- Runs are measured on two types of systems: systems where only the benchmarking suite is running; and systems where additional traffic is saturating both the MPE and the available memory subsystem bandwidth.\*

**Remark 4.1** A new idea we adopt in our implementations consists in evicting DHs that are stored in normal RAM in blocks, which are encrypted directly. We use this technique only if the MACs are 32 bits long. In this case, four DHs are actually encrypted directly as a single 128b block. Any attempt to corrupt one DH will corrupt all four with high probability, vastly increasingly the likelihood of detection. By doing this we increase both security and the robustness of the system, and also speed up integrity verification of CLs that are fetched from memory when the hash is already in the DH\$, because the latter does not have to be decrypted.

If freshness is available, then the four minor counters corresponding to the four DHs that must be directly encrypted together and their common major (and possibly middle) counter are concatenated together. This is used to create a tweak for QARMA-128.

**Remark 4.2** Many of the above choices are to some extent independent of each other. However, the selection of the encryption and authentication schemes follow from chosen the level of protection and primitives, as well as on other factors, i.e. whether counters are kept in on-chip memory or ECC bits are repurposed for data MACs. This will be clear in the next section.

**Remark 4.3** When multi-CL MACs are used, each CL is still encrypted individually and is associated with a monolithic or major counter. Hence, evicting a CL from the LLC will not require the re-encryption of any adjacent CL.

# 4.2 Technologies used for each level

We list the technologies used to implement the protection levels defined in Section 2.3 on page 7.

- L1 If AES-128 is the chosen encryption primitive, a CL is encrypted using the XEX mode (Fig. 35 on page 47), with the PA as the tweak. If QARMA-128 is chosen, it is used in Tweaked *Electronic Codebook (ECB)* mode as in Fig. 36 on page 47, with the PA as tweak.

- L2 The same encryption modes are used for L1. Hashing is done by a ML UHF at 32 or 64 bits. The hashes are encrypted block-wise when they are evicted from the DH\$ in CL worth groups. This means that an evicted data hash block is encrypted using its own PA. Since this address is linearly related to the PAs of the corresponding CLs, there is no security concern (all security proofs of the similar *Authenticated Encryption (AE)* modes carry over). This approach has good security and reliability implications, cf. Remark 4.1 on the previous page.

- L2+ This level provides freshness over L2. A counter mode is used with both AES and QARMA, where the text input is a concatenation of PA and freshness information for AES-128, and CTRT mode (Fig. 37 on page 47) is used with QARMA. We recall that this level does not offer protection against active adversaries with access to the memory bus if both counters or MACs are in off-chip memory. Hence, there is no need to feed the freshness to the MAC computation function, which has the positive side effects of eliminating a potentially blocking dependency in the hardware. Therefore, we use direct encryption for DHs as in L2.

- L3 We use the same encryption mechanism as in L2+. Full integrity is achieved by preventing the adversary from successfully tampering with either the DHs or the CGs *and* including the freshness in the tag computation. Thus, an adversary may still be able to replace a CL together with either its DH or CG, but not both.

Protecting the DHs or the CGs is achieved by either using an integrity tree, or by storing them on-chip: we choose to consider only the protection of the CGs, as they require less memory.

- oCC on-Chip Counters. Applied to L2+ it gives an L3 level of protection, provided that the freshness be included in the tag computation. This is due to the fact that we assume counter on-chip memory to be non-interposable and MPE private, hence outside adversarial control.

- MirE *MACs in repurposed ECC bits.* Eliminates the need to reserve memory for the MACs , and only memory for counters needs to be allocated (which, with oCC, is on-chip), at the price of a

slightly higher latency for writes to reach the memory controller (but less writes overall) and for processing reads. MACs are still accessible to a HW capable adversary. Hence freshness information, if available, *must* enter the MAC computation, otherwise birthday bound replay attacks apply. Following [SNR<sup>+</sup>18, JLK<sup>+</sup>23], the tag is computed using QARMA<sub>5</sub>-64- $\sigma_0$  and is truncated to 56b to reserve eight bits for parity.

## 4.3 Choice of the cryptographic parameters

In the choice of parameters such as lengths of keys and MAC, the fundamental difference between encryption and authentication is that the encryption parameters must provide long term confidentiality, whereas authentication needs only to deter an adversary, since a system that can monitor unrecoverable integrity violations may determine that unusual activity is occurring.

As a result, the following parameters are recommended:

- Encryption keys should be at least 128 bits long. A single key may be used for the AES in the XEX construction. We note that even on a quantum computer, the complexity for a key search attack on AES-128 given as the product of total number of decomposed gates and full depth required is around 2<sup>160</sup> [BNS19, JBS<sup>+</sup>22]. The block size must also be at least 128 bits. For this reason from the QARMA family we choose QARMA-128 over QARMA-64 for encryption.

- 2. For a MT the required hash length is 128b to practically prevent replay attacks.

- 3. The recommended length for the authentication key is 128b.

- 4. Data MACs should be at least 32b long.

- 5. Monolithic counters must be at least 64b long. The aggregated length of a major counter with a minor counter (or major plus middle plus minor) should be also at least 64 bits.

As a consequence of the above choices, a successful replay attack on the memory of a L3 system would require both the counter and the MAC to be repeated, with complexity  $2^{64} \times O(2^{64/2}) = O(2^{96})$ .

### 4.4 Benchmarking environment

Developing new features for integration into processors and SoCs is an expensive and error-prone endeavour with multiple layers of risk. To provide a comparison of potentially thousands of combinations of techniques it would financially unjustifiable to implement each variant in silicon.

A solution to this problem lies in prototyping, i.e. the creation of an approximate implementation of the desired features that can be integrated, tested, and benchmarked on various metrics. This allows us to create very accurate models without having to implement all details. For instance, the latencies of cryptographic primitives are derived from actual implementations, and they are inserted as delays into a simulation framework, simplifying the implementation of the simulation and speeding it up at the same time.

The prototypes used in this paper are built in the gem5 simulator [BBB<sup>+</sup>11, LAA<sup>+</sup>20]. gem5 allows engineers to build software versions of hardware components typically included in computer systems. The framework also helps abstract away the interfaces between components. The components can thus be combined programmatically and configured at run-time. It includes very precise models for several common CPU cores.

### 4.5 The simulated system

The simulated system is a single core A72, with a 2GHz CPU frequency and a 1GHz system frequency. The CPU cache hierarchy includes separate L1 instruction (48KiB, LRU replacement policy, 3-way set associative, 1 cycle latency) and data (32KiB, LRU replacement policy, 2-way, 1 cycle latency) caches, and a L2 unified cache (1MiB, tree-PLRU replacement policy, 16-way, 5 cycles latency). The latter plays in our prototyping the role of the System Cache. The memory system consists in 16GiB DRAM as dual-rank DDR4 DIMMs. External memory has a load and access pattern dependent latency on the order of  $\approx$ 75ns in most cases, and a bandwidth asymptotically reaching of 14GiB/sec at higher latencies (up to 300ns).

The MPE-private caches are 4-way set associative with a LRU replacement policy. The on-chip memory has a access latency of 50ns, and a bandwidth of 20GiB/sec.

We also assume that the SoC is implemented in a 7nm process, in order to re-use the information about latencies from [Ava17], for instance a latency of 15.76ns for a pipelined implementation of AES-128, of 4.8ns for QARMA<sub>11</sub>-128- $\sigma_1$  and 2.2ns for QARMA<sub>5</sub>-64- $\sigma_0$ . The latter two implementations are also pipelined, and are included in the Qameleon NIST Lightweight Cryptography Standardization Process submission [ABB<sup>+</sup>19]. This latency of QARMA<sub>5</sub>-64- $\sigma_0$  is also used in [JLK<sup>+</sup>23].

### 4.6 Benchmarking suite and testing methodology

We benchmark the chosen compositions of technologies on the SPEC2006 suite [Heno6].

Simulations of hardware systems via software models such as gem5 have lengthy execution times even for short workloads. As shown in [San14], a typical SPEC benchmark could take around a month to run, making it infeasible for rapid prototyping and analysis. Our benchmarking strategy relies, instead, on previously characterized SPECint 2006 workloads [SPHC02].

Each SPEC2006 benchmark has been analysed at run-time and split into a set of small workloads that distill the performance characteristics of the initial benchmark. The workloads are weighted to more closely approximate the significance of their content to the entire benchmark. In our case 10 workloads of roughly 30 million instructions each are used to estimate performance for each benchmark in the suite. After each of these is run with our test system, the metrics of interest are combined to produce one representative result for the entire benchmark. The combining step takes into account the values produced by the workloads and their weights.

#### 4.7 Description of the plan of simulations

Comparing thousands of different configurations is not only unfeasible in hardware, but it would require too much time and resources also in a simulated environment, not to speak of the difficulties of properly presenting the data. For this reason as have planned a tour through the jungle of combination, in various stages, each stage resulting in a selection of cases to be compared in the successive ones with added variability in only a few parameters.

We use shorthands to describe the various configurations. They have the following form:

Level / {additional technologies} / Cipher / CL length / MAC length

where the optional field additional technologies may include mono (for monolithic counters), split (counters), oCC, or MirE. The default CL length is 64B, except when indicated or when the CGs are on chip, in which case it is always 128B. The default MAC length is 56–64b. Furthermore, "{Intel} TDX" is equivalent to L2/AES/MirE, "{Intel} SGX" to L2/AES/mono, and "{AMD} SME" to L1. oCC always implies split. The shorthand L3/oCC is used to denote the combination of L2+ with oCC. We understand L3 *without* oCC as a full integrity capable scheme based an on integrity tree and *neither counters nor hashes on-chip*.

Stage 1 We initially focus on the state of the art and our most basic technologies.

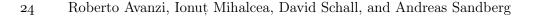

We compare AMD SME (i.e. L1 with AES), L1/QARMA, L2/AES, Intel TDX (i.e. L2/AES/MirE), L2/QARMA, L2/QARMA/MirE, L2+/QARMA with both monolithic and split counters, SGX, L3/QARMA with split counters – all with and without a DH\$ if it is not fixed by the manufacturer's architecture. We also compare in some cases the performance with 32b vs. 64b MACs.

For SGX, hash encryption is OTP as described by intel. We use this method also for the split counters variant of it (L3/AES/split), and in any case where counters are monolithic or MACs are 64 bits long, such as L2/QARMA/64b MACs, L2+/QARMA/split/64b MACs, and L3/QARMA/split/64b MACs. For every other variant counters are split, MACs are 32b, and encrypted in groups, directly.

For levels with freshness, the CG\$ is 64KiB as in SGX, to level the comparisons.

These principles apply to every successive stage as well, except where explicitly indicated.

From now on, MACs are 32 bits long, directly encrypted in groups of four, except where SGX is benchmarked, the MirE technology is used, or where explicitly indicated.

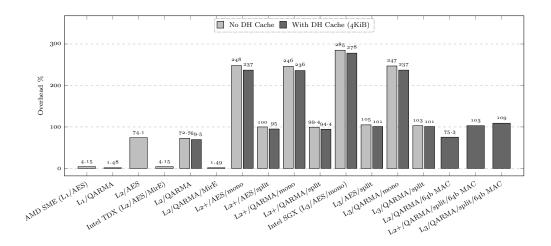

Stage 2 For L2, L2+, and L3 only, we study the impact of the sizes of the two MPE caches. The possible sizes of the DH\$ are 4KiB, 16KiB, and 64KiB. The possible sizes of the CG\$ are 16KiB, 64KiB, 256KiB, and 1MiB. This simulation set is restricted to QARMA only for encryption, as the AES results would show similar relative performances.

Starting with Stage 3, we assume that the MPE has both private caches, where the size of the DH<sup>\$</sup> is 16KiB, and the size of the CG<sup>\$</sup> to 256KiB. Similarly, levels L2+ and L3 will use split counters, except when explicitly indicated, or when SGX is benchmarked.

Stages 3 and 4 are intermediate stages towards the more interesting combinations, and we restricted the simulation set to QARMA only for the encryption, as AES results would be substantially equivalent.

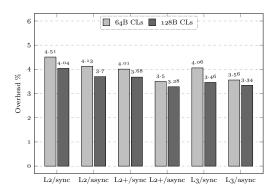

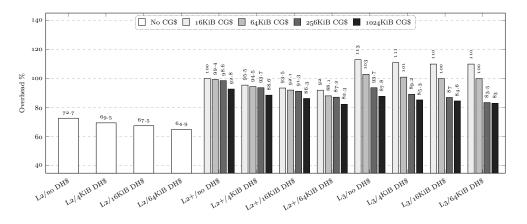

Stage 3 Consider 64B and 128B CLs for L2, L2+, and L3. A CG and a CL have the same size.

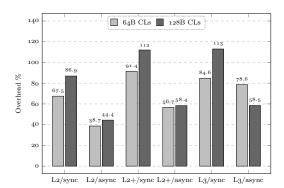

**Stage 4** We compare synchronous to asynchronous verification for L2, L2+, and L3.

The next few steps will test the impact of the techniques mentioned in Remark 3.2 on page 12.

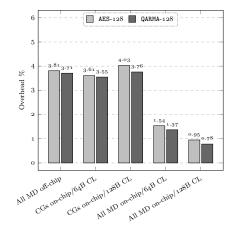

Stage 5 We analyse the impact of on-chip memory on realisations of full integrity levels.

As the MAC overhead is larger than the CG overhead, we do not consider the case where the MACs (actually, hashes) are on-chip and the counters off-chip.

Since these variants together with the ones in the next stage are amongst the most promising ones in terms of performance, we run them with both AES-128 and QARMA-128.

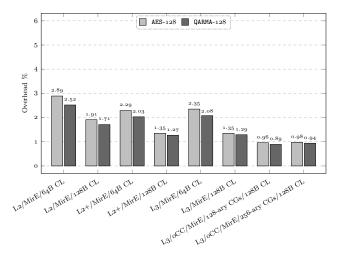

Stage 6 We consider here the performance impact of repurposing the ECC bits for tags (see Appendix B.5 on page 53). We compare four schemes: L2, L2+, L3, and L3/oCC, all with and without MirE. To keep the total number of tests manageable, we measure the impact for both 64B and 128B CLs when the counters are off-chip, and consider only 128B CLs oCC.

If we store MACs in the ECC tag bits, we do not need a DH cache, and the MACs are computed as described in Appendix B.2.4 on page 46.

The types of high-arity CGs on-chip we consider are:

- 128B CLs and CGs with: 128 7b minor, 8 8b middle, and 1 64b (49b) major counters; This results in a memory overhead of 1/128.

- 128B CLs and CGs with: 256 3b minor, 32 6b middle, and 1 64b (55b) major counters;

This results in a memory overhead of 1/256.

What follows is some off-path branching:

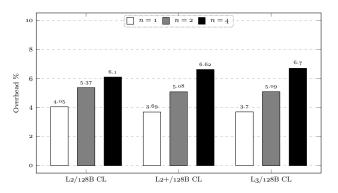

Stage 7 We want to show what can be optimised storage-wise when when cannot repurpose ECC bits, yet we cannot store the MACs in on-chip memory. MACs are thus stored off-chip, but Cached Incremental Hashing for multi-CL MACs can be used to reduce their memory storage requirements [ASC<sup>+</sup>19]. This makes sense only when we have already chosen to use 128B CLs, as these already lead to a halving of MD storage requirements.

We test levels L2, L2+, L3, and L3/oCC, all with 1,2, or 4 CLs covered by a single MAC.

These runs are performed only with QARMA-128 as the encryption cipher, since the performance differences are caused only by the increased memory traffic, and therefore we can expect that AES performance will follow the already seen differences for the previous cases.

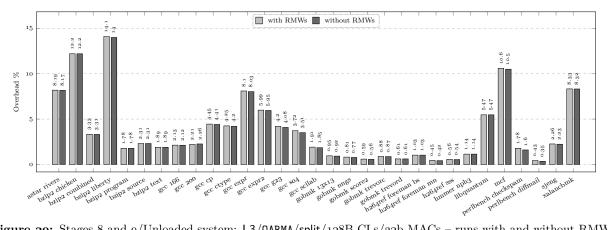

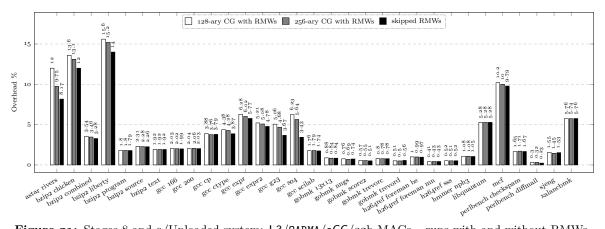

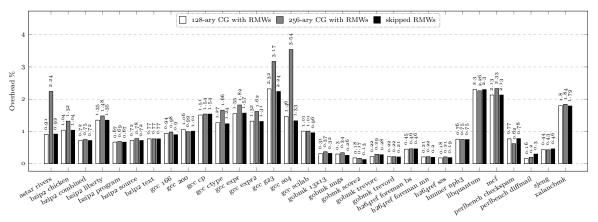

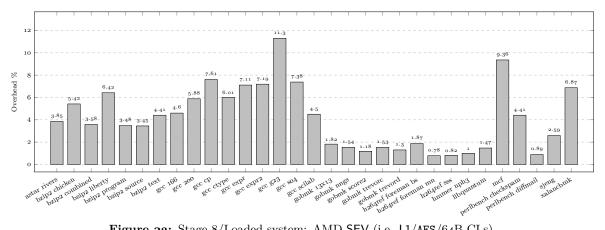

- Stage 8 We select some combinations from the above and show all individual benchmarks in the suite:

- AMD SEV (i.e. L1/AES/64B CLs), and L1/QARMA/64B CLs;

- Intel TDX/64B CLs (i.e. L2/AES/MirE);

- L2/QARMA/64B CLs/64b MACs and L2/QARMA/64B CLs/MirE;

- Intel SGX (i.e. L3/AES/56b MACs);

- L3/QARMA/split/128B CLs/32b MACs;

- L3/QARMA/oCC 128-ary/32b MACs, and also with 256-ary oCCs; and

- L3/QARMA/oCC 128-ary/MirE, and also with 256-ary oCCs.

- Stage 9 In this stage we compare the performance of an MPE with a hypothetical one where the RMW operations have zero costs, i.e. they are instantaneous. This is achieved by simply skipping them. Such an experiment is possible because the simulated MPE does not actually perform the cryptographic operations on any data passing through, simulating instead the timing

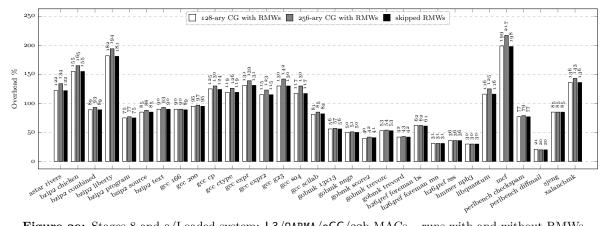

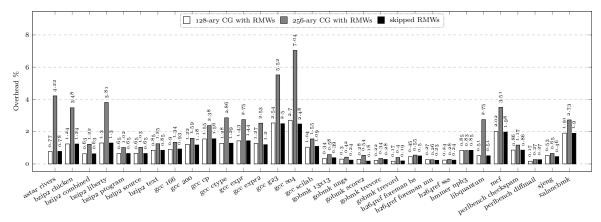

delays involved in the processing steps. By doing this we obtain an upper bound on the actual time spent performing RMW operations. The selected combinations are the last five of **Stage** 8, which are L3 schemes with split counters, i.e. the only ones in **Stage** 8 with RMWs.

## 4.8 ECC-memory vs. non-ECC memory

We are not explicitly considering the impact of using ECC vs non-ECC memory. ECC memory needs to store and retrieve 9/8 of the data with respect to non-ECC memory (newer DDR5 memories even 5/4) but since this is performed in a very quick burst within a single command, the performance loss is much smaller than the overhead. In fact, the usual figures are of penalties smaller than 2% and benchmarks show a loss usually smaller than 0.5% [Bac14]. We thus observe that:

- 1. If deployed on servers, the schemes that do not repurpose the ECC bits are assumed to be still using ECC bits for error detection and correction; and

- 2. For all the methods that do not repurpose the ECC bits, the relative performance losses should be nearly identical regardless of whether they run on non-ECC or on ECC memory.

Therefore, we do not consider the impact of ECC memory as a separate parameter.

## 4.9 Unloaded vs. loaded systems

The various Stages described in Section 4.7 on page 16 are first run on an *unloaded* system, i.e. in a simulated environment where the only task running is benchmarking. The results of these runs are reported and discussed in Section 5.1 on the next page.

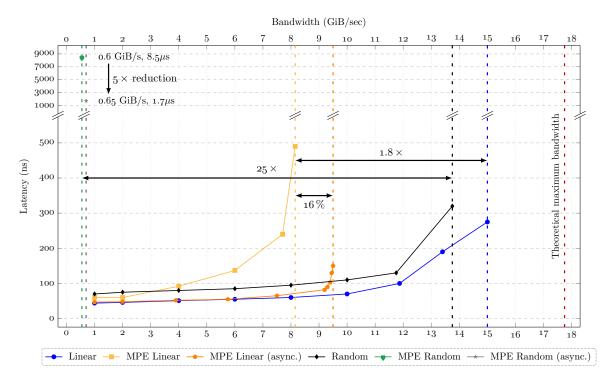

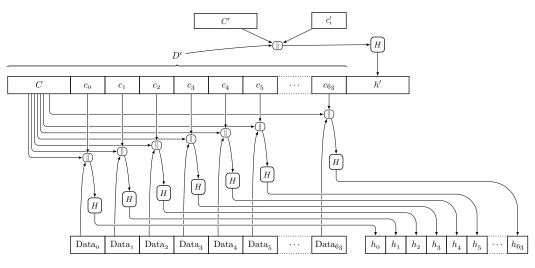

We want an upper bound for the performance degradation in a fully *loaded* system, with up to hundreds of processes running on dozens of processing elements, all sharing the bandwidth of the memory subsystem, such as in a cloud server. It is unfeasible to run that many processes in the simulated environment, for the same reasons mentioned in Section 4.6 on page 16. We instead inject synthetic traffic upstream of the MPE, but after the L2 cache. The amount of traffic injected is 8GiB/s. This corresponds to the point where the latency of the memory subsystem starts to diverge for a SGX-like L3 MPE covering the entire memory, with mostly linear synthetic traffic, and synchronous MAC verification. We assume that MAC verification is synchronous because, following the discussion of the benchmark runs, this will be the most likely implementation. The bandwidth of 8GiB/s is derived from the measurements reported in Fig. 2 on the next page.

The simulated traffic in the loaded benchmark run is a mix of linear and random accesses. We do not add a L<sub>3</sub> cache to the system, in order to simulate the extreme situation where the latter has been completely swamped by the additional traffic. The results of the runs are reported and discussed in Section 5.2 on page 23.

# 5 Results and discussion

We now analyse the results of the selected test runs.

Figure 2: Bandwidth/latency plot with and without MPE, for linear or random synthetic traffic, and with synchronous and asynchronous integrity verification

# 5.1 Unloaded system

Changing CL length from 64B to 128B in our simulated system slows down the system by 1% on the chosen benchmarking suite. Each run is compared to the baseline with the same CL length.

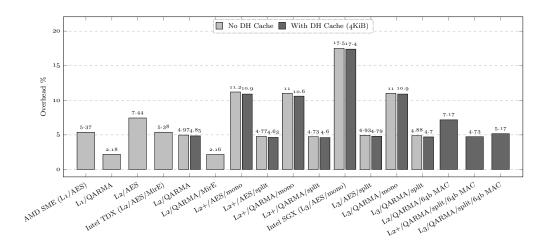

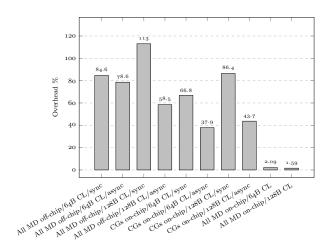

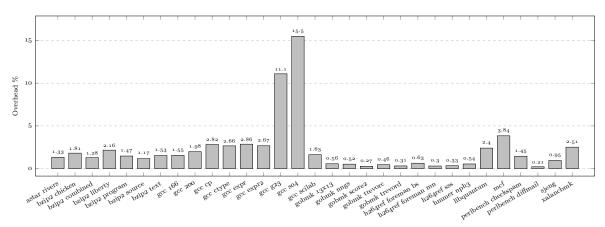

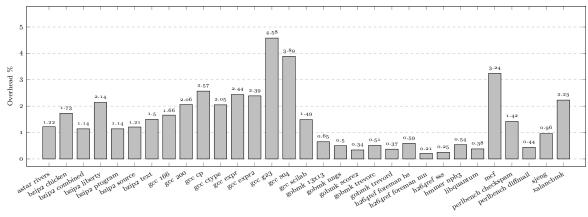

- For Stage 1 on an unloaded system (see Fig. 3 on the next page) we observe that:

- If implemented in a plain way, the performance penalty of lower levels of protection is smaller than the performance penalty of the higher ones.

- For L1 and L2 the latency of AES in XEX mode causes a significant higher slowdown than the use of QARMA-128. Even for L3 the use of QARMA-128 significantly improves the performance with respect to AES, because the generation of the OTP, while it can be performed in parallel with a memory fetch, is still increasing memory latency to the point that it has a noticeable effect.

- We confirm that for L3/split counter trees are superior to monolithic trees in both memory overhead (see Table 1 on page 12) and performance.

- A small DH\$ does not significantly affect performance on the selected benchmarks.

- As expected, using 64b MACs results in worse performance than using 32b MACs, but the difference is contained.

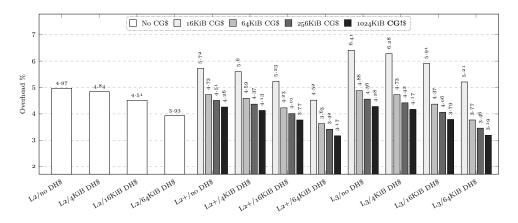

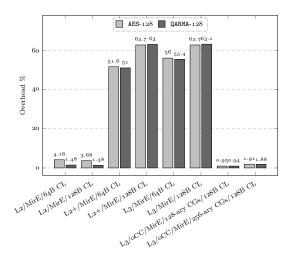

- Stage 2 results (see Fig. 4 on the next page) confirm expected significant performance gains with larger MPE caches, the CG\$ cache having a higher effect than the DH\$.

Figure 3: Stage 1/Unloaded system: Comparison of base levels and state of the art; MACs are 32 bits long except for TDX (28 bits), SGX (56 bits) and 64 bits where indicated; The CG\$ is 64KiB as in SGX

Figure 4: Stage 2/Unloaded system: Impact of MPE cache sizes; ME cipher is QARMA-128; CLs are 64B

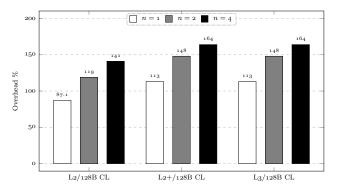

Figure 5: Stages 3 and 4/Unloaded system: Impact of System CL size and asynchronous MAC verification; ME cipher is QARMA-128

Figure 6: Stage 5/Unloaded system: L3; Impact of storing MD on-chip

Figure 7: Stage 6/Unloaded system: Impact of repurposing ECC bits for MACs

Figure 8: Stage 7/Unloaded system: Impact of using multiple-CL MACs (128B CL)

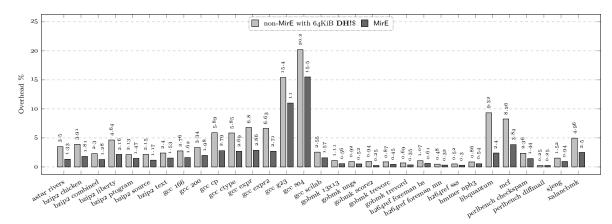

- Stage 3 (the results are combined with those of Stage 4 in Fig. 5 on the preceding page) proves that the impact of these technologies is comparable across systems with 64B CLs and systems with 128B CLs. Note that using 128B CLs slows down the system by 1% on average, and the data for 128B CL systems is relative to the baseline with a 128B CL and no MPE, so the performance of a memory protected 128B CL system is slightly slower than that of a memory protected 64B CL system. However, switching to 128B CLs halves MD memory requirements (cf. Table 1 on page 12).

- **Stage 4** results (see Fig. 5 on the preceding page) suggest that keeping MAC verification synchronous does not impact performance in a significant way.

- Stage 5 results (see Fig. 6) show, as expected, that relieving the contention on the memory bus between data and MD reduces the performance overhead. The latency difference between ciphers has little relevance in L3 systems, but QARMA still offers a a minor performance

advantage.

- Stage 6 results (see Fig. 7 on the facing page) prove that combining oCC and MirE provides the highest level of memory protection with extremely low performance penalties.

- The results of **Stage** 7 (see Fig. 8 on the preceding page) show that multiple-CL MACs effectively reduce memory overheads, but at a significant performance price. Noter that L2+ and L3 performance is virtually identical. This is due to the fact that MAC traffic becomes dominant whereas the need to cover freshness for adjacent CLs profits from counter locality.

Note, however, we do not implement evicted cache line compression as in [TSB18], which would have allowed to store a MAC in the CL in external memory if the data section can be sufficiently compressed, thus reducing the amount of memory accesses. To get an idea of the improvements in that case we refer to the paper. Following it, we can estimate that adding compression may approximately halve the performance penalties.

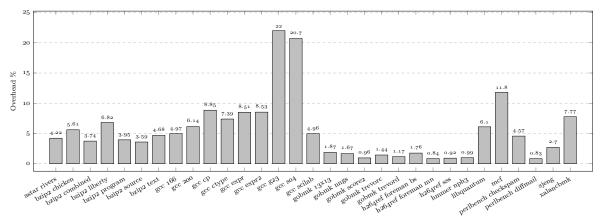

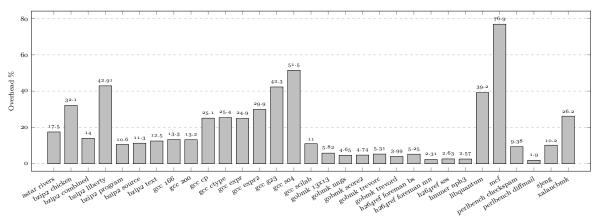

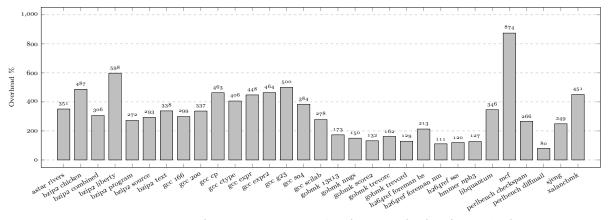

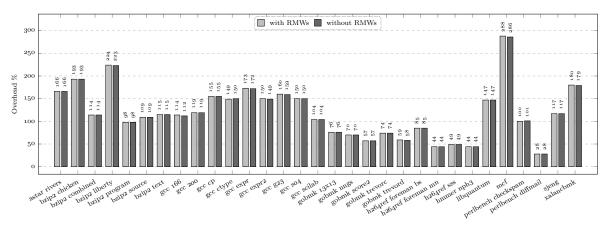

- Stage 8: The performance of the individual SPEC2006 benchmarks (Figs. 15 to 22 on pages 37-39) shows a few expected results, namely that some programs such as gcc g23, gcc so4, mcf, libquantum, and xalancbmk suffer significantly more than average under every MPE configuration. Other programs are affected in a significant way only when there is traffic expansion, such as the remaining gcc programs, bzip2 chicken, and bzip2 liberty. Increasing integrity tree arity by split counters is instrumental in reducing the penalties, but it is only with the compressed oCC and the MirE that all penalties are consistently brought down to less than 5%. For client and edge applications, L3/QARMA/split/128B CLs/32b MACs provides excellent performance, esp. if the tasks profit from good spatial locality properties.

- Stage 9 (see Figs. 20 to 22 on pages 38–39) shows that the impact of RMWs is small and often negligible. This signifies that techniques for reducing RMWs, such as snooping the CLs to be re-encrypted in the LLC in order to skip RMWs for data still in the LLC and marked as dirty, will not give a significant performance boost. Hence, they could be omitted in order to keep state machines simple, at least if we only consider unloaded systems.

## 5.2 Loaded system

Our benchmarking suite runs on a loaded system with 64B CLs 16.5% slower than on an unloaded system. If CLs are 128B long, the benchmarks run 12.2% slower on the loaded system w.r.t the unloaded one. Changing CL length from 64B to 128B in our simulated loaded system on the chosen benchmarking suite makes the system faster by 2.7%.

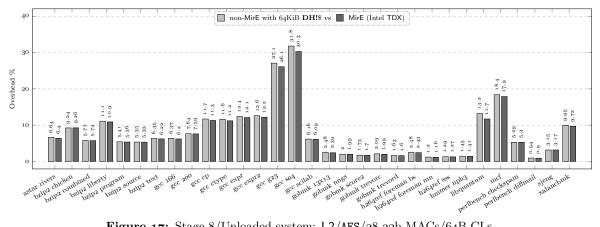

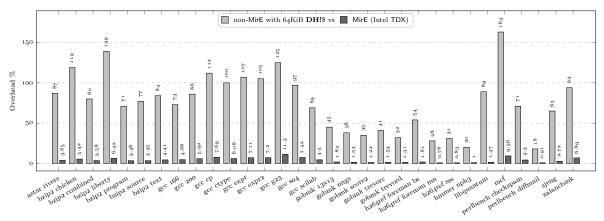

• For **Stage 1** on a *loaded system* (see Fig. 9 on the following page) we observe that L1 always performs better than all other levels, as expected since the expanded traffic will face extreme contention on the memory bus. Two observations are however roughly the same as for the unloaded case: A performance penalty reduction by a factor of roughly 3 occurs between the use of monolithic and split counters; and a small DH\$ offers only a minimal improvement.

Figure 9: Stage 1/Loaded system: Comparison of base levels and state of the art; MACs are 32 bits long except for TDX (28 bits), SGX (56 bits) and 64 bits where indicated; The CG\$ is 64KiB as in SGX

Figure 10: Stage 2/Loaded system: Impact of MPE cache sizes; ME cipher is QARMA-128; CL are 64B

Figure 11: Stages 3 and 4/Loaded system: Impact of System CL size and asynchronous MAC verification; ME cipher is QARMA-128

Figure 12: Stage 5/Loaded system: L3; Impact of storing MD on-chip; AES and QARMA results are identical

Figure 13: Stage 6/Loaded system: Impact of repurposing ECC bits for MACs

Figure 14: Stage 7/Loaded system: Impact of using multiple-CL MACs (128B CL)  $\,$

- Stage 2 results (see Fig. 10 on the preceding page) show a significant difference in behaviour between the unloaded and loaded cases. Whereas in the unloaded case larger MPE caches brought significant improvements, this is not the case for loaded systems, the performance bottleneck at the memory subsystem being dominant.

- Stage 3 results (combined with those of Stage 4 in Fig. 11 on the facing page) indicate that in most cases the performance penalty induced by the MPE is higher with 128B CLs.

- Stage 4 results (see Fig. 11 on the preceding page) show that in the loaded case asynchronous verification brings a significant speedup. This is due to the fact that memory access latencies increase significantly as the memory bus approaches saturation. Hence, decoupling decryption and MAC verification logics allows a noticeably better use of the MPE resources.

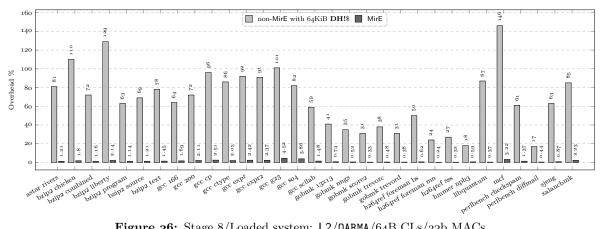

- Stage 5 results (see Fig. 12) are quite interesting because they go against the initial intuition that using longer CLs should perform better because of reduced MD traffic. In fact, the

increased data traffic with 128B CLs is a noticeable penalty. However, as expected, bringing all MD on chip brings performance quite close to that of a system without memory protection.

- Stage 6 results (see Fig. 13 on the previous page) finally bring us that the only way to achieve nearly negligible performance penalties on a loaded system is to use on-chip memory for the CGs and repurpose ECC bits for MAC storage. In fact, by doing this even better performance than with L1 direct encryption can be achieved.

- The results of **Stage 7** (see Fig. 14 on the preceding page) show that using multiple-CL MACs offers increasingly worse performance, as expected, also in the loaded case.

- Stage 8 (see Figs. 23 to 30 on pages 39–42): The results are similar to the unloaded case, however the penalties are larges and in some cases dramatically so, because of the significant amount of usually non-linear traffic expansion. It is only with oCC and MirE that the performance becomes reasonable, with penalties larger than 5% being the exception. Indeed, our best architecture even outperforms a simple L1/AES, as the effect of the latency of a direct encryption method is amplified when the memory subsystem is saturated.

- Stage 9 results are displayed in Figs. 28 to 30 on pages 41–42. Note that Figs. 29 and 30 on page 41 and on page 42 have bars for 128-ary and 256-ary CGs, but a single bar for overheads while skipping RMWs because in this case timings are independent of the CG arity. We observe that: The impact of RMWs on a loaded system is still small; if the counters are off-chip or the MACs require their own addressable storage, the impact of the RMWs is minor, and is negligible if sufficiently long (7b) minor counters are used; with oCC and MirE the reduced performance of the 256-ary CGs with respect to the 128-ary CGs (which uses twice as much on-chip memory) due to the larger amount of RMWs becomes noticeable, but even in this case the worst penalties with 256-ary CGs are still lower than with a direct encryption L2/AES/64B CLs/MirE scheme such as the one used in TDX.

# 6 Conclusions

In this work we have performed one of the most thorough and extensive evaluations of techniques for the cryptographic protection of in-use memory contents in the literature. We have considered the state of the art as well as some new technologies, and hitherto not considered combinations thereof.

We have also unified the evaluation of different protection levels, which are to be selected according to a given adversarial model. This results in a vast set of mutually independent choices, for each of which different types of hardening may be deployed, with correspondingly different prices in term of performance penalty, memory overhead, and hardware cost. The lack of an absolute metric to combine these three costs in a single rating makes it challenging to provide recommendations that may be suitable for different applications.

Therefore, the extensive set of benchmarking runs we document should be used as a guidance for further investigations. This said, we can provide rough indications for some use cases.

For simplicity, let us restrict ourselves to confidentiality and full integrity protection, i.e. L3.

Let us start with the use case of cloud computing. The SoCs for cloud servers are expensive, may contain several dozens of cores, have multiple memory channels and can easily address hundreds of GiBs of physical memory. Because of the very high HW costs, we believe there is no reason for not using freshness-based OTP encryption based on AES or QARMA, with on-chip memory for split counters in the amount of 1/128 or 1/256 of the off-chip memory, and repurposing the ECC bits to store MACs for both integrity and bit flip detection and correction. The additional cost for implementing these technologies would be relatively minor, and likely still less expensive than basing the protection of local memory on the CXL.memory IDE. This would enable the highest level of memory protection at a performance cost which is actually lower than some currently deployed schemes that provide encryption and, optionally also integrity – but not anti-replay.

For lower end devices the situation is more nuanced. Whereas L3/oCC/MirE is definitely applicable, many non-server devices lack ECC bits. If the use case considers memory bus saturation as an exceptional event, which is often the case for edge applications or client applications limited to business oriented virtual machines and special secure modules, then high arity split counter trees with counters either on-chip or in a dynamically allocated carveout together with the MACs can be considered. However, as the results in Fig. 29 on page 41 indicate, performance can quickly deteriorate if extra accesses are needed for MACs. So the use of ECC-capable memory, or memories with, say, only 32 or 40 extra tag bits for each 128B cache line should be seriously considered (the case of 40 extra bits would include 8 parity bits).

The main takeaway from our study is that nearly-transparent strong memory protection can be realised with current technologies and manufacturing processes, especially if we consider recent developments in 2.5D chip manufacturing. It is also achievable for use cases where only a few processes need to be protected, such as banking, content delivery, and software licensing modules, whereas the rest of the traffic would bypass the MPE.

Future work includes upstreaming our MPE framework into gem5. This will allow interested parties to perform simulations tailored to their specific use cases. A further promising research direction is the development of strategies to reduce the impact of RMWs in some schemes, such as L3/oCC/MirE with 256-ary CGs, where in corner cases the performance penalty can exceed 5%, even thought the weighted average of all benchmarks remains lower than 2%.

#### Acknowledgements

Parts of Ionut Mihalcea's work for this paper were performed in partial fulfilment of the requirements for a MSc degree [Mih22]. Ionut wishes to thank his academic supervisor Prof. Konstantinos Markantonakis, and his line manager at Arm, Paul Howard, for their unwavering support.

The work by David Schall described herein was done during two internships at Arm Research and Arm's Architecture and Technology Group, respectively. Part of the work performed during the first internship was documented in his Master's Thesis [Sch19].

The authors are grateful to Héctor Montaner for his help in programming and testing, and to Matthias Boettcher, Mike Campbell, Yuval Elad, Wendy Elsasser, Charles Garçia-Tobin, Alexander Klimov, Jason Parker, Prakash Ramrakhyani, Gururaj Saileshwar, Andrew Swaine, Peter Williams and Nicholas Wood for interesting and oftentimes eye opening discussions on memory protection.

28 Roberto Avanzi, Ionut Mihalcea, David Schall, and Andreas Sandberg

# References

- [AB12] Jean-Philippe Aumasson and Daniel J. Bernstein. SipHash: A Fast Short-Input PRF. In Steven D. Galbraith and Mridul Nandi, editors, Progress in Cryptology INDOCRYPT 2012, 13th International Conference on Cryptology in India, Kolkata, India, December 9-12, 2012. Proceedings, volume 7668 of Lecture Notes in Computer Science, pages 489–508. Springer, 2012. doi:10.1007/978-3-642-34931-7\_28. Cited on pages 10 and 44.

- [ABB<sup>+</sup>19] Roberto Avanzi, Subhadeep Banik, Andrey Bogdanov, Orr Dunkelman, Senyang Huang, and Francesco Regazzoni. Qameleon v.1.0 - A Submission to the NIST Lightweight Cryptography Standardization Process, 2019. Available from: https://csrc.nist.gov/CSRC/media/Projects/ Lightweight-Cryptography/documents/round-1/submissions/qameleon.zip. Cited on page 16.

- [AKT14] Can Acar, Arvind Krishnaswamy, and Robert Turner. Code pointer authentication for hardware flow control, October 2014. United States Patent US9514305 B2. Assignee: QUALCOMM Incorporated. Available from: http://pdfpiw.uspto.gov/.piw?Docid=09514305. Cited on page 43.

- [AMD20] AMD. Secure Encrypted Virtualization API Version 0.24, April 2020. Available from: https://www.amd. com/system/files/TechDocs/55766\_SEV-KM\_API\_Specification.pdf. Cited on page 43.

- [AN17] Shaizeen Aga and Satish Narayanasamy. InvisiMem: Smart Memory Defenses for Memory Bus Side Channel. In Proceedings of the 44th Annual International Symposium on Computer Architecture, ISCA 2017, Toronto, ON, Canada, June 24-28, 2017, pages 94-106. ACM, 2017. Available from: http://doi.acm.org/10.1145/3079856, doi:10.1145/3079856.3080232. Cited on page 8.

- [ARM16] ARM Connected blog. ARMv8-A architecture 2016 additions. https://www.community.arm.com/ processors/b/blog/posts/armv8-a-architecture-2016-additions, October 2016. Cited on page 43.

- [ASC<sup>+</sup>19] Roberto Avanzi, Andreas Sandberg, Michael Andrew Campbell, Matthias Boettcher, and Prakash Ramrakhyani. Cached Incremental Hashing for Reducing Memory Integrity Overhead, 2019. To appear. Cited on page 18.

- [Ava17] Roberto Avanzi. The QARMA Block Cipher Family Almost MDS Matrices over Rings with Zero Divisors, Nearly Symmetric Even-Mansour Constructions with Non-Involutory Central Rounds, and Search Heuristics for Low-Latency S-Boxes. *IACR Transactions on Symmetric Cryptology*, 2017(1):4– 44, 2017. Available from: http://ojs.ub.rub.de/index.php/ToSC/article/view/583, doi:10.13154/ tosc.v2017.i1.4-44. Cited on pages 4, 10, 16, and 43.

- [Bac14] Matt Bach. ECC and REG ECC Memory Performance, May 2014. Available from: https://www. pugetsystems.com/labs/articles/ECC-and-REG-ECC-Memory-Performance-560/. Cited on page 19.

- [BBB<sup>+</sup>11] Nathan L. Binkert, Bradford M. Beckmann, Gabriel Black, Steven K. Reinhardt, Ali G. Saidi, Arkaprava Basu, Joel Hestness, Derek Hower, Tushar Krishna, Somayeh Sardashti, Rathijit Sen, Korey Sewell, Muhammad Shoaib Bin Altaf, Nilay Vaish, Mark D. Hill, and David A. Wood. The gem5 simulator. SIGARCH Comput. Archit. News, 39(2):1–7, 2011. doi:10.1145/2024716.2024718. Cited on page 15.

- [BBKN12] Alessandro Barenghi, Luca Breveglieri, Israel Koren, and David Naccache. Fault Injection Attacks on Cryptographic Devices: Theory, Practice, and Countermeasures. Proc. IEEE, 100(11):3056–3076, 2012. doi:10.1109/JPROC.2012.2188769. Cited on page 6.