# SoK: Hardware-Supported Cryptographic Protection of Random Access Memory

Roberto Avanzi<sup>1,2</sup>, Andreas Sandberg<sup>3</sup>, Ionuț Mihalcea<sup>3</sup>, David Schall<sup>4</sup> and Héctor Montaner<sup>5</sup>

<sup>1</sup> Arm Germany GmbH, Grasbrunn, Germany roberto.avanzi@arm.com

<sup>2</sup> Caesarea Rothschild Institute, University of Haifa, Israel roberto.avanzi@gmail.com

<sup>3</sup> Arm Limited, Cambridge, United Kingdom {andreas.sandberg,ionut.mihalcea}@arm.com

<sup>4</sup> School of Informatics, University of Edinburgh, United Kingdom david.schall@ed.ac.uk

<sup>5</sup> Graphcore, Cambridge, United Kingdom hector.montaner@outlook.com

**Abstract.** Confidential Computing is the protection of data in use from access or modification by any unauthorized agent, including privileged software. For example, in Intel SGX (Client and Scalable versions) and TDX, AMD SEV, Arm CCA, and IBM Ultravisor this protection is implemented via access control policies. Some of these architectures also include memory protection schemes relying on *cryptography*, to protect against physical attacks. We review and classify such schemes, from academia and industry, according to protection levels corresponding of adversaries with varying capabilities, budget, and strategy.

The building blocks of all cryptographic memory protection schemes are encryption and integrity primitives and modes of operation, as well as anti-replay structures. We review the possible implementation of these building blocks, and discuss their relative merits. We consider their possible combinations of these alternatives, and evaluate the performance impact of the resulting schemes.

In order to be able to perform a relatively quick evaluation of hundreds of variations, we introduce a framework for performance evaluation in a simulated system based on the SimPoints methodology. To understand the best and worst case overhead, we also consider systems with varying load levels.

Finally, we propose new solutions to further reduce the performance and memory overheads of such technologies. Advanced counter compression techniques make it viable to store counters used for replay protection in a physically protected memory. By additionally repurposing some ECC bits to store integrity tags, we can provide the highest levels of confidentiality, integrity, and replay protection at a hitherto unattained performance penalty, namely 3.32%, even under extreme load and at costs that make them reasonable in data centers. Combinations of technologies that are suitable for client devices are also discussed.

**Keywords:** Security and privacy · Hardware-based security protocols · Memory Encryption · Memory Integrity · Lightweight ciphers · Integrity Trees

# **Contents**

| 1        | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                           |  |  |  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|--|--|--|--|--|

| <b>2</b> | Summary of the Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                           |  |  |  |  |  |  |

| 3        | Definitions and Background Material           3.1 Definitions            3.2 Adversaries            3.3 Protection Levels            3.3.1 L0: Access control            3.3.2 L1: Memory encryption            3.3.3.1 Implementation aspects.            3.3.3 L2: Encryption and integrity verification            3.3.3.1 MirE: Message Authentication Codes (MACs) in repurposed ECC bits.            3.3.3.2 Implementation aspects.            3.3.4.1 Implementation aspects.                                                                                                                                                                                                                                                                                                            | 88<br>88<br>99<br>99<br>100<br>100<br>111<br>111                          |  |  |  |  |  |  |

| 4        | Review of the Building Blocks  4.1 Cryptographic Primitives  4.1.1 Memory encryption primitives  4.1.2 Authentication primitives  4.1.3 Modes of operation  4.2 Memory integrity structures  4.2.1 Memory overhead comparison  4.2.2 Methods Excluded from Performance Evaluations  4.2.2.1 Log Hashes.  4.2.2.2 Morphable Counters.  4.2.2.3 Isolated Tree with Embedded Shared Parity.  4.2.2.4 Approximate Set Membership.                                                                                                                                                                                                                                                                                                                                                                    | 111<br>111<br>122<br>133<br>155<br>155<br>156<br>166                      |  |  |  |  |  |  |

|          | 4.3 Cryptographic parameters and practices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 17<br>17                                                                  |  |  |  |  |  |  |

| 5        | Benchmarking plan, results, and discussion  5.1 Benchmarking environment and methodology  5.2 Selection of the benchmarking sets  5.2.1 Simulation of system load  5.2.2 Baseline performance  5.2.3 Initialization of short counters  5.3 Set 1: State-of-the-Art, AES vs. Lightweight encryption ciphers, and 64-bit vs. 32-bit MACs  5.4 Set 2: Impact of MPE cache sizes  5.5 Set 3: Impact of the cache line length  5.6 Set 4: Asynchronous MAC verification  5.7 Set 5: Use of on-chip memory for L2 and L3  5.8 Set 6: Impact of repurposing ECC Bits, 3-way split counters, and large counter caches  5.9 Set 7: Impact of incremental MACs  5.10 Set 8: Breakdown of selected configurations  5.11 Set 9: Impact of Read-Modify-Write (RMW) operations  5.12 Remarks on area and power | 188<br>199<br>200<br>200<br>211<br>233<br>244<br>244<br>266<br>269<br>299 |  |  |  |  |  |  |

| 6<br>D   | Conclusions and Open Questions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 30                                                                        |  |  |  |  |  |  |

| Re       | eferences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 31                                                                        |  |  |  |  |  |  |

# 1 Introduction

Cloud computing promises to increase efficiency and drive down cost for users. Such services co-locate multiple mutually untrusted tenants in the same data center and sometimes even on the same physical machines. Compared to traditional on-premises solutions, users of cloud computing face two additional threats. First, hostile tenants may try to exploit bugs in the hypervisor or access control mechanisms to impact the confidentiality, integrity, or availability of co-located virtual machines. Second, compromised insiders at the service provider or its contractors may try to gain access to customer data.

Similar threats exist in client devices, such as phones, which have evolved into smart terminals and identity providers. Like in a data center, adversaries may use co-located untrusted code or even have physical access to the device. Use cases such as secure payments, secure identification, and software anti-piracy rely on strong confidentiality and integrity guarantees. These are often provided in separate components, e.g., SIM cards, USB tokens, or *Trusted Platform Modules* (TPMs). Consolidating their functionality onto the main *System-on-a-Chip* (SoC) enables new use cases while reducing total costs — but also enables opportunities for the aforementioned adversaries.

AMD SEV [KPW16], Arm CCA [MPS<sup>+</sup>21], Intel's Client SGX [Gue16a] and Scalable SGX [JMSS20], and Intel TDX [Int21] move towards this goal by providing access control mechanisms. The latter are managed by a HW-supported *Trusted Computing Base* (TCB). Some of these technologies even include protection against adversaries with physical access to the system. For instance, Intel's Client SGX implements a *Memory Encryption Engine* (MEE) [Gue16a] that provides confidentiality, as well as integrity and protection against replay attacks. Such strong security guarantees can be very costly in terms of performance and storage. For this reason, AMD SEV, Intel TDX, and Scalable SGX (the latter two sharing the same memory protection scheme) provide weaker guarantees in exchange for better performance.

In this study we review what cryptographic technologies are available to protect the contents of data-in-use in RAM against an adversary with physical access to the system. We also evaluate the costs associated to the most meaningful combinations of these technologies.

The starting point is a thorough review of the techniques documented in the scientific and technical literature. Even though we cite several architectures for implementing complete *Trusted Execution Environments* (TEEs), the scope of this paper does not address aspects such as *Operating System* (OS) and Hypervisor support, I/O, virtualization, attestation and IPC mechanisms. We focus on solutions for cryptographic memory protection that are entirely implemented within the SoC package limits.

For real-world applications, understanding the cost of a solution is crucial. Area and power constraints limit the viable options, but relaxing them can be justified by strong market requirements. On the other hand, solutions with high performance penalties and memory overheads risk being rejected without further consideration of their merits. For this reason, we compare the costs of several schemes and variations thereof, where we focus mainly on performance penalty and memory overheads. We also propose new methods to further reduce these costs.

Our performance evaluation uses the entire industry-standard SPEC 2017 [BLvK18] benchmark suite running on the gem5 simulator [BBB+11, LAA+20].

This work also fills a gap in the literature, as there are only very few papers surveying the subject. The 2009 paper [ECG<sup>+</sup>09] is a survey of memory integrity schemes, intended as full integrity, i.e., including replay protection. The 2013 paper [HT13] contains a thorough survey of memory encryption techniques until its publication, but its performance data is taken from the surveyed papers, which more often than not cannot be properly compared to each other. Its abstract states "To date, little practical experimentation has been

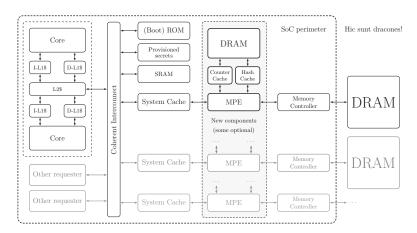

Figure 1: Simplified system level view of a SoC with Memory Protection Engine(s).

conducted, and the improvements in security and associated performance degradation has yet to be quantified." Ten years later, this sentence still holds true. The more recent papers [Shw15, MZLS18, SNR<sup>+</sup>18a, SNR<sup>+</sup>18b, TSB18, TBC<sup>+</sup>20, SNOT21, IMO<sup>+</sup>22] (and many more) only compare their proposals to few other schemes. We conjecture that one reason for the limited comparisons is the long-running time of simulations, a serious issue we address with the use of SimPoints (cf. Section 5.1). The recent survey on HW-supported TEEs [SMS<sup>+</sup>22] focuses on the offered features and does not address performance penalties and memory overheads: We refer the reader to it for information on overall Architecture, supported types of isolated processes, Attestation, dynamic/static nature of the Root of Trust (RoT), support for secure I/O and storage, and size of the TCB.

**Outline of the paper.** We open with a summary of the contributions in Section 2. Section 3 contains background material, such as: the models of the adversaries and a discussion of the memory protection levels. Section 4 contains a review of the cryptographic primitives and memory integrity structures; as well as a discussion of cryptographic parameters such as key and MAC lengths. Section 5 describes the actual benchmarks and discusses how these support the claims in Section 2. In Section 6 we conclude.

# 2 Summary of the Results

Cryptographic memory protection relies on:

- (i) Encryption,

- (ii) Authentication, and

- (iii) Replay protection structures.

In the third group we also include the protection of a relatively small amount of RAM, such as placing it on-chip, or in a tamper-proof or -evident device with a secured communication channel to the SoC. We exclude applying this approach to the entire RAM, because cost and thermal considerations would make it impractical for general use.

There are only a few meaningful combinations of these technologies, forming various *Protection Levels*, the first one comprising only access control, and three increasingly robust level based on cryptography, which may or may be not combined with the first:

L0: Access Control only;

Table 1: Selected documented TEEs and cryptographic memory protection schemes.

| Scheme or Technology     | Year | Level   | Encryption                        | Authentication        | Integrity structure (and other technologies)                                             | References                            |

|--------------------------|------|---------|-----------------------------------|-----------------------|------------------------------------------------------------------------------------------|---------------------------------------|

| Hall and Jutla's PAT     | 2002 | _       | _                                 | _                     | Counter Tree                                                                             | [HJ08]                                |

| AEGIS                    | 2003 | L3      | AES-CBC                           | Incremental hash      | Merkle Tree (MT)                                                                         | $[SCG^{+}03a, GSC^{+}03]$             |

| AEGIS (alt. design)      | 2003 | L3      | "OTP"                             | MD5/SHA-1             | Log Hashes                                                                               | [SCG <sup>+</sup> 03b]                |

| Yan et al.               | 2006 | L3      | AES-GCM                           | GMAC                  | Split Counter Tree (SCT)                                                                 | [YEP <sup>+</sup> 06]                 |

| SecureMe                 | 2007 | L3      | AES-CTR (AISE)                    | SHA-1/HMAC            | Bonsai MT                                                                                | [RCPS07]                              |

| Flicker, resp. SEA       | 2008 | L0      | _                                 | _                     | (TCB-managed Page Tables (PTs))                                                          | $[MPP^{+}08a], resp. [MPP^{+}08b]$    |

| Bastion                  | 2010 | L0 + L3 | AES-ECB                           | AES-CMAC              | MT                                                                                       | [CL10]                                |

| IVEC                     | 2010 | _       | _                                 | GMAC                  | SCT                                                                                      | [HS10]                                |

| SecureBlue++             | 2011 | L3      | Undocumented                      | Undocumented          | "Integrity tree"                                                                         | [WB11]                                |

| H-SVM, resp. SICE        | 2011 | L0      | _                                 | _                     | (TCB-managed PTs)                                                                        | [JACH11], resp. [ANZ11]               |

| Hyperwall                | 2011 | L0      | _                                 | _                     | (TCB-verified PTs)                                                                       | [SL12]                                |

| HyperCoffer              | 2013 | L3      | (Same as SecureMe)                | (Same as SecureMe)    | (Same as SecureMe)                                                                       | [XLC13]                               |

| Intel's Client SGX1/SGX2 | 2013 | L0 + L3 | AES-CTR                           | Encrypted UHF         | Counter Tree only on a small <i>Enclave Page</i> and secure paging from EPC to other RAM | Cache (EPC), $[MAB^+13]$              |

| Iso-X, resp. EqualVisor  | 2014 | L0      | _                                 | Optional              | Optional                                                                                 | [EEO <sup>+</sup> 14], resp. [DZWL14] |

| PodArch                  | 2015 | L0 + L3 | $\mathtt{AES}	ext{-}\mathrm{GCM}$ | GMAC                  | On-demand secure encryption                                                              | [Shw15]                               |

| AMD-SEV {-SNP}           | 2016 | L1      | AES-XEX                           | _                     | (TCB-managed Nested PTs in SNP)                                                          | [KPW16, AMD20]                        |

| VAULT                    | 2018 | L3      | Unspecified                       | Unspecified           | Variable arity tree, encrypted MAC-less leav                                             | res [TSB18]                           |

| Delta-Encoding           | 2018 | L3      | AES-CTR                           | Encrypted UHF         | Delta Encoded SCT                                                                        | [YA18]                                |

| Morphable Counters       | 2018 | L3      | AES-CTR                           | Encrypted UHF         | Morphable Counters SCT                                                                   | [SNR <sup>+</sup> 18a]                |

| SYNERGY                  | 2018 | L3      | AES-GCM                           | GMAC                  | Bonsai MT, MACs in ECC bits                                                              | [SNR <sup>+</sup> 18b]                |

| TIMBER-V                 | 2019 | L0      | _                                 | _                     | (Tagged Memory)                                                                          | [WWB <sup>+</sup> 19]                 |

| Apple's Secure Enclave   | 2020 | L0 + L3 | AES-XEX                           | AES-based CMAC        | Bonsai "Integrity tree"                                                                  | [App20]                               |

| Intel TDX, Scalable SGX  | 2020 | L0 + L2 | AES-XEX                           | Reduced SHA-3         | MACs in ECC bits                                                                         | [JMSS20, Int21]                       |

| Keystone                 | 2020 | L0 + +  | AES-128, unspecified mode         | Unspecified           | Secure on-chip $\leftrightarrow$ external RAM paging                                     | $[LKS^{+}20]$                         |

| Arm CCA                  | 2021 | L0      | _                                 | _                     | (TCB-managed page ownership table)                                                       | $[MPS^{+}21]$                         |

| IBM Ultravisor           | 2021 | L0      | None on Power9                    | None on Power9        | (Tagged memory addresses)                                                                | [HPL <sup>+</sup> 21]                 |

| PENGLAI                  | 2021 | L0 + L3 | Unspecified                       | Unspecified           | Dynamically allocated MT                                                                 | [FLD <sup>+</sup> 21]                 |

| ELM                      | 2022 | L0 + L3 | Flat-ΘCB (OCB)                    | Flat-ΘCB and PXOR-MAC | Counter Tree                                                                             | [IMO <sup>+</sup> 22]                 |

| CSI:RowHammer            | 2023 | _       | Optional                          | PMAC                  | MACs in ECC bits                                                                         | [JLK <sup>+</sup> 23]                 |

|                          |      |         |                                   |                       |                                                                                          |                                       |

- L1: Memory encryption;

- L2: Memory encryption and integrity; and

- L3: Memory encryption, integrity, and protection against replay attacks.

While one can imagine use cases for various degrees of integrity protection only without encryption, we are not aware of any such scheme.

We implement Protection Levels L1 to L3 in the *Memory Protection Engine* (MPE), an IP block sometimes known as *Memory Encryption Engine* (MEE), e.g., in SGX. As depicted in Fig. 1, in a typical SoC the MPE sits between the main interconnect (or a system cache) and a memory controller. It can optionally have its own caches, and even access to a physically secure private DRAM to store metadata.

As a starting point for choosing the components used to implement each Protection Level, we first review the state-of-the-art. Table 1 outlines cryptographic memory protection in various TEEs. While the TEE list is not exhaustive (a more complete list is given in [SMS<sup>+</sup>22]), the list of primitives and structures is comprehensive, except for some deprecated methods and some exclusions as explained in Section 4.2.2. (These technologies are detailed in Sections 4.1 and 4.2.)

We obtain the following groups of alternatives:

- 1. The AES vs. a lightweight cipher suitable for memory encryption. The selected lightweight cipher is QARMA-128 [Ava17], as explained in Section 4.1.1.

- 2. Direct encryption, where a plaintext block is input to the cipher to compute the corresponding ciphertext, vs. CounTeR mode (CTR) encryption, where the encryption of successive counter values results in a keystream which is then XOR-ed to the plaintext to obtain the ciphertext (cf. Section 4.1.3 for more details).

- 3. Various MAC algorithms for memory integrity, such as Carter-Wegman Universal Hash Functions (UHFs) [CW79] (for instance, encrypted linear functions of the message), encrypted checksums of the plaintext, or Parallel MAC (PMAC) [Rog04] (see Section 4.1.2 for a discussion of the options).

- 4. The choice of 32-bit vs. 64-bit MACs for the integrity tags.

- 5. Different sizes of the caches used by the MPE, as well as on-chip memory to store MACs or counters.

- 6. Optionally repurposing some ECC bits to store MACs.

- 7. Different sizes of the memory regions protected by one MAC. This is obtained both varying the CL size and letting a single MACs cover multiple CLs.

- 8. Synchronous vs. asynchronous integrity verification.

- 9. Integrity counter trees with increasing arity. Their nodes, which in this paper always fit in one CL, contain from 8 to 256 highly compressed counters, one for each child. To achieve such high arities, the operations on the tree are designed to guarantee that the most significant bits (e.g., 56 bits) of all counters in a node are equal. This common part is stored once in the node, and the least significant bits of each counter are stored individually (cf. Section 4.2.) We also study counters split into three parts.

We simulate various combinations of the above alternatives in the gem5 simulator, and run the benchmark suite in these simulated systems with different loads on the memory subsystem. To our knowledge, this is the first evaluation of this type. We also randomize the internal state of the system structures to simulate the more realistic performance characteristics of a not-freshly booted system.

#### The main two results are:

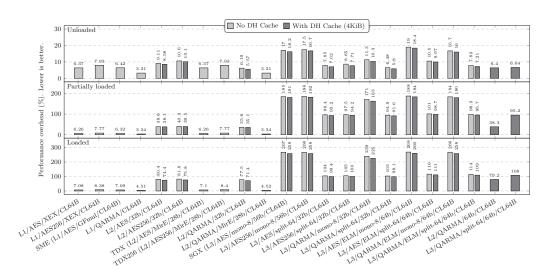

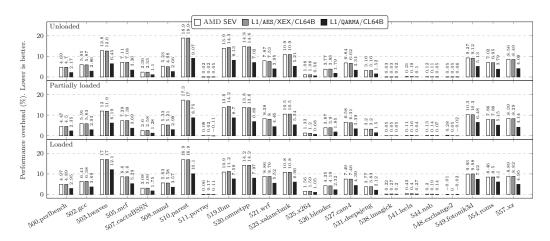

- R1 Nearly-transparent strong memory protection is possible with current technology, for both client and server systems and in most conditions (cf. Section 5.3 for L1 and L2, and Sections 5.8 and 5.11 for L3. See also Section 6).

- R2 Lightweight ciphers clearly outperform the AES in area and power (cf. Section 5.12), but their impact on performance is major only in L1 and L2 schemes (cf. Sections 5.3, 5.7 and 5.8). For L3 schemes that use counter based encryption, the primary influence on system performance is the organization of the data integrity structures, and the choice of cipher is secondary.

#### More detailed results and other observations follow:

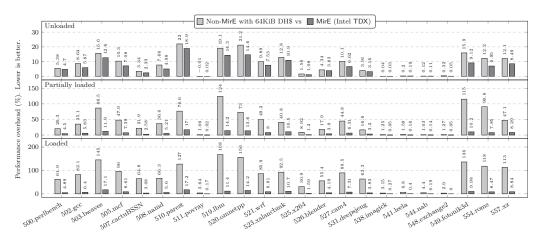

- R3 The performance of schemes based on *direct encryption* methods, such as L1 and L2 schemes, is very sensitive to the latency of the cipher. Moving from the AES to QARMA brings a significant reduction in performance loss. (Cf. Section 5.3.)

- R4 Regarding the previous result, the performance penalty depends much more on the additional decryption latency on memory reads than on the additional latency induced by encryption on memory writes Also, linear interpolation based on the encryption cipher's latency provides a good approximation of the performance penalties, with our measurements and cipher latency smaller than the AES-256's. (Cf. Section 5.10.)

- **R5** Using 32-bit in place of 64-bit MACs halves MAC memory requirements, which is significant. However, MAC memory accesses have poor spatial locality, and the impact on performance is marginal (cf. Section 5.3).

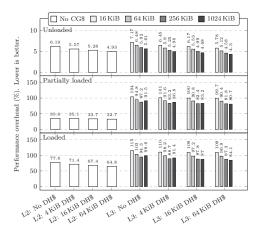

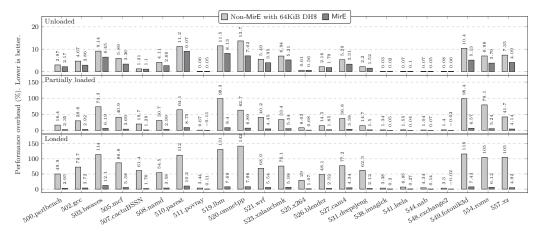

- **R6** Similarly, the MAC caches are not a major performance factor. Counter caches are more effective. The relative improvements due to caching increase with the load of the system. (Cf. Section 5.4.)

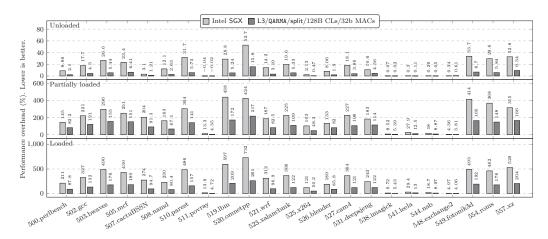

- **R7** Using longer CLs (i.e., 128 B instead of 64 B) does not necessarily improve overall performance significantly. However, it halves the memory used by the MACs and enables more aggressive metadata packing in the counter trees. (Cf. Section 5.5.)

- **R8** While asynchronous integrity verification improves performance, it is a security risk as the system may speculate on potentially corrupted data (cf. Section 5.6).

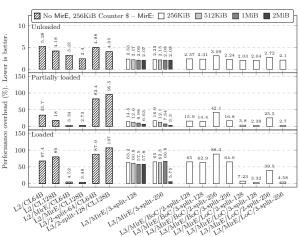

- **R9** If *MACs* [are stored] in repurposed *ECC* bits (short: MirE) or in an internal memory, the L2 and L3 performance has a major improvement (cf. Sections 5.7 and 5.8).

- **R10** We find that incremental MACs covering multiple CLs, while significantly decreasing the memory overhead, adversely impact performance. The degradation is in part due to the fact that we do not implement an optimization that exploits the compressibility of the plaintext to reduce memory accesses. This optimization may compromise plaintext confidentiality, hence it represents a severe security risk (cf. Section 5.9).

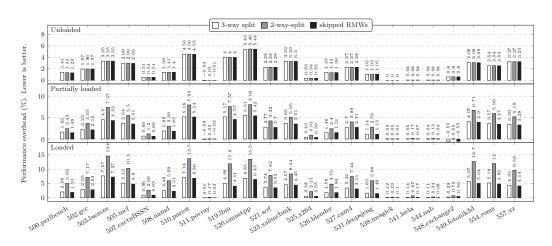

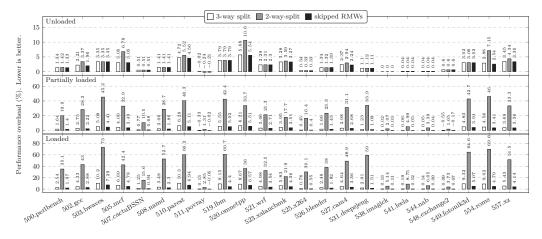

- R11 Increasingly higher arity counter trees offer major and progressive reduction in both memory overhead (cf. Table 2) and performance penalties. However, as the arity of such integrity trees increases, with the counter group size staying constant, the system must re-encrypt memory or regenerate integrity nodes increasingly often. The use of 3-way split counters substantially reduces the cost of these RMWs operations. (Cf. Sections 5.3, 5.8 and 5.11.) The resulting scheme is more effective than techniques such as Morphable Counters, which are very complex to implement (cf. § 4.2.2.2).

- R12 In this paper for the first time we show the advantages of counters split into three parts. The leaf level of our 3-way, high arity split counter trees is just 1:128 or 1:256 of the total RAM. It is small enough to be stored in a physically secure, on-chip or in-package memory. No other tree levels need to be maintained. This enables L3 schemes with very good performance. Combined with MirE, the performance penalty under extreme bus contention is just 3.32%. (Cf. Sections 5.7, 5.8, 5.10 and 5.11.)

# 3 Definitions and Background Material

#### 3.1 Definitions

Following the Arm terminology [MPS $^+$ 21], a *Realm* is a process domain that is isolated from other process domains through policies enforced by a small TCB. This term encompasses both small *Enclaves* as well as processes and larger virtual machines.

The SW-accessible volatile, external memory, connected to a memory controller, is seen as an array of blocks. These blocks match the *Last Level Cache* (LLC)'s *Cache Line* (CL) size and are thus also called CLs.

An encryption or authentication function is said to provide *spatial uniqueness* if, when computed on equal inputs, but written to different locations, it results in different outputs. This is achieved by including the *Physical Address* (PA) of the encrypted or authenticated CL in the computation.

An encryption or authentication function provides temporal uniqueness (freshness) when repeated writes of the same plaintext to the same location result in different outputs. This is achieved by including a counter in its computation.

In what follows a mode (of operation) is a general purpose encryption mode of operation. A *Memory Encryption* (ME) mode is understood to be an encryption mode of operation with plaintext and ciphertext having the size as a CL, and no associated data.

An *on-chip* component is defined as a physically secure block in the same package as the processing elements. In this case the package shall be *tamper-averting*, i.e., a package that is either tamper-proof/resistant, or tamper-evident/detecting.

#### 3.2 Adversaries

To adequately answer the question posed in the Introduction, we categorize technologies based on the considered adversaries. The latter are distinguished according to their access to the target, and their resourcefulness. Before doing this, however, we must make a few critical remarks. Cryptographic memory protection cannot completely address most side channels, including those that exploit physical effects, hence these are out of scope. The exclusion applies to the access-pattern side channel as well: Adversaries can reverse engineer software properties or elicit secrets from access patterns. The only generic and provably effective mitigation would be *Oblivious RAMs* (ORAM) [Gol87], which carry prohibitive performance penalties. The same applies to SW exploitation, timing attacks and micro-architectural side-channels. For all these threats, mitigations should be applied to SW as needed. User-space services can always deny resources to Realms, including scheduled time, hence Denial-of-Service attacks cannot be completely mitigated. In particular, availability of memory cannot be guaranteed by cryptographic means once an adversary has access to the HW.

We can now define the following Adversaries:

- $\mathcal{A}^{\mathrm{SW}}$  can run SW on the target, and provide inputs to it, including through external interfaces.

- $\mathcal{A}_{\mathrm{passive}}^{\mathrm{HW}}$  has physical access to the system that contains the target, including its internals, but does not have the capabilities to access on-chip communication interfaces. They can interpose chips and modules for the sole purpose of monitoring transactions.

- $\mathcal{A}_{\text{active}}^{\text{HW}}$ , also performs *active* attacks, e.g., blocking, corrupting, replaying or injecting transactions on the memory bus [KLR<sup>+</sup>20] or other interfaces.

- $\mathcal{A}_{\text{invasive}}^{\text{HW}}$  can mount highly invasive attacks at the chip or package level. Examples range from micro-probing attacks [Sko17] to actual chip reverse engineering and

editing using a Focused Ion Beam Microscope [TJ09].  $\mathcal{A}_{\text{invasive}}^{\text{HW}}$  is out of scope in this paper as the proper defenses require HW countermeasures.

SW and HW-capable adversaries are independent. The HW adversaries form a hierarchy  $\mathcal{A}_{\text{passive}}^{\text{HW}} \subseteq \mathcal{A}_{\text{active}}^{\text{HW}} \subseteq \mathcal{A}_{\text{invasive}}^{\text{HW}}$ .

# 3.3 Protection Levels

We provide detailed definitions of the Protection Levels. Table 1 shows how some documented solutions map to them. The technologies used to implement each level are listed. They are taken from options described in Section 2, Table 1. For more details about these technologies, cf. Section 4.1.

#### 3.3.1 L0: Access control

Access control policies to implement reverse sanbdboxing are the first line of defense against  $\mathcal{A}^{\mathrm{SW}}$ . However, RowHammer attacks (and micro-architectural side channels) have significantly increased the power of  $\mathcal{A}^{\mathrm{SW}}$ , enabling them to bypass reverse sandboxing.

Physically separating memory rows of different process domains through access control and precise memory allocation policies could theoretically prevent RowHammer attacks. However, this approach requires complex system software changes and is impractical in real-world scenarios.

We do not discuss the implementation of L0.

From here on, we assume that appropriate access control policies are in place to stop unauthorized agents within the SoC, but not to prevent RowHammer attacks.

#### 3.3.2 L1: Memory encryption

This level provides spatial uniqueness, but not temporal uniqueness.

Interest in L1 is driven by confidentiality requirements and to make attacks that depend on memory corruption (for instance RowHammer) more difficult. For this reason, L1 must use direct encryption with a cipher that enjoys a strong diffusion property, i.e., any input change induces a flip of each output bit with likelihood 1/2.

In general, protection against  $\mathcal{A}^{\mathrm{SW}}$  is very limited, as is against  $\mathcal{A}^{\mathrm{HW}}_{\mathrm{passive}}$  since the latter can detect ciphertext repeats. Also, note that attacks on the integrity of a system may still cause SW to reveal its contents, therefore this scheme alone does guarantee confidentiality. Only full replay protection (L3) thwarts the particular attack just mentioned. Warm-boot and cold-boot attacks [HSH<sup>+</sup>09] are properly mitigated. Note that the same arguments apply also to L2.

A common requirement for L1 (and L2) system is the *cryptographic separation* of Realms, which serves to thwart combined SW/HW attacks based on the replay of memory from a target Realm into an adversary-controlled one. This can be achieved by per-Realm unique encryption *differentiators*. (Replay attacks into the *same* Realm, to reset it to a previously known state, require L3 protection.) The differentiators can be encryption keys or, if a single global encryption key is used, bit-strings to be used in a designated bit-field of the tweaks. Differentiators must be discarded upon Realm termination. They should not repeat. If they are tweak contributions, they can be implemented by, say, a TCB-managed 64-bit counter.

Address scrambling (a very lightweight encryption mechanism of the PA to permute the memory layout) may also be somewhat effective against RowHammer. It is deployed in some devices like smart cards for the purpose of mitigating side channel attacks. Note that since these schemes are usually static per boot session, address reuse can be detected:

this is often all an adversary needs to mount an attack. Hence, it should be considered only as an additional *defense-in-depth* measure and not as a complete mitigation per se.

**3.3.2.1 Implementation aspects.** With the AES, a CL is encrypted in *XOR*, *Encrypt*, and *XOR* (XEX) mode [Rog04], as in AMD SEV, TDX, and Apple's Secure Enclave.

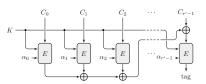

The chosen low-latency block cipher for memory encryption is QARMA-128 (as explained in Section 4.1.1). QARMA-128 is used in a Tweaked *Electronic Codebook* (ECB) mode as in Fig. 2a. In both cases the tweak is the address.

#### 3.3.3 L2: Encryption and integrity verification

This level extends L1 with integrity tags, to detect memory corruption. It does not provide any temporal uniqueness, hence it must rely on a direct encryption method. An integrity tag is usually a MAC. Adversaries can still mount replay attacks.

L2 targets  $\mathcal{A}_{\text{passive}}^{\text{HW}}$ . It is also partly effective against  $\mathcal{A}_{\text{active}}^{\text{HW}}$ , if they only corrupt individual memory locations or have a limited time budget. To defeat targeted replay of memory including its integrity tags, stronger countermeasures are required (see Level L3).

This distinction within  $\mathcal{A}_{\text{active}}^{\text{HW}}$ , though seemingly arbitrary, is necessary due to varying complexities and costs not only of the attacks but also of the *countermeasures*. System designers can assess threats and make business decisions about accepting specific risks. Similarly, active Adversaries might opt for keeping their attacks passive at least initially, to avoid detection and to collect data for cryptanalysis.

**3.3.3.1 MirE: MACs in repurposed ECC bits.** If ECC memory is available, storing the MACs in (possibly some of) the ECC bits eliminates the need to reserve a RAM carve-out for the MACs, and significantly reduces memory traffic. Note that MACs are still accessible to  $\mathcal{A}^{\mathrm{HW}}$ .

The Intel TDX MKTMEi is such a solution. We found no documentation on error correction in a TDX system, but the 28-bit MAC field size suggests that a *Single-Error Correction and Double-Error Detection* (SECDED) (255, 247) Hamming code is used. This code is truncated to (143, 135) to cover 128 bits and 7 bits of the MAC each. The remaining 4 bits of the effective 576 bits in each CL are used for parity.

A different configuration is presented in [YA18], where a 56-bit MAC is used for integrity and error correction and a 7-bit ECC provides SECDED to the MAC.

Remark 1. MirE raises the question of the performance impact of using ECC memory. Reported penalties are smaller than 0.5% [Bac14], stemming from increased traffic and additional processing in the DRAM controller: the impact is so small that we do not evaluate it as a separate configuration.

Remark 2. Beside SECDED codes for 9-chip RAMs, there are several memory-specific Reliability, Availability, and Serviceability (RAS) designs, with varying levels of redundancy, starting with Chipkill [IBM99]. These are capable of handling also multiple errors. MirE can be easily implemented in these systems using suitable codes.

**3.3.3.2** Implementation aspects. The same encryption techniques are used as for L1. For Intel TDX the MAC is computed using truncated SHA-3, with the latency assumed to be comparable to AES-128. In any other MirE scheme, following [JLK<sup>+</sup>23], the tag is computed using QARMA<sub>5</sub>-64- $\sigma_0$ . Note that not all the ECC bits need to be repurposed for a MAC: these bits may contain both a shorter ECC and a MAC. If the MACs are not stored in repurposed ECC bits, hashing is done by a multilinear UHF [CW79] at 32 or 64 bits. Note that these MACs are actually kept as unencrypted hashes while on-chip, which speeds up verification, and we encrypt them block-wise when they are evicted from

the hash cache groups. For instance, four 32-bit hashes are encrypted as a single 128-bit block. This enhances system robustness and security against corruption and replay attacks. In schemes with freshness (i.e., L3), the freshness data of the hashes that are encrypted together must be joined to form the common tweak for the hash block encryption.

#### 3.3.4 L3: Encryption, integrity, and replay protection

This level is capable of detecting not only memory corruption, but also replay of memory contents including associated metadata.

With respect to L2, this level fully mitigates also against  $\mathcal{A}_{\text{active}}^{\text{HW}}$ . In order to replay a CL together with its counter and MACs the adversary either must successfully perform cryptanalysis or wait for a counter repeat. Note that in some variants, the counters themselves may be hidden to the adversary. More information about these data structures is found in Section 4.2.

Remark 3. In a L3 system, a single system-wide key is sufficient for authentication, since nodes closer to the root need to cover memory across Realms. In any case, this is not a security issue. Encryption differentiators are also not required, but they may be a hard customer requirement. Computing integrity tags on the ciphertext ensures that orphaned memory can still be verified, which is essential for secure erasure.

**3.3.4.1 Implementation aspects.** The same freshness information is included in the encryption and in the tag computation. A CounTeR mode (CTR) encryption mode is used with both AES (following AEGIS, the method by Yan et al., and SGX) and QARMA, except with Encryption for Large Memory (ELM), which uses Flat- $\Theta$ CB. The anti-replay technologies are described in Section 4.2.

# 4 Review of the Building Blocks

# 4.1 Cryptographic Primitives

#### 4.1.1 Memory encryption primitives

RAM is commonly encrypted using a block cipher: the long initial latency of stream ciphers makes them unsuitable for the purpose.

For simplicity, we only consider block ciphers with a block size of 128 bits: smaller block sizes are used only for smart cards and small embedded devices, and longer blocks are uncommon. The selected block ciphers are the AES [DR02] and QARMA [Ava17], where the second is chosen as a representative of lightweight ciphers.

QARMA is a *Tweakable Block Cipher* (TBC): Beside the secret key and a text, a TBC accepts a *third* input known as a *tweak*, which is used together with the key to select the permutation computed by the cipher. Unlike the key, the tweak may be controlled by an adversary. TBCs simplify the design of modes of operation, with an early application to memory encryption [HT13].

The latencies of most suitable lightweight ciphers are similar (e.g., PRINCE [BCG<sup>+</sup>12]) or worse (for instance SKINNY [BJK<sup>+</sup>16]). To estimate performance penalties for these ciphers, readers can interpolate between our AES and QARMA results. A revised version of QARMA, QARMAv2 [ABD<sup>+</sup>23], has been introduced. Its latency is nearly equal to QARMA's, so we do not consider it as a separate configuration option.

Beside the AES, we do not consider other non twekable block ciphers. The reason is that as they would require constructions that lead to increased latency anyway. We also do not consider ciphers with block sizes that make them less suitable for memory encryption: For instance SPEEDY [LMMR21] has a block size of 192 bits, and ASCON [DEMS21] in a

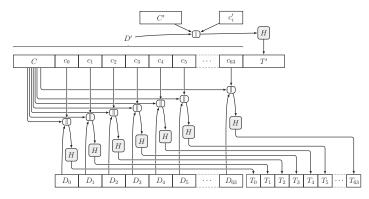

(a) Tweaked *Electronic Codebook* (ECB) mode for encryption, with optional freshness.

(c) Parallel MAC (PMAC) for authentication computed with a TBC when freshness is not implemented.

(b) CounTeR in Tweak (CTRT) mode for encryption.

(d) PMAC for authentication computed with a TBC when freshness information is available.

Figure 2: Encryption and authentication methods designed around a Tweakable Block Cipher (TBC). They show how freshness can lead to shorter critical paths. Notation: E is a TBC, the two inputs on the left side of the block being the key (above) and the tweak;  $P = P_0 \| \cdots \| P_{r-1}$ , resp.  $C = C_0 \| \cdots \| C_{r-1}$  is the partition of a plaintext, resp. ciphertext in blocks of equal size;  $\alpha_i$  is the Physical Address (PA) of the i-th block; and  $\nu$  a nonce. If freshness is available, both encryption and authentication algorithms use it, and they share the same nonce. The TBC used for authentication may have a smaller block size than the encryption TBC, in which case  $r \neq r'$ .

tweaked mode such as *Masked Even-Mansour* (MEM) [GJMN16] has a block size of 320 bits. (For completeness' sake, given a public permutation  $\pi : \mathbb{F}_2^n \to \mathbb{F}_2^n$ , we describe an example of a MEM construction: Given a key K, a tweak T, and a plaintext P, all n bits long, the ciphertext C is computed as  $C = M \oplus \pi(P \oplus M)$ , where  $M = K \oplus \pi(T \oplus K)$ .)

#### 4.1.2 Authentication primitives

Standard hash functions such as SHA-2 [NIS12] or SHA-3 [NIS15] can be turned into MACs, but the resulting schemes are very slow and not parallelizable.

Carter-Wegman Hashes [CW79], i.e., encrypted UHFs, are a better choice. UHFs admit fully parallelizable constructions, such as multilinear functions of the input computed over a binary Galois field, as used in SGX [Gue16b]. If there is a MAC cache, it is actually the not-yet-encrypted UHF values that are cached, which are thus verified more efficiently.

Apple's Secure Enclave [App20] uses a Cipher-based MAC (CMAC) [IK03] to compute integrity tags. CMAC, being a block-wise chained construction, can not be made parallel and has a high latency, but Apple's use case does not need very high throughput. It is however unsuitable for general usage requiring high bandwidth and low latency. Instead, we evaluate TBC-based PMACs [Rog04]. PMACs are more expensive than encrypted UHFs, but they can be used for error detection and correction beside integrity, cf. [HS10,SNR+18b, JLK+23]. The computation of PMACs is depicted in Figs. 2c and 2d. Such constructions can easily be made incremental where, upon a write, only the part of the message that has changed needs to be recomputed. A variant for non-TBCs, called PXOR-MAC is described in [IMO+22].

Encrypted checksums of the plaintext as in Rogaway's Offset Codebook mode (OCB) mode [Rog04] are an inexpensive method to compute integrity tags, but they suffer from two drawbacks. First, they need to be verified after decryption, potentially worsening overall latency. Second, since they require freshness, a CTR encryption should be used which has lower latency than direct encryption. With CTR encryption, using checksums of the plaintext as the basis for integrity would make the ciphertext malleable, whence a UHF-based MACs should be used instead.

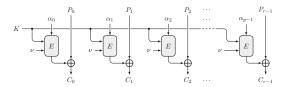

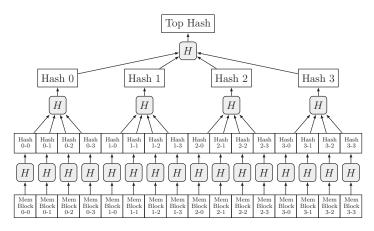

**Figure 3:** Merkle tree. H is a hash function.

#### 4.1.3 Modes of operation

For memory encryption, many (authenticated encryption) modes of operation can be simplified somewhat because the length of the payload is a fixed multiple of the underlying cipher's block length.

Some older schemes, such as Bastion [CL10], use the block cipher in *Electronic Codebook* (ECB) mode, but the lack of spatial uniqueness keeps plaintext patterns in the ciphertext, therefore modes that provide spatial uniqueness are necessary.

For direct encryption, spatial uniqueness is achieved by using the PA as the tweak. With a non twekable block ciphers, the latter is used in the XOR, Encrypt, and XOR (XEX) construction [Rog04], which is just the XTS mode of operation [IEE19] for a message whose length is a multiple of the block size. XEX is defined as  $C_i = E_K(P_i \oplus M_i) \oplus M_i$ . In other words, a tweak-derived mask is added to the input and the output of the cipher. The first mask  $M_0$  is derived by encrypting the tweak, and the successive masks  $M_i$  for  $i \geq 1$  are obtained by multiplying the first mask by a fixed sequence of values. Using a single finite field element  $\gamma$  we can put  $M_i = \gamma^i \cdot M_0$ . Inoue et al. introduce a Flat- $\Theta$ CB mode [IMO+22] which is similar to OCB [Rog04]. They define the L3 scheme ELM using Flat- $\Theta$ CB mode for data and PXOR-MAC to authenticate counter groups.

With a TBC, the PA (concatenated with freshness if provided) of each block is used directly as a tweak, cf. Fig. 2a, and a XEX construction is not needed.

In CTR encryption with a TBC, the counter and PA are used as tweak and text respectively (cf. Fig. 2b) to generate the keystream. When not using a TBC, the counter and PA are concatenated and then encrypted.

# 4.2 Memory integrity structures

A table of hashes or MACs protects against memory corruption, but it is not sufficient against replay attacks, unless the table is itself protected. This can be achieved by storing it in a tamper-averting memory or by covering it with a structure such as a *Merkle Tree* (MT) [Mer80] (cf. Fig. 3). MT nodes can be cached [GSC<sup>+</sup>03] to speed up verification.

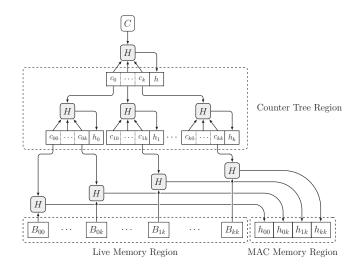

With freshness-based encryption, we can protect the memory by just protecting the counters, for instance with a *Bonsai Merkle Tree*, i.e., a MT protecting the counter table [RCPS07]. A different method in the *counter tree*, of which examples are Hall and Jutla's *Parallelizable Authentication Tree* (PAT) [HJ05] and the integrity tree used in SGX [Gue16a]. A node of the counter tree is called a *Counter Group* (CG). A CG contains a counters, which correspond to the a children of the node. The counters in a leaf, resp. non-leaf CG are one-to-one with a CLs, resp. children CGs, A MAC is computed on every

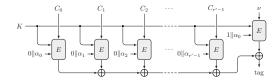

Figure 4: Counter tree for memory integrity.

**Figure 5:** Split counters. The  $i^{\text{th}}$  logical counter is the concatenation of a major counter C (resp. C') and of the  $i^{\text{th}}$  minor counter  $c_i$  (resp.  $c'_i$ ). This is then used in the function to compute the hash of the  $i^{\text{th}}$  data block (resp. counter group).

node and it is either stored dedicated table, along with the MACs of the data CLs or in the node's CL along with the counters. Since the latter approach has better performance, for simplicity we consider only it. The MAC of a CG is computed on the a counters in the node and the parent counter. Before a node is evicted, its parent counter is first incremented and the node's MAC is recomputed.

The split counters optimization [YEP+06] replaces a group of a counters with a group consisting of a single major counter and a' > a smaller, minor counters, associated with that major counter (cf. Fig. 5). A logical counter in this scheme is defined as the concatenation of a minor counter and its associated major counter. Each node (a data CL or a CG) is associated with a logical counter. The increased arity (for instance, from a=8 to a'=64) reduces both counter storage overhead and tree depth. When a minor counter overflows, the common major counter is ticked to ensure that values do not repeat. Since this changes the values of all the logical counters associated with that major counter, all the sibling nodes need to be refreshed. For data CLs this means that they are re-encrypted, and for both types of nodes the MACs need to be recomputed. All minor counters in the group are reset to zero at this point to reduce the rate of minor counter overflows.

Delta encoding [YA18] works by representing a logical counter as the sum of the major counter and of a minor counter, instead of their concatenation. When a minor counter is about to overflow, the minimum of all minor counters m is computed, and if  $m \neq 0$  then it

is subtracted from all minor counters and added to the major counter to delay the RMWs. This operation is also called *rebasing*.

Despite the RMWs, split counter trees bring a major performance improvement over monolithic counters. We introduce here 3-way split counters (with major, middle, and minor counters) to both increase arity and reduce RMWs.

Instead of using full trees, two optimizations can be done.

- LoC One option is storing the data cache line counters in an in-package tamper-averting DRAM (a SRAM would be too large) which is MPE private (i.e., invisible to the rest of the system and outside adversarial control). We call this solution LoC which stands for *Leaves-on-Chip*. In fact, if we store the leaf nodes in a physically protected memory, such as on-chip, then we do not need to compute any other nodes from the original tree. LoC is sometimes mentioned in the literature only to be dismissed as unviable because of the large overhead.

- BoC A less expensive version of the LoC solution consists of keeping the leaf nodes in external memory and store the level immediately above on chip. We call this tree arrangement BoC for *Branches-on-Chip*. Similarly to LoC, the system needs no further levels of the tree to ensure memory integrity. This idea seems new.

#### 4.2.1 Memory overhead comparison

In Table 2, we compare memory overheads of different integrity trees, including the new very high arity trees introduced in this paper. Multi-CL MACs encrypt each CL individually with its own counter, whence the eviction of a CL from the last level cache does not require re-encryption of adjacent CLs. The table also includes the *Tamper-Evident Counter* (TEC) tree [ECL<sup>+</sup>07], which has high memory overhead and requires wide encryption with substantial latency, making it impractical for deployment.

#### 4.2.2 Methods Excluded from Performance Evaluations

- **4.2.2.1 Log Hashes.** Log Hashes [SCG $^+$ 03b] are an interesting option because they do not employ a tree structure and have a negligible memory overhead. Log Hashes maintain an incremental hash of a Realm's entire memory by adding the hashes of all cache lines in it. The hash of a cache line is computed on the concatenation of the contents of the line, its address, and a secret key. The Log Hash is updated with each memory write, by subtracting the contribution of the old contents, and adding that of new contents. Verification of the memory occurs only when the Realm interacts externally, but the Realm's entire protected memory region needs to be verified. Log Hashes are well-suited only for long-running tasks with minimal I/O, where their performance impact can be negligible. They are unsuitable for general applications and remain undeployed in practice.

- **4.2.2.2 Morphable Counters.** In the *Morphable Counters* paper [SNR $^+$ 18a] various optimizations are presented to reduce the amount of RMWs associated to minor counter overflow. The first optimization builds on the observation that, for most tasks, either only a few counters in a group are incremented regularly, or all counters are. A counter group can have two representations, both intended as delta encoding. For a 64 B CL length, all CGs contain a 64-bit embedded MAC, and a 57-bit major counter, a 1-bit format flag F and a 6-bit *Non-Zero Counters* (NZC) field. Then:

- 1. The first representation has F = "Zero Counter Compression" and stores the number of non-zero counters in NZC. A 128-bit bitmap is used to mark which counters are non-zero, and the remaining 256 bits are partitioned in equal fields of size  $\lfloor 256/\text{NZC} \rfloor$  each to store these counters.

| Table 2: Memory Overhead of Various Types of Integrity Trees.                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------|

| <b>Legend:</b> $\ell_H$ , $\ell_c$ , and $\ell'_c$ are the bit lengths of a hash or MAC; of a monolithic or major counter; and a |

| minor counter, respectively. $a$ is a counter group's arity, and $n$ is the number of CLs a MAC covers.                          |

|                                                          | CL Length |       |  |  |

|----------------------------------------------------------|-----------|-------|--|--|

| Type of Tree                                             | 64 B      | 128 B |  |  |

| Merkle Tree with $a = 4$ , resp. 8                       | 33.3%     | 16.7% |  |  |

| Monolithic Counter Tree with embedded MAC, $\ell_c = 56$ |           |       |  |  |

| • $\ell_H = 64$ ; $n = 1$ ; $a = 8$ , resp. 16           | 26.8%     | 12.9% |  |  |

| • $\ell_H = 32$ ; $n = 1$ ; $a = 8$ , resp. 16           | 20.5%     | 9.79% |  |  |

| • $\ell_H = 32$ ; $n = 2$ ; $a = 8$ , resp. 16           | 17.4%     | 8.23% |  |  |

| • $\ell_H = 32$ ; $n = 4$ ; $a = 8$ , resp. 16           | 15.8%     | 7.45% |  |  |

| Split Counter Tree with embedded MAC, $\ell_c = 64$      |           |       |  |  |

| • $\ell_H = 64$ ; $n = 1$ ; $\ell'_c = 6$ , resp. 7      | 14.1%     | 7.04% |  |  |

| • $\ell_H = 32$ ; $n = 1$ ; $\ell'_c = 6$ , resp. 7      | 7.84%     | 3.91% |  |  |

| • $\ell_H = 32$ ; $n = 2$ ; $\ell'_c = 6$ , resp. 7      | 4.71%     | 2.34% |  |  |

| • $\ell_H = 32$ ; $n = 4$ ; $\ell'_c = 6$ , resp. 7      | 3.15%     | 1.57% |  |  |

| • $\ell_H = 32; n = 1; \ell'_c = 3$                      | 7.04%     | 3.52% |  |  |

| • $\ell_H = 32; n = 2; \ell'_c = 3$                      | 3.91%     | 1.95% |  |  |

| • $\ell_H = 32; n = 4; \ell'_c = 3$                      | 2.35%     | 1.17% |  |  |

| PAT with $a = 8$ , resp. $a = 16$                        | 28.6%     | 13.3% |  |  |

| TEC tree with $a = 8$ , resp. $a = 16$                   | 42.9%     | 20.0% |  |  |

| 128-ary 3-way Split Counter Tree, $\ell_H = 32$          | _         | 3.91% |  |  |

| 256-ary 3-way Split Counter Tree, $\ell_H=32$            | _         | 3.52% |  |  |

| 128-ary 3-way Split Counter Tree with MirE, $\ell_H=32$  |           | 0.78% |  |  |

| 256-ary 3-way Split Counter Tree with MirE, $\ell_H=32$  |           | 0.39% |  |  |

2. If the number of non-zero counters is larger than 63, then the flag F is set to "Uniform" and the remaining 384 bits contain 128 3-bit minor counters. Rebasing is used only in this second representation.

While morphable counters are effective in reducing the number of RMW, we do not implement them since 3-way counters effectively eliminate the RMW overhead, and are much easier to implement (cf. Sections 5.8 and 5.11).

4.2.2.3 Isolated Tree with Embedded Shared Parity. We do not evaluate the *Isolated Tree with Embedded Shared Parity* (ITESP) [TBC<sup>+</sup>20] separately. One of its configurations packs 32 counters in a 64B cache line where the size of minor counters is 4 bits, and the freed 128 bits are used to store two 64-bit parity/integrity fields, each covering 16 cache lines. We speculate that its performance for a single Realm should be just slightly worse than a 64-ary 64B split counter groups L3 scheme with MirE, since no MAC table is kept. The main benefits of ITESP emerge when multiple Realms run concurrently, a configuration not supported by our setup, because each Realm would have its own integrity tree and metadata cache.

**4.2.2.4 Approximate Set Membership.** Attempts have been made to use Bloom Filters [Blo70] or Cuckoo Filters [FAKM14] for memory integrity schemes. The intention is to store the MACs of a group or CLs as *keys* in such probabilistic filters instead of storing them separately in memory. In order to achieve a *false positive rate* of at most p, Bloom filters, resp. Cuckoo filters, need at least  $1.44 \log_2(1/p)$  [PPR05], resp.  $\log_2(1/p)$  bits of space per inserted key [FAKM14]. Since we want the false positive rate to approach, if not match, the claimed security level of the MACs inserted as keys in the filters, which is their bit length,

these filters cannot occupy less memory than an equivalent table of MACs.<sup>1</sup> Therefore, all the proposed schemes that claim a memory overhead reduction [NHSQ12,SA21] fail this basic security scrutiny.

# 4.3 Cryptographic parameters and practices

To ensure long-term confidentiality, encryption keys should be at least 128 bits long. Shorter keys are not used in any currently deployed or recently proposed memory protection scheme. Sometimes longer keys are an option, for instance 256-bit keys for Intel's TDX, but we posit that this does not offer increased practical security and only increases latency: indeed, a proper complexity analysis of quantum-computer-assisted key search against AES-128 proves it is secure even against adversaries with access to a large-scale quantum computer [JNRV20]. Deployed technologies such as Intel's SGX and TDX, and AMD's SEV use the AES in modes that need two independent keys, or even AES-256. QARMA-128 and QARMAv2-128 allow the use of 256-bit keys as well.

Encryption block sizes must be at least 128 bits, to reduce the likelihood of any attack that exploits ciphertext collisions.

Authentication keys should be at least 128 bits long as well.

Only the TCB and no SW environment may set any key, and SW will only manage process identities.

We posit that a length of 32 (or even 28) bits is sufficient for both data and counter group MACs, to deter Adversaries that simply want to corrupt memory, for instance with RowHammer attacks. This is, in fact, one of the main reasons to deploy a L2 scheme. The TCB must destroy (i.e., internally invalidate and overwrite) any differentiator, i.e., key or tweak, associated with the address where an integrity violation occurred — and possibly other internal information. The target process will no longer be able to execute, and the information in it will be lost to the adversaries. It is essential that the TCB responds so to integrity violations before giving back control to the operating system or the hypervisor. Otherwise, to make just one example, an  $\mathcal{A}_{\text{active}}^{\text{HW}}$  adversary with the ability to run privileged SW would be able to brute force a short MACs.

If the chosen authentication primitive produces a longer MAC than needed, the output is simply truncated.

In L3 schemes, an Adversary may attempt to replace a CL together with its MAC. To do this without triggering an integrity fault, they wait until the counter associated with the target CL repeats. If the counters are sufficiently long, the attack cannot succeed. For this reason, monolithic counters must be at least 64 bits long (it can be argued that 56 bits suffice). The minimal aggregated length of a major and a minor counter (or major plus middle plus minor) shall also be 64 bits. If an Adversary wants to replay a CL together with its MAC and counter, they will similarly have to either guess the embedded MAC or wait that the parent counter repeats.

For Merkle Trees the minimal hash length is 128 bits, regardless of whether the hash is keyed or not, to ensure that attacks have a time complexity of at least  $2^{64}$ .

# 4.4 On the design space

In Fig. 1 an MPE is associated with a memory channel, benefitting from memory interleaving and thus reducing bandwidth saturation risks. In the figure an MPE is also represented as a separate block between system cache and memory controller, but this is far from the only option: it can be implemented as part of the memory controller or a wrapper around the system cache. A different MPE configuration involves a core-private MPE, positioned

<sup>&</sup>lt;sup>1</sup>Entropy is a harsh mistress. Attempts to cheat on her are severely punished by mathematics.

upstream of the on-chip interconnect. In such a design, the MPE can be a performance bottleneck, but it is suitable for *secure cores*, like SoC-embedded TPMs.

Pure SW solutions are possible: At boot, a part of a cache is *address locked* in order to keep the TCB in it (and effectively reducing its size). All memory reads/writes to external memory are then trapped to this code to augment them with encryption and integrity support. Performance is clearly severely impacted, as in [CZG<sup>+</sup>15, MMS<sup>+</sup>20]. A different, less secure, approach [Pet10, GMD<sup>+</sup>16] keeps most of the RAM encrypted except for a few recently used pages, which are re-encrypted once they have been idle for some time.

Recall that we only consider solutions contained in the SoC package. This excludes any form of "smart memory" [AN17] where the protection logic is split between the Requester and the Completer, such as the CXL.memory Integrity and Data Encryption (IDE) scheme [CXL19]. Such architectures require logic for attestation, secure link setup, and encryption, involving cryptographic engines in every memory module if not every chip, so it would be more expensive, hardware-wise, than an MPE-based solution. CXL is however suitable for disaggregated memory configurations, covering transport between compute and memory nodes.

The breadth of the subject and constant developments (cf. Table 1) imply that the full design space is likely not knowable. The present work represents just a snapshot.

# 5 Benchmarking plan, results, and discussion

# 5.1 Benchmarking environment and methodology

It would be impractical to implement several thousands of combinations of technologies in silicon for the purpose of evaluating them. A solution to this problem lies in prototyping, i.e., the creation of an approximate implementation of the desired features, which can thus be tested and benchmarked. Very accurate models can be created even without implementing all details. For instance, the latencies of cryptographic primitives can be derived from actual implementations and inserted as delays into the simulation.

The prototypes used in this paper are built in the gem5 simulator [BBB<sup>+</sup>11,LAA<sup>+</sup>20]. gem5 allows engineers to build SW versions of HW components typically included in computer systems. It abstracts the interfaces between components, which can be combined flexibly. It provides approximate timing models for many processor cores.

The modeled CPU core approximated an Arm Cortex A72, with a 2 GHz frequency and a 1 GHz system frequency. The cache hierarchy includes L1-I (48 KiB, LRU replacement policy, 3-way set associative, 1 cycle latency) and L1-D (32 KiB, LRU replacement policy, 2-way, 1 cycle latency) caches, and a unified L2 cache (1MiB, tree-PLRU replacement policy, 16-way, 5 cycles latency). The memory is 16 GiB DRAM in a dual-rank DDR4 DIMMs configuration. The MPE-private caches are 4-way set associative with a LRU replacement policy.

The simulated SoC is implemented in a 7 nm process. We take the latencies of some components from [Ava17], for instance 15.67 ns for a pipelined implementation of AES-128, 4.8 ns for QARMA<sub>11</sub>-128- $\sigma_1$  and 2.2 ns for QARMA<sub>5</sub>-64- $\sigma_0$ . Note that implementation, process, libraries all affect the crypto block's latency, but system and CPU clocks do not. We assume we reuse the IP blocks from [Ava17] with their own clocks, thus with the exact same performance characteristics. This is a reasonable assumption since this is how hard macros are used in practice. The above latency of QARMA<sub>5</sub>-64- $\sigma_0$  is also used in [JLK<sup>+</sup>23], and essentially for the same purpose as ours.

Lastly, all MPE algorithms are thoroughly parallelized to their maximum extent for all considered schemes.

Our evaluation uses the SPEC 2017 [BLvK18] benchmark suite. Detailed software models such as gem5 increase execution time by several orders of magnitude: a typical

SPEC benchmark can take around a month to run [San14]. To facilitate rapid prototyping, we use the SimPoint [SPHC02] methodology, which is well understood in academia and industry. It uses clustering to find representative regions that serve as a proxy for the whole application. The results are finally combined using weighted averages, that reflect the regions' importance to the overall application. Up to 10 SimPoints of 30 million instructions from each benchmark are simulated in place of several billions of instructions. Regarding reproducibility, including all details needed to re-generate our SimPoints would be impractical. We also note that the SPEC consortium themselves encourages the use of SimPoints [SPE18].

Remark 4. An alternative approach would have been to run the entire benchmarks, as opposed to SimPoints, in parallel on a large distributed cloud. This unfortunately does not work in practice since the longest running workloads would have taken weeks to months to run to completion, without any expectation that the results would be any different from the SimPoints methodology. The quicker turnaround, less than an hour to run all SPEC 2017 on a big-enough cluster, is in fact instrumental when exploring a vast space of optimizations.

Remark 5. A legitimate question is whether we can verify the reliability of our simulations by porting SPEC2017 to run under Client SGX. This would be a major undertaking, even with the help of general-purpose wrappers, we would have to avoid the penalties related to the EPC. In fact [Gue16a] only runs 445.gobmk from SPEC2006 with selected data sets. This said, on the trevorc.tst and nngs.tst data sets, [Gue16a] reports slowdowns of 4.90% and 3.29%, respectively, and on our simulated SGX-like method we measure 5.31% and 4.65%, in line with expectations from a deeper tree.

Remark 6. Regardless of how the simulation is performed, we may ask ourselves about the impact on systems that include context switches, virtual memory swap, and any type of I/O. These aspects are very difficult to emulate. In fact, benchmarking in such a context seems absent from the literature on cryptographic memory protection. However, (i) We can observe that the additional memory used for metadata is not visible to the operating system and will be unaffected by paging and similar operations; and (ii) It can be argued that context switches, paging, and general I/O are affected by the performance penalties on memory accesses only in a minor way: context switch code and data can reside in pinned memory, and the timing of disk, network operations is dominated by media which are orders of magnitude slower than physical RAM. Speaking in particular of context switches, on a typical many-core system (for instance 128-core) with several users (roughly 50 users and up to 500 active user sessions), we observe less than a handful of context switches per second per core. Any cold start effect after the context switch would be in the noise since warming all the caches take just a few million instructions (roughly a few milliseconds).

Therefore, any performance penalty we present here is likely an upper bound to the real-world one.

# 5.2 Selection of the benchmarking sets

All MPE configurations span a vast multidimensional space. Exhaustively evaluating them all is clearly infeasible, not to speak of the difficulties of properly presenting the data. Hence, we explore the design space in various stages, each consisting of a *set* of runs of the benchmark suite. Each set focuses on some previous configurations and expands the parameter space *where we expect that it has some noticeable impact*. Some schemes, such as L1 schemes, do not carry over to the successive sets because they do not have implementation parameters beyond the encryption primitive.

We use shorthands to describe the various configurations:

The optional "additional technologies" may include: counter representation (mono or split) and arity, Leaves or Branches on Chip (LoC or BoC), or the use of MACs in Repurposed ECC bits (MirE).

The default CL length is  $64\,\mathrm{B}$ , unless the counter groups are on chip, in which case it is  $128\,\mathrm{B}$ . The default MAC length is 56 to 64 bits.

"{AMD} SME" is equivalent to L1/AES/GFmul/CL64B. Here, GFmul denotes a XEX scheme where the tweaking mask is computed by multiplication of the tweak by an additional secret key, whereas when we just write XEX the mask is derived by encryption of the tweak; "{Intel} TDX" is equivalent to L2/AES/MirE/28b/CL64B, and "{Intel} SGX" is based on Client SGX, i.e., L3/AES/mono-8/56b/CL64B. LoC always implies counters are split. L2 implies that a non twekable block ciphers is used in a XEX construction, except when explicitly stated otherwise. The shorthand L3/LoC denotes a version of L3 that uses LoC, and thus no integrity tree. Similarly, L3/BoC is a L3 solution with the leaf counters off chip and the next level on chip, also without a full tree. L3 without BoC or LoC denotes a replay-protection-capable scheme based on an integrity tree and no counters on-chip.

#### 5.2.1 Simulation of system load

The benchmarks are first run on an *unloaded* system, where the current benchmark is the only running task.

We then want an upper bound for the performance degradation in a fully loaded system, with up to hundreds of processes running on dozens of processing elements, all sharing the bandwidth of the memory subsystem, such as in a cloud server. Directly simulating such a system is very complex and impractical. We instead inject synthetic traffic upstream of the MPE, but after the L2 cache. We do not include a L3 cache in the system to simulate the extreme situation where the latter has been completely swamped by traffic coming from other requesters or clusters of requesters.

The question is then, how much extra traffic we must inject.

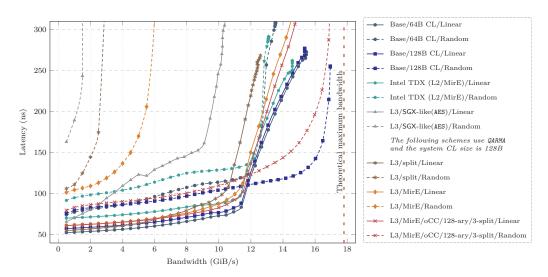

Therefore, we measure the effective memory latency of the system with various levels and schemes of memory protection, and we observe that the latency starts to degenerate catastrophically for most of them between 8 and 10 GiB/s. Fig. 6 shows how latency, and thus, at least part, also performance penalty depend on the load of the system. For instance, a SGX-like L3 MPE covering the entire memory starts to degrade if more than 8 GiB/s of traffic is injected. We take this value as the traffic for a fully-loaded system and halve it, i.e., 4 GiB/s for the partially-loaded system.

The simulated traffic consists of 75% reads and 25% writes of entire cache lines (64 B or 128 B). The access pattern is a mix of cache-line-aligned linear and random accesses. The linear accesses are sequential, and the random ones are at randomly generated addresses, both across the whole reserved range. The traffic generator alternates  $100\,\mu s$  of simulated time of linear accesses with  $200\,\mu s$  of random accesses, for as long as the workload is running.

#### 5.2.2 Baseline performance

Without memory protection, our benchmarks run on a loaded system 14.1% slower than on an unloaded system with  $64\,\mathrm{B}$  CLs, and 9.5% slower with resp.  $128\,\mathrm{B}$  CLs. Changing the CL length from  $64\,\mathrm{B}$  to  $128\,\mathrm{B}$  results in an average speedup of 1.4% in an unloaded system and 5.5% in a loaded system. The timings of all benchmark runs are always compared to the baseline with the same load and CL size.

#### 5.2.3 Initialization of short counters

When a piece of software starts to run, in a real-world setting any minor/middle counter will have assumed, because of previous processes, essentially random values. If all counters

Figure 6: Bandwidth/latency plot with various MPEs and without, for linear or random synthetic traffic.