# SCA Evaluation and Benchmarking of Finalists in the NIST Lightweight Cryptography Standardization Process

Kamyar Mohajerani<sup>1</sup>, Luke Beckwith<sup>1,2</sup>, Abubakr Abdulgadir<sup>2</sup>, Eduardo Ferrufino<sup>1</sup>, Jens-Peter Kaps<sup>1</sup> and Kris Gaj<sup>1</sup>

<sup>1</sup>Cryptographic Engineering Research Group, George Mason University Fairfax, VA, U.S.A. <sup>2</sup>PQSecure Technologies {mmohajer, lbeckwit, aabdulga, eferruf, jkaps, kgaj}@gmu.edu

Abstract. Side-channel resistance is one of the primary criteria identified by NIST for use in evaluating candidates in the Lightweight Cryptography (LWC) Standardization process. In Rounds 1 and 2 of this process, when the number of candidates was still substantial (56 and 32, respectively), evaluating this feature was close to impossible. With ten finalists remaining, side-channel resistance and its effect on the performance and cost of practical implementations became of utmost importance. In this paper, we describe a general framework for evaluating the side-channel resistance of LWC candidates using resources, experience, and general practices of the cryptographic engineering community developed over the last two decades. The primary features of our approach are a) self-identification and self-characterization of side-channel security evaluation labs, b) distributed development of protected hardware and software implementations, matching certain high-level requirements and deliverable formats, and c) dynamic and transparent matching of evaluators with implementers in order to achieve the most meaningful and fair evaluation report. After the classes of hardware implementations with similar resistance to side-channel attacks are established, these implementations are comprehensively benchmarked using Xilinx Artix-7 FPGAs. All implementations belonging to the same class are then ranked according to several performance and cost metrics. Four candidates - Ascon, Xoodyak, TinyJAMBU, and ISAP - are selected as offering unique advantages over other finalists in terms of the throughput, area, throughput-to-area ratio, or randomness requirements of their protected hardware implementations.

$\textbf{Keywords:} \ \, \text{lightweight cryptography} \, \cdot \, \text{side-channel analysis} \, \cdot \, \text{authenticated ciphers} \, \cdot \, \text{hash functions} \, \cdot \, \text{hardware} \, \cdot \, \text{software} \, \cdot \, \text{benchmarking}$

## 1 Introduction

NIST has specified resistance to Side-Channel Analysis (SCA) as one of the primary criteria for evaluating candidates in the Lightweight Cryptography (LWC) Standardization Process [1]. To assist NIST in evaluating finalists in this process, we have developed the following three calls:

- 1. Call for Side-Channel Security Validation Labs

- 2. Call for Protected Hardware Implementations, targeting low-cost modern FPGAs

- 3. Call for Protected Software Implementations, targeting low-cost modern embedded processors.

The general idea was that no single group was likely to have resources and expertise to develop and evaluate SCA-protected implementations of all 10 finalists. Additionally, self-evaluation by developers might have been insufficient and/or error-prone. Therefore, it has been the collective responsibility of the cryptographic engineering community to contribute to the evaluation process and make it as transparent and fair as possible. Contributions by multiple groups have made:

- each group's workload more manageable;

- coverage of implementation platforms more complete;

- results more credible.

These contributions were strongly encouraged and justified by at least the following factors:

- The new LWC standard is likely to be used for decades. Choosing the right algorithm had a potential to save the community countless man-hours necessary to secure implementations of a hard-to-protect standard or start a new standardization process from scratch.

- It was a joint project that multiple experts in the field could focus on in the limited amount of time devoted to analysis. Most implementations have been, by nature, open-source. Most evaluations were transparent and reproducible. This process has revealed and highlighted some implementation and evaluation methods that rarely got fully disclosed and published in the past.

- Automated insertion of countermeasures was highly desirable (especially considering the very short period reserved for developing protected implementations). Insights gained through these developments may lead to tremendous progress in the field of Computer-Aided Design (CAD) tools for SCA.

- The developed protected implementations can become benchmarks for new attacks and leakage assessment methods that can be discovered and published in years to come.

- Research on NIST standards is highly visible. Participants have been rewarded with recognition by the cryptographic community that may translate to new collaboration, funding, and publication opportunities.

The results of this effort were presented to NIST on October 27, 2022. The corresponding slides were published on the George Mason University website titled "Lightweight Cryptography in Hardware and Embedded Systems" under "Evaluation of Finalists in the NIST LWC Process" shortly after and announced on lwc-forum on November 1, 2022. Minor modifications and extensions were made on November 25, 2022. This report is a written record of these earlier presentations, providing additional details, numerical results, and additional commentary. It is published for archival purposes and to support NIST efforts on providing full justification and explanation regarding the choice of Ascon as a future federal lightweight cryptography standard.

# 2 Side-Channel Security Evaluation Labs

#### 2.1 General Idea

We called for groups capable and willing to serve as side-channel security evaluation labs to identify their capabilities and contribute to the evaluation process. Our draft call was sent for comments to lwc-forum in December 2021. The final version of this call was published on January 18, 2022. The deadline for submitting lab specifications was initially set to February 28, 2022, and then extended to March 15, 2022, for groups that expressed initial interest.

The assumption was that submitters should have access to the equipment used for side-channel leakage assessment and/or attacks, experience, and human resources necessary to perform security analysis. Suggested devices used for evaluating hardware implementations were low-cost modern FPGAs, such as Artix-7 and Spartan-7 from Xilinx, Cyclone 10 LP from Intel, and ECP5 from Lattice Semiconductor. Suggested embedded processors used for evaluating software implementations were ARM Cortex-M4F, RISC-V (e.g., RV32IMAC), Microchip 8-bit AVR, and TI MSP430. A particular lab could specialize in evaluating only hardware implementations, only software implementations, or both.

$<sup>^{1} \</sup>verb|https://cryptography.gmu.edu/athena/index.php?id=LWC|$

Table 1: Side-Channel Security Evaluation Labs that Reported Experiments Targeting Hardware Implementations

| No. | Team                                                | Evaluation<br>Platform                                                      | Target<br>FPGA<br>Family | Target<br>Boards      | Leakage<br>Assessment<br>Methods                   | Attacks                           |

|-----|-----------------------------------------------------|-----------------------------------------------------------------------------|--------------------------|-----------------------|----------------------------------------------------|-----------------------------------|

| 1   | IAIK, TU Graz,<br>Austria                           | NewAE ChipWhisperer                                                         | Artix-7                  | NewAE CW305           | t-test                                             |                                   |

| 2   | CCSL,<br>Shanghai Jiao Tong<br>University, China    | Riscure Inspector,<br>NewAE ChipWhisperer,<br>SAKURA                        | Kintex-7,<br>Spartan-6   | SAKURA-G,<br>SAKURA-X | t-test, $\chi^2$ -test, DL-LA                      | CPA, TA, MIA,<br>DL-based methods |

| 3   | HSCP Lab,<br>Tsinghua University,<br>Beijing, China | SAKURA                                                                      | Kintex-7,<br>Spartan-6   | SAKURA-G,<br>SAKURA-X | NICV, t-test, $\chi^2$ -test                       | SPA, DPA, CPA,<br>MIA, TA, LRA,   |

| 4   | Secure-IC, France                                   | Secure-IC Analyzr,<br>SAKURA                                                | Spartan-6                | SAKURA-G              | Tests specified in ISO/IEC 17825:2016              |                                   |

| 5   | CERG,<br>George Mason University,<br>USA            | FOBOS3                                                                      | Artix-7                  | NewAE CW305           | t-test                                             |                                   |

| 6   | Ruhr-Universitat Bochum,<br>Germany                 | PROLEAD and other simulation-based probing security leakage-detection tools |                          |                       | simulation-based<br>probing security<br>evaluation |                                   |

Table 2: Side-Channel Security Evaluation Labs that Reported Experiments Targeting Software Implementations

| No. | Team                                                 | Evaluation<br>Platform                                           | Target<br>Processors                           | Leakage<br>Assessment<br>Methods | Attacks                                       |

|-----|------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------|----------------------------------|-----------------------------------------------|

| 1   | CCSL, Shanghai Jiao Tong University, China           | Riscure Inspector,<br>NewAE<br>ChipWhisperer                     | ARM Cortex-M4F,<br>ATxmega128D4,<br>ATmega128A | t-test, $\chi^2$ -test, DL-LA    | CPA, TA, MIA, DL-based methods                |

| 2   | HSCP Lab, Tsinghua University, Beijing, China        |                                                                  | ARM Cortex-M4F,<br>ARM Cortex-M3               | NICV, t-test, $\chi^2$ -test     | SPA, DPA, CPA,<br>MIA, TA, LRA                |

| 3   | CESCA Lab,<br>Radboud University,<br>the Netherlands | Riscure Inspector, NewAE ChipWhisperer, Jupyter notebook scripts | ARM Cortex-M4F,<br>ATxmega128D4                | t-test, $\chi^2$ -test, DL-LA    | SPA, DPA, CPA<br>TA; DEMA;<br>DFA, FI attacks |

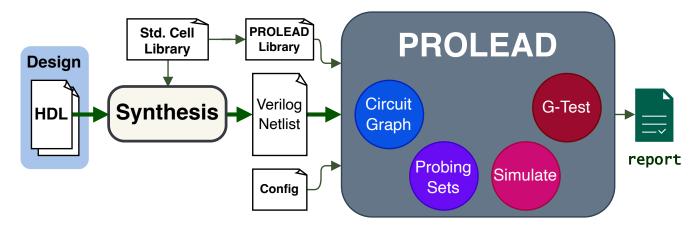

Figure 1: A simulation-based evaluation of protected hardware designs using PROLEAD

## 2.2 Lab Specifications

The specifications of labs that reported results of experiments targeting protected hardware and software implementations are summarized in Tables 1 and 2. These tables describe

- 2 labs that supported both software and hardware implementations,

- 4 labs that supported only hardware implementations, and

- 1 lab that supported only software implementations.

The detailed specifications are posted on our ATHENa Lightweight Cryptography web page at https://cryptography.gmu.edu/athena/index.php?id=LWC.

In Table 1, we summarize the major capabilities of the labs targeting hardware implementations in terms of the Evaluation Platform, Target FPGA Family, Target Board, Leakage Assessment Methods, and Key Recovery Attacks.

The most popular Evaluation Platforms were NewAE ChipWhisper and SAKURA, declared by 4 out of 6 labs. Riscure Inspector, Secure-IC Analyzr, and FOBOS3 were used by one lab each. PROLEAD [2], which is a leakage-detection tool based on simulation and probing security model, was used by one lab.

Four labs supported Xilinx 7 Series FPGA families, such as Artix-7 and Kintex-7, based on six-input Look-Up Tables (LUTs). Three labs supported Spartan-6 based on four-input Look-Up Tables (LUTs). Among the Target Boards, the most popular were SAKURA boards and NewAE CW305.

The most widely supported Leakage Assessment Method was Welch's t-test a.k.a. TVLA (Test Vector Leakage Assessment) [3]–[8]. Two labs supported a newer and supplementary Pearson's  $\chi^2$ -test introduced in [9]. The team representing Secure-IC used tests specified in ISO/IEC 17825:2016. These tests were described and critically analyzed in [10]. One lab declared support for NICV: Normalized Inter-Class Variance for Detection of Side-Channel Leakage [11], [12]. One lab listed among their methods DL-LA: Deep Learning Leakage Assessment, defined in [13]. The team from Ruhr-Universitat Bochum relied on the simulation-based tool called PROLEAD [2]. The procedure for leakage assessment with PROLEAD is depicted in Fig. 1. After the full design is synthesized, the netlist is provided to the tool, along with a description of gates (PROLEAD library) and a configuration file with details about the design operation (e.g., random and fixed inputs for the simulation step) and tool settings (e.g., number of simulations). For a d order evaluation, PROLEAD analyzes the circuit graph, generates all possible sets of d glitch-and transition- extended probes [14], simulates the design using the configured fixed and random inputs, and then analyzes the observed value on the probes using statistical G-test. By using the extended robust probing model, PROLEAD can narrow down the choice of probing sets to only primary outputs and register inputs of the design while being able to detect implementation flaws, including those arising from physical defaults such as glitches and transitions.

Two labs supported attacks, such as Simple Power Analysis (SPA), Differential Power Analysis (DPA), Correlation Power Analysis (CPA), Template Attacks (TA), Mutual Information Analysis (MIA), and Deep Learning (DL)-based methods [15].

In Table 2, we summarize major capabilities of the labs targeting software implementations in terms of the Evaluation Platform, Target Processors, Leakage Assessment Methods, and Key Recovery Attacks. The most supported target processor was ARM Cortex-M4F, listed by all three labs. Two labs supported ATxmega128D4. ATmega128A and ARM Cortex-M3 were supported by one lab each. In terms of the Leakage Assessment Methods, all labs supported the t-test and  $\chi^2$ -test. The third most popular test was the Deep Learning Leakage Assessment (DL-LA), supported by two out of three labs. The most supported attacks were Correlation Power Analysis (CPA) and Template Attacks (TA).

# 3 Protected Hardware Implementations

#### 3.1 Introduction

We submitted a draft version of the Call for Protected Hardware Implementations to lwc-forum on December 13, 2021. After analyzing all received comments and incorporating the best-received suggestions, we posted a final version of this call on the GMU Lightweight Cryptography website on January 18, 2022. According to the call, the submitted designs were expected to demonstrate strong resistance against side-channel attacks when implemented on low-cost modern FPGAs, such as Artix-7 and Spartan-7 from Xilinx, Cyclone 10 LP from Intel, and ECP5 from Lattice Semiconductor. A potential for porting the designs to ASIC (Application-Specific Integrated Circuit) technology and demonstrating their resistance in this environment was highly desirable. All submitted implementations were planned to be investigated by one or more Side-Channel Security Evaluation Labs.

#### 3.2 Requirements

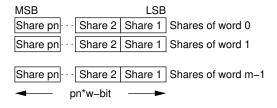

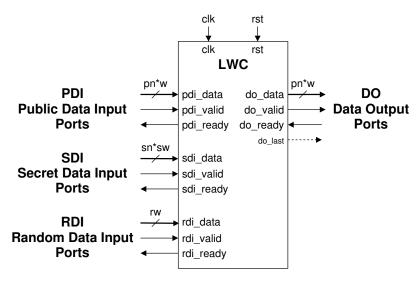

Protected hardware implementations were required to follow the LWC Hardware API v1.2.0 or later. In this extended API, we assumed that inputs and outputs are split into shares, as shown in Fig. 2. Input that is not shared (e.g., an instruction or a segment header) is put into share 1, with the remaining shares being set to zeros. The updated interface is shown in Fig. 3. In unprotected implementations, the public data input PDI accepts data of size w. For protected implementations, we modified this input to accept pn shares of size w in parallel. The same holds for the data output DO, which now provides pn shares of size w. The number of shares on the secret data input SDI is denoted as sn, as it can differ from the number of shares on PDI.

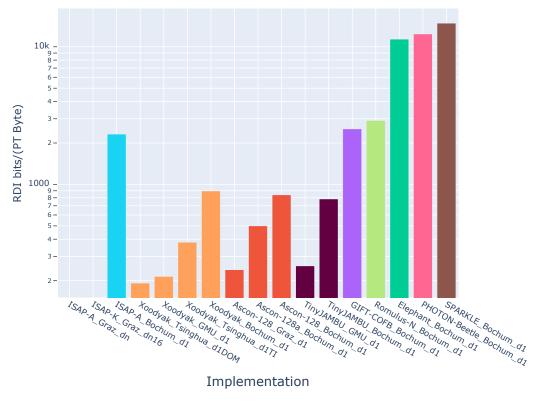

A majority of common side-channel countermeasures require the consumption of randomness during cipher operations. Any randomness an LWC implementation needs can be provided by the random data input RDI, which is of size rw. This port, just like all the others, follows a simple FIFO protocol. Each read will provide rw bits. The value of rw can be arbitrary up to 2048 bits. Note that independent of how many random bits are actually used, our testbench assumes that all rw bits are used with each read.

Figure 2: Pre-Shared Data

We also assume that a deterministic random bit generator (DRBG) used as a source of fresh randomness is located outside of the protected LWC core. The important advantages of this approach include:

- ability to share DBRG with other units (e.g., for the generation of nonces, protection of other units, e.g., those implementing public-key cryptography, etc.)

- ease of replacing the type of DBRG (e.g., due to compliance with other standards, validation requirements, evolving understanding of how cryptographically strong the DBRG used for refreshing randomness must be, etc.)

Figure 3: LWC API extended with Random Data Input (RDI)

- we are interested in evaluating/benchmarking LWC candidates and not DBRGs. The final NIST LWC selection itself could become the basis of future lightweight DBRGs.

- Concurrent operation of the DBRG circuit could introduce additional noise in the measurements and make leakage detection more difficult. There is no guarantee that this type of noise by itself could hinder an actual attack scenario, but it is likely to make the leakage evaluation more difficult (more traces, more computations, or more expensive measurement equipment).

Our testbench counted how many random bits were consumed by the protected implementation during its operation and used this information, together with the width of the rdi\_data bus, to differentiate between various protected designs. Specifically, the total number of consumed fresh random bits was one of the major items on the list of reported evaluation metrics.

We proposed the following constraints on a first-order protected implementation of an LWC candidate: 8000 LUTs, 0 Block RAMs, and 0 DSP units of Artix-7 FPGAs. The number of LUTs corresponded to the smallest device of the Artix-7 family of FPGAs. This number is also consistent with the Round 2 limit on the number of LUTs, set to 2000 LUTs, and the observation that the first-order protected hardware implementations typically took 3-4x more hardware resources than the corresponding unprotected implementations. For the implementations of two-pass algorithms, the memory (FIFO) required for the second-pass processing is instantiated as Block RAM, but stays outside of the LWC boundary and is not accounted for in the reported resource utilization of these implementations.

Table 3: Proposed constraints on resource utilization

| Type of Implementation | $\# \mathrm{LUTs}$ | # BRAMs | #DSP units |

|------------------------|--------------------|---------|------------|

| Unprotected            | $\leq 2000$        | 0       | 0          |

| 1st Order Protected    | $\leq 8000$        | 0       | 0          |

#### 3.3 Submissions

In response to our call for protected implementations, 42 protected hardware designs were received from 4 groups, covering 9 out of 10 LWC finalist schemes (all except Grain-128AEAD). These implementations are summarized in Table 4.

ISAP [16] provides mode-level robustness against a large class of implementation attacks (such as Differential Power Analysis (DPA) and fault attacks) through the usage of leakage-resilient re-keying and a two-pass construction. All other protected implementations use masking as a countermeasure against power and electromagnetic (EM)

side-channel attacks. ISAP specification recommends two underlying cryptographic permutations: ASCON-p (same as Ascon-128a) for the primary variant ISAP-A-128a, and KECCAK-p[400] for the secondary variant ISAP-K-128a. ISAP team's hardware submission <sup>2</sup> included 5 variants of ISAP-A-128a (32, 16, 8-bit interface, 2x unrolled, and StP-based tag verification) and 1 variant of ISAP-K-128a (only with 16-bit interface). Due to hardware similarities, only ISAP-A-128a with the 32-bit interface (ISAP-A\_Graz\_dn) and ISAP-K-128a (ISAP-K\_Graz\_dn16) were benchmarked. Masked implementations of ISAP provide side-channel resistance in hashing mode, as well as improved resistance against simple power analysis and template attacks.

All masked implementations are based on previously released unprotected hardware designs as listed in Table 5. Among the masked designs, 6 designs are manually protected. Three of them were developed for Xoodyak, two for Ascon, and one for TinyJAMBU.

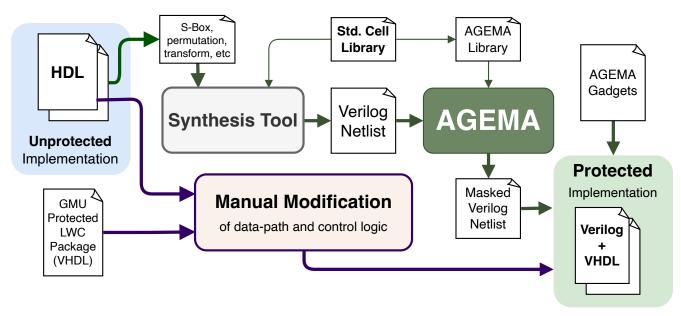

Thirty masked implementations have been generated by utilizing AGEMA [17], a tool for the semi-automated generation of masked hardware. These implementations were generated by Ruhr-University Bochum. The flow for generating masked implementations using AGEMA is depicted in Fig. 4. AGEMA operates on a synthesized netlist, identifies the wires and gates that need to be secured, and replaces them with their masked versions. To ensure secure masking, AGEMA relies on the concept of Probe-Isolating Non-Interference (PINI) and composable gadgets. Due to the insertion of extra gadget registers, the control logic of the design needs to be modified accordingly, but AGEMA is not able to detect or make the necessary adjustments to the control logic. Additionally, portions of the design which handle protocol-level and handshaking details need to be manually modified. As a result, only the combinational cryptographic permutations were processed by AGEMA and were subsequently integrated into the designs through manual modification and the use of the updated LWC package with support for masked implementations. Out of the 30 AGEMA designs made available for benchmarking, three either failed verification or synthesis, mapping, placing, and routing.

The manually protected designs use Domain Oriented Masking (DOM) [18] (Ascon-128\_Graz\_d{1,2}, Tiny-JAMBU\_GMU\_d1, Xoodyak\_GMU\_d1, and Xoodyak\_Tsinghua\_d1DOM) and Threshold Implementation (TI) [19] (Xoodyak\_Tsinghua\_d1TI) masking schemes. The semi-automatically protected designs utilize HPC2 [20] composable gadgets. For security order d, TI-based implementations require  $t \cdot d + 1$  shares, where  $t \geq 2$  is the multiplicative complexity of the non-linear portion of the design (t=2 in case of Xoodyak\_Tsinghua\_d1TI). The DOM and HPC2 schemes require d+1 shares.

A total of 63 designs, including 35 protected and 28 unprotected implementations, were benchmarked for performance and FPGA resource utilization (area).

Figure 4: Development of protected hardware designs using AGEMA

$<sup>^2 \</sup>verb|https://github.com/isap-lwc/isap-hardware-package|$

Table 4: Summary of protected and unprotected hardware designs used in this study (M: manually protected, A: protected using AGEMA)

| Finalist           | Unprotected | Order 1         | Order 2           | Order 3       |  |

|--------------------|-------------|-----------------|-------------------|---------------|--|

| Ascon              | Graz        | M: Graz         | M: Graz           | A: Bochum (2) |  |

|                    | GMU (2)     | A: Bochum (2)   | A: Bochum (2)     |               |  |

| Elephant           | GMU         | A: Bochum       | A: Bochum         | A: Bochum     |  |

| Grain-128AEAD      | GMU         |                 |                   |               |  |

| GIFT-COFB          | VT          | A: Bochum       | A: Bochum         | A: Bochum     |  |

| GIF 1-COFD         | GMU         | A. Bochum       | A. Bochum         | A. Dochum     |  |

| ISAP (Masked) Graz |             | A: Bochum       | A: Bochum         | A: Bochum     |  |

| ISAP               |             | Graz (mode-leve | l protection) (6) |               |  |

| PHOTON-Beetle      | GMU         | A: Bochum       | A: Bochum         | A: Bochum     |  |

| Romulus            | NTU         | A: Bochum       | A: Bochum         | A: Bochum     |  |

| SPARKLE            | VT          | A: Bochum       | A: Bochum         | A: Bochum     |  |

| SIARRE             | GMU         | A. Bochum       | A. Dochum         | A. Dochum     |  |

| TinyJAMBU          | GMU         | M: GMU          | A: Bochum         | A: Bochum     |  |

| ImyJAMDO           | TJ Team     | A: Bochum       | A. Bochum         | A. Dochum     |  |

|                    | XT Team     | M: Tsinghua (2) |                   |               |  |

| Xoodyak            |             | M: GMU          | A: Bochum         | A: Bochum     |  |

|                    | GMU (2)     | A: Bochum       |                   |               |  |

Table 5: Protected implementations and the corresponding unprotected designs they are based on. Fastest and Smallest columns specify whether the unprotected base has the highest encryption (PT) throughput and/or lowest area (number of LUTs) respectively among the benchmarked unprotected implementations of the same scheme. "OA" signifies that the unprotected base was the only implementation available and "OO" means that the unprotected base was the only implementation which the source code was publicly available.

| Implementation                                    | Unprotected Base             | Fastest | Smallest     |

|---------------------------------------------------|------------------------------|---------|--------------|

| $\overline{\text{Ascon-128\_Bochum\_d}\{1,2,3\}}$ | Ascon-128_Graz-x1            | Х       | X            |

| $Ascon\text{-}128\_Graz\_d\{1,2\}$                | Ascon-128_Graz-x1            | X       | X            |

| $Ascon-128a\_Bochum\_d\{1,2,3\}$                  | Ascon-128a_Graz-x1           | X       | $\checkmark$ |

| $Elephant\_Bochum\_d\{1,2,3\}$                    | ${\bf Elephant\_GMU}$        | OA      | OA           |

| ${\tt GIFT\text{-}COFB\_Bochum\_d\{1,2,3\}}$      | ${\rm GIFT\text{-}COFB\_VT}$ | X       | X            |

| $ISAP-A\_Bochum\_d\{1,2,3\}$                      | $ISAP-A\_Graz\_dn$           | OA      | OA           |

| $PHOTON\text{-}Beetle\_Bochum\_d\{1,2,3\}$        | $PHOTON\text{-}Beetle\_GMU$  | OA      | OA           |

| $Romulus-N\_Bochum\_d\{1,2,3\}$                   | Romulus-N_RT-x1              | OA      | OA           |

| $SPARKLE\_Bochum\_d\{1,2,3\}$                     | SPARKLE_VT                   | X       | X            |

| $TinyJAMBU\_Bochum\_d\{1,2,3\}$                   | ${\bf TinyJAMBU\_GMU}$       | 00      | 00           |

| $TinyJAMBU\_GMU\_d1$                              | $TinyJAMBU\_GMU$             | OO      | 00           |

| $Xoodyak\_Bochum\_d\{1,2,3\}$                     | Xoodyak_XT-x1                | X       | $\checkmark$ |

| $Xoodyak\_GMU\_d1$                                | Xoodyak_GMU-x1               | X       | X            |

| $Xoodyak\_Tsinghua\_d1\{DOM,TI\}$                 | Xoodyak_XT-x1                | X       | ✓            |

Table 6: Protected Hardware Implementations of LWC Finalists

| Candidates                                                                                 | Protection<br>Order | Protection<br>Method  | HDL                  | Variants             | Initial<br>Evaluation | Primary<br>Hardware<br>Designers                                                        | Academic Advisors /<br>Program Managers  |

|--------------------------------------------------------------------------------------------|---------------------|-----------------------|----------------------|----------------------|-----------------------|-----------------------------------------------------------------------------------------|------------------------------------------|

| $ISAP^3$                                                                                   | N/A                 | Mode-level robustness | VHDL                 | 6                    | Analytical            | Robert Primas                                                                           | Stefan Mangard                           |

| Ascon Elephant GIFT-COFB ISAP PHOTON-Beetle <sup>4</sup> Romulus SPARKLE TinyJAMBU Xoodyak | 1, 2, 3             | HPC2                  | Verilog<br>+<br>VHDL | Ascon:6<br>Others: 3 | PROLEAD [2]           |                                                                                         | Amir Moradi                              |

| $egin{aligned} \mathbf{TinyJAMBU}^5 \ \mathbf{Xoodyak}^6 \end{aligned}$                    | 1                   | DOM                   | VHDL                 | 1                    | t-test                | TinyJAMBU: Sammy Lin, Abubakr Abdulgadir Xoodyak: Abubakr Abdulgadir, Richard Haeussler | Jens-Peter Kaps,<br>Kris Gaj             |

| $\mathbf{A}\mathbf{scon}^7$                                                                | 1, 2                | DOM                   | VHDL                 | 1                    | CocoAlma<br>[21]      | Robert Primas,<br>Rishub Nagpal                                                         | Stefan Mangard                           |

| Xoodyak <sup>8</sup>                                                                       | 1                   | DOM, TI               | Verilog<br>+<br>VHDL | 2                    | t-test                | Shuohang Peng,<br>Shuying Yin,<br>Cankun Zhao                                           | Leibo Liu,<br>Bohan Yang,<br>Wenping Zhu |

<sup>3</sup>https://github.com/isap-lwc/isap-hardware-package

4https://github.com/Chair-for-Security-Engineering/LWC-Masking

5https://github.com/GMUCERG/TinyJAMBU-SCA

6https://github.com/GMUCERG/Xoodyak-SCA

7https://github.com/ascon-hardware

<sup>8</sup>https://github.com/ybhphoenix/THU\_HWSec\_LWC

# 4 Protected Software Implementations

We called for software implementations of finalists resistant against side-channel attacks such as power and electromagnetic analysis, using the same timeline as in the case of hardware implementations. The focus of our call was on the use of platform-independent algorithmic countermeasures. The submitted code was expected to demonstrate strong resistance against side-channel attacks when executed on low-cost modern embedded processors, such as ARM Cortex M4F, RISC-V (e.g., RV32IMAC), Microchip 8-bit AVR, and TI MSP430. This code could contain assembly language instructions specific to a given Instruction Set Architecture (ISA).

Protected software implementations were expected to use the standard NIST API defined in Submission Requirements and Evaluation Criteria for the Lightweight Cryptography Standardization Process, published in August 2018<sup>9</sup>. Protected implementations were not allowed to use nsec, beyond specifying it as an argument of crypto\_aead\_encrypt() and crypto\_aead\_decrypt() set to NULL.

## 5 GMU Team role

Our team was in communication with the evaluation labs and the implementation submitters aiming at the best match between both groups. The final matches are summarized at the GMU Lightweight Cryptography in Hardware and Embedded Systems web page<sup>10</sup>.

Our team also performed a t-test on the protected implementations of Ascon, Elephant, PHOTON-Beetle, TinyJAMBU, and Xoodyak developed using AGEMA at the Ruhr University of Bochum.

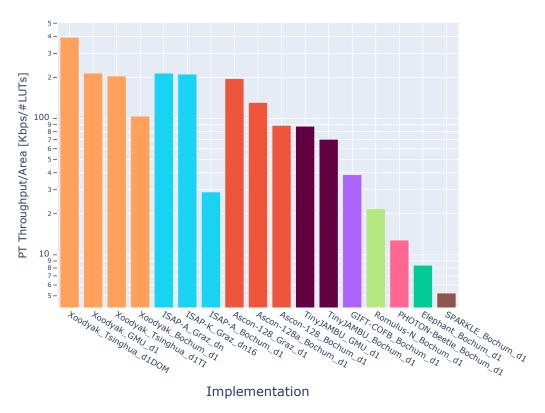

Additionally, the GMU team benchmarked and ranked implementations with a comparable security level in terms of Throughput, Area, Throughput/Area, and the number of random bits per each byte of plaintext and associated data (AD). The benchmarking was performed using the Xilinx Artix-7 family of FPGA devices.

Our team has published the record of evaluations in progress and reports from the completed evaluations on the mentioned above website.

## 6 Side-channel Evaluation Results

The parameters of security validation experiments and the corresponding results are shown in Tables 7 and 8 for hardware implementations and Tables 9 and 10 for software implementations. The tables capture the significant parameters of each experiment and results, and interested readers are referred to the detailed reports available on the ATHENa Lightweight Cryptography web page<sup>11,12</sup>. The goal of these tests was to provide confidence in the effectiveness of the countermeasures to achieve the stated security level. Additionally, feedback from evaluations was helpful for implementation teams to refine their implementations and fix bugs so that benchmarked designs were as close as possible to achieving the claimed side-channel resistance.

#### 6.1 Hardware Implementations Result Summary

Table 7 shows that most of the tests are leakage assessment tests. Specifically, the Test Vector Leakage Assessment [3], [5] and  $\chi^2$ -test [9] have been used. The attack performed was Correlation Power Analysis (CPA). In one instance, a template attack (TA) was attempted.

The most used targets (Evaluation Platforms) were NewAE ChipWhisperer CW305, SASEBO-GIII, and SAKURA boards using Xilinx Artix-7 and Kintex-7 FPGAs. These targets were clocked at 1-100 MHz, and side-channel information was measured using both shunt resistors and electromagnetic emanation (EM).

A wide range of oscilloscope settings has been used. The sampling rate varied from 22 MHz to 6.25 GHz, and the resolution from 8 to 12 bits. Most of the experiments used sampling clocks that were not synchronized to the target clock. The experiments performed by CERG use the FOBOS control board, which contains a version of OpenADC, as the oscilloscope.

<sup>9</sup>https://csrc.nist.gov/CSRC/media/Projects/Lightweight-Cryptography/documents/final-lwc-submission-requirements-august2018.pdf

$<sup>^{10} {\</sup>tt https://cryptography.gmu.edu/athena/index.php?id=LWC}$

<sup>11</sup>https://cryptography.gmu.edu/athena/LWC/Lab\_Implementation\_Matching\_HW.html

$<sup>^{12} \</sup>mathtt{https://cryptography.gmu.edu/athena/LWC/Lab\_Implementation\_Matching\_SW.html}$

Table 7: Results of Side-channel Evaluation of Protected Hardware Implementations

|                                                                                      |           |             |                  | Freq.    | Sampl. |        | Meas. |                |

|--------------------------------------------------------------------------------------|-----------|-------------|------------------|----------|--------|--------|-------|----------------|

| Implementation                                                                       | Lab       | Target      | Oscilloscope     | [MHz]    | Freq.  | lution | Type  | Test           |

|                                                                                      |           |             |                  | [IVIIIZ] | [MS/s] | [bits] | турс  |                |

| Ascon_Bochum_d1                                                                      | CERG      | CW305       | FOBOS3 ADC       | 16       | 80     | 10     | power | TVLA           |

| $Ascon\_Bochum\_d1$                                                                  | IAIK      | CW305       | PicoScope 6404C  | 1        | 22     | 8      | power | TVLA           |

| $Ascon\_Bochum\_d1$                                                                  | CCSL      | SAKURA-X    | LeCroy 610Zi     |          | 1000   | 8      | EM    | TVLA           |

| Ascon_Bochum_d1                                                                      | CCSL      | SAKURA-X    | LeCroy 610Zi     |          | 1000   | 8      | EM    | $\chi^2$ -test |

| Ascon_Bochum_d1                                                                      | CCSL      | SAKURA-X    | LeCroy 610Zi     |          | 1000   | 8      | EM    | CPA            |

| $Ascon_v1\_Graz\_d1$                                                                 | HSCP      | SAKURA-G    | WaveRunner 8404M | 4        | 100    | 8      | power | TVLA           |

| $Elephant\_Bochum\_d1$                                                               | CERG      | CW305       | FOBOS3 ADC       | 10       | 50     | 10     | power | TVLA           |

| $Elephant\_Bochum\_d1$                                                               | IAIK      | CW305       | PicoScope 6404C  | 1        | 22     | 8      | power | TVLA           |

| $GIFT\_COFB\_Bochum\_d1$                                                             | IAIK      | CW305       | PicoScope 6404C  | 1        | 22     | 8      | power | TVLA           |

| $GIFT\_COFB\_Bochum\_d1$                                                             | CCSL      | SASEBO-GIII |                  |          | 500    | 8      | EM    | TVLA           |

| $GIFT\_COFB\_Bochum\_d1$                                                             | CCSL      | SASEBO-GIII |                  |          | 500    | 8      | EM    | $\chi^2$ -test |

| $\operatorname{GIFT}_{\operatorname{COFB}}_{\operatorname{Bochum}}\operatorname{d}1$ | CCSL      | SASEBO-GIII |                  |          | 500    | 8      | EM    | $\chi^2$ -test |

| $\operatorname{GIFT}_{\operatorname{COFB}}_{\operatorname{Bochum}}\operatorname{d}1$ | CCSL      | SASEBO-GIII |                  |          | 500    | 8      | EM    | CPA            |

| $ISAP\_Bochum\_d1$                                                                   | CCSL      | Kintex 7    | LeCroy 610Zi     |          |        |        | EM    | CPA            |

| $ISAP\_Bochum\_d1$                                                                   | CCSL      | Kintex 7    | LeCroy 610Zi     |          |        |        | EM    | TVLA           |

| $ISAP\_Bochum\_d1$                                                                   | CCSL      | Kintex 7    | LeCroy 610Zi     |          |        |        | EM    | $\chi^2$ -test |

| $ISAP\_Graz$                                                                         | CCSL      | Kintex 7    | LeCroy 610Zi     |          |        |        | EM    | CPA            |

| Photon Beetle_Bochum_d1                                                              | CERG      | CW305       | FOBOS3 ADC       | 16       | 80     | 10     | power | TVLA           |

| Romulus_Bochum_d1                                                                    | IAIK      | CW305       | PicoScope 6404C  | 1        | 22     | 8      | power | TVLA           |

| $Romulus\_Bochum\_d1$                                                                | CCSL      | SASEBO-GIII |                  |          | 500    | 8      | EM    | TVLA           |

| $Romulus\_Bochum\_d1$                                                                | CCSL      | SASEBO-GIII |                  |          | 500    | 8      | EM    | TVLA           |

| Romulus_Bochum_d1                                                                    | CCSL      | SASEBO-GIII |                  |          | 500    | 8      | EM    | $\chi^2$ -test |

| Romulus_Bochum_d1                                                                    | CCSL      | SASEBO-GIII |                  |          | 500    | 8      | EM    | $\chi^2$ -test |

| $Romulus\_Bochum\_d1$                                                                | CCSL      | SASEBO-GIII |                  |          | 500    | 8      | EM    | CPA            |

| $Romulus\_Bochum\_d1$                                                                | CCSL      | SASEBO-GIII |                  |          | 500    | 8      | EM    | TA             |

| TinyJAMBU_Bochum_d1                                                                  | CERG      | CW305       | FOBOS3 ADC       | 10       | 50     | 10     | power | TVLA           |

| TinyJAMBU_GMU_d1                                                                     | HSCP      | SAKURA-G    | WaveRunner 8404M | 4        | 100    | 8      | power | TVLA           |

| Xoodyak_Bochum_d1                                                                    | IAIK      | CW305       | PicoScope 6404C  | 1        | 22     | 8      | power | TVLA           |

| Xoodyak_GMU_d1                                                                       | Secure-IC | Arty A7     | Tektronix MSO64  | 100      | 6250   | 12     | EM    | TVLA           |

| $Xoodyak_Bochum_d1$                                                                  | CERG      | CW305       | FOBOS3 ADC       | 10       | 50     | 10     | power | TVLA           |

Num. of Thresh. Implementation Lab Test Notes Traces Exc.  $[\times 10^{6}]$ Y(1.5M) Ascon Bochum d1 **CERG TVLA** 10 6 out of 1000+ samples exceed the threshold Ascon\_Bochum\_d1 IAIK TVLA Ν 10 Ascon Bochum d1 CCSL TVLA 1 Ν  $\chi^2$ -test Ascon Bochum d1 CCSL 1 Ν CCSL Ascon Bochum d1 CPA 11 No bytes revealed Ascon v1 Graz d1 **HSCP** TVLAΝ 10 Elephant\_Bochum\_d1 CERG TVLA 7 Y(2.7M)3 out of 12,000+ samples exceed the threshold Elephant\_Bochum\_d1 IAIK TVLA 10 Ν GIFT COFB Bochum d1 IAIK TVLA 10 Ν Classification based on a nonce bit. A similar test was CCSL GIFT\_COFB\_Bochum\_d1 TVLA 1 Ν also based on a bit in an intermediate value. Classification based on a nonce bit: threshold  $\chi^2$ -test GIFT\_COFB\_Bochum\_d1 CCSL 1  $\mathbf{Y}$ exceeded CCSL  $\chi^2$ -test Classification based on a bit in an intermediate value GIFT COFB Bochum d1 1 Ν CCSLCPA1 GIFT\_COFB\_Bochum\_d1 Key not revealed ISAP Bochum d1 CCSL CPA Kev not revealed Some samples exceeding the threshold observed ISAP\_Bochum\_d1 CCSL **TVLA**  $\mathbf{Y}$  $\chi^2$ -test ISAP\_Bochum\_d1 CCSL $\mathbf{Y}$ Some samples exceeding the threshold observed ISAP Graz CCSL CPAKey not revealed t-values crossed threshold briefly before returning PHOTON-Beetle Bochum d1 CERG TVLA 10 Ν below threshold Romulus\_Bochum\_d1 IAIK TVLA 10 Ν Case A: Few samples exceed the threshold at Romulus Bochum d1 CCSL **TVLA** 10  $\mathbf{Y}$ 1 M traces. Classification based on a nonce bit. Case B: No samples exceed the threshold CCSL Romulus Bochum d1 TVLA 1 Ν at 1 M traces. Classification based on an intermediate bit. Case A: Few samples exceed the threshold at  $\mathbf{Y}$  $\chi^2$ -test Romulus Bochum d1 CCSL1 1 M traces. Classification based on a nonce bit.

Table 8: Results of Side-channel Evaluation of Protected Hardware Implementations

| Romulus_Bochum_d1     | CCSL      | $\chi^2$ -test | 1   | N            | Case B: No samples exceed the threshold at 1 M traces. Classification based on an intermediate bit.                                                      |

|-----------------------|-----------|----------------|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| $Romulus\_Bochum\_d1$ | CCSL      | CPA            | 1   | _            | Key not revealed                                                                                                                                         |

| $Romulus\_Bochum\_d1$ | CCSL      | TA             | 1   | _            | Key not revealed                                                                                                                                         |

| TinyJAMBU_Bochum_d1   | CERG      | TVLA           | 10  | N            | One sample exceeded the threshold so the test repeated again. Another sample exceeded the threshold but at another location indicating a false positive. |

| $TinyJAMBU\_GMU\_d1$  | HSCP      | TVLA           | 10  | $\mathbf N$  |                                                                                                                                                          |

| Xoodyak_Bochum_d1     | IAIK      | TVLA           | 10  | $\mathbf{N}$ |                                                                                                                                                          |

| $Xoodyak\_GMU\_d1$    | Secure-IC | TVLA           | 0.1 | $\mathbf N$  | Classification based on an input plaintext bit                                                                                                           |

| $Xoodyak\_Bochum\_d1$ | CERG      | TVLA           | 10  | Y(3.2M)      | 10 out of 900 samples exceed the threshold                                                                                                               |

SCA Evaluation and Benchmarking of LWC Finalists

| Implementation                | Lab   | Target                  | TM32F407 Pico 3206D 1 TM32F303 Pico 3203D TM32F303 Pico 3203D TM32F303 Pico 3203D TM32F303 | Freq. | Sampl. Freq. $[MS/s]$ | Resolution [bits] | Meas. Type | Test    |

|-------------------------------|-------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------|-------------------|------------|---------|

| Ascon_Graz_d1                 | CESCA | STM32F407               | Pico 3206D                                                                                                                                                                                                                        | 168   | 100-1000              | 8                 | EM         | CPA     |

| $Ascon\_Graz\_d2$             | CCSL  | ${\rm STM}32{\rm F}303$ | Pico 3203D                                                                                                                                                                                                                        |       | 62.5                  | 16                | EM         | TVLA    |

| $Ascon\_Graz\_d2$             | CCSL  | ${\rm STM}32{\rm F}303$ | Pico 3203D                                                                                                                                                                                                                        |       | 62.5                  | 16                | EM         | X2-test |

| $Ascon\_Graz\_d2$             | CCSL  | ${\rm STM}32{\rm F}303$ | Pico 3203D                                                                                                                                                                                                                        |       | 62.5                  | 16                | EM         | CPA     |

| ${\rm GIFT\_COFB\_Adomnicai}$ | CCSL  | ${\rm STM}32{\rm F}303$ |                                                                                                                                                                                                                                   |       | 125                   | 16                | EM         | TVLA    |

| ${\rm GIFT\_COFB\_Adomnicai}$ | CCSL  | ${\rm STM}32{\rm F}303$ |                                                                                                                                                                                                                                   |       | 125                   | 16                | EM         | X2-test |

| ${\rm GIFT\_COFB\_Adomnicai}$ | CCSL  | ${\rm STM}32{\rm F}303$ |                                                                                                                                                                                                                                   |       | 125                   | 16                | EM         | CPA     |

| ${\it GIFT-COFB\_Adominicai}$ | HSCP  | ${\rm STM}32{\rm F}303$ |                                                                                                                                                                                                                                   | 8     | 25                    | 8                 | power      | TVLA    |

| $ISAP\_ISAP\_Team$            | CESCA | ${\rm STM}32{\rm F}407$ |                                                                                                                                                                                                                                   | 100   | 100-1000              | 8                 | EM         | TVLA    |

| $ISAP\_ISAP\text{-}team$      | CCSL  | ${\rm STM}32{\rm F}303$ | LeCroy 610Zi                                                                                                                                                                                                                      |       |                       |                   | EM         | CPA     |

| Romulus_Adominicai            | HSCP  | ${\rm STM}32{\rm F}303$ | WaveRunner 8404M                                                                                                                                                                                                                  | 8 I   | 25                    | 8                 | power      | TVLA    |

| Romulus_Adomnicai             | CCSL  | ${\rm STM}32{\rm F}303$ |                                                                                                                                                                                                                                   |       | 125                   | 16                | EM         | TVLA    |

| Romulus_Adomnicai             | CCSL  | ${\rm STM}32{\rm F}303$ |                                                                                                                                                                                                                                   |       | 125                   | 16                | EM         | TVLA    |

| Romulus_Adomnicai             | CCSL  | ${\rm STM}32{\rm F}303$ |                                                                                                                                                                                                                                   |       | 125                   | 16                | EM         | DL-LA   |

| Romulus_Adomnicai             | CCSL  | ${\rm STM}32{\rm F}303$ |                                                                                                                                                                                                                                   |       | 125                   | 16                | EM         | DL-LA   |

| Romulus_Adomnicai             | CCSL  | ${\rm STM}32{\rm F}303$ |                                                                                                                                                                                                                                   |       | 125                   | 16                | EM         | CPA     |

| Romulus_Adomnicai             | CCSL  | STM32F303               |                                                                                                                                                                                                                                   |       | 125                   | 16                | EM         | TA      |

Table 9: Results of Side-channel Evaluation of Protected Software Implementations

Table 10: Results of Side-channel Evaluation of Protected Software Implementations

| Implementation       | Lab   | Test           | Num. of Traces $[\times 10^6]$ | Thresh.      | Notes                                                    |

|----------------------|-------|----------------|--------------------------------|--------------|----------------------------------------------------------|

| Ascon_Graz_d1        | CESCA | CPA            | 15                             | _            | Second order CPA. No bytes revealed.                     |

| $Ascon\_Graz\_d2$    | CCSL  | TVLA           | 0.06                           | N            |                                                          |

| $Ascon\_Graz\_d2$    | CCSL  | $\chi^2$ -test | 0.06                           | N            |                                                          |

| $Ascon\_Graz\_d2$    | CCSL  | CPA            | 0.06                           | _            | Key not revealed                                         |

|                      |       |                |                                |              | Classification based on a nonce bit.                     |

| GIFT_COFB_Adomnicai  | CCSL  | TVLA           | 0.02                           | N            | Another test was done with classification                |

|                      |       |                |                                |              | based on an intermediate bit.                            |

|                      |       |                |                                |              | Classification based on a nonce bit.                     |

| GIFT_COFB_Adomnicai  | CCSL  | $\chi^2$ -test | 0.02                           | N            | Another test was done with classification                |

|                      |       |                |                                |              | based on an intermediate bit.                            |

| GIFT_COFB_Adomnicai  | CCSL  | CPA            | 0.02                           | _            | Key not revealed                                         |

| GIFT-COFB_Adominicai | HSCP  | TVLA           | 0.1                            | $\mathbf{Y}$ | Threshold exceeded. Report mentions possible causes.     |

| ISAP_ISAP_Team       | CESCA | TVLA           | 0.1                            | N            | Fixed key vs random key test                             |

| ISAP_ISAP-team       | CCSL  | CPA            |                                | _            | Key not revealed                                         |

| Romulus_Adominicai   | HSCP  | TVLA           | 0.1                            | ${f Y}$      | Threshold exceeded. Report mentions possible causes.     |

| Romulus_Adomnicai    | CCSL  | TVLA           | 1                              | N            | Case A: No sample exceeded the threshold for 1 M traces. |

| Romulus_Adomnicai    | CCSL  | IVLA           | 1                              | IN           | Classification based on a nonce bit.                     |

| Romulus_Adomnicai    | CCCT  | TVLA           | 1                              | N            | Case B: No samples exceed the threshold for 1 M traces.  |

| Romulus_Adomnicai    | CCSL  | IVLA           | 1                              | IN           | Classification based on an intermediate bit.             |

| D                    | CCCT  | DIIA           |                                | <b>N</b> T   | Case A: No sample exceed the threshold for 1 M traces.   |

| Romulus_Adomnicai    | CCSL  | DL-LA          |                                | N            | Classification based on a nonce bit.                     |

| D 1 A1               | CCCT  | DIIA           |                                |              | Case B: No samples exceed the threshold for 1 M traces.  |

| Romulus_Adomnicai    | CCSL  | DL-LA          |                                | _            | Classification based on an intermediate bit.             |

| Romulus_Adomnicai    | CCSL  | CPA            |                                | _            | Key not revealed                                         |

| Romulus_Adomnicai    | CCSL  | TA             |                                | _            | Key not revealed                                         |

Table 8 highlights the results of security evaluation experiments. In most leakage assessment tests, the predefined threshold was not crossed for the given test parameters. In some cases, the threshold was exceeded. In such cases, we report the number of traces at which the threshold was exceeded if mentioned in the report. Below, we provide notes on the experiments that exceeded the pre-defined threshold. It is noteworthy that having a leakage assessment test exceeding the threshold does not necessarily indicate an exploitable leakage, and there is a possibility of false positives.

- The tests on Ascon\_Bochum\_d1, Elephant\_Bochum\_d1, and Xoodyak\_Bochum\_d1 by the CERG lab: In all of these cases, the TVLA 4.5 threshold is exceeded at a few (3-10) samples. These tests use a sampling clock that is synchronized with the target clock, which results in more precise measurements. For all of these tests, t-values do not exceed the threshold until more than one million traces have been considered.

- The TVLA and  $\chi^2$ -tests on GIFT\_COFB\_Bochum\_d1, ISAP\_Bochum\_d1, and Romulus\_Bochum\_d1 by the CCSL lab: In these tests, the threshold has been exceeded. These test results were published in August 2022. Consequently, these implementations were updated in November 2022 when a bug related to providing randomness to masked gadgets was fixed.

The implementations from Bochum were generated using the AGEMA tool, which is used to convert the datapath to a masked design. The control logic, however, needs manual modification to provide the needed randomness to the masked gadgets in the proper cycles. In the first round of evaluations, leakage in the Bochum submissions was attributed to the fact that random data was not fed correctly to the masked gadgets. In other words, required fresh randomness was not provided in some clock cycles. The submitter corrected this issue by minor changes in the control logic that had a negligible effect on area and throughput. This negligible effect was confirmed for the cases of the TinyJAMBU\_Bochum\_d1 and Ascon\_Bochum\_d1 implementations, analyzed by CERG.

None of the reported CPA or template attacks attempted on the protected designs resulted in the reliable recovery of any key fragment. CPA attacks, as expected, attempted key recovery at the initialization phase when the nonce and the key are used to initialize the state and before intermediate values become a function of too many secret key bits.

All the tested hardware implementations use first-order masking except ISAP\_Graz, which depends on mode-level protection. For mode-level resistance attack-based evaluation is more meaningful than leakage assessment which can show unexploitable leakage. As shown in Table 8, the CPA attack on the ISAP\_Graz did not reveal the key.

We conclude that although some implementations show some leakage in the leakage assessment tests, these leakages are most likely fixable without significant changes in cost and performance. In many tests, we observed that leakage is significantly reduced by minor fixes in the control logic responsible for feeding randomness to the masked gadgets with no change to the datapath, which uses the majority of resources.

## 6.2 Software Implementations Result Summary

Tables 9 and 10 summarize the parameters and the results of the experiments performed on the protected software implementations. Similar to the case of hardware implementations, most of the experiments are leakage assessment tests in the form of TVLA,  $\chi^2$ -test, and DL-LA. Correlation Power Analysis and template attacks (TA) were also attempted. All experiments used ARM Cortex-M4 as a target, and side-channel information was measured using shunt resistors and electromagnetic emanation (EM). None of the experiments reported the usage of sampling clocks that were synchronized to the target clock.

None of the reported CPA or template attacks attempted on the protected software designs resulted in the recovery of any part of the key. A second-order CPA attack by the CESCA lab could not reveal the key for Ascon\_Graz\_d1 using 15 million traces. In comparison, their CPA attack on the unprotected Ascon implementation can reliably reveal the key using 500 thousand traces.

The security analysis on ISAP by the CESCA lab concluded that DPA attacks were not an option except for the tag generation operation.

In most leakage assessment tests, the predefined threshold has not been crossed for the given test parameters. In some cases, the threshold has been exceeded. Below, we provide notes on the experiments that exceeded the predefined threshold.

- GIFT-COFB\_Adominical TVLA test by the HSCP lab: TVLA threshold has been exceeded in this test, and the submitted report attributes this to the unmasking of the state when performing encryption and decryption. The report shows no leakage in the key scheduling part of the algorithm.

- Romulus\_Adominical TVLA test by the HSCP lab: TVLA threshold has been exceeded. The evaluation report points out that this leakage is partially due to the associated data not being masked.

As noted in the reports by the HSCP team, these implementations could be leveled implementations where some part of the algorithm is protected against DPA while other parts are protected against SPA. In this case, direct application of leakage assessment tests will show a leakage.

In conclusion, in the outcomes of the tests on the protected software implementations, no leakage has been detected except in the two cases listed above. For these cases, further analysis is needed to see if the leakage is exploitable.

## 6.3 Target and Sampling Clock Synchronization

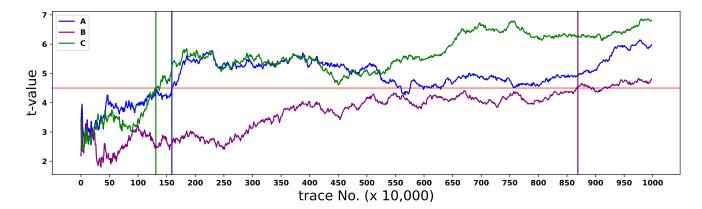

The effect of synchronizing the sampling and the target clocks on the number of traces needed for key recovery has been observed and discussed in the literature [22]. In this section, we show that performing sampling for leakage assessment using a synchronized clock is significantly more effective in leakage detection. In other words, using synchronized sampling and target clocks, one can detect leakage using significantly fewer traces than in setups using asynchronous clocks.

In the following tests, we use a masked implementation of the NIST LWC finalist Xoodyak\_Bochum\_d1. While the datapath of the design is masked, the control logic has an issue with providing random bits at some clock cycles, causing leakage.

We performed TVLA tests on the masked implementation of Xoodyak using an external oscilloscope at a sampling rate of 1 GS/s and 125 MS/s using 8-bit and 15-bit resolution, respectively. We repeated the same experiment, but this time, we used FOBOS 3 to capture traces at 50 MS/s with 10-bit resolution. In the FOBOS 3 case, the ADC clock is synchronized with the target clock, while the external oscilloscope sampling clock is not. Table 11 shows the details of each experiment and the corresponding results. In all cases, we used exactly the same Xoodyak implementation, which was instantiated in the NewAE C305 board and ran at 10 MHz, and we used the same fixed-vs-random test vectors.

Figure 5 shows the maximum t value in each experiment as a function of the number of traces processed. The red line marks the 4.5 threshold with t values exceeding this threshold, indicating leakage detection. The figure shows that in test C, which uses the synchronous clock, the t values exceed the threshold after processing 1.3 million traces. For experiment A, the test detects leakage after processing 1.6 million traces, while in experiment B, the leakage is detected after 8.7 million traces are processed.

When comparing experiment C, which uses synchronous clocks v.s, experiment B, we observe that although both sampling rate and resolution are higher in experiment B, the experiment with synchronized clocks detects the leakage using significantly fewer traces.

Table 11: TVLA results for the masked Xoodyak implementation depending on the measurement setup; all run for 10 Million traces

| Oscilloscope    | DUT   | Reso-            | Sync. | $\mathbf{Sample}$  | $\mathbf{DUT}$   | Fails at        | Label |  |

|-----------------|-------|------------------|-------|--------------------|------------------|-----------------|-------|--|

| Oscinoscope     | DOI   | lution           | bync. | Rate               | Freq.            | Traces          | Laber |  |

| PicoScope 5244D | CW305 | 8 bit            | No    | $1\mathrm{GS/s}$   | $10\mathrm{MHz}$ | $1.6\mathrm{M}$ | A     |  |

| PicoScope 5244D | CW305 | $15\mathrm{bit}$ | No    | $125\mathrm{MS/s}$ | $10\mathrm{MHz}$ | $8.7\mathrm{M}$ | В     |  |

| FOBOS 3         | CW305 | $10\mathrm{bit}$ | Yes   | $50\mathrm{MS/s}$  | $10\mathrm{MHz}$ | $1.3\mathrm{M}$ | С     |  |

### 6.4 Qualitative Evaluation

In addition to quantitative evaluations, such as those summarized in this report, theoretical analysis of leakage properties and countermeasures are of extreme importance. An insightful analysis of the side-channel security of NIST LWC finalists was carried out by Verhamme et al. in [23]. Additionally, the authors investigated "leveled" implementations for Ascon, ISAP, Romulus-T, and Romulus-N, where only parts of the implementation require

Figure 5: Maximum t value vs. the number of processed traces. Vertical lines indicate the point at which the t value exceeds the threshold in each experiment

masking (or higher order masking), reducing the performance and/or area overhead while maintaining the desired level of side-channel security. We believe that both qualitative and quantitative approaches have their merits and limitations and provide complementary information for evaluating cryptographic schemes and their implementations. Unfortunately, no implementations incorporating the "leveled" protection approach were available to us while conducting the evaluation, and therefore, they are not being represented in our results.

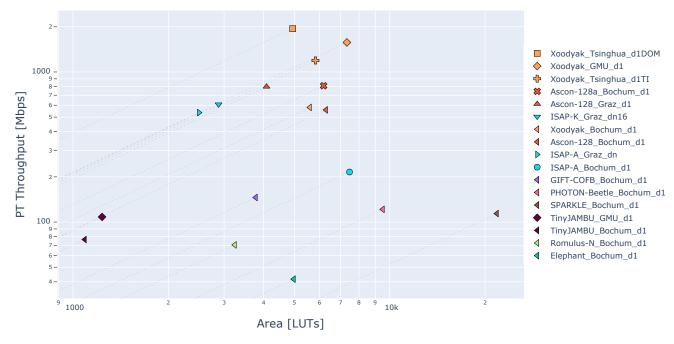

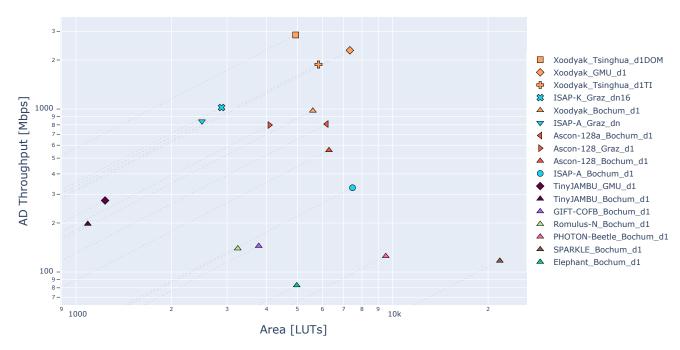

# 7 Benchmarking of Hardware Implementations

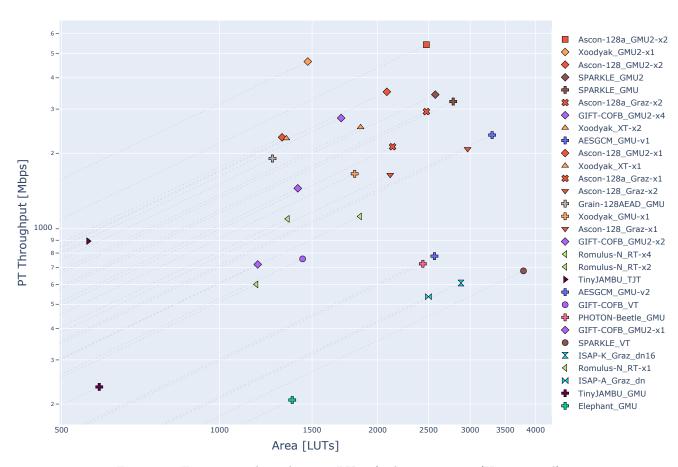

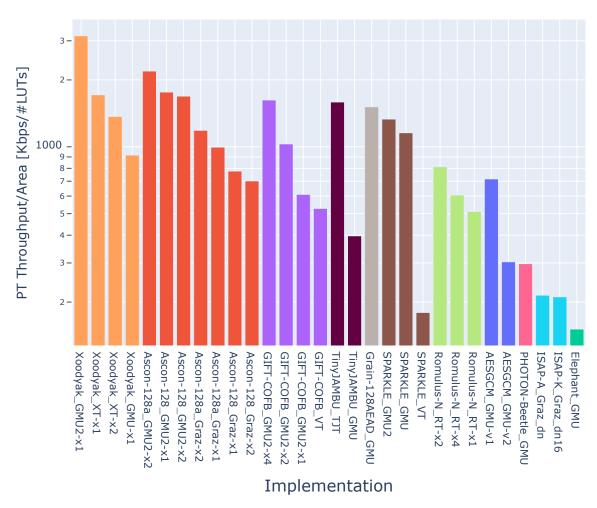

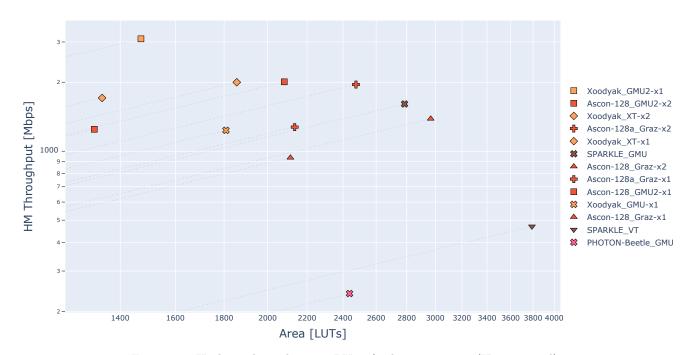

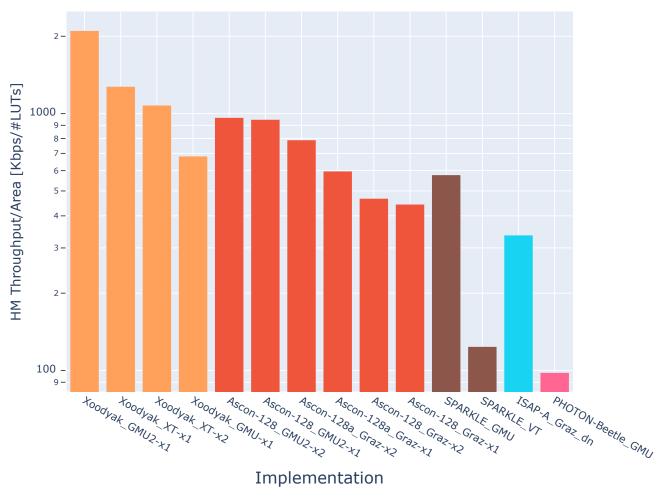

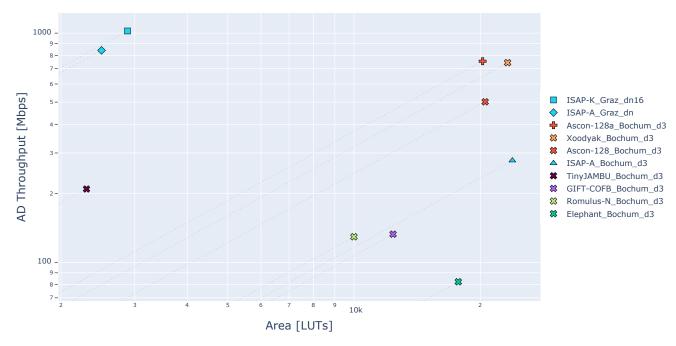

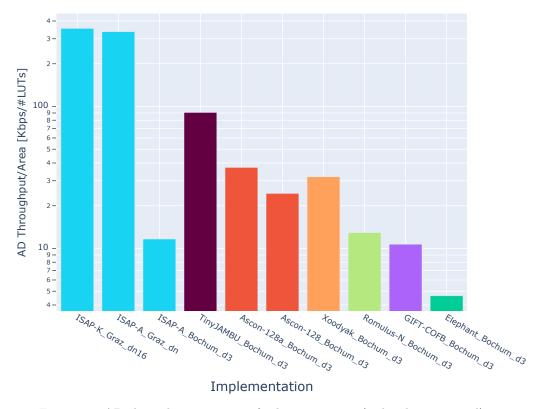

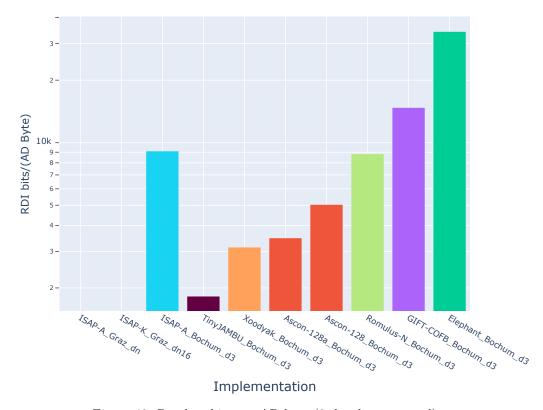

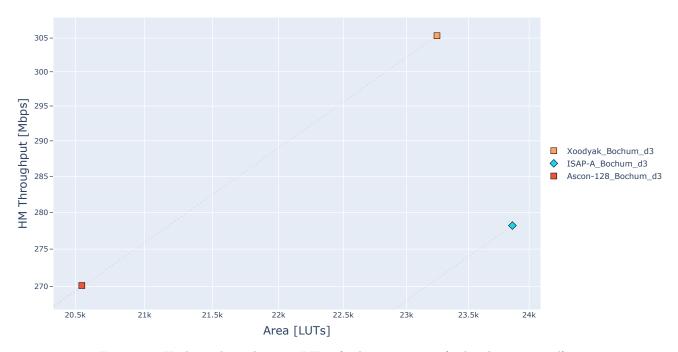

In this section, we compare the performance and area results for the protected hardware implementations. As a reference point, we also provide benchmarking results for the unprotected designs that were used as a *starting point for the protected designs* as well as the unprotected design with the *highest throughput over area ratio* for each algorithm. The results are generated for the Xilinx Artix-7 FPGA family. The target FPGA device is XC7A100T-2FTG256L, the main component of the NewAE CW305 board, which was used by many groups for the side-channel evaluation.

All evaluated designs are compatible with the GMU LWC API. The latency of major operations, expressed in clock cycles, is determined using simulation. The cycle count is determined for various lengths of plaintext, associated data, and hash input so that implementations can be compared for both short and long inputs. The area and maximum frequency were calculated using Xeda [24], a tool that automates simulation and synthesis for various FPGA and ASIC toolchains. Xeda can search for the maximum frequency for a specific target by sweeping through target frequency (through a heuristic variant of binary search) as well as different synthesis/implementation options and strategies (through evolutionary optimization). The maximum frequency is combined with the latency and input size to calculate the throughput of each design.

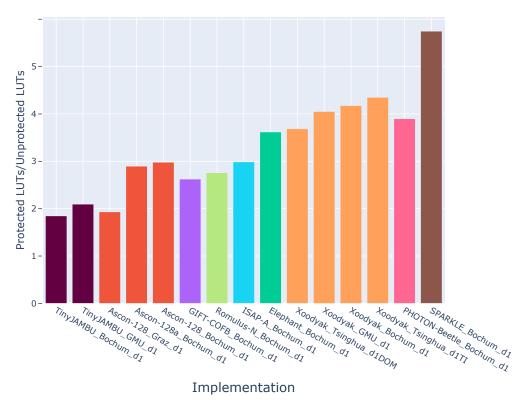

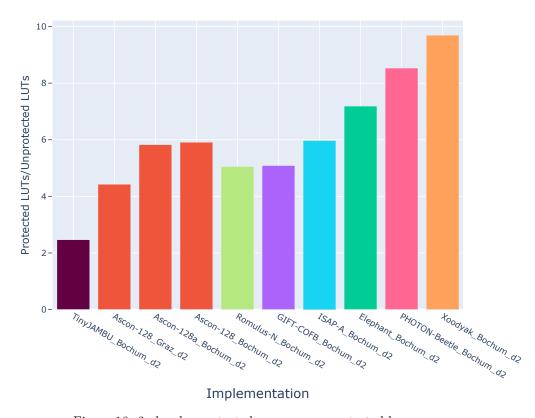

# 7.1 Protected vs. Unprotected Hardware Designs

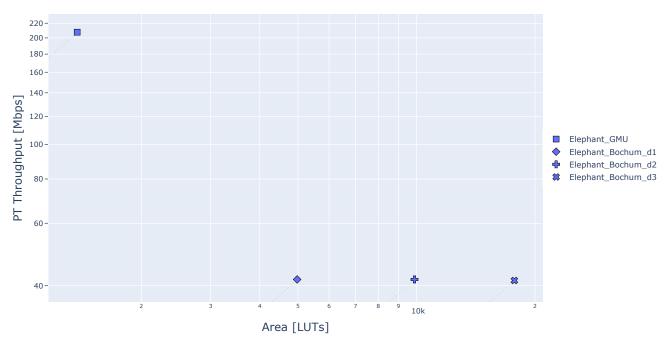

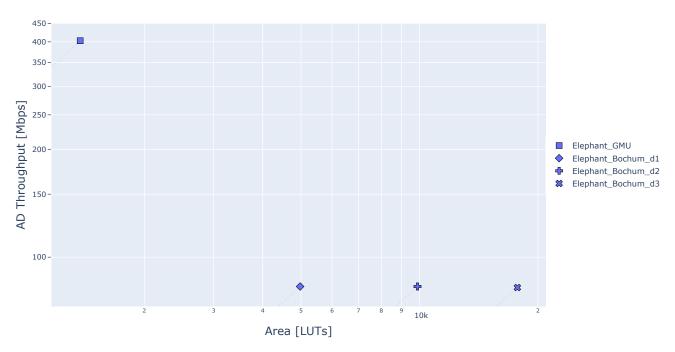

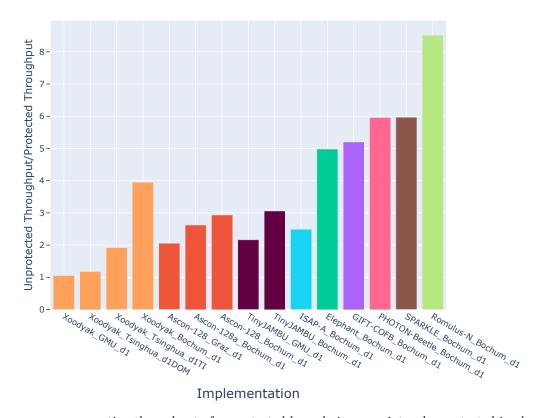

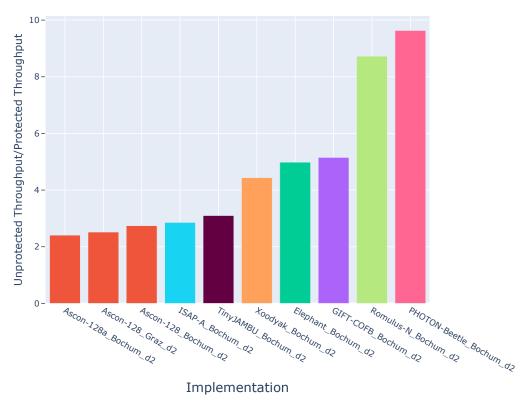

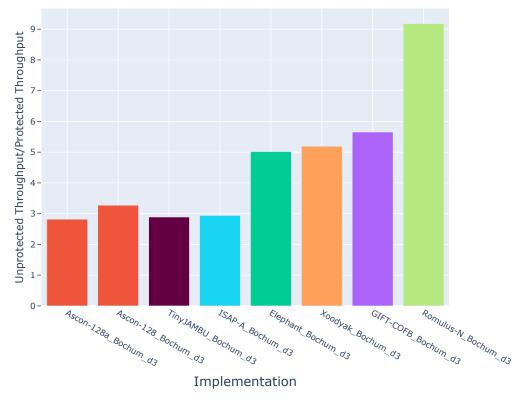

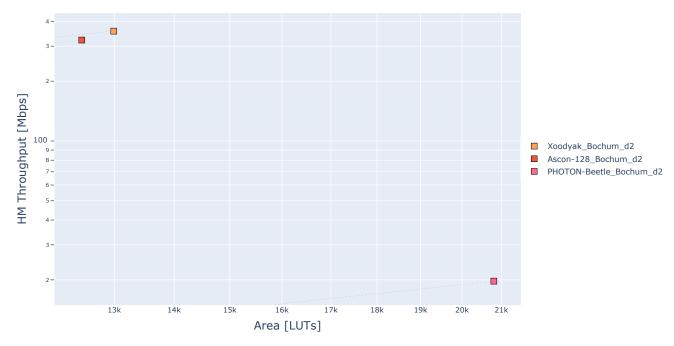

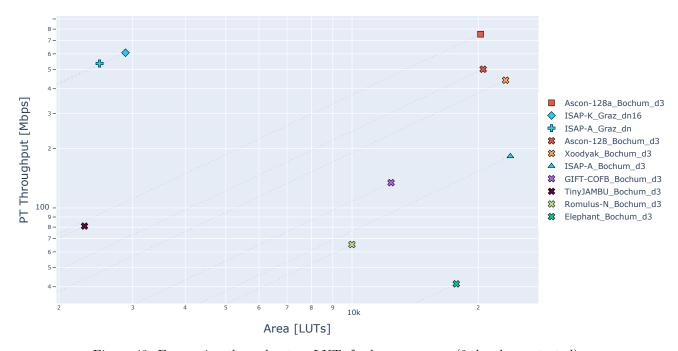

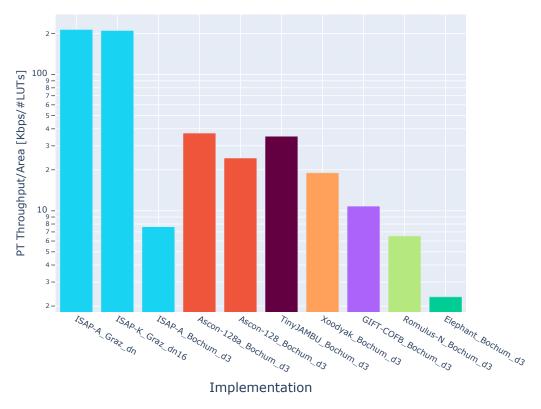

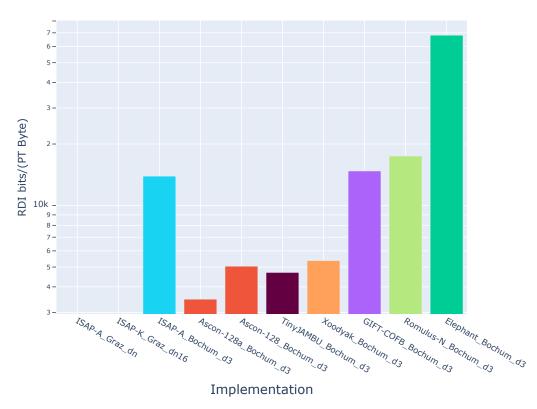

A typical dependence between the throughput vs. area characteristics of unprotected and protected designs of various orders is shown in Fig. 6. Three protected implementations of orders 1, 2, and 3, respectively, are generated with the help of AGEMA. They are all based on a single unprotected implementation, Elephant\_GMU. All protected designs operate with a very similar plaintext throughput. In the case of Elephant, this throughput is about 5 times smaller than in the case of an unprotected design. Additionally, the SCA countermeasures introduce area overhead (for area expressed in LUTs), which is dependent on the protection order. For Elephant, this overhead is about 3.6 for order 1, 7.2 for order 2, and 12.9 for order 3. Thus, the area of protected designs is almost exactly proportional to the protection order.

The same designs offer similar dependencies when used for processing ADs, as shown in Fig. 7. The only major difference is a significantly higher throughput for processing of AD vs. plaintext. The areas of all designs are exactly the same as in Fig. 7, as each design is capable of processing both plaintext and AD.

Figure 6: Elephant: Plaintext Throughput vs. Area for Unprotected and Protected Designs

Figure 7: Elephant: AD Throughput vs. Area for Unprotected and Protected Designs

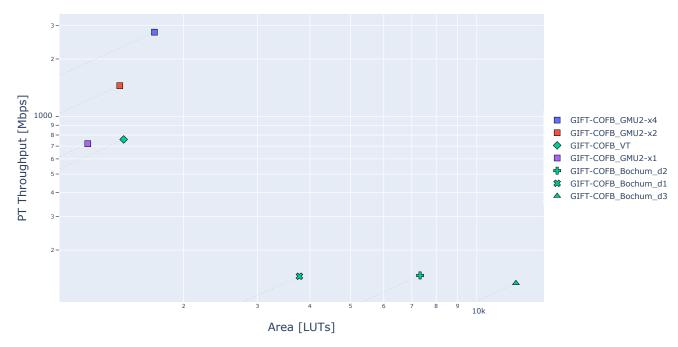

Figure 8: GIFT-COFB: Plaintext Throughput vs. Area for Unprotected and Protected Designs

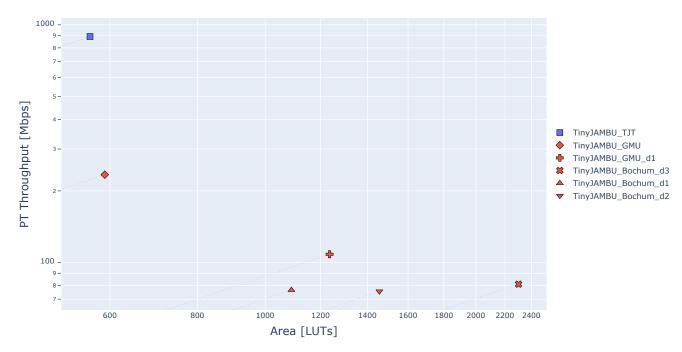

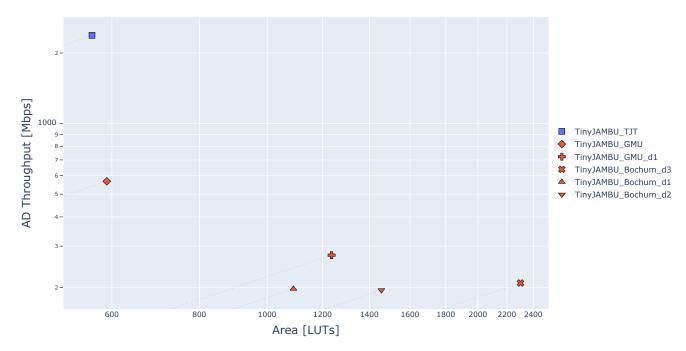

Figure 9: TinyJAMBU: Plaintext Throughput vs. Area for Unprotected and Protected Designs

Figure 10: TinyJAMBU: AD Throughput vs. Area for Unprotected and Protected Designs

The case of GIFT-COFB is illustrated in Fig. 8. The primary difference as compared to Elephant is that there are now four unprotected implementations, GIFT-COFB VT<sup>13</sup> from Virginia Tech, and GIFT-COFB GMU2-x{1,2,4}<sup>14</sup> from GMU, where GIFT-COFB\_GMU2-x2 and GIFT-COFB\_GMU2-x4 are respectively 2x and 4x unrolled versions of GIFT-COFB\_GMU2-x1. One interesting observation is that the maximum frequency of the 2x unrolled design GIFT-COFB\_GMU2-x2 is not lower than GIFT-COFB\_GMU2-x1, and unrolling results in substantially improved performance while incurring only a moderate overhead in the area. The protected designs are based on the GIFT-COFB\_VT, which is neither the fastest nor the smallest design. The primary reason for choosing a sub-optimal design as a starting point for protected designs was most likely that GIFT-COFB\_VT was written in VHDL, while GIFT-COFB\_GMU2-x{1,2,4} designs are modeled in Bluespec SystemVerilog. The choice of the underlying design was made by the Bochum group. Consequently, it is fair to compare only the overheads of designs derived from GIFT-COFB\_VT while keeping in mind that a more optimal starting point might have led to more efficient protected designs as well. The overhead in terms of throughput varies from 5.15 for order 2 to 5.65 for order 3. The small differences in throughputs of protected implementations are the result of the different clock frequencies, while the number of clock cycles remains the same. The overheads in terms of area are 2.6, 5.1, and 8.6, respectively. Similarly to the case of Elephant, the area of the protected implementation of order 2 is approximately twice as large as compared to the protected implementation of order 1. Protection order 3 leads to the increase in area by a factor larger than 3 as compared to the implementation of order 1.

The case of TinyJAMBU is somewhat similar to the case of GIFT-COFB. The protected designs are based on the less efficient of the two unprotected implementations, TinyJAMBU\_GMU. The primary difference compared to the case of GIFT-COFB is the existence of the manually developed 1st-order protected implementation, TinyJAMBU\_GMU\_d1. As expected, the 1st-order manually protected design, TinyJAMBU\_GMU\_d1, is faster than the automatically generated design of the same order, TinyJAMBU\_Bochum\_d1. The throughput ratio is about 1.40. However, contrary to expectations, the manually developed design has a larger area. The area ratio is about 1.13. Thus, overall, the manual implementation is still more efficient in terms of the throughput-to-area ratio.

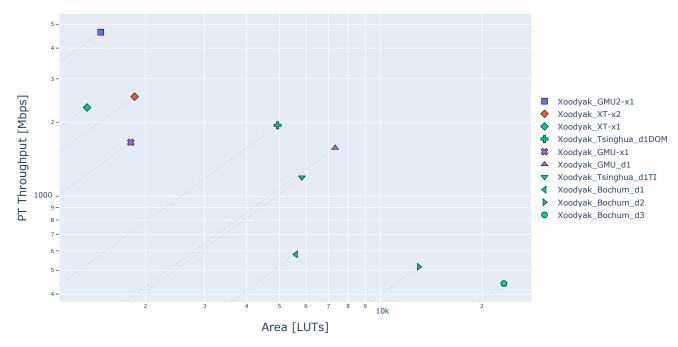

The case of Xoodyak, shown in Fig. 11 is exceptional, as this candidate has three manually developed protected implementations of order 1:

1. Xoodyak\_Tsinghua\_d1DOM – developed by the group from Tsinghua University using the Domain Oriented Masking (DOM) method

$<sup>^{13} \</sup>verb|https://github.com/vtsal/gift_cofb_lwc_v2|$

<sup>14</sup>https://github.com/kammoh/bluelight

Figure 11: Xoodyak: Plaintext Throughput vs. Area for Unprotected and Protected Designs

Figure 12: Xoodyak: Hashing Throughput vs. Area for Unprotected and Protected Designs

- 2. Xoodyak\_Tsinghua\_d1TI developed by the group from Tsinghua University using the Threshold Implementation (TI) method, and

- 3. Xoodyak\_GMU\_d1 developed by the group from George Mason University using the Domain Oriented Masking method.

All of these implementations offer only first-order protection. Additionally, there exist semi-automatically generated implementations of orders 1, 2, and 3, respectively, developed by the group from Ruhr University Bochum. The protected designs developed by Tsinghua University and Ruhr University Bochum used as a starting point the unprotected implementation developed by the Xoodyak Team, Xoodyak\_XT-x1, based on the basic iterative architecture (a.k.a. the architecture with the unrolling factor x1). The protected design developed by George Mason University, used as a starting point a folded design, Xoodyak\_GMU-x1, developed by the same team.

Apart from the mentioned above implementations, Fig. 11 also shows results for two fastest unprotected implementations:  $Xoodyak\_GMU2-x1$  developed using Bluespec SystemVerilog, and  $Xoodyak\_XT-x2$  – a two times unrolled variant of  $Xoodyak\_XT-x1$ .

Both manually developed protected implementations, generated using DOM, produced a relatively small throughput overhead. The slowdown for the design from Tsinghua University, Xoodyak\_Tsinghua\_d1DOM was about 15% as compared to the corresponding unprotected design. The slowdown for the design from George Mason University, Xoodyak\_GMU\_d1, was only about 5%. The threshold implementation from Tsinghua University, Xoodyak\_Tsinghua\_d1TI, was both slower and larger than the corresponding DOM implementation, Xoodyak\_Tsinghua\_d1DOM.

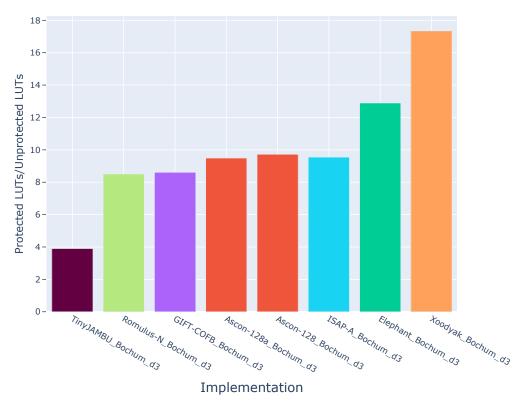

Overall, Xoodyak\_Tsinghua\_d1DOM is the best-protected implementation of Xoodyak, both in terms of speed and area. It outperforms the semi-automatically created design from Bochum, Xoodyak\_Bochum\_d1, by a factor of about 3.3 in terms of throughput. It is also about 12% smaller in terms of the number of LUTs. The first-order protected implementations use between 3.7 and 4.35 more LUTs than the corresponding unprotected designs. The second-order implementation has an area overhead of about 9.7, and the third order 17.3.

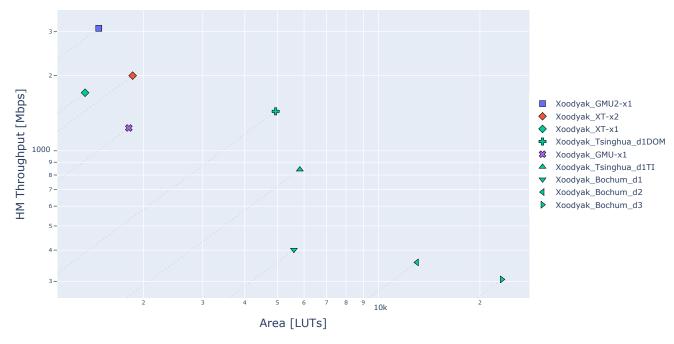

The performance for hashing, illustrated in Fig. 12, is almost the same. The primary differences include smaller absolute values of throughput and no support for hashing in Xoodyak\_GMU\_d1. On the other hand, all areas are identical, as the designs supporting hashing use the same circuits for processing Plaintext, AD, and Hash Messages.

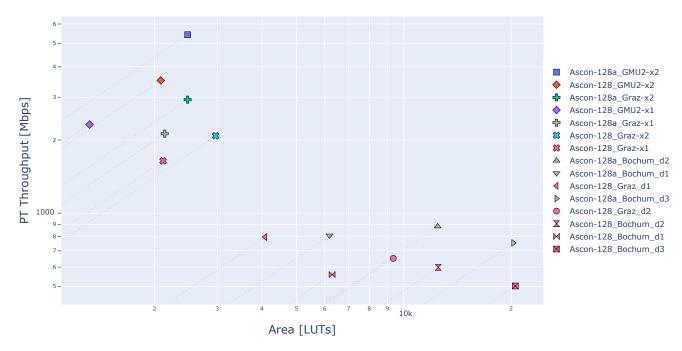

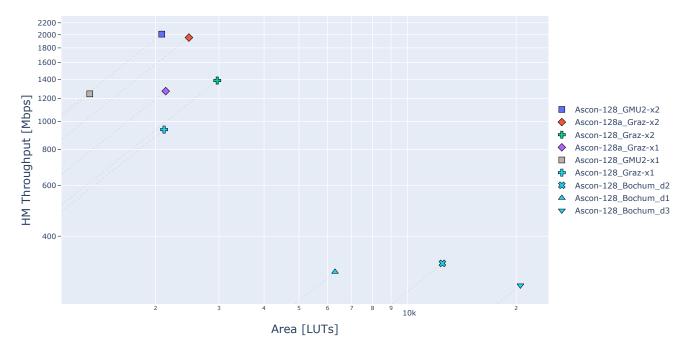

The case of Ascon, illustrated in Figs. 13 and 14 is, no doubt, the most complicated of all candidates. First, Ascon has two variants for authenticated encryption – Ascon-128 and Ascon-128a. They differ in terms of the data block size (64 bits for Ascon-128 and 128 bits for Ascon-128a). They also have a different number of rounds in the permutation used to process AD, plaintext, and ciphertext. This number of rounds is 6 for Ascon-128 and 8 for Ascon-128a. Ascon also has two different variants of a hash function: Ascon-Hash and Ascon-Hasha. They both use the same message block size of 64 bits. They differ in terms of the number of permutation rounds in the Absorb Message and Squeeze Hash phases. Ascon-Hash has 12 rounds, and Ascon-Hasha 8 rounds. In hardware, where the entire block is typically processed in parallel, and the rounds are executed sequentially, Ascon-128a and Ascon-Hasha are typically faster. Ascon-128 and Ascon-Hash are more conservative designs and are the primary recommendations of Ascon's authors.

Ascon has the following protected implementations:

- 1. Ascon-128\_Graz\_d1 and Ascon-128\_Graz\_d2 two implementations of Ascon-128, of order 1 and 2, respectively, developed by the Ascon Team manually, using the Domain Oriented Masking (DOM) method. The starting point was the unprotected implementation from the same team Ascon-128\_Graz-x1.

- 2. Ascon-128\_Bochum\_d{1,2,3} implementations of Ascon-128 of orders 1, 2, and 3, generated semi-automatically with the help of AGEMA, using Ascon-128\_Graz-x1 as an underlying unprotected implementation, and

- 3. Ascon-128a\_Bochum\_d{1,2,3} implementations of Ascon-128a of orders 1, 2, and 3, generated semi-automatically with the help of AGEMA, using Ascon-128a\_Graz-x1 as an underlying unprotected implementation.

Each unprotected implementation from Graz University has a corresponding two-times unrolled implementation from the same group, with the name ending with x2. The two-times unrolled architectures are faster but bigger than the basic architectures. Because of the increased area, they were not used as a basis for any protected implementations.

The two fastest unprotected designs were developed by the GMU group. Ascon-128a\_GMU<sup>15</sup> implements Ascon-128a. Ascon-128\_GMU2-x1<sup>16</sup> and Ascon-128\_GMU2-x2<sup>16</sup> implement Ascon-128 using the basic iterative and 2x unrolled architectures, respectively. All of them were modeled using Bluespec SystemVerilog.

Corresponding implementations of Ascon-128 and Ascon-128a developed by the Graz Team<sup>17</sup> (Ascon-128\_Graz-x1 and Ascon-128a\_Graz-x1) and generated semi-automatically by the Bochum Team (e.g., Ascon-128\_Bochum\_d1 and Ascon-128a\_Bochum\_d1) have the same areas. Within each pair, the implementation of Ascon-128a is approximately x1.3 faster than the implementation of Ascon-128 for unprotected designs and between 1.45 and 1.50 for protected designs.

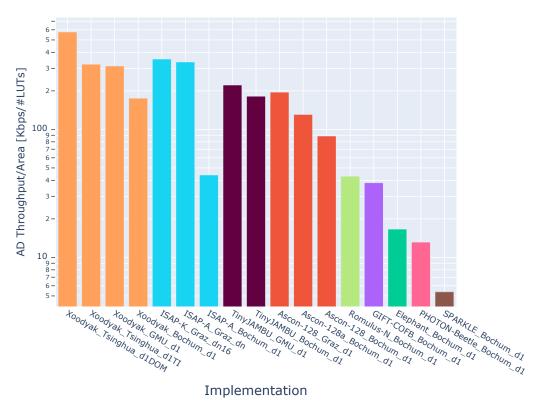

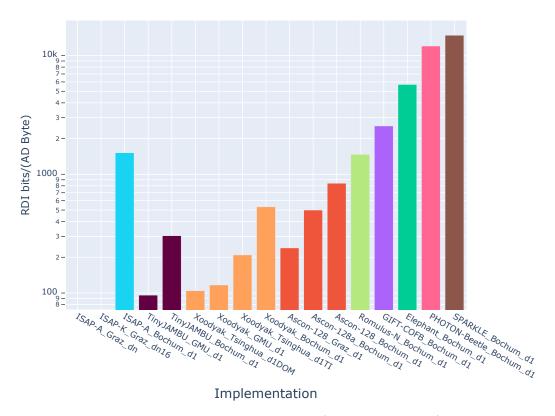

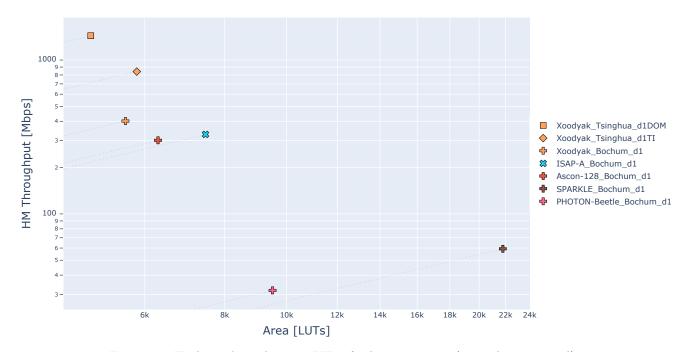

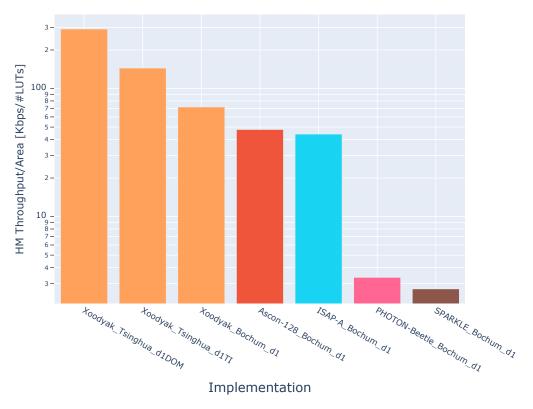

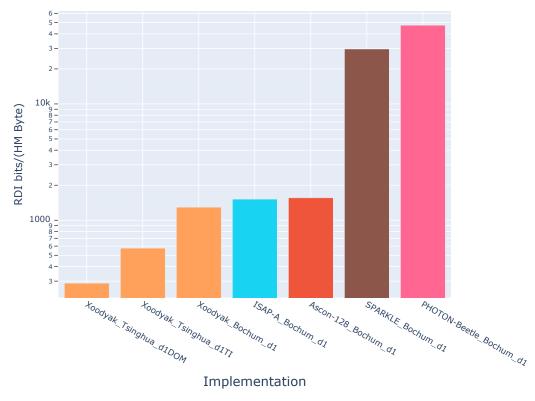

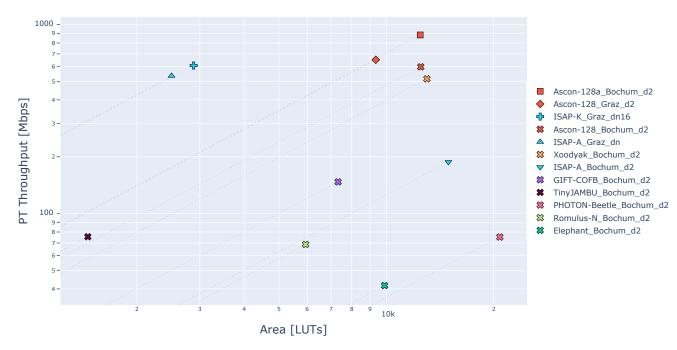

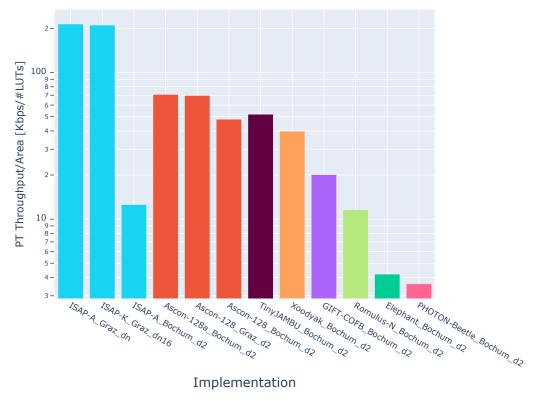

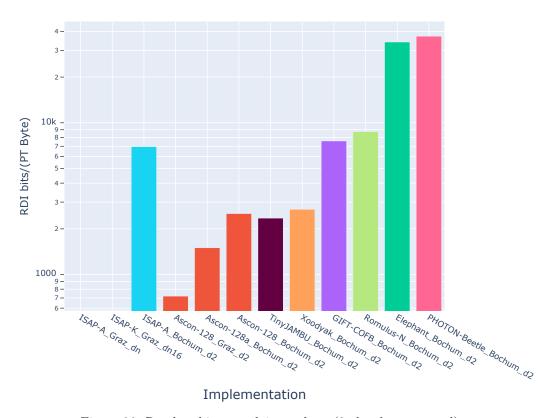

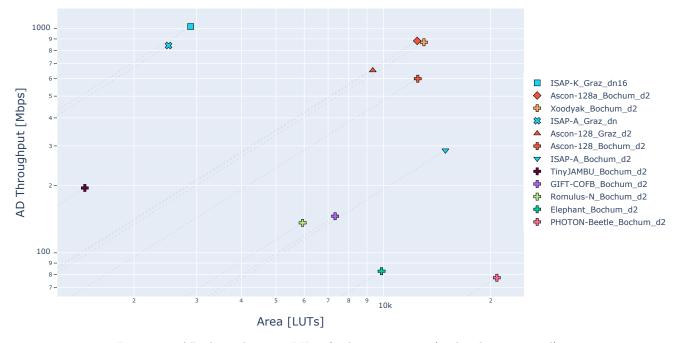

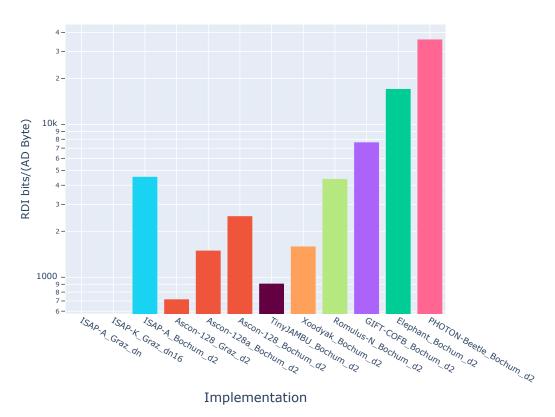

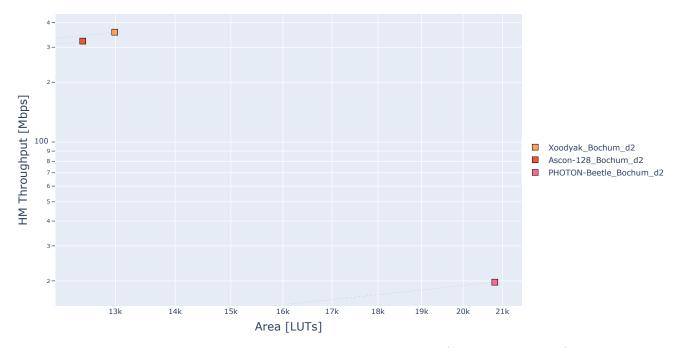

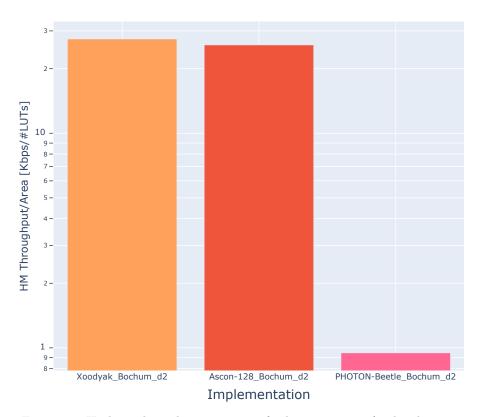

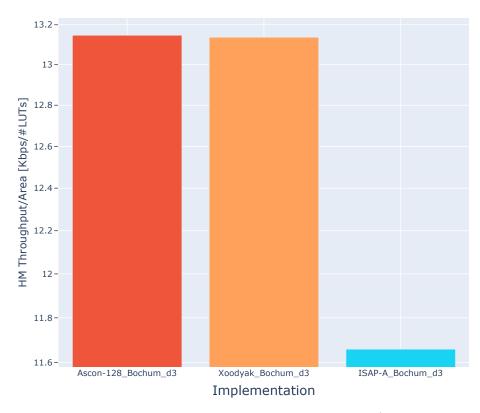

The manually developed first-order protected implementation of Ascon-128 is 43% faster and 34% smaller than the corresponding semi-automatically generated design. The manually developed second-order protected implementation of Ascon-128 is about 9% faster and 25% smaller than the corresponding semi-automatically generated design.