# Towards Generic MPC Compilers via Variable Instruction Set Architectures (VISAs)

Yibin Yang\* Stanislav Peceny<sup>†</sup> David Heath<sup>‡</sup> Vladimir Kolesnikov<sup>§</sup>

August 20, 2023

#### Abstract

In MPC, we usually represent programs as circuits. This is a poor fit for programs that use complex control flow, as it is costly to compile control flow to circuits. This motivated prior work to emulate CPUs inside MPC. Emulated CPUs can run complex programs, but they introduce high overhead due to the need to evaluate not just the program, but also the machinery of the CPU, including fetching, decoding, and executing instructions, accessing RAM, etc.

Thus, both circuits and CPU emulation seem a poor fit for general MPC. The former cannot scale to arbitrary programs; the latter incurs high per-operation overhead.

We propose variable instruction set architectures (VISAs), an approach that inherits the best features of both circuits and CPU emulation. Unlike a CPU, a VISA machine repeatedly executes entire program fragments, not individual instructions. By considering larger building blocks, we avoid most of the machinery associated with CPU emulation: we directly handle each fragment as a circuit.

We instantiated a VISA machine via garbled circuits (GC), yielding constant-round 2PC for arbitrary assembly programs. We use improved branching (Stacked Garbling, Heath and Kolesnikov, Crypto 2020) and recent Garbled RAM (GRAM) (Heath et al., Eurocrypt 2022). Composing these securely and efficiently is intricate, and is one of our main contributions.

We implemented our approach and ran it on common programs, including Dijkstra's and Knuth-Morris-Pratt. Our 2PC VISA machine executes assembly instructions at 300Hz to 4000Hz, depending on the target program. We significantly outperform the state-of-the-art CPU-based approach (Wang et al., ESORICS 2016, whose tool we re-benchmarked on our setup). We run in constant rounds, use  $6\times$  less bandwidth, and run more than  $40\times$  faster on a low-latency network. With 50ms (resp. 100ms) latency, we are  $898\times$  (resp.  $1585\times$ ) faster on the same setup.

While our focus is MPC, the VISA model also benefits CPU-emulation-based Zero-Knowledge proof compilers, such as ZEE and EZEE (Heath et al., Oakland'21 and Yang et al., EuroS&P'22).

**Keywords:** MPC; General Purpose Programs; Garbled Circuits.

<sup>\*</sup>Georgia Institute of Technology, yyang811@gatech.edu.

<sup>&</sup>lt;sup>†</sup>Georgia Institute of Technology, stan.peceny@gatech.edu.

<sup>&</sup>lt;sup>‡</sup>University of Illinois Urbana-Champaign, daheath@illinois.edu.

<sup>§</sup>Georgia Institute of Technology, kolesnikov@gatech.edu

# Contents

| 1            | Introduction                                           | 1   |

|--------------|--------------------------------------------------------|-----|

|              | 1.1 Case study: Dijkstra's algorithm                   | 2   |

|              | 1.2 Contribution                                       | 4   |

| 2            | Overview                                               | F   |

| 4            |                                                        | 6   |

|              | 2.2 VISA Advantages                                    |     |

|              | 2.3 VISA Technical Challenges and Solutions            |     |

|              | 2.5 VISA Technical Chahenges and Solutions             | '   |

| 3            | Related Work                                           | 8   |

| 4            | Preliminaries                                          | 10  |

| -            | 4.1 Garbled RAM                                        |     |

|              | 4.2 Stacked Garbling (SGC)                             |     |

|              | 4.3 Cryptographic Assumptions                          |     |

|              | 1.0 Cryptograpme rissumptions                          | 10  |

| 5            | Our VISA                                               | 11  |

|              | 5.1 Base ISA                                           | 11  |

|              | 5.2 Fragments                                          | 13  |

|              | 5.3 Memory Hierarchy                                   |     |

|              | 5.4 Fragment Generation                                |     |

|              |                                                        |     |

| 6            |                                                        | 15  |

|              | 6.1 SGC with GRAM                                      |     |

|              | 6.2 Our Scheme: Formalization and Theorems             | 16  |

| _            |                                                        |     |

| 7            |                                                        | 18  |

|              | 7.1 Implementation and Testing Environment             |     |

|              | 7.2 Benchmarks and Metrics                             |     |

|              | 7.3 Overall Improvement                                |     |

|              | 7.4 Performance Breakdown and Discussion               |     |

|              | 7.4.1 Breakdown of Wall-Clock Time                     |     |

|              | 7.4.2 SGC Savings                                      |     |

|              | 7.4.3 Communication Rounds and Latency Impact          |     |

|              | 7.4.4 Active Set Sizes                                 |     |

|              | 7.4.5 Comparison with Straight-Line Circuit Evaluation | 22  |

| Δ            | Assembly Benchmarks                                    | 27  |

| 1.           | ·                                                      | 27  |

|              |                                                        | 27  |

|              |                                                        | 29  |

|              | 11.0 11.11                                             | ت ∠ |

| $\mathbf{B}$ |                                                        | 30  |

|              |                                                        | 30  |

|              | B.2 Correctness/Security Definitions and Proofs        | 30  |

## 1 Introduction

Secure multi-party computation (MPC) allows mutually untrusting parties to execute programs on their private inputs while revealing only the output. MPC has become relevant in academia and industry. It has been commercially deployed in online auctions, electronic voting, financial technology, and has found many use cases in medicine, privacy-preserving machine learning, and distributed databases.

Typically in MPC, we encode programs as circuits. While any bounded program can be compiled to a circuit, the compiled circuit is often *much* larger than the source program. Real world programs (1) access large arrays of data and (2) use complex control flow. Compiling these two program features often results in huge circuits, and MPC cost scales with the size of the circuit. If we wish to enable secure computation of real-world programs, we must circumvent the cost imposed by compiling these features to circuits.

While the issue of array access can be resolved via oblivious RAM (ORAM) [GO96] or garbled RAM (GRAM) [LO13], complex control flow has gone largely unaddressed.

Straight-line execution Indeed, most existing MPC tools "solve" the control flow problem by disallowing complex control flow. Most existing MPC toolchains require that the programmer hand-annotate each loop with a hard-coded upper bound on the number of loop iterations [HHNZ19]. With these annotations, the program becomes a simple straight-line program, compatible with the circuit model. A compiler can now unroll each loop precisely the specified number of times, then compile each iteration into gates.

This approach is problematic. At best, annotating programs is an annoyance. At worst, hard-coded loop bounds *ruin performance*, since we must execute each loop iteration, even if the loop should terminate early. Many programs are awkward to write and will have wildly wrong asymptotic complexity. In other words, the programmer is left with an incomplete programming environment where she cannot write every program she might need.

**CPU Emulation** There is another approach that addresses the control flow problem. Instead of evaluating the program directly, use MPC to *emulate a CPU*, then run the program on that CPU. To achieve this, we must fully emulate a CPU, including its program counter, register file, ALU, and main memory. At each step, the CPU will look up and decode the next instruction, load/store registers, run arithmetic operations, and read/write main memory. In this way, the parties can securely evaluate one instruction at a time.

CPU emulation can securely evaluate arbitrary programs, but at a cost. When we emulate a CPU, we pay to evaluate not just the program, but also the machinery inside the CPU. In comparison to straight-line execution, CPU emulation incurs *very* high per-operation cost. In straight-line execution, the arguments to each program operation are decided statically; in a CPU, the arguments are *dynamic* and must be moved into and out of the register file. Similarly, in straight-line execution, the operation to be performed at each step is decided statically; in a CPU, we must look up the next instruction from a large memory, then conditionally dispatch over each operation in the ISA. In short, while CPU emulation solves the control flow problem, it introduces high overhead.

```

1

#define MAX 100

2

#define MAX_INT 1000000

3

int dijkstra(int *a, int *b) {

4

int n = a[0];

5

int e = a[1];

6

int * node = a + 2;

7

int * edge = a + 2 + 101;

8

int * weight = a + 2 + 401;

9

int vis[MAX];

10

int dis[MAX];

11

dis[b[0]] = 0;

12

int i = 0;

13

while (i < n) {

14

int bestj = -1, bestdis = MAX_INT;

15

int j = 0;

16

while (j < n) {

17

if( vis[j] == 0 && dis[j] < bestdis ) {</pre>

18

bestj = j;

19

bestdis = dis[j];

}

20

21

j++;

22

23

vis[bestj] = 1;

j = node[bestj];

24

25

int bound = node[bestj+1];

26

while (j < bound) {</pre>

27

int newDis = bestdis + weight[j];

28

if(newDis < dis[edge[j]])</pre>

29

dis[edge[j]] = newDis;

30

31

}

32

i++;

33

}

34

return dis[b[1]];

35

}

```

Figure 1: Dijkstra's algorithm written in C. Each vertical line on the left denotes a contiguous string of instructions that are grouped into a fragment. I.e., this program has seven fragments.

## 1.1 Case study: Dijkstra's algorithm

We illustrate the challenge of handling general programs in MPC. Consider Dijkstra's algorithm (Figure 1).

<sup>&</sup>lt;sup>1</sup>For performance, Dijkstra's algorithm may be implemented with a *priority queue* containing partial solutions sorted by distance from the start node. Standard Dijkstra is based on a simple array, as is also done in [WGMK16]. We use standard Dijkstra for illustration and direct performance comparison with [WGMK16].

Dijkstra's is a graph algorithm that computes the shortest path between a source node  $(\mathfrak{b}[0])$  and a target node  $(\mathfrak{b}[1])$ . Assume that the graph, the source, and the target are private inputs (e.g., secret-shared between the parties). Both straight-line execution and CPU emulation struggle with this small program.

Straight-line execution Straight-line execution-based tools will generally achieve the wrong cost for the algorithm. Consider a graph (V, E). Even if we suppose that |V| and |E| are public, this simple program presents a challenge to straight-line execution. The problem is that the loop on lines 26–31 dynamically accesses each edge from a graph node. The number of edges from this node is private, so the loop must be unrolled |E| times to accommodate the maximum possible number of edges. In a cleartext execution of Dijkstra's, this inner loop will in total iterate only O(|E|) times; in this unrolled version, the inner loop will iterate  $O(|E| \cdot |V|)$  times.

Even worse, suppose that Dijkstra's is not the full program, but rather is a subprocedure of a larger program. Here, |V| and |E| are likely dynamic and should be kept secret. In this case, straight-line execution-based tools must pessimistically assume that |V| and |E| are maximal, ruining performance.

ObliVM [LWN<sup>+</sup>15] showed that for Dijkstra's algorithm and if |V| and |E| are public, the straight-line approach can reclaim the loop asymptotics via *loop coalescing*. Using loop coalescing, we can flatten the nested loop on lines 13–33 into a single loop with an internal conditional. Then, the number of iterations of this top level loop is a function of |V| and |E|, so it is possible to properly bound the loop. See further discussion in Section 3.

While loop coalescing can solve this particular problem, it places a significant burden on the programmer: the programmer must now reason about and properly specify upper bounds on coalesced loops. This may be expensive if |V| and |E| are secret, such as if Dijkstra's is nested inside another data-dependent loop, requiring costly further coalescing or excessive padding. This syntactic transformation produces expensive code that is difficult to further optimize.

**CPU emulation** CPU emulation correctly implements Dijkstra's asymptotics<sup>2</sup>, but incurs significant concrete cost.

The state-of-the-art CPU emulator implements a sufficient subset of the MIPS instruction set [WGMK16] to handle Dijkstra's. This CPU stores the compiled assembly program, the register file, and the main memory in three separate RAMs. [WGMK16] implements RAM using either Circuit ORAM [WCS15] or trivial linear scans, depending on the size of the needed array. Their CPU proceeds by continually fetching and executing instructions.

Storing the program in RAM and applying the fetch-and-execute paradigm discards all useful static information, some of which [WGMK16] manually reclaims by implementing various heuristics, such as periodic (rather than per-instruction) RAM access. Even applying this heuristic, their number of main memory accesses is suboptimal. Further, they must always access smaller memories to fetch instructions and to read/write registers. Their ALU decodes the instruction and conditionally executes the operation for each instruction type that is statically possible at a given step. As a result, each CPU step is a large circuit that often improves on the circuit-based computation only for problem instances where MPC is impractical.

<sup>&</sup>lt;sup>2</sup>To be pedantic, the CPU emulation approach achieves the correct asymptotics modulo polylog factors imposed by ORAM/GRAM. Neither CPU emulation nor straight-line execution, nor indeed our approach, can avoid polylog overhead from ORAM/GRAM [LN18].

Our approach, discussed next, systematically optimizes away many of the principal inefficiencies of [WGMK16] and results in significantly improved performance. For instance, for Dijkstra's with 100 nodes and 300 edges and when run on the *same* setup, our VISA machine uses  $5.8\times$  fewer RAM accesses, consumes  $7.3\times$  less bandwidth, and runs  $44.9\times$  faster. We are  $1585\times$  faster on a 100ms-latency network.

**Our Solution: VISA Machines** The state of the art presents a dichotomy: CPU emulation or straight-line programs.

In this work, we suggest and explore a hybrid approach to handling arbitrary programs inside MPC. Our *variable instruction set architecture machine*, or VISA machine, handles programs with arbitrary control flow, but avoids most of the overhead of the CPU emulation approach. It uses the statically available context to optimize the scope (and hence the cost) of each execution step.

In short, a VISA machine is distinct from a CPU in that it does not repeatedly execute instructions, but rather repeatedly executes entire *fragments* of the source program. Each fragment is an arbitrarily long straight-line portion of the source program text. The basic advantage of this is that we can cheaply handle each fragment as a circuit. While we still need CPU-like machinery to coordinate the execution of the fragments and ensure privacy, the amount of needed machinery is substantially reduced.

#### 1.2 Contribution

We propose variable instruction set architectures, a basic approach to evaluating arbitrary programs inside MPC. We believe that VISAs are the sensible approach to executing arbitrary programs in MPC. VISAs do not limit the programmer to straight-line programs, and they do not incur the high overhead of a basic CPU. A VISA adapts to the target program of interest, an appropriate choice for MPC where we generally assume that the parties agree on a program.

In more detail, we:

- Introduce and motivate the VISA model.

- Construct a complete VISA-based 2PC toolchain for assembly programs. Our toolchain is implemented via garbled circuits (GC).

- Resolve technical issues needed to combine core components of a GC-based VISA machine: GC conditional branching [HK20a, HK21b] and Garbled RAM [HKO21].

- Formalize our instantiation as a *garbling scheme* [BHR12] and prove the resulting formalism secure. Our garbling scheme securely evaluates arbitrary assembly programs written in our ISA. Using garbling schemes as the underlying mechanism has two key benefits.

- First, we dramatically decrease the number of communication rounds, resulting in orders of magnitude improvement (see Section 7.4.3). Prior work [WGMK16, Kel17] used tens of rounds per CPU step, while we require one message plus an OT for the entire 2PC.

- Second, our technique can be elevated to the covert, PVC, and malicious models using standard techniques.

- We implemented VISA machine including, significantly, the first implementation of Garbled RAM [HKO21].

- Experimentally evaluate performance of our toolchain. We ran our VISA machine on a number of assembly benchmarks, including Dijkstra's, Knuth-Morris-Pratt, and a private set intersection benchmark from [WGMK16]. Our results indicate significant improvement over the prior best approach to arbitrary assembly programs [WGMK16]: we run in constant rounds, use 4–7× less bandwidth, use 5–10× fewer RAM accesses, and run 40–70× faster (up to 1585× with 100ms latency), yielding a machine that executes assembly instructions at 300–4000Hz. We also experimentally show our work, as expected, overtakes circuit-based 2PC (EMP [WMK16]) even for small programs with non-trivial control flow.

- We plan to open source and maintain a cleaned version of our prototype toolchain.

- While our focus is on MPC, the VISA model also directly applies to CPU-emulation-based Zero-Knowledge Proof (ZKP) compilers, such as ZEE and EZEE [HYDK21, YHKD22]. Indeed, they face similar problems of more efficient CPU design (e.g., fragmentation and stacking), ZK ORAM integration with branching, etc., and the VISA approach is similarly beneficial to ZKP compiler work. We leave specific instantiations of ZKP VISA as exciting future work.

Recent breakthrough GC and MPC improvements on free branching [HK20a, HK21b, HKP20, HKP21] and efficient GRAM [HKO21] removed fundamental technical roadblocks needed to move away from straight-line circuit execution. We believe that our hybrid approach – contextual fragment-based execution engines – will underlie the next generation of 2PC and MPC toolchains. This paper initiates this direction and sets the stage for future cryptographic and interdisciplinary work that will likely involve programming language, static analysis, and compiler techniques, and that will interface with high-level programming languages.

## 2 Overview

In this section we at a high level introduce our model and explain the fundamental benefits of our approach. We then introduce lower-level technical challenges and briefly outline our approach to solving them.

Our basic observation is that CPU emulation is a blunt generic mechanism: CPUs in cleartext machines are static devices that can execute *each* step of *any* program. But in MPC, the program is public, and there is no need to use a fixed generic set of instructions. Instead, we can derive our machine's 'instruction types', which we call *fragments*, from the target program itself.

Each fragment can be arbitrarily large and complex, so long as it does not contain datadependent loops. We can generate custom circuitry tailored to each fragment, avoiding the need to mechanistically execute the fragment one instruction at a time. Thus, once our machine enters a fragment, we pay essentially no overhead to execute that fragment. In this sense, we obtain the benefit of straight-line execution.

At the same time, our machine dynamically dispatches over the fragments, so we can handle all possible execution paths. In this sense, we obtain the benefit of CPU emulation.

Our execution engine does not necessarily need to dynamically dispatch over each program fragment at each step. At each step it is sufficient to only guarantee execution of fragments that may occur at *this* step. In many useful programs, this *active set* is *much* smaller and consists of cheaper fragments than the full set.

Program fragments are generated by a compiler. There are many choices for how to fragment a program, and good fragmentation is crucial to performance. We discuss related trade-offs (see Section 5.4).

#### 2.1 Notation

Our execution engine repeatedly conditionally dispatches over varying sets of fragments chosen from the target program. We call the specification of a machine that operates this way a *variable instruction set architecture* (VISA). A *VISA machine* instantiates a VISA specification. Our VISA machine, which we call GAR, is implemented via GC; of course, one could implement a VISA machine from different primitives, such as a secret-sharing-based protocol and off-the-shelf ORAM.

At each step i, a VISA machine can execute any fragment in the *active set* of step i. We compose each fragment from many *base instructions* in the program text. Note we thus consider two kinds of instructions: *base* instructions are typical low-level assembly instructions, whereas *fragments* are the instructions of a VISA and are composed from multiple base instructions. Fragments are automatically chosen by a type of compiler that we call a *fragmentation strategy*; our GAR construction includes a built-in fragmentation strategy.

In the remainder of this section, we explain and motivate VISA machines in more detail. We explain our advantages by referring to Dijkstra's algorithm (Figure 1).

## 2.2 VISA Advantages

VISA machines do not repeatedly execute instructions, but rather repeatedly execute entire *frag*ments of the source program. This leads to several important advantages:

**Free register file** As each fragment is a straight-line piece of code, we do not need to dynamically store and access local variables from a register file. Instead, like the straight-line approach, a VISA machine routes arguments to operations directly and without cryptographic cost.

We still pay to route the content of the register file between fragments, but within a single fragment, the register file is free.

Example 1. Consider line 18 of Dijkstra's (Figure 1). Under CPU emulation, this simple assignment requires reading j from and writing best j to the register file. In practice, these would be implemented by linear scans of a modest array. Linear scans are expensive. As a reference point, suppose the register file holds 16 32-bit registers. Using state-of-the-art GC, each linear scan of this register file costs  $\approx 16KB$  of communication. In the CPU emulation approach, this cost is paid multiple times per CPU cycle. In our VISA machine, this overhead is erased: to handle line 18 the parties may simply agree to name certain wires in the fragment circuit best j.

No instruction memory Programs execute fewer fragments than they do base instructions. Thus, when the VISA machine dynamically decides which fragment to execute next, the space of choices is smaller. This means that the VISA machine does not need to store fragments in an instruction memory. Instead, we conditionally dispatch over an integer that indicates which of the small number of statically known fragments should be executed next. This eliminates many usages of ORAM/GRAM.

**Example 2.** In our ISA, Dijkstra's has 56 instructions<sup>3</sup> but only 7 fragments. (Our actual fragmentation is more nuanced; see Section 5.4.) At each step, we conditionally execute only those fragments that are possible. As a simple example, on the first cycle of Dijkstra's, our VISA machine unconditionally executes the fragment on lines 4–12, since this is statically the only fragment possible. We track the fragments that are possible at each step by tracing the target program's control flow graph.

Fewer conditional choices Each fragment implements a larger portion of the overall execution than does each instruction. This is significant because there is overhead associated with conditionally executing code inside MPC, whether classically or by stacking [HK20a]. Since we execute fewer fragments than CPU emulation executes instructions, we make fewer conditional decisions, and hence pay the overhead of conditional branching fewer times. With SGC, this advantage manifests in the fact that we need fewer SGC multiplexer gadgets [HK20a, HK21b]. Importantly, for small branches, these gadgets dominate the cost of SGC.

**Example 3.** Running Dijkstra's with |V| = 100 and |E| = 300 involves executing 198,814 instructions, and hence making 198,814 conditional decisions. In contrast, we need only execute 21,800 fragments, and hence make only 21,800 conditional decisions.

Fewer data RAM accesses Since each fragment is static, we know precisely how many times each fragment must move data to/from main memory. This allows a VISA machine to access memory less often than a CPU, since in a CPU it is possible that each instruction is a memory access.

**Example 4.** Consider again line 18 of Dijkstra's. Under CPU emulation, the CPU cannot statically deduce that the current instruction is not a RAM access, so when emulating line 18, it must perform a RAM access. Our VISA machine eliminates this access.

The sum advantage of our approach as compared to CPU emulation is well illustrated by again considering line 18 of Dijkstra's. Under CPU emulation, this instruction will involve fetching and decoding the instruction, linearly scanning the register file multiple times, conditionally executing the various instruction types, and accessing main memory. Each of these actions are expensive. In our VISA-based approach, line 18 is free of cryptographic cost.

#### 2.3 VISA Technical Challenges and Solutions

Our core contribution is the introduction of VISA-based MPC. Efficiently implementing an MPC VISA machine presents crypto- and system-technical challenges; we discuss the main challenges here.

Managing the active set Inside a fragment, we have full static knowledge of the straight-line code, so we can directly and efficiently compile the code to a circuit. However, a VISA machine must conditionally execute fragments in the active set at each step.

The cost of this conditional dispatch is greatly improved thanks to the recent line of work on MPC conditional branching, in particular Stacked Garbling (SGC) [HK20a, HK21b]. By integrating

$<sup>^3</sup>$ For readability, Figure 1 is written in C; our machine manipulates low level assembly, and each line of C code can correspond to multiple assembly instructions. See Appendix A for the corresponding assembly.

SGC, we can conditionally dispatch over active set fragments with communication proportional to a single (largest) fragment. Although SGC improves communication, it still requires computation: for b fragments, the computational cost scales with  $O(b \log b)$  [HK21b]. Thus, we must not allow the active set to grow too large.

Further, SGC-based conditional branching incurs communication cost that scales with the size of the conditional's interface, i.e., the number of input/output wires, with additional factor dependent on the number of branches b. This cost imposes constraints on the efficiency of using small fragments, and impacts the utility of breaking down fragments, e.g., in alignment with RAM accesses.

In this work, we do not significantly optimize fragments, leaving it as crucial and significant future work. Our fragments are syntactically derived from the control flow structure of the assembly program. This choice is sufficient for modest programs. We envision that future work can use compiler techniques and static analysis to more intelligently select fragments. For example, a fragment can be split into pieces, or multiple fragments can be combined into one. We emphasize the complexity of this problem space: a good solution should simultaneously consider the size of each active set, the size of fragments, the number of RAM accesses, the per-fragment overhead, such as the size of the interface to SGC, etc.

Stacked Garbling with RAM Access Using SGC to conditionally evaluate fragments introduces a subtle technical challenge in handling RAM accesses within fragments. For multiple technical reasons, it is not possible or desired to access RAM directly from inside an SGC conditional branch. This is primarily because GRAM and ORAM reveal random-looking access patterns to the parties. If an access comes from an inactive conditional SGC branch, then SGC's optimization will reveal information incompatible with the normal access pattern of the GRAM/ORAM. Thus, this use is insecure, as it allows the GC evaluator to identify the active branch in a conditional. See detailed discussion in Section 6. Other issues include the increased computational cost of processing GRAM's expensive access procedure in each branch. Similar concerns may apply to accessing other types of resources, such as stacks, queues, expensive procedure calls (e.g. non-black-box crypto primitives), or recent improved and unstackable GC techniques [HK21a].

In Section 6, we design a novel mechanism for efficiently and securely handling RAM accesses from within SGC branches. In short, our mechanism allows us to cheaply escape the conditional branch, access the resource, and then re-enter *that same branch*. Each branch can access a resource multiple times. Our mechanism allows fragments to access RAM without paying high cost for SGC gadgets.

We also note the following lower-level contributions:

**Entire System and Security Proof** We package our approach as a garbling scheme and prove it secure.

**Implementation** Our system is a non-trivial systems-technical undertaking.

## 3 Related Work

In our review of related work, we focus on prior general purpose MPC tools.

Straight-line execution tools The vast majority of MPC tools use straight-line execution, e.g. [RHH14, ZE15, DSZ15, WMK16, ACC<sup>+</sup>22, LHS<sup>+</sup>14]. These tools require that each program loop has a hard-coded upper bound. CBMC-GC goes one step further by trying to infer loop bounds automatically, but still ultimately models the program as a straight-line circuit [FHK<sup>+</sup>14].

Straight-line execution cannot suitably support arbitrary programs where the number of loop iterations depends on the data. We note that [HHNZ19] is an excellent systematization of knowledge that explores the pros and cons of such tools.

**CPU emulation tools** We consider two works that operated in the CPU emulation paradigm [Kel17, WGMK16]. [Kel17] used SPDZ to implement a CPU-emulation-based protocol for malicious adversaries. While their online efficiency is competitive with the total cost of [WGMK16], their offline efficiency is  $\approx 100 \times$  slower. In our evaluation (Section 7), we accordingly focus our comparison on [WGMK16]. We described [WGMK16]'s approach in Section 1, and we compare to their performance in Section 7.

[WGMK16]'s uses Circuit ORAM [WCS15], which could be modularly swapped for a different ORAM, such as [Ds17], correspondingly affecting (improving) performance. We only compare to the existing system [WGMK16]. Constant-round complexity (and hence using EPIGRAM) is essential for CPU-emulation and VISA MPC due to the sequential nature of RAM accesses in these models. Interactive ORAMs incur latency cost proportional to the (large) number of steps of a typical program (cf. discussion in Section 7.4.3). Further, GRAM can be easily and cheaply upgraded to stronger security models, e.g. covert or malicious, using existing techniques. Such an upgrade for ORAM constructions, including [Ds17], is a challenge.

We note that TinyGarble implemented a MIPS ALU, but did not build on this to implement a working CPU emulation tool [SHS<sup>+</sup>15]. For example, they do not integrate RAM support to their prototype. Their main contributions are (1) better management of plaintext function by avoiding unrolling it into a plaintext circuit, and (2) applying hardware synthesis tools to reduce the size of the MIPS CPU, improving over naïve by up to 14.95%.

**Loop Coalescing.** Loop coalescing is a compiler technique explored in the MPC context by [LWN<sup>+</sup>15] (and in the proof system context by [WSR<sup>+</sup>15]). The basic idea is to combine the bodies of loops into a single loop with an internal conditional. [LWN<sup>+</sup>15, WSR<sup>+</sup>15] show that this can improve MPC (resp. proof system) performance by reducing the number of hard-coded loop bounds in the program (cf. Section 1.1). The technique does not suggest (nor do [LWN<sup>+</sup>15, WSR<sup>+</sup>15] explore) further optimization, such as fragment design.

There are common characteristics of loop coalescing and VISA. Both techniques conditionally dispatch over program fragments.

Crucially, VISA approaches MPC optimization holistically, providing a clean abstraction and vocabulary for general optimization of oblivious programs (e.g. include stacking, GRAM, our new gadgets, etc.) and for expressing optimization constraints. Indeed, VISA emphasizes fragment design as a crucial optimization problem. VISA also provides a convenient vocabulary for discussing low level details, such as the size of a register file and managing the active set. See further discussion in Sections 5.3 and 5.4. In contrast, coalescing is a source code transformation, and is at the wrong level of abstraction for fragmentation and low-level optimization.

## 4 Preliminaries

We implement our VISA machine using garbled circuits (GC). GC allows for powerful protocols that achieve secure computation in only a constant number of protocol rounds. We build on the half-gates GC technique [ZRE15], which requires that the parties communicate two ciphertexts per AND gate and zero ciphertexts per XOR gate [KS08].

We combine the basic [ZRE15] scheme with recent improvements in Garbled RAM [HKO21] and with Stacked Garbling [HK20a, HK21b]. Garbled RAM is needed when accessing data from the VISA machine's main memory, and Stacked Garbling improves the communication consumption incurred when conditionally handling fragments.

We use these GC improvements heavily, and we overcome technical problems needed to compose them.

## 4.1 Garbled RAM

Compiling large arrays to Boolean circuits is infeasible. The problem is that on each array access, the circuit must touch each element of the array. Hence, on each access we pay cost proportional to the size of the array. Garbled RAM (GRAM) [LO13] equips GC with random-access arrays that incur only *sublinear cost*. GRAM preserves GC's important constant-round property.

A recent GRAM, called EpiGRAM, dramatically improved the concrete cost of the technique [HKO21]. We implemented EpiGRAM, and we use it to instantiate our VISA machine's main memory.

Our formalism manipulates GRAM directly by using two gates provided by EPIGRAM:

- An ARRAY gate takes as input public natural numbers n and w. It outputs a zero-initialized size-n array of width-w elements. We initialize all of our arrays width w = 32.

- An ACCESS gate performs an array access. The gate accepts as input (1) an array A, (2)  $\log_2 n$  bits that together encode an array index  $\alpha$ , (3) a bit rw that indicates if this is a read or a write, and (4) a w-bit value y that indicates what to store in the array if this is a write. As output, the gate yields (1)  $A[\alpha]$  and (2) the updated array where the content of index  $\alpha$  has been replaced by y iff rw = 1.

## 4.2 Stacked Garbling (SGC)

Until recent breakthrough work [HK20a, HK21b], GC techniques required communication proportional to the computed program, including inactive branches. SGC [HK20a, HK21b] achieves communication proportional to only the single longest execution path of the program.

This improvement is a boon to our approach, because we repeatedly conditionally evaluate the target program's fragments. SGC greatly improves the communication cost of fragments (see Section 7).

#### 4.3 Cryptographic Assumptions

Our garbling scheme (Section 6.2) is secure under a typical GC assumption: We assume that the function H is a circular correlation robust hash function [CKKZ12, ZRE15].

As is standard in MPC (e.g., [GKK<sup>+</sup>12, WGMK16]), total runtime, i.e., the number of CPU emulation steps, is public. If desired, the steps can be padded.

We consider security in the presence of a semi-honest adversary. Since our construction is a garbling scheme, its security can be extended into covert, public verifiable covert (PVC), malicious models using standard techniques.

## 5 Our VISA

The general idea of a VISA is agnostic of low-level details. Of course, it is interesting to instantiate and experiment with a specific architecture. We formalize our specific VISA here.

Our VISA is built on top of a base ISA. Our base ISA is indeed basic, providing primitive instructions that (1) perform algebraic operations, (2) achieve dynamic control flow, and (3) read/write main memory. We first formalize this base ISA. We choose a custom base ISA for simplicity of presentation and implementation; it may be desirable in future work to replace the base ISA with an off-the-shelf ISA, such as MIPS.

Once we establish the base ISA, we formalize our VISA, which essentially aggregates base instructions into fragments.

#### 5.1 Base ISA

The base ISA specifies the instructions that can appear in our supported assembly programs. We emphasize that we do not execute these instructions one by one; rather, our VISA groups base instructions into fragments, and our VISA machine treats fragments as its atomic units of computation.

The base ISA formalizes both the syntax and the semantics of instructions. Our instructions each provide a simple mechanism for performing algebra, achieving control flow, or accessing memory. To define instruction semantics, we define an abstract machine that executes instructions. Our ISA simultaneously defines our instruction set and the abstract machine that runs them.

**Definition 1** (Base ISA). Our instruction set is formally defined in Figure 2. The semantics of instructions are defined by reference to an abstract machine with a program counter pc, a register file  $\mathcal{R}$ , a main memory  $\mathcal{M}$ , and a program  $\mathcal{P}$ . pc is a 32-bit index that indicates which base instruction to execute next.  $\mathcal{R}$  is a length-m array of 32-bit integers.  $\mathcal{M}$  is a length-m array of 32-bit integers.  $\mathcal{P}$  is an array of instructions. Both m and m are configurable parameters of the abstract machine. A machine is initialized with an arbitrary program. At initialization, pc,  $\mathcal{R}$ , and  $\mathcal{M}$  are zero initialized. At each step, the machine updates itself based on the semantics of instruction  $\mathcal{P}[pc]$ .

In our implementation, we instantiate a machine with a size-13 register file; we vary the size of RAM depending on the requirements of the executed program.

We emphasize that while both the register file and the memory are key-value data structures, our VISA machine handles them very differently. Our memory supports dynamic access and is implemented using Garbled RAM. On the other hand, our register file does not need to implement dynamic access: each usage of the register file is statically specified by an instruction, so each register is essentially just a named collection of 32 circuit wires. Inside a fragment, accessing the register file is free.

|               | Syntax                                    | Semantics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|---------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|               | COPY tar src                              | $\mathcal{R}[tar] \leftarrow \mathcal{R}[src]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|               | CCOPY $tar \ src_0 \ src_1$               | $\mathcal{R}[tar] \leftarrow \begin{cases} \mathcal{R}[src_1], & \text{if } \mathcal{R}[src_0] = 1\\ \mathcal{R}[tar], & \text{otherwise} \end{cases}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|               | ADD $tar \ src_0 \ \{src_1\}$             | $\mathcal{R}[tar] \leftarrow \mathcal{R}[src_0] + val(src_1)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|               | SUB $tar \ src_0 \ \{src_1\}$             | $\mathcal{R}[tar] \leftarrow \mathcal{R}[src_0] - val(src_1)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|               | MUL $tar \ src_0 \ \{src_1\}$             | $\mathcal{R}[tar] \leftarrow \mathcal{R}[src_0] \cdot val(src_1)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|               | XOR $tar \ src_0 \ \{src_1\}$             | $\mathcal{R}[tar] \leftarrow \mathcal{R}[src_0] \oplus val(src_1)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Algebra       | AND $tar \ src_0 \ \{src_1\}$             | $\mathcal{R}[tar] \leftarrow \mathcal{R}[src_0] \wedge val(src_1)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| J             | EQ $tar \ src_0 \ \{src_1\}$              | $\mathcal{R}[tar] \leftarrow \begin{cases} 1, & \text{if } \mathcal{R}[src_0] = val(src_1) \\ 0, & \text{otherwise} \end{cases}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|               | CMP $tar \ src_0 \ src_1$                 | $\mathcal{R}[tar] \leftarrow 2 \cdot (\mathcal{R}[src_0] \overset{u}{<} \mathcal{R}[src_1]) + (\mathcal{R}[src_0] \overset{s}{<} \mathcal{R}[src_1])$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|               | SWAP $src_0$ $src_1$                      | $\mathcal{R}[src_0], \mathcal{R}[src_1] \leftarrow \mathcal{R}[src_1], \mathcal{R}[src_0]$ $\mathcal{R}[dst] \leftarrow \lfloor \mathcal{R}[dst]/2 \rfloor$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|               | RS1 $dst$                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|               | ${\tt IMM}\ dst\ imm$                     | $\mathcal{R}[dst] \leftarrow imm$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|               | J imm                                     | $pc \leftarrow imm$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|               | JE $src\ imm$                             | $\operatorname{pc} \leftarrow \lim_{n \to \infty} \operatorname{if} \mathcal{R}[src] \neq 0$ $\operatorname{pc} \leftarrow \begin{cases} imm, & \text{if } \mathcal{R}[src] \neq 0 \\ \operatorname{pc} + 1, & \text{otherwise} \end{cases}$ $\operatorname{pc} \leftarrow \begin{cases} imm, & \text{if } \mathcal{R}[src] = 0 \\ \operatorname{pc} + 1, & \text{otherwise} \end{cases}$ $\operatorname{pc} \leftarrow \begin{cases} imm, & \text{if } \mathcal{R}[src] \& 1 \neq 0 \\ \operatorname{pc} + 1, & \text{otherwise} \end{cases}$ $\operatorname{pc} \leftarrow \begin{cases} imm, & \text{if } \mathcal{R}[src] \& 2 \neq 0 \\ \operatorname{pc} + 1, & \text{otherwise} \end{cases}$ |  |  |  |  |  |

|               |                                           | pc + 1, otherwise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|               | JNE src imm                               | $pc \leftarrow \begin{cases} imm, & \text{if } \mathcal{R}[src] = 0 \end{cases}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Control Flow  |                                           | $\int \mathbf{pc} + 1$ , otherwise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Collitor Flow | II ana imm                                | $\int imm$ , if $\mathcal{R}[src]\&1 \neq 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|               | JL src imm                                | $pc \leftarrow pc + 1$ , otherwise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|               |                                           | $\lim_{n \to \infty} \inf \mathcal{R}[src] \& 2 \neq 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|               | JB $src\ imm$                             | $pc \leftarrow \begin{cases} pc + 1 & \text{otherwise} \end{cases}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|               | HALT                                      | - no effect, pc unchanged -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|               | LOAD tar src                              | $\mathcal{R}[tar] \leftarrow \mathcal{M}[\mathcal{R}[src]]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Memory        | STORE tar src                             | $\mathcal{M}[\mathcal{R}[tar]] \leftarrow \mathcal{R}[src]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|               |                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|               | 7/ \ A                                    | $\int x$ , if x is an immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|               | $val(x) \stackrel{\triangle}{=} \epsilon$ | $\begin{cases} x, & \text{if } x \text{ is an immediate} \\ \mathcal{R}[x], & \text{if } x \text{ is a register id} \end{cases}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|               |                                           | ( f., 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

Figure 2: Our base ISA. Each instruction type handles between zero and three arguments. In general, arguments refer to *registers*, but some arguments, denoted  $\{\cdot\}$ , can also optionally be *immediates* (i.e., compile-time constants). val is a helper function that resolves an argument that can be either a register or an immediate. Unless the semantics otherwise mention an effect on the pc, each instruction also increments the pc. The symbol < with an overset u (resp. s) denotes a comparison where the arguments are treated as an unsigned (resp. signed) integers.

## 5.2 Fragments

As discussed and motivated in Section 2, batching multiple instructions by creating fragments resolves the bulk of the cost of the CPU emulation approach.

**Definition 2** (Fragment). A fragment is a straight-line sequence of base ISA instructions where only the final instruction may be a Control Flow instruction (c.f. Figure 2).

Definition 2 coincides with the notion of a program basic block. We still elect to use new terminology because the notion of a fragment can be (and, we expect, will be) generalized, for example by allowing intra-fragment control flow. The only limitation in extending the above definition is that a fragment should never contain a data-dependent loop, since this would break the straight-line nature of the fragment. For simplicity, we do not explore this direction here, but we believe that this can be exploited heavily in future work.

We now define the syntax/semantics of our VISA.

**Definition 3** (Our VISA). Like our base ISA, a VISA is a set of instructions together with the abstract machine that executes them. A VISA instruction is a fragment (Definition 2). The VISA abstract machine is identical to the base ISA machine, except that the program  $\mathcal{P}$  consists of fragments, and at each step the machine executes the semantics of the current fragment  $\mathcal{P}[pc]$ .

Remark 1. Note, a VISA program is thus viewed as including the corresponding variable instruction set. A VISA then specifies the interpretation of the program. A VISA machine instantiates the (secure) execution of the program. While a full toolchain starts from programs written in a base ISA, the VISA definition is about programs that have been fragmented. In practice, the VISA machine toolchain will generate the fragmentation and hence the program's instruction set.

While the above *specification* indicates an array lookup  $\mathcal{P}[pc]$ , our instantiation dispatches fragments via conditional branching. Note that to achieve the prescribed semantics, we do not need to conditionally dispatch over *each* fragment at each step. In general, not all fragments will be possible at a given step. We reduce the number of conditionally dispatched fragments by considering a control flow graph (CFG) representation of the target program. We maintain a set of pointers into the CFG that indicates the set of possible pc values. At each step, our VISA machine only dispatches over those fragments that are currently pointed to.

#### 5.3 Memory Hierarchy

A VISA introduces the opportunity to distinguish three types of memory:

- Main memory. Most program state is stored in a large main memory that is accessed dynamically at high cost.

- Persistent Registers. The local state of a VISA machine is held in *persistent registers*. Inside the fragment, these registers are free. However, to conditionally dispatch over fragments, this local state must be passed to each branch. SGC imposes cost for each bit that crosses the interface to/from the conditional. It is sensible to store frequently used data in persistent registers, but the number of these registers should be kept in check.

• Local Registers. Since register access is free inside a fragment, a VISA program can introduce arbitrary numbers of local registers, allowing the fragment to store a large state without paying for it. At the exit of the fragment, the content of local registers is lost.

Allocating data to these levels of memory is a large and interesting optimization space. We use 13 persistent registers and a RAM of size up to  $2^{13}$  32-bit words in our experiments.

## 5.4 Fragment Generation

As discussed in Section 2, the choice of strategy for breaking a program into fragments can dramatically affect performance. In this work, we align fragments with program basic blocks (i.e., each control flow instruction maps to a fragment), with one exception: we introduce extra fragments for RAM accesses such that each fragment has at most one RAM access. We found that this simple strategy reduces the overall number of RAM accesses<sup>4</sup>, which we found is the performance bottleneck.

Note that for simplicity of presentation, Figure 1 does not show the extra fragments resulting from RAM accesses. Our actual fragmentation has 14 fragments.

While we leave further in-depth exploration of intelligently selecting fragments as significant future work, we outline several guidelines for such strategies. We note that these guidelines sometimes contradict one another, as fragment optimization is a challenging problem.

Generate fragments such that each conditional dispatch is over fragments of similar size and with a similar number of RAM accesses SGC, and other approaches to MPC free branching [HKP20, HKP21], achieves communication cost proportional to the single most expensive branch. To best take advantage of free branching, ensure that branches have similar cost. This can be achieved, e.g., by splitting large program basic blocks into more than one fragment and/or by merging multiple basic blocks into a single fragment.

RAM access is an expensive resource; an unbalanced allocation across dispatched fragments misses an opportunity to amortize accesses.

**Prefer larger fragments** This reduces the number of VISA machine steps. Hence, larger fragments further reduce the amount of CPU-emulation-style machinery.

Compress the interface to each fragment As explained in Section 5.3, we pay to transport the content of persistent registers into and out of branches. Using compiler techniques to reduce the number of needed persistent registers will reduce cost.

Prefer fragmentation that leads to smaller active sets SGC computational and interface costs scale with the number of branches, so we should seek to reduce the number of branches per step (i.e., to shrink each active set). One way this guideline might be achieved is by artificially introducing periodicity into a program's execution. For instance, we can split each loop into a number of fragments that is a power of two. Without periodicity in consecutive loops the active set will tend to grow with each step until it includes each program fragment. Artificially introducing periodicity groups fragments into "congruence classes" and ensures that most fragments never

<sup>&</sup>lt;sup>4</sup>I.e., all active set fragments will have a same number of accesses.

coincide in the same active set. [WGMK16] considered a similar technique in their MIPS processor. Introducing periodicity for fragments introduces further opportunities to align code and amortize cost.

## 6 GAR: Our VISA Machine

This section introduces GAR (Garbled Assembly with RAM) our implementation of the VISA machine. GAR is formalized as a garbling scheme [BHR12]. As already mentioned, GAR conditionally dispatches fragments using SGC and implements main memory via GRAM.

We first discuss technical issues and our solution in combining our two main building blocks, SGC and GRAM. Then, in Section 6.2 we present the GAR scheme and state the main security theorem (proofs are presented in the Appendix).

#### 6.1 SGC with GRAM

The incompatibility of SGC and GRAM SGC is compatible with many, but not all GC techniques. SGC requires that the string of material encoding each branch be indistinguishable from a uniform string. This restriction is needed to mask from the GC evaluator the identity of the conditional's active branch: if a branch is inactive, SGC arranges that the evaluator obtains uniform garbage material.

Unfortunately, GRAM's material is distinguishable from a uniform string. In short, GRAM will one-by-one reveal to the evaluator RAM indices that are randomly generated without replacement [HKO21]. These revealed indices are indistinguishable from a uniform permutation, but not from a uniform string. Thus it is not secure to use GRAM's ACCESS gate inside an SGC conditional.

SGC's uniform string requirement and GRAM's revealed uniform permutations seem somewhat inherent to the techniques, and it is not clear that we can revise these techniques to make them compatible with one another. Even if it were possible to make the two techniques compatible, it would not be desirable. SGC requires that each party garble each branch multiple times, introducing added computational cost. Since the GRAM access procedure is large, we would like to avoid repeatedly garbling it. It is more pragmatic to simply garble each access once, as we end up doing.

Our Approach One way we could handle RAM access in a VISA machine would be to place each RAM access instruction in its own single-instruction fragment. While correct and secure, the approach violates several of our guidelines for program fragmentation (Section 5.4), and is undesirable for a number of performance reasons. In particular, the resulting fragments are smaller, more numerous, and each RAM access will service a smaller fragment. Ultimately, this discards many of the VISA's benefits.

A much better way would be to temporarily escape a fragment just to perform the RAM access, then re-enter that fragment. This is the approach we take. We design a new scheme that allows us to temporarily escape an SGC conditional branch (i.e., a fragment), perform the access, then re-enter that same branch. Because we escape the SGC branch before accessing RAM, we avoid SGC's uniform string requirement. Thus, RAM access is simulatable. Crucially for performance, our gadgets escape, and not fully exit SGC, and transfer across the SGC interface only those specific

bits that are directly related to the RAM access. Thus, we do not, for example, pay to transfer the full register file on each RAM access.

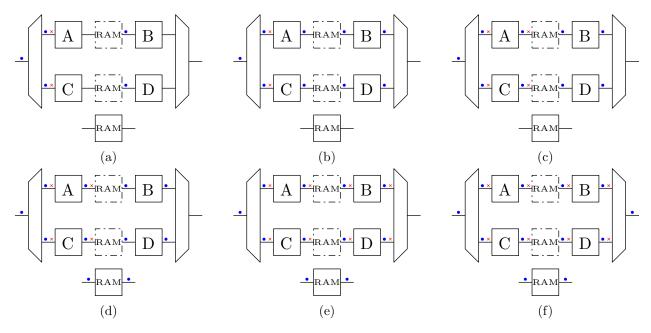

Instrumenting GRAM access in SGC SGC uses two garbled gadgets, the *demux* and the *mux*, to enter and exit a conditional, respectively. Each of these gadgets handles branch input/output wire-by-wire, where each wire is (indirectly) connected from the outside of the conditional to the internal circuit of each branch. We refer to each of these wire connections as a *port* of the demux/mux. There is one port per external wire.

Our observation is that, in contrast with standard SGC, the demux/mux need not be evaluated in one shot at the very beginning/end of the conditional. Instead, the GC evaluator can process ports of the gadgets in an *arbitrary* order, so long as data dependencies in the circuit are satisfied.

This in particular means that the evaluator can (1) process input to a branch by handling only some ports of the demux, (2) evaluate some gates in that branch, generating input to a RAM query, (3) feed the RAM query through ports in the mux to temporarily escape the branch, (4) execute the RAM access outside of SGC, in plain GC, (5) feed the RAM result through ports of the demux back into the branch, and (6) continue evaluation of the branch.

Interestingly, the GC generator's order of building the corresponding GC material is different. Because each branch must be generated from a seed (this is a key trick behind SGC's improvement), the generator garbles each branch all at once, before any RAM accesses are handled. As part of doing so, he assigns uniformly random GC labels to the branch side of each demux port. Only once each branch is fully generated, does he generate GC for RAM access(es). Labels of these GCs match the labels of the ports of the SGC conditional. Finally, he generates the GC material for the demux and mux.

We include a diagram illustrating this process in additional detail in Appendix C (Figure 14). Our modification to SGC still uses the main ideas of Stacked Garbling [HK20a]: our GC generator garbles each branch starting from a distinct PRG seed and then stacks the material together using XOR. Our GC evaluator can decrypt the seed for each inactive branch and hence can reconstruct their garblings, unstack the material for the active branch, and evaluate. I.e., our scheme retains the important communication advantage of SGC.

Next, we formalize our full garbling scheme GAR, which includes the above trick.

#### 6.2 Our Scheme: Formalization and Theorems

We formalize our VISA machine as a *garbling scheme* [BHR12]. SGC [HK21b] and GRAM [HKO21] are also formalized as garbling schemes; our scheme reorganizes and adjusts their procedures, making them compatible with each other and with our VISA (Section 5).

At a high level, our scheme should be understood as a new SGC scheme equipped with black-box GRAM. As an aside, it is possible to replace black-box GRAM with other garbled resources, for example a stack or queue [ZE13].

**Program Description** A garbling scheme securely handles any program from some specified language. Our goal is to support programs expressed in our base ISA (Figure 2). At the lowest level, we have primitive support for AND gates [ZRE15], XOR gates [KS08], SWITCH statements [HK21b], and ARRAY and ACCESS gates [HKO21]. The semantics of XOR and AND gates are natural; ARRAY and ACCESS gate semantics are specified in Section 4.1. A SWITCH executes only the

indicated branch and outputs the result. We group instructions from our base ISA, then compile these to our low level primitives. Thus, our formal garbling scheme consists of three major steps:

- Compile base ISA program to VISA program. Our scheme first groups base ISA instructions into fragments using the strategy described in Section 5.4.

- Compile VISA program to primitives. We compile each fragment primitive operation using standard techniques. Each basic instruction has a corresponding straight-line circuit, and our scheme stitches together each of the circuits in the fragment. To conditionally dispatch, the scheme wraps the fragment circuits in a SWITCH.

- Evaluate primitives via GC. The most interesting step is the evaluation of primitives, which is explained below.

Note that the first two steps of our handling are quite modular. It is easy to replace the ISA to VISA compiler with one that, for example, more intelligently selects fragments. Similarly, we could replace the compiler from fragments to circuits with more sophisticated techniques. From here, our scheme focuses on the handling of primitives, which is its crypto-technical component.