# Fast polynomial multiplication using matrix multiplication accelerators with applications to NTRU on Apple M1/M3 SoCs

Décio Luiz Gazzoni Filho<sup>1,2</sup>, Guilherme Brandão<sup>3</sup> and Julio López<sup>1</sup>

<sup>1</sup> Instituto de Computação, Universidade Estadual de Campinas (UNICAMP), Campinas, Brazil

<sup>2</sup> Department of Electrical Engineering, State University of Londrina, Londrina, Brazil

<sup>3</sup> Independent Researcher, Londrina, Brazil

**Abstract.** Efficient polynomial multiplication routines are critical to the performance of lattice-based post-quantum cryptography (PQC). As PQC standards only recently started to emerge, CPUs still lack specialized instructions to accelerate such routines. Meanwhile, deep learning has grown immeasurably in importance. Its workloads call for teraflops-level of processing power for linear algebra operations, mainly matrix multiplication. Computer architects have responded by introducing ISA extensions, coprocessors and special-purpose cores to accelerate such operations. In particular, Apple ships an undocumented matrix-multiplication coprocessor, AMX, in hundreds of millions of mobile phones, tablets and personal computers. Our work repurposes AMX to implement polynomial multiplication and applies it to the NTRU cryptosystem, setting new speed records on the Apple M1 and M3 systems-on-chip (SoCs).

Keywords: PQC · NTRU · Apple Silicon · Accelerators

# 1 Introduction

In the 1990s, Shor [Sho97] described an efficient quantum algorithm to solve hard problems (integer factorization and discrete logarithms) for classical computers, compromising many existing cryptosystems. Post-quantum cryptography (PQC) seeks to develop new public-key cryptosystems based on hard computational problems resistant to quantum attacks, such as those based on lattices. Research into efficient implementation flourished as multiprecision integer arithmetic gave way to polynomial multiplication modulo "small" (CPU word size) integers for lattice-based schemes, introducing new challenges and performance tradeoffs.

In their Turing lecture [HP19], computer architecture pioneers Hennessy and Patterson claim that "(a)n era without Dennard scaling, along with reduced Moore's Law and Amdahl's Law in full effect means inefficiency limits improvement in performance to only a few percent per year", suggesting that further hardware improvements must come from domain-specific architectures tailored to specific applications. This is seen in the addition of SIMD extensions and special-purpose instructions (such as for symmetric cryptography and binary polynomial multiplication) to CPUs, as well as increasingly popular accelerators such as programmable graphics processing units (GPUs), FPGAs and others. Such developments have opened up new research agendas for efficient implementation of cryptosystems.

The meteoric rise of artificial intelligence, machine learning and deep learning in the 2010s, and their demand for teraflops-level linear algebra performance, led to an introduction of domain-specific architectures such as tensor cores for NVIDIA's GPUs

E-mail: decio.gazzoni@ic.unicamp.br,dgazzoni@uel.br (Décio Luiz Gazzoni Filho), brandaogbs@gmail.com (Guilherme Brandão), jlopez@ic.unicamp.br (Julio López)

[MCL<sup>+</sup>18], IBM Power ISA's Matrix-Multiply Assist (MMA) [MBB<sup>+</sup>21], Intel's Advanced Matrix Extensions (AMX) [Int22], and ARMv9-A's Scalable Matrix Extensions (SME) [WMS22]. The first three have launched in production hardware in 2017, 2021 and 2023, respectively, whereas the latter, to our knowledge, hasn't shipped as of 2023. Although less publicized, a matrix multiplication accelerator has shipped in hundreds of millions of mobile phones, tablets and personal computers, specifically those made by Apple, starting with the 2019 A13 system-on-chip (SoC) used in the iPhone 11 [Rod20, Section 7.6]. It is a coprocessor named AMX (no relationship to Intel AMX), also present in newer generations of Apple SoCs, such as the M-series powering ARM-based Apple personal computers.

Our work investigates repurposing AMX to accelerate cryptographic operations, in particular the core polynomial multiplication routines of lattice-based post-quantum cryptosystems. To that end, we implement NTRU [HPS98], specifically the proposal [CDH<sup>+</sup>20] that advanced to the third round of the NIST PQC standardization process [Nat17], in the Apple M1 and M3 SoCs using AMX. Despite NIST's preference for Kyber [ABD<sup>+</sup>19], NTRU has been standardized by IEEE Std 1363.1 [Ins09] and ASC X9.98 [Ame17]. It is also representative of a wider class of lattice-based schemes based on NTT-unfriendly rings such as SABER [BMD<sup>+</sup>20] and FrodoKEM [BCD<sup>+</sup>16, ABD<sup>+</sup>21]; the latter is recommended by the German BSI [Bun21] and under standardization by ISO [Int23c]. In case of any cryptanalytic attack on Kyber, NTRU may be the target of renewed interest.

A potential roadblock is that AMX is undocumented by Apple; programmers are intended to access it via calls to Apple's Accelerate framework [App23], which provides accelerated versions of the industry-standard BLAS library [LHKK79] and the proprietary BNNS neural network API. Fortunately, extensive reverse-engineering efforts [Joh22b, Han23, Caw23] document AMX's instruction set and performance characteristics, allowing us to develop a full NTRU implementation with AMX-accelerated polynomial multiplication routines, as presented in this paper. The authors were not involved in these reverse-engineering efforts, working only with the information made public in these references.

Related works. Google's Tensor Processing Unit is described in [JYP $^+$ 17]. It achieves a peak throughput of 92 TOPS/s and 15–30× faster neural network inference than CPUs and GPUs of that era. [MBB $^+$ 21] reports a 2× speedup by using MMA over regular vector code for double-precision matrix multiplication in the POWER10 CPU. Some works validate speedups from NVIDIA GPU tensor cores, including for PQC schemes [MCL $^+$ 18, WZF $^+$ 22, LSH $^+$ 22, LSZH22]. We refrain from further analysis as we consider AMX and GPUs distinct types of accelerators, as discussed in "Our contributions" below.

We found no references to Apple AMX in the scientific literature, and Apple does not officially document AMX functionality or performance characteristics. We resort to reverse engineering efforts of [Joh22b, Han23, Caw23], which we summarize in Section 3.

Lastly, we consider ARMv8-A implementations of NTRU. Karatsuba and Toom-Cook algorithms are implemented in [NG21], achieving speedups on the M1 of up to  $6.68\times$  and  $8.49\times$  for encapsulation and decapsulation, respectively, versus the reference implementation. [CCHY23] set new speed records for the HPS2048677 and HRSS701 parameter sets using the TMVP algorithm. They also optimized polynomial inversion and constant-time sorting, speeding up key generation, encapsulation and decapsulation by  $7.67\times$ ,  $2.48\times$  and  $1.77\times$ , respectively, compared to [NG21] on the Cortex-A72 core.

**Our contributions.** We present the first (to our knowledge) implementation targeting AMX in the scientific literature, and also the first cryptographic implementation on a CPU-coupled matrix multiplication accelerator; previous works targeted GPU tensor cores.

It is difficult to compare CPU-only and accelerated implementations (e.g. for GPUs), due to enormous architectural differences: GPUs are massively parallel, high-throughput and high-latency devices, whose parallelism must be exploited by batching a large number

of operations to realize their performance potential, severely limiting applicable use cases.

In contrast, CPU-coupled matrix multiplication accelerators (coprocessors or instruction set extensions) can achieve high throughput without sacrificing latency. Indeed, we set new NTRU speed records on Apple M1 and M3 SoCs, outperforming state-of-the-art NEON implementations under conditions previously seen in CPU implementations only: latency (cycle count) for a *single* execution of the scheme's operations, with *no batching at all*.

SIMD extensions required a paradigm shift from a scalar to a vector (1D) view of computation; matrix multiplication accelerators require a further paradigm shift towards a matrix (2D) view. While AMX's peak theoretical throughput is considerably higher than NEON, it is only achievable for its basic matrix (outer product) operation; while a restricted set of vector operations are available, their throughput is comparable to NEON.

AMX's very limited instruction set reinforces its designed purpose for matrix multiplication; we view our main contribution as repurposing AMX for polynomial multiplication, which required a deep rethinking of polynomial multiplier architectures to better fit its new performance paradigms and tradeoffs. We conjecture that the techniques we propose for AMX may be applicable to many similar accelerators soon to reach the market.

Our implementation is freely available at https://github.com/...<sup>1</sup>

# 2 Preliminaries

**Notation.** Let  $a(x) = a_0 + a_1x + \dots + a_{n-1}x^{n-1}$ . A "slice" of the *i*-th through *j*-th coefficients  $(j \ge i)$  of a(x) is written as  $a_{i:j}(x) = a_ix^i + a_{i+1}x^{i+1} + \dots + a_jx^j$ . Boldface variable names refer to an associated row vector representation:  $\mathbf{a}_{i:j} = [a_i, a_{i+1}, \dots, a_j]$ . Let  $\mathbf{x}_{i:j} = [x^i, x^{i+1}, \dots, x^j]$ ; then  $a_{i:j}(x) = \mathbf{a}_{i:j}\mathbf{x}_{i:j}^\mathsf{T}$ . Finally, i:k:j represents ranges with a non-unit step of k; e.g.  $\mathbf{a}_{i:k:j} = [a_i, a_{i+k}, a_{i+2k}, \dots, a_j]$ . We also combine slice notation with C's array indexing notation, i.e.  $\mathbf{X}[i:j]$  selects elements of index  $i, \dots, j$  of  $\mathbf{X}$ .

The NTRU cryptosystem. Based on the pioneering work of [HPS98], NTRU [CDH $^+$ 20] is a key encapsulation mechanism (KEM) merging the previous NTRUEncrypt [CHWZ17] and NTRU-HRSS-KEM [HRSS17b] proposals, providing the suggested NTRU-HPS and NTRU-HRSS parameter sets, respectively. Based on structured lattices, it uses polynomial arithmetic modulo  $x^n-1$  for prime n with coefficients reduced either modulo 3 or a power of two, q. The original cryptosystem [HPS98] is a partially correct, probabilistic public-key encryption (PKE) scheme. The NIST submission uses the techniques of [HPS96] to obtain a perfectly correct, deterministic PKE, and constructs a KEM using a generic transformation from this PKE [HHK17] which is IND-CCA2 secure in the random oracle model (ROM), and in the quantum-accessible ROM under a non-standard assumption.

Let  $\Phi_1 = x - 1$  and  $\Phi_n = x^{n-1} + x^{n-2} + \ldots + 1$ , so that  $\Phi_1 \Phi_n = x^n - 1$ . Let  $S_3 = \mathbb{Z}_3 / \Phi_n$ ; we define the canonical representative of an element in  $S_3$ , denoted as  $S_3$ , as the polynomial of degree at most n-2 with coefficients in  $\{-1,0,1\}$ .

We present the NTRU PKE algorithms, in which most of the execution time is spent, as Algorithms 2.1, 2.2 and 2.3. We refer to  $[CDH^+20]$  for a full description of the scheme, including the algorithm  $Sample_{f,g}$ . Lift(m), for m(x) a polynomial, is defined as  $\underline{S_3}(m)$  and  $\Phi_1 \cdot \underline{S_3}(m/\Phi_1)$  for HPS and HRSS parameter sets, respectively. Algorithms 2.2 and 2.3 require 1 and 3 polynomial multiplication in the HPS parameter set, and an additional multiplication for each in HRSS as part of the Lift procedure. Algorithm 2.1 appears to call for 5 polynomial multiplications; however, polynomial inversion modulo q in line 3 is usually realized as modulo-2 inversion followed by 4 Newton iterations to lift the result to  $\mathbb{Z}_q/(\Phi_1\Phi_n)$ ; this requires eight more polynomial multiplications, for a total of 13.

$<sup>^1\</sup>mathrm{A}$  GitHub repository will be made available following the paper's publication.

```

Algorithm 2.1 PKE.KeyGen: PKE keypair

Algorithm 2.3 PKE.Dec: PKE decryption

generation

Input: ((f, f_q, h_q), c)

Input: seed

Output: (r, m, fail)

Output: (sk = (f, f_p, h_q), pk = h)

1: v_1 \leftarrow cf \pmod{q, \Phi_1 \Phi_n}

1: (f,g) \leftarrow \mathtt{Sample}_{f,g}(\mathrm{seed})

2: m_0 \leftarrow v_1 f_p \pmod{3, \Phi_n}

2: f_p \leftarrow (1/f) \pmod{3, \Phi_n}

3: m_1 \leftarrow \text{Lift}(m_0)

4: r \leftarrow (c - m_1)h_q \pmod{q, \Phi_n}

3: v_1 \leftarrow 1/(3gf) \pmod{q, \Phi_n}

4: h \leftarrow (v_1(3g)^2) \pmod{q, \Phi_1 \Phi_n}

5: if (r, m_0) \in \mathcal{L}_r \times \mathcal{L}_m then

5: h_q \leftarrow (v_1 f^2) \pmod{q, \Phi_1 \Phi_n}

\triangleright See [CDH<sup>+</sup>20, Sections 1.2 and 1.3]

6: return (sk = (f, f_p, h_q), pk = h)

for definitions of \mathcal{L}_r and \mathcal{L}_m

return (r, m_0, 0)

6:

7: else

Algorithm 2.2 PKE.Enc: PKE encryption

return (r, m_0, 1)

Input: h, (r, m)

Output: c

1: m' \leftarrow \text{Lift}(m)

2: c \leftarrow r \cdot h + m' \pmod{q, \Phi_1 \Phi_n}

3: return c

```

**Table 1:** NTRU parameters and sizes (in bytes).

| Parameter                   | HPS2048509  | HPS2048677  | HPS4096821  | HRSS701     |

|-----------------------------|-------------|-------------|-------------|-------------|

| (n,q)                       | (509, 2048) | (677, 2048) | (821, 4096) | (701, 8192) |

| Key sizes (public, private) | 699, 935    | 930, 1234   | 1230, 1590  | 1138, 1450  |

| Ciphertext sizes            | 699         | 930         | 1230        | 1138        |

The submission includes four parameter sets: HPS2048509, HPS2048677, HPS4096821, and HRSS701. The first three use fixed-weight sample spaces proposed by Hoffstein, Pipher, and Silverman [HPS96, HPS98]; the last uses arbitrary-weight sample spaces proposed by Hülsing, Rijneveld, Schanck, and Schwabe [HRSS17a]. Table 1 lists parameters and sizes.

# 3 Apple's AMX coprocessor

AMX is a coprocessor from Apple to accelerate matrix multiplication operations, first introduced in the Apple A13 SoC powering the iPhone 11 [Rod20]. All the information in this section comes from reverse engineering efforts and analyses of Apple patents by [Joh22b, Han23, Caw23], and is, by its nature, conjectural, although backed by extensive functional and performance experiments. Throughout this section, we focus on the M1 AMX unit, as we found no information about changes in the recently released M3, although our results of Section 5 indicate that M3 delivers increased AMX performance over M1.

#### 3.1 Programmer's model

AMX exposes 80 64-byte registers, split into eight X and eight Y registers (numbered as  $X_0$  to  $X_7$  and  $Y_0$  to  $Y_7$ ), and 64 Z registers better viewed as rows of a matrix, which we number as  $Z[0], \ldots, Z[63]$ . Figure 1, redrawn from an Apple patent [SBG<sup>+</sup>16, Figure 2], is a visualization of intended register file organization. Some instructions can concatenate together either the X or Y registers for bytewise addressing as 512-byte circular buffers.

X and Y are inputs and Z are outputs for most instructions, with a few exceptions. Data cannot be moved between CPU and AMX registers directly; it must go through memory.

Figure 1: AMX register file organization.

Different data types can be represented (8-, 16- or 32-bit integers, or 16-, 32- or 64-bit floating-point values). Input/output lane widths may be identical or mixed in specific combinations [Caw23]; in this paper we only use 16-bit inputs and outputs. The inputs to outer product operations ( $X_i$  and  $Y_i$ ) are 32-element vectors of 16 bits each, resulting in a 32 × 32 output matrix of 16-bit elements; this is smaller than Z's available storage space (16,384 out of an available 32,768 bits). In AMX, each row of the output matrix is mapped to either the even or odd rows of Z, which are fully populated with output coefficients, as the size of a row of Z (512 bits) matches the size of a row of the output matrix.

CPUs in a cluster can share an AMX unit through per-CPU replication of architectural state [Joh22a, Han23]. Instructions are tagged with their source CPU to identify their copy of the state; thus, multiple CPUs may interleave instruction execution [Han23]. Special instructions (set/clr) control AMX's enabled/disabled status for each thread [Caw23].

## 3.2 Programming interface

AMX instructions are inserted into the CPU's instruction stream, and once no longer speculative, are dispatched to AMX via the CPU's store units [Han23]. They are encoded as A64 instructions within a reserved opcode space [Caw23]; given A64's fixed 32-bit instruction encoding, only 10 bits remain, 5 of which encode the instruction's opcode. The remaining 5 bits either encode the index of a scalar 64-bit register through which parameters are passed, or an immediate. This layout is shown in Figure 2. [Caw23] provides preprocessor macros to emit AMX instructions, with an intrinsics-like syntax.

| 31                       | 10   | 9 |        | 5 | 4              | 0    |

|--------------------------|------|---|--------|---|----------------|------|

| 0000 0000 0010 0000 0001 | . 00 |   | opcode |   | register/immed | iate |

**Figure 2:** AMX instruction encoding.

#### 3.3 Instruction set

We now list all known AMX instructions, reviewing those used by our polynomial multiplication implementation, as well as parameters of interest; for an exhaustive specification, see [Caw23]. We propose a taxonomy of instructions in Table 2, categorized by functionality.

We first consider loads and stores. The least-significant 56 bits of their 64-bit argument are treated as a pointer to the source/target memory address; remaining bits encode parameters as per Table 3. While many other instructions can address X/Y registers at arbitrary byte positions, loads and stores require aligning to the start of a register (64-byte boundary); register indices are encoded in bits 58–56 of the argument (or 61–56 for Z rows). Memory accesses can be 64 bytes (bit 62 = 0) or 128 bytes (bit 62 = 1) wide.

| Instruction Type                       | ${\bf Mnemonics (Opcode)}$                                                        | Description                                               |  |  |

|----------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------|--|--|

| Loads and stores                       | ldx(0), ldy(1), stx(2), sty(3), ldz(4), stz(5), ldzi(6), stzi(7)                  | Data movement between memory and AMX registers            |  |  |

| Extract                                | extrh(8), extrx(8),<br>extrv(9), extry(9)                                         | Data movement within<br>the AMX register file             |  |  |

| First generation<br>matrix/vector      | fma64(10), fms64(11),<br>fma32(12), fms32(13),<br>mac16(14), fma16(15), fms16(16) | Outer or pointwise products with accumulation/subtraction |  |  |

| Second generation<br>matrix and vector | <pre>vecint(18), vecfp(19), matint(20), matfp(21)</pre>                           | Outer or pointwise products with accumulation/subtraction |  |  |

| Miscellaneous                          | set(17), clr(17), genlut(22)                                                      | Context switching, lookup tables                          |  |  |

**Table 2:** A taxonomy of AMX instructions. Opcodes given in base 10.

**Table 3:** Parameters for AMX load and store instructions.

| Bits  | ldx, ldy, stx, sty                 | ldz, stz                          |

|-------|------------------------------------|-----------------------------------|

| 63    |                                    |                                   |

| 62    | Load/store single register (0) or  | pair of consecutive registers (1) |

| 61–59 |                                    | Z-row index (0 to 63)             |

| 58-56 | Register index $(0 \text{ to } 7)$ | Z-10w index (0 to 03)             |

| 55-0  | Least significant                  | 56 bits of pointer                |

We illustrate [Caw23]'s macros with an example of a load from an array with base address v to register X<sub>4</sub>. We show a version using just their macros, a second using helper macros defined by us, and a simplified notation used in the algorithms of Section 4:

| C notation                      | C notation, our helper macros     | Algorithm notation                     |

|---------------------------------|-----------------------------------|----------------------------------------|

| AMX LDX((uint64 t)v   4 << 56); | AMX LDX(AMX PTR(v)   LDX REG(4)); | $X_4 \leftarrow ldx(\mathbf{v}[0:31])$ |

We now briefly review other instructions, listing only functionalities of interest. Due to the default role of X and Y as input and Z as output registers, at times data must be moved from Z to X or Y, for which we use the extrh instruction. Its basic operation is copying a chosen row of Z to a byte-addressable 64-byte slice of either X or Y; it also supports other functionalities not required by us. For a visualization of extrh in use, refer to Figure 3. Our algorithmic notation for an example operation of extracting Z[63] to Y0 is:

$$Y_0 \leftarrow \text{extrh}(Z[63])$$

The main AMX arithmetic instruction we use is mac16, which supports vector and matrix modes. Let  $\mathbf{x}, \mathbf{y}, \mathbf{z}$  be 32-element vectors of 16-bit integers. Vector-mode mac16 computes pointwise multiply-accumulates (MACs):  $\mathbf{z} \leftarrow \mathbf{z} + \mathbf{x} \circ \mathbf{y}$ , where + is vector addition and  $\circ$  is the Hadamard (pointwise) product. Concretely,  $\mathbf{z}$  is a row of  $\mathbf{Z}$ , and  $\mathbf{x}$  and  $\mathbf{y}$  are 32-element slices of  $\mathbf{X}$  and  $\mathbf{Y}$ . Each of  $\mathbf{x}, \mathbf{y}, \mathbf{z}$  can be optionally "skipped" to realize different operations: vector addition ( $\mathbf{z} \leftarrow \mathbf{z} + \mathbf{x}$  or  $\mathbf{z} \leftarrow \mathbf{z} + \mathbf{y}$ ), Hadamard product without accumulation ( $\mathbf{z} \leftarrow \mathbf{x} \circ \mathbf{y}$ ), or copying  $\mathbf{x}$  or  $\mathbf{y}$  to  $\mathbf{z}$ , i.e. the extrh instruction in reverse. We now define an algorithmic notation, using an example computation of  $\mathbf{z} \leftarrow \mathbf{z} + \mathbf{x}$  (skipping the  $\mathbf{y}$  input), in which we choose  $\mathbf{z}$  to be the first row (i.e. that of index 0) of  $\mathbf{Z}$  and  $\mathbf{x}$  to be elements 64 to 95 of  $\mathbf{X}$  (i.e. bytes 128 to 191, or equivalently, the full  $\mathbf{X}_2$  register):

$$Z[0] \leftarrow mac16(Z[0] + X[64:95])$$

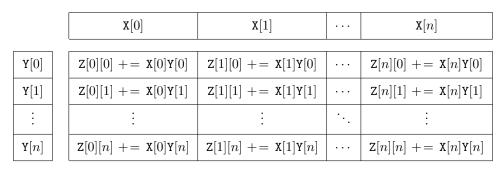

Let  $\mathbf{Z}$  be a  $32 \times 32$  matrix, and  $\mathbf{x}$  and  $\mathbf{y}$  be 32-element (row) vectors. Matrix-mode mac16 realizes an outer product operation with accumulation, as shown in Figure 1:  $\mathbf{Z} \leftarrow \mathbf{Z} + \mathbf{y}^T \mathbf{x}$ . Concretely, the operands  $\mathbf{x}, \mathbf{y}, \mathbf{Z}$  are mapped to slices of  $\mathbf{X}$  and  $\mathbf{Y}$ , and even or odd rows of  $\mathbf{Z}$ , respectively. As with vector-mode mac16, operands can be skipped, although skipping  $\mathbf{Z}$  appears to be the only sensible possibility, which disables accumulation. It is also possible to partially skip either the  $\mathbf{X}$  or  $\mathbf{Y}$  registers (i.e. select only a range of elements within each register for the computation). Consider an example operation of computing the outer product  $\mathbf{Y}_0^T\mathbf{X}_0$  (i.e. elements 0 to 31 of each of these registers), which are accumulated with, and saved to, the even rows of  $\mathbf{Z}$ , while updating only columns 0 to 15 of the output matrix, using the partial  $\mathbf{X}$  skip feature. Our algorithmic notation for this operation is:

$$Z[0:2:62] \leftarrow mac16(Z[0:2:62] + Y_0^TX_0, columns = 0:15)$$

When the "columns" parameter is omitted, it is understood that all columns of the output matrix are updated. It should be clear, from the operation performed, whether vector- or matrix-mode mac16 is intended. A caveat: although within the context of AMX, the Y registers are best understood as column vectors, our choice of notation takes a to be a row vector, and thus  $\mathbf{a}^{\mathsf{T}}$  as a column vector, throughout the paper. We extend this convention to AMX's X and Y registers, and thus write outer products in the form  $Y_i^{\mathsf{T}} X_j$ .

Finally, vecint is a vector (pointwise) instruction which generalizes vector-mode mac16; in particular, a single instruction can compute  $\mathbf{z} \leftarrow \mathbf{z} + \mathbf{x} + \mathbf{y}$ , attaining twice the throughput as vector-mode mac16, a fact which we've used to speed up some of our algorithms. As an example, this is how we denote an example operation of 16-bit integer addition of elements 16 to 47 of the X register (i.e., bytes 32 to 95 of X, incorporating elements of both  $X_0$  and  $X_1$ ) with elements 0 to 31 of the Y register (i.e.  $Y_0$ ), accumulating to Z[1]:

$$\mathbf{Z}[1] \leftarrow \mathtt{vecint}(\mathbf{Z}[1] + \mathbf{X}[16:47] + \mathbf{Y}[0:31])$$

# 3.4 Performance considerations

The M1 has two AMX coprocessors, one per core cluster (performance and efficiency), implementing a second generation of AMX instructions [Caw23]. It runs at the same clock speed as the cores and accesses memory via the L2 cache [Joh22b]. It supports out-of-order execution independently of the CPU, with buffers for 28 to 32 operations [Joh22b].

Outer product latency and throughput is discussed in [Joh22b] for floating-point operations. The performance cluster's AMX unit has an array of pipelined MAC units with 4-cycle latency, capable of executing one 32- or 64-bit outer product operation per cycle, or a 16-bit operation every two cycles. To achieve maximum performance, inter-instruction data dependencies must be avoided; either by using multiple *accumulators*, i.e. different subsets of Z as a destination (such as even and odd rows), or by issuing instructions from different CPUs, due to independent per-CPU AMX register files (see Section 3.1).

AMX microbenchmarking code is supplied in [Caw23]. We have run this code on an M1-based laptop, and report selected throughput figures, restricted to single-threaded results, presumably running on the AMX performance-cluster unit. Multiply-accumulates (MACs) count as 2 operations, and we report best-case scenarios, often using multiple accumulators; performance may degrade, significantly in certain cases, if fewer accumulators are used.

Outer products achieve up to 3.05 TFLOPS/s throughput with 16-bit floating-point data or mixed-lane integer arithmetic (8- and 16-bit operands); throughput drops to 1.53 TOPS/s for pure 16-bit integer arithmetic. In vector mode, up to 381 GFLOPS/s is achievable with floating-point or mixed 8-/16-bit integer MACs, dropping to 191 GOPS/s for pure 16-bit integer arithmetic. Replacing MACs with additions or multiplications alone further halves throughput. As a comparison, peak NEON throughput on M1 performance cores for 16-bit integer data is 204.8 GOPS/s for MACs and 102.4 GOPS/s for additions or multiplications alone, based on the microarchitectural investigations of [Joh22a].

Thus, AMX's peak throughput is  $\approx 8 \times$  higher for matrix (outer product) operations versus vector operations, whose peak performance approaches NEON's. That is, *outer products are much cheaper than vector operations*. Throughout the paper, we consistently strive to reduce vector operation count, which are the bottleneck of our computations.

While our implementation takes the usual constant-time precautions, such as foregoing branches and memory accesses conditional/indexed on secret data, it implicitly relies on constant-time execution of AMX instructions. Recently, ARM and Intel have started giving guarantees regarding data-independent timing of selected instructions [ARM, Int23b, Int23a]. Given AMX's lack of official documentation, it is impossible to obtain such assurances. Instead, we report in Section 5.1 on experiments that suggest AMX, and thus our implementation, is indeed constant-time. The previous lack of data-independent timing guarantees for CPUs hasn't prevented implementors from striving for, and achieving in practice, implementations with apparent constant-time characteristics, and may have played a key part in incentivizing manufacturers to provide such guarantees. We believe our paper is a first step in that direction for CPU-coupled matrix-multiplication accelerators.

# 4 Implementing polynomial multiplication on AMX

We now describe our AMX implementation of schoolbook multiplication in  $\mathbb{Z}_{2^{16}}/(x^n-1)$ .

#### 4.1 Basic block: multiplication of 32-coefficient slices

The basic block of our implementation multiplies slices of 32 coefficients from each input polynomial. We define a specific notation for polynomial slices starting at indices that are a multiple of 32:  $a_{32k:32k+31}(x) = a_{\mathbf{k}}(x)$  (note boldface  $\mathbf{k}$ ). We also define a notation for the product of 32-coefficient polynomial slices:  $c_{\mathbf{k},\mathbf{l}}(x) = a_{\mathbf{k}}(x)b_{\mathbf{l}}(x)$ . To clarify, we have:

$$c_{\mathbf{k},\mathbf{l}}(x) = (a_{32k}x^{32k} + \dots + a_{32k+31}x^{32k+31})(b_{32l}x^{32l} + \dots + b_{32l+31}x^{32l+31})$$

=  $c_{32(k+l)}x^{32(k+l)} + \dots + c_{32(k+l)+62}x^{32(k+l)+62}$ ,

where  $c_m = \sum_{i+j=m} a_i b_j$ . As before,  $\mathbf{c_{k,l}}$  is the associated row vector representation. Throughout the rest of Section 4, we resort to examples using a hypothetical 1/8-size AMX unit for space reasons. Boldface indices will then refer to 4-coefficient slices as appropriate for these examples, rather than 32-coefficient slices for full AMX; thus,  $\mathbf{a_k}$  would refer to  $\mathbf{a}_{4k:4k+3}$ . It will be clear from the context whether we refer to 4- or 32-coefficient slices.

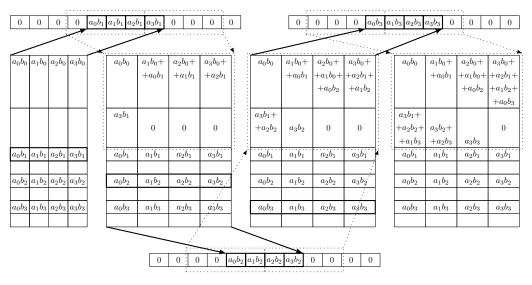

We first note that the outer product  $\mathbf{b_l^T} \mathbf{a_k}$  generates the required partial products; shifting each row produces the usual multiplication parallelogram. We then perform sum-reduction of partial products in each column (an operation which we refer throughout the rest of Section 4 as *flattening* to avoid confusion with polynomial reduction) to obtain  $\mathbf{c_{k,l}}$ . This can be visualized by considering an analogous operation in a hypothetical 1/8-size AMX unit, operating on 4-coefficient slices starting at the constant coefficient:

We then flatten the parallelogram by sum-reduction of columns and multiplication by the corresponding power of x to obtain

$$a_3b_3x^6 + (a_2b_3 + a_3b_2)x^5 + \ldots + (a_0b_1 + a_1b_0)x + a_0b_0.$$

We now turn to the implementation of these operations on AMX. Outer products are easily realized by loading  $a_k$  and  $b_l$  to one of the 8 available X or Y registers, and executing the matrix-mode mac16 instruction. By default, these instructions accumulate with the existing values in the output Z registers, although mac16 allows skipping Z to realize multiplication without accumulation. The result occupies half of the Z register file, either the odd or even rows of Z; we assume the latter for the sake of example.

In order to realize shifts and flattenings, we first initialize the two ends of a 3-register-wide slice of X (say  $X_0$  and  $X_2$ ) as well as Z[1], the first odd row of Z, with zero values. For each even row of Z except the first, we use the <code>extrh</code> instruction to extract it to the remaining X register of the slice, i.e.  $X_1$  in this example. We can now use AMX's register addressing capabilities, in particular the ability to choose any 64-byte slice of the full 512-byte X register, to select slices containing the appropriate number of zero 16-bit values to realize the desired shifting. These slices are used as input to a pair of <code>vecint</code> or vector-mode <code>mac16</code> instructions, performing additions only, in order to accumulate the least significant coefficients to Z[0], and the most significant coefficients to Z[1]. See Figure 3 for an illustration of this operation, again on a hypothetical 1/8-size AMX unit, performing the complete small multiplication example shown previously.

Figure 3: Full multiplication process of 4-coefficient polynomial slices on a hypothetical 1/8-size AMX unit. The sequence of operations starts from the leftmost state of the Z registers (result of the outer product operation) and follows the arrows, representing different states of Z and the relevant part of X. Thick arrows indicate an extrh operation of the thick-bordered row of Z to X, while dotted arrows indicate an accumulation of each dotted slice of X with a corresponding row (0 or 1) of the target Z registers.

Performance is further improved by working on pairs of even rows of Z, extracting one to X and the other to Y. As discussed in Section 3.3, a single vecint can accumulate slices of both X and Y registers to the desired Z row. Microbenchmarks indicate that vecint, on its own, achieves twice the arithmetic throughput of addition with X or Y alone; however, this improvement is not fully realized as there appears to be contention with resources used to execute extrh, and moreover, microbenchmarks suggest there is a penalty for unaligned accesses to the X and Y registers, as required to shift the input operands.

We formalize the description above in the form of an algorithm to multiply 32-coefficient slices of input polynomials. It is displayed as Algorithm 4.1.

**Algorithm 4.1** PolyMul $32 \times 32(\mathbf{c_{k,l}}, \mathbf{a_k}, \mathbf{b_j})$ : modulo- $2^{16}$  multiplication of two 32-coefficient polynomials using AMX.

```

Input: \mathbf{a_k}, \mathbf{b_l} (arrays of 32-coefficient slices of \mathbf{a} and \mathbf{b})

Output: \mathbf{c_{k,l}} (array of 63 coefficients of c_{\mathbf{k},\mathbf{l}}(x) = a_{\mathbf{k}}(x) \times b_{\mathbf{l}}(x))

Notes: since AMX stores 64 bytes (in this case, 32 coefficients of 16 bits each) at a time,

output array must be allocated with enough space for 64 coefficients

1: X_0, X_2, Y_0, Y_2 \leftarrow ldx([0\ 0\ \dots\ 0])

▷ load zeros to all indicated registers

2: X_1, Y_1 \leftarrow ldx(a_k), ldy(b_l)

3: \mathbf{Z}[0:2:62] \leftarrow \mathtt{mac16}(\mathbf{Y}_1^\mathsf{T}\mathbf{X}_1)

4: X_1 \leftarrow \text{extrh}(Z[2])

5: Z[0] \leftarrow vecint(Z[0] + X[31:62])

6: Z[1] \leftarrow mac16(X[63:94])

⊳ both Y and Z skipped; just a copy from X to Z

7: for i \in \{2, 4, 6, \dots, 30\} do

X_1, Y_1 \leftarrow \text{extrh}(Z[2i]), \text{extrh}(Z[2(i+1)])

Z[0] \leftarrow \mathtt{vecint}(Z[0] + X[32 - i : 63 - i] + Y[31 - i : 62 - i])

9:

Z[1] \leftarrow \text{vecint}(Z[1] + X[64 - i: 95 - i] + Y[63 - i: 94 - i])

\textbf{11:} \ \mathbf{c_{k,l}}[0:31], \ \mathbf{c_{k,l}}[32:63] \leftarrow \mathtt{stz}(\mathtt{Z}[0]), \ \mathtt{stz}(\mathtt{Z}[1])

```

#### 4.2 Polynomial multiplication by product-scanning of basic blocks

We turn to the issue of realizing a full multiplication of n-coefficient inputs. Since NTRU requires n to be prime, and the basic block of Section 4.1 works on 32-coefficient slices, we work around this issue by zero-padding input polynomials to  $n' = 32 \lceil n/32 \rceil$  coefficients.

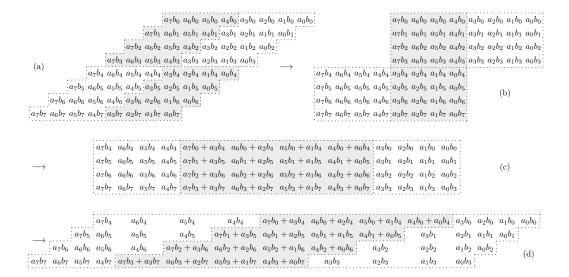

In principle, we could apply Algorithm 4.1 to each slice and accumulate results using vector instructions to realize a full-size multiplication. However, we propose a different architecture, based on blockwise product scanning with lazy sum-reduction, to increase the balance of faster matrix (outer product) to slower vector (extraction/addition) operations. We again illustrate with a small example for a hypothetical 1/8-size AMX unit, multiplying 8-coefficient input polynomials split into 4-coefficient slices as in Section 4.1.

The parallelogram of Figure 4 consists of 4 outer products:  $\mathbf{b}_{\mathbf{0}}^{\mathsf{T}}\mathbf{a}_{\mathbf{0}}$ ,  $\mathbf{b}_{\mathbf{1}}^{\mathsf{T}}\mathbf{a}_{\mathbf{0}}$  and  $\mathbf{b}_{\mathbf{1}}^{\mathsf{T}}\mathbf{a}_{\mathbf{1}}$ . It is seen in Figure 4(b) that  $\mathbf{b}_{\mathbf{1}}^{\mathsf{T}}\mathbf{a}_{\mathbf{0}}$  and  $\mathbf{b}_{\mathbf{0}}^{\mathsf{T}}\mathbf{a}_{\mathbf{1}}$  are aligned columnwise and can be accumulated (by matrix addition) prior to shifting and flattening; that is, shifting and flattening are performed lazily. In general, outer products of the form  $\mathbf{b}_{\mathbf{j}}^{\mathsf{T}}\mathbf{a}_{\mathbf{i}}$  and  $\mathbf{b}_{\mathbf{l}}^{\mathsf{T}}\mathbf{a}_{\mathbf{k}}$  are aligned, and can be accumulated, if i+j=k+l. Note that matrix addition does not need to be performed explicitly in AMX, as the outer product instructions accumulate with the existing contents of the Z registers at no extra cost. The accumulation procedure is shown as Algorithm 4.2, a subroutine of our polynomial multiplication algorithm given later.

Algorithm 4.2 ACCUMULATEOUTERPRODUCTS( $\mathbf{a}, \mathbf{b}, j, r$ ): accumulate outer products  $\mathbf{b}_{\mathbf{l}}^{\mathsf{T}} \mathbf{a}_{\mathbf{k}}$  such that k+l=j to  $\mathsf{Z}[r:2:62+r]$ , where r=0 or 1.

```

1: X_1, Y_1 \leftarrow \text{ldx}(\mathbf{a}[32j:32j+31]), \text{ldy}(\mathbf{b}[0:31])

2: \mathbf{Z}[r:2:62+r] \leftarrow \text{mac16}(\mathbf{Y}_1^\mathsf{T}\mathbf{X}_1)

3: \mathbf{for}\ 1 \leq l \leq j\ \mathbf{do}

4: k \leftarrow j - l \triangleright \text{Thus: } k+l=j

5: \mathbf{X}_1, \mathbf{Y}_1 \leftarrow \text{ldx}(\mathbf{a}[32k:32k+31]), \text{ldy}(\mathbf{b}[32l:32l+31])

6: \mathbf{Z}[r:2:62+r] \leftarrow \text{mac16}(\mathbf{Z}[r:2:62+r] + \mathbf{Y}_1^\mathsf{T}\mathbf{X}_1)

```

We now consider a full-size AMX unit and realistic polynomial sizes, say n' coefficients. The naïve approach suggested at the beginning of this section would call for  $(n'/32)^2 = O(n^2)$  applications of Algorithm 4.1, that is  $O(n^2)$  outer products and shifts/flattenings, plus extra operations to combine the results to obtain the desired polynomial multiplication

Figure 4: Transformations of the multiplication parallelogram for 8-coefficient polynomials for efficient implementation on a hypothetical 1/8-size AMX unit. Dotted lines enclose each outer product of 4-coefficient slices. Starting from the regular parallelogram (a), the i-th row is shifted right by  $i \mod 4$  positions (i.e. the reverse of the shifting step of Figure 3) to obtain (b), revealing how two outer products are aligned. In (c), these two outer products are summed prior to left-shifting the i-th row by i positions in the last state shown, (d). The final result is obtained by flattening each column (not shown).

result. The advantage of lazy shifting/flattening is clear from extrapolation of Figure 4: we see that it results in 2(n'/32) - 1 = O(n) matrices of dimension  $32 \times 32$  in the third step of the process (Figure 4(c)), which are shifted (Figure 4(d)) and flattened (not shown) to obtain the final polynomial multiplication result. While we still compute the same amount of outer products,  $(n'/32)^2 = O(n^2)$ , they are considerably cheaper than shifts and flattenings realized by AMX vector instructions, of which only O(n) are required.

Moving on to practical implementation issues, the Z register, where outer products accumulate, can only store two  $32 \times 32$  matrices, one in the even rows and another in the odd rows. Careful sequencing of shift and flattening operations is needed to avoid spills and reloads of Z's contents. Consider the flattened parallelogram in Figure 4(d), which is split into three sub-parallelograms, each corresponding to one of three matrices of Figure 4(c), formed from accumulating outer products; we denote them, from right to left, as  $M_0$ ,  $M_1$  and  $M_2$ , respectively. Working through the final flattening step (i.e. sum-reduction of columns, not shown in the figure), from the rightmost column towards the leftmost one, we see that the first columns (0 to 3) contain only elements from  $M_0$ . As we move left, columns 4 to 6 contain elements from  $M_0$  and  $M_1$ ; column 7 from  $M_1$  only; columns 8 to 10 from  $M_1$  and  $M_2$ ; and columns 11 to 14 from  $M_2$  only. A general pattern emerges: each column contains either elements from  $M_i$  only, or from  $M_i$  and  $M_{i+1}$ .

This suggests a structure for our polynomial multiplication algorithm, described in terms of full-size (n' coefficients) input polynomials. Formalizing the concept from the previous paragraph, we define  $M_j = \sum_{k+l=j} \mathbf{b}_l^\mathsf{T} \mathbf{a}_k$ ; the computation of each  $M_j$  is performed by Algorithm 4.2. We first compute  $M_0$  and  $M_1$ , storing them in the even and odd rows of  $\mathsf{Z}$ , respectively, as needed to perform shifts and flattenings to obtain the first 64 coefficients  $c_0, \ldots, c_{63}$  of c(x) = a(x)b(x), a procedure we formalize as Algorithm 4.3. We now compute  $M_2$  overwriting the even rows of  $\mathsf{Z}$ , and use both  $M_1$  (still available in the odd rows of  $\mathsf{Z}$ ) and  $M_2$  to obtain the next 32 coefficients of c(x), i.e.  $c_{64}, \ldots, c_{95}$ , by the procedure of

Algorithm 4.4. The pattern continues for j = 3, ..., 2(n/32) - 3 with  $M_j$  overwriting even or odd rows of Z, according to whether j is even or odd, respectively, and using  $M_{j-1}$  and  $M_j$  to compute  $c_{32j}, ..., c_{32j+31}$  using Algorithm 4.4. Finally, the case j = 2(n'/32) - 2 is handled by a third procedure, Algorithm 4.5, which computes the final batch of coefficients of c(x) from  $M_{j-1}$  and  $M_j$ . We formalize the complete procedure as Algorithm 4.6.

**Algorithm 4.3** FLATTENFIRSTTWOBLOCKS( $\mathbf{c}$ ): sum-reduction of columns from the two least significant multiplication sub-parallelograms.

```

Input: Z[0:2:62] = \mathbf{b_0^T} \mathbf{a_0} and Z[1:2:63] = \mathbf{b_0^T} \mathbf{a_1} + \mathbf{b_1^T} \mathbf{a_0} (implicitly)

Output: \mathbf{c}[0:63] (coefficients of x^0 through x^{63} of the polynomial multiplication result)

Notes: assumes X_0 = Y_0 = [0,0,\dots,0]

1: X_1, X_2 \leftarrow \text{extrh}(Z[2]), \text{ extrh}(Z[3])

2: Z[0], Z[1] \leftarrow \text{mac16}(Z[0] + X[31:62]), \text{ mac16}(Z[1] + X[63:94])

3: for i \in \{2,4,6,\dots,30\} do

4: X_1, X_2 \leftarrow \text{extrh}(Z[2i]), \text{ extrh}(Z[2i+1])

5: Y_1, Y_2 \leftarrow \text{extrh}(Z[2i+2]), \text{ extrh}(Z[2i+3])

6: Z[0] \leftarrow \text{vecint}(Z[0] + X[32-i:63-i] + Y[31-i:62-i])

7: Z[1] \leftarrow \text{vecint}(Z[1] + X[64-i:95-i] + Y[63-i:94-i])

8: \mathbf{c}[0:31], \mathbf{c}[32:63] \leftarrow \text{stz}(Z[0]), \text{ stz}(Z[1])

```

## **4.3** Integrated reduction modulo $x^n - 1$

The algorithms of Section 4.2, culminating in Algorithm 4.6, multiply polynomials of  $n \times n$  coefficients and return the full result with 2n-1 coefficients. In NTRU, the result must be reduced modulo  $x^n-1$ , a special form which allows efficient implementation as a post-processing step using e.g. NEON instructions, but also allowing reduction to be merged with multiplication in an integrated procedure, reducing the number of shifting/flattening operations by  $\approx 50\%$  compared to Algorithm 4.6, improving performance considerably.

To exemplify the integrated procedure, we again resort to a hypothetical 1/8-size AMX unit, now performing polynomial multiplication modulo  $x^{10}-1$ , which illustrates the main issues faced with larger polynomials on a full-size AMX unit. Although 10 coefficients are enough to represent polynomial inputs and outputs for this case, note that each block in this hypothetical 1/8-size AMX unit perfoms to a  $4 \times 4$  outer-product operation. Thus, we work with the next multiple of 4 coefficients, which is 12. We refer to Figure 5 as we work through the procedure, and assume input polynomials have  $a_i = b_j = 0$  for  $i, j \ge 10$ .

The results of all required outer product calculations are shown explicitly in Figure 5(a). The actual procedure accumulates  $4 \times 4$  outer product results of a given color (white, light gray or gray) into a single per-color  $4 \times 4$  matrix, as in Figure 4(c); for didactic reasons, we omit this step in the course of the explanation. Zero partial products are struck out in the figure; for some of these, this is a natural result of having  $a_i$  or  $b_j$  as input for  $i, j \geq 10$ , and for the others, we explicitly disable some columns during outer product computations.

Viewing Figure 5(a) as a block matrix of  $4 \times 4$  submatrices, note that submatrices in and above the secondary (block) diagonal are constructed identically to the example of Figure 4, as formalized in Algorithm 4.2. Notice the pattern followed by partial products  $a_ib_j$  in each row: those to its left and right are of the form  $a_{i+1}b_j$  and  $a_{i-1}b_j$ , respectively. The rightmost columns of each submatrix in the secondary (block) diagonal have i = 0, and the pattern continues to their right, with i - 1 taken modulo n (10 in the example). For each partial product  $a_ib_j$ , with k its row index modulo 4 and l its column index, as indicated to the left and below the matrix in Figure 5(a), we have  $k + l \equiv i + j \pmod{n}$ .

As an aside, note that submatrices in and above the secondary (block) diagonal are obtained from outer products of the form  $\mathbf{b}_{4l:4l+3}^\mathsf{T} \mathbf{a}_{4k:4k+3}$  (no relation to k and l in the

7:  $\mathbf{c}[32j : 32j + 31] \leftarrow \mathsf{stz}(\mathsf{Z}[r])$

**Algorithm 4.4** FLATTENMIDDLEBLOCK( $\mathbf{c}, j, r$ ): sum-reduction of columns from multiplication sub-parallelograms.

```

Input: j (index of current sub-parallelogram)

Input: r \in \{0,1\} (indicates relative order of even and odd rows of Z)

Output: \mathbf{c}[32j:32j+31] (coefficients of x^{32j} through x^{32j+31} of the polynomial multiplication result)

Notes: assumes that \mathbf{Z}[1-r:2:63-r] and \mathbf{Z}[r:2:62+r] contain the output of Algorithm 4.2 for sub-parallelogram indices j-1 and j, respectively

1: \mathbf{X}_1, \ \mathbf{X}_2 \leftarrow \text{extrh}(\mathbf{Z}[3-r]), \ \text{extrh}(\mathbf{Z}[2+r])

2: \mathbf{Z}[r] \leftarrow \text{mac16}(\mathbf{Z}[r] + \mathbf{X}[63:94])

3: \mathbf{for} \ i \in \{2,4,6,\ldots,30\} \ \mathbf{do}

4: \mathbf{X}_1, \ \mathbf{X}_2 \leftarrow \text{extrh}(\mathbf{Z}[2i+1-r]), \ \text{extrh}(\mathbf{Z}[2i+r])

5: \mathbf{Y}_1, \ \mathbf{Y}_2 \leftarrow \text{extrh}(\mathbf{Z}[2i+3-r]), \ \text{extrh}(\mathbf{Z}[2i+2+r])

6: \mathbf{Z}[r] \leftarrow \text{vecint}(\mathbf{Z}[r] + \mathbf{X}[64-i:95-i] + \mathbf{Y}[63-i:94-i])

```

**Algorithm 4.5** FLATTENLASTTWOBLOCKS( $\mathbf{c}, j$ ): sum-reduction of columns from the two most significant multiplication sub-parallelograms.

```

Input: j (index of current block)

Output: \mathbf{c}[32j:32j+62] (coefficients of x^{32j} through x^{32j+62} of c(x)=a(x)\times b(x))

Notes: assumes X_3 = Y_3 = [0, 0, \dots, 0], and that Z[1:2:63] and Z[0:2:62] contain the

output of Algorithm 4.2 for sub-parallelogram indices j-1 and j, respectively; one

extra coefficient written at \mathbf{c}[32j+63] since AMX writes 64 bytes at a time

1: \ \texttt{X}_1, \ \texttt{X}_2 \leftarrow \texttt{extrh}(\texttt{Z}[3]), \ \texttt{extrh}(\texttt{Z}[2])

2: Z[0], Z[1] \leftarrow mac16(Z[0] + X[63:94]), mac16(Z[1] + X[95:126])

3: for i \in \{2, 4, 6, \dots, 30\} do

X_2, X_1 \leftarrow \text{extrh}(Z[2i]), \text{extrh}(Z[2i+1])

4:

Y_2, Y_1 \leftarrow \text{extrh}(Z[2i+2]), \text{extrh}(Z[2i+3])

5:

Z[0] \leftarrow \mathtt{vecint}(Z[0] + X[32 - i : 63 - i] + Y[31 - i : 62 - i])

6:

Z[1] \leftarrow \text{vecint}(Z[1] + X[64 - i: 95 - i] + Y[63 - i: 94 - i])

8: \mathbf{c}[32j:32j+31], \ \mathbf{c}[32j+32:32j+63] \leftarrow \mathtt{stz}(\mathtt{Z}[0]), \ \mathtt{stz}(\mathtt{Z}[1])

```

**Algorithm 4.6** POLYMUL( $\mathbf{c}, \mathbf{a}, \mathbf{b}$ ): modulo- $2^{16}$  multiplication of two *n*-coefficient polynomials using AMX. Assumes *n* a multiple of 32; input must be zero-padded otherwise.

```

Input: \mathbf{a}, \mathbf{b} (arrays of n coefficients each of a(x) and b(x))

Output: \mathbf{c} (array of 2n-1 coefficients of c(x)=a(x)b(x))

Notes: since AMX stores 64 bytes (in this case, 32 coefficients of 16 bits each) at a time, output array must be allocated with 2n coefficients

1: \mathbf{X}_0, \mathbf{X}_3, \mathbf{Y}_0, \mathbf{Y}_3 \leftarrow \mathbf{1dx}([0,0,\dots,0]) \triangleright load zeros to all indicated registers

2: \mathbf{ACCUMULATEOUTERPRODUCTS}(\mathbf{a},\mathbf{b},0,0)

3: \mathbf{ACCUMULATEOUTERPRODUCTS}(\mathbf{a},\mathbf{b},1,1)

4: \mathbf{FLATTENFIRSTTWOBLOCKS}(\mathbf{c})

5: \mathbf{for}\ i=2\ \mathbf{to}\ 2(n/32)-3\ \mathbf{do}

6: \mathbf{ACCUMULATEOUTERPRODUCTS}(\mathbf{a},\mathbf{b},i,i\bmod 2)

7: \mathbf{FLATTENMIDDLEBLOCK}(\mathbf{c},i,i\bmod 2)

8: \mathbf{ACCUMULATEOUTERPRODUCTS}(\mathbf{a},\mathbf{b},2(n/32)-2,0)

9: \mathbf{FLATTENLASTTWOBLOCKS}(\mathbf{c},2(n/32)-2)

```

|       | 0     | $a_{11}b_{0}$         | $a_{10}b_{0}$                   | $a_9b_0$    | $a_8b_0$    | $a_7b_0$      | $a_6b_0$     | $a_5b_0$    | $a_4b_0$    | $a_3b_0$      | $a_2b_0$    | $a_1b_0$    | $a_0b_0$    |  |

|-------|-------|-----------------------|---------------------------------|-------------|-------------|---------------|--------------|-------------|-------------|---------------|-------------|-------------|-------------|--|

|       | 1     | $a_{\rm II}b_{\rm I}$ | $a_{10}b_{\rm T}$               | $a_9b_1$    | $a_8b_1$    | $a_7b_1$      | $a_6b_1$     | $a_5b_1$    | $a_4b_1$    | $a_3b_1$      | $a_2b_1$    | $a_1b_1$    | $a_0b_1$    |  |

|       | 2     | $a_{11}b_2$           | $a_{10}b_2$                     | $a_9b_2$    | $a_8b_2$    | $a_7b_2$      | $a_6b_2$     | $a_5b_2$    | $a_4b_2$    | $a_3b_2$      | $a_2b_2$    | $a_1b_2$    | $a_0b_2$    |  |

|       | 3     | $a_{11}b_3$           | $a_{10}b_3$                     | $a_9b_3$    | $a_8b_3$    | $a_7b_3$      | $a_6b_3$     | $a_5b_3$    | $a_4b_3$    | $a_3b_3$      | $a_2b_3$    | $a_1b_3$    | $a_0b_3$    |  |

|       | 0     | $a_7b_4$              | $a_6b_4$                        | $a_5b_4$    | $a_4b_4$    | $a_3b_4$      | $a_2b_4$     | $a_1b_4$    | $a_0b_4$    | $a_9b_4$      | $a_8b_4$    | $a_7b_4$    | $a_6b_4$    |  |

| (-)   | 1     | $a_{7}b_{5}$          | $a_6b_5$                        | $a_5b_5$    | $a_4b_5$    | $a_3b_5$      | $a_2b_5$     | $a_1b_5$    | $a_0b_5$    | $a_9b_5$      | $a_8b_5$    | $a_7b_5$    | $a_6b_5$    |  |

| (a)   | 2     | $a_{7}b_{6}$          | $a_6b_6$                        | $a_5b_6$    | $a_4b_6$    | $a_3b_6$      | $a_2b_6$     | $a_1b_6$    | $a_0b_6$    | $a_9b_6$      | $a_8b_6$    | $a_7b_6$    | $a_6b_6$    |  |

|       | 3     | $a_{7}b_{7}$          | $a_6b_7$                        | $a_5b_7$    | $a_4b_7$    | $a_3b_7$      | $a_2b_7$     | $a_1b_7$    | $a_0b_7$    | $a_9b_7$      | $a_8b_7$    | $a_7b_7$    | $a_6b_7$    |  |

|       | 0     | $a_3b_8$              | $\frac{a_{2}b_{8}}{a_{2}b_{8}}$ | $a_1b_8$    | $a_0b_8$    | $a_9b_8$      | $a_8b_8$     | $a_7b_8$    | $a_6b_8$    | $a_5b_8$      | $a_4b_8$    | $a_3b_8$    | $a_2b_8$    |  |

|       | 1     | $a_3b_9$              | $a_2b_9$                        | $a_1b_9$    | $a_0b_9$    | $a_9b_9$      | $a_8b_9$     | $a_7b_9$    | $a_6b_9$    | $a_5b_9$      | $a_4b_9$    | $a_3b_9$    | $a_2b_9$    |  |

|       | 2     | $a_3b_{10}$           | $a_2b_{10}$                     | $a_1b_{10}$ | $a_0b_{10}$ | $a_{9}b_{10}$ | $a_8b_{10}$  | $a_7b_{10}$ | $a_6b_{10}$ | $a_{5}b_{10}$ | $a_4b_{10}$ | $a_3b_{10}$ | $a_2b_{10}$ |  |

|       | 3     | $a_3b_{11}$           | $a_2b_{11}$                     | $a_1b_{11}$ | $a_0b_{11}$ | $a_9b_{11}$   | $a_8b_{11}$  | $a_7b_{11}$ | $a_6b_{11}$ | $a_5b_{11}$   | $a_4b_{11}$ | $a_3b_{11}$ | $a_2b_{11}$ |  |

| 1:    | 2     | 11                    | 10                              | 9           | 8           | 7             | 6            | 5           | 4           | 3             | 2           | 1           | 0           |  |

|       |       |                       |                                 | $a_9b_0$    | $a_8b_0$    | $a_7b_0$      | $a_6b_0$     | $a_5b_0$    | $a_4b_0$    | $a_3b_0$      | $a_2b_0$    | $a_1b_0$    | $a_0b_0$    |  |

|       |       |                       | $a_9b_1$                        | $a_8b_1$    | $a_7b_1$    | $a_6b_1$      | $a_5b_1$     | $a_4b_1$    | $a_3b_1$    | $a_2b_1$      | $a_1b_1$    | $a_0b_1$    |             |  |

|       |       | $a_{9}b_{2}$          | $a_8b_2$                        | $a_7b_2$    | $a_6b_2$    | $a_5b_2$      | $a_4b_2$     | $a_3b_2$    | $a_2b_2$    | $a_1b_2$      | $a_0b_2$    |             |             |  |

| $a_9$ | $b_3$ | $a_{8}b_{3}$          | $a_7b_3$                        | $a_6b_3$    | $a_5b_3$    | $a_4b_3$      | $a_3b_3$     | $a_2b_3$    | $a_1b_3$    | $a_0b_3$      |             |             |             |  |

| (ls)  |       |                       |                                 | $a_5b_4$    | $a_4b_4$    | $a_3b_4$      | $a_2b_4$     | $a_1b_4$    | $a_0b_4$    | $a_9b_4$      | $a_8b_4$    | $a_7b_4$    | $a_6b_4$    |  |

| (b)   |       |                       | $a_5b_5$                        | $a_4b_5$    | $a_3b_5$    | $a_2b_5$      | $a_1b_5$     | $a_0b_5$    | $a_9b_5$    | $a_8b_5$      | $a_7b_5$    | $a_6b_5$    |             |  |

|       |       | $a_{5}b_{6}$          | $a_4b_6$                        | $a_3b_6$    | $a_2b_6$    | $a_1b_6$      | $a_0b_6$     | $a_9b_6$    | $a_8b_6$    | $a_7b_6$      | $a_6b_6$    |             |             |  |

| $a_5$ | $b_7$ | $a_{4}b_{7}$          | $a_3b_7$                        | $a_2b_7$    | $a_1b_7$    | $a_0b_7$      | $a_{9}b_{7}$ | $a_8b_7$    | $a_7b_7$    | $a_6b_7$      |             |             |             |  |

|       |       |                       |                                 | $a_1b_8$    | $a_0b_8$    | $a_9b_8$      | $a_8b_8$     | $a_7b_8$    | $a_6b_8$    | $a_5b_8$      | $a_4b_8$    | $a_3b_8$    | $a_2b_8$    |  |

|       |       |                       | $a_1b_9$                        | $a_0b_9$    | $a_9b_9$    | $a_8b_9$      | $a_7b_9$     | $a_6b_9$    | $a_5b_9$    | $a_4b_9$      | $a_3b_9$    | $a_2b_9$    |             |  |

| 1:    | 2     | 11                    | 10                              | 9           | 8           | 7             | 6            | 5           | 4           | 3             | 2           | 1           | 0           |  |

|       |       |                       |                                 | $a_9b_0$    | $a_8b_0$    | $a_7b_0$      | $a_6b_0$     | $a_5b_0$    | $a_4b_0$    | $a_3b_0$      | $a_2b_0$    | $a_1b_0$    | $a_0b_0$    |  |

|       |       |                       |                                 | $a_8b_1$    | $a_7b_1$    | $a_6b_1$      | $a_5b_1$     | $a_4b_1$    | $a_3b_1$    | $a_2b_1$      | $a_1b_1$    | $a_0b_1$    | $a_9b_1$    |  |

|       |       |                       |                                 | $a_7b_2$    | $a_6b_2$    | $a_5b_2$      | $a_4b_2$     | $a_3b_2$    | $a_2b_2$    | $a_1b_2$      | $a_0b_2$    | $a_9b_2$    | $a_8b_2$    |  |

|       |       |                       |                                 | $a_6b_3$    | $a_5b_3$    | $a_4b_3$      | $a_3b_3$     | $a_2b_3$    | $a_1b_3$    | $a_0b_3$      | $a_9b_3$    | $a_8b_3$    | $a_7b_3$    |  |

|       |       |                       |                                 | $a_5b_4$    | $a_4b_4$    | $a_3b_4$      | $a_2b_4$     | $a_1b_4$    | $a_0b_4$    | $a_9b_4$      | $a_8b_4$    | $a_7b_4$    | $a_6b_4$    |  |

| (c)   |       |                       |                                 | $a_4b_5$    | $a_3b_5$    | $a_2b_5$      | $a_1b_5$     | $a_0b_5$    | $a_9b_5$    | $a_8b_5$      | $a_7b_5$    | $a_6b_5$    | $a_5b_5$    |  |

| (0)   |       |                       |                                 | $a_3b_6$    | $a_2b_6$    | $a_1b_6$      | $a_0b_6$     | $a_9b_6$    | $a_8b_6$    | $a_7b_6$      | $a_6b_6$    | $a_5b_6$    | $a_4b_6$    |  |

|       |       |                       |                                 | $a_2b_7$    | $a_1b_7$    | $a_0b_7$      | $a_9b_7$     | $a_8b_7$    | $a_7b_7$    | $a_6b_7$      | $a_5b_7$    | $a_4b_7$    | $a_3b_7$    |  |

|       |       |                       |                                 | $a_1b_8$    | $a_0b_8$    | $a_9b_8$      | $a_8b_8$     | $a_7b_8$    | $a_6b_8$    | $a_5b_8$      | $a_4b_8$    | $a_3b_8$    | $a_2b_8$    |  |

|       |       |                       |                                 | $a_0b_9$    | $a_9b_9$    | $a_8b_9$      | $a_7b_9$     | $a_6b_9$    | $a_5b_9$    | $a_4b_9$      | $a_3b_9$    | $a_2b_9$    | $a_1b_9$    |  |

|       |       |                       |                                 |             |             |               |              |             |             |               |             |             |             |  |

**Figure 5:** Sequence of operations to implement integrated polynomial multiplication and reduction of 12-coefficient polynomials modulo  $x^{10} - 1$  on a hypothetical 1/8-size AMX unit. See text for a description of transformations from each subfigure to the next.

previous paragraph). On the other hand, submatrices underneath the secondary (block) diagonal are obtained from outer products  $\mathbf{b}_{4l:4l+3}^\mathsf{T} \mathbf{a}_{4k+2:4k+5}$ ; note how the coefficients of  $\mathbf{a}$  are "unaligned", i.e. the starting index is not a multiple of 4 (or 32 for a full-size AMX unit). The offset 2 in the example corresponds in general to  $n \mod 4$ , arising from the modulo  $x^n - 1$  reduction when n is not a multiple of 4 (or 32 for a full-size AMX unit).

We now present Algorithm 4.7, a counterpart of Algorithm 4.2 for the integrated polynomial multiplication and reduction procedure. It follows Algorithm 4.2 in accumulating outer products with matching columns (i.e. the submatrices of the same color in Figure 5(a)), a step which we recall was omitted from the example for ease of exposition.

We transform Figure 5(a) into Figure 5(b) by removing struck-out partial products and shifting each row of Figure 5(a) by their modulo-4 row index; note that indices i, j of partial products  $a_ib_j$  in each column precisely add (modulo 10) to the column index. Since we are working modulo  $x^{10} - 1$ , the result should only contain coefficients with indices from 0 to 9; we mark this boundary with a thick vertical line in the figure. However, there remain partial products in columns with index  $k \ge 10$ , i.e. to the left of this vertical line. By moving them to the column with index  $k' = k \mod 10$  in the same row, we arrive at Figure 5(c). In all cases, i + j remains congruent to the column index modulo 10.

It is instructive to compare the width of the parallelogram in Figure 4(c) and (d), which is 2n-1 coefficients, with that of Figure 5(c), which is n coefficients. This validates the

**Algorithm 4.7** ACCUMULATEOUTERPRODUCTSREDUCTION( $\mathbf{a}, \mathbf{b}, j, r, n, m$ ): accumulate outer products for polynomial multiplication with reduction modulo  $x^n-1$  to  $\mathbf{Z}[r:2:62+r]$ , where r=0 or 1; only the first  $m\leq 32$  columns are computed.

```

\begin{array}{lll} 1: \ \mathbf{X}_1, \ \mathbf{Y}_1 \leftarrow \mathbf{1} \mathbf{dx} (\mathbf{a}[32j:32j+31]), \ \mathbf{1} \mathbf{dy} (\mathbf{b}[0:31]) \\ 2: \ \mathbf{Z}[r:2:62+r] \leftarrow \mathbf{mac16} (\mathbf{Y}_1^\mathsf{T} \mathbf{X}_1, \mathbf{columns} = 0:m-1) \\ 3: \ \mathbf{for} \ 1 \leq l \leq j \ \mathbf{do} \\ 4: \quad k \leftarrow j-l & \rhd \mathbf{Thus}: \ k+l=j \\ 5: \quad \mathbf{X}_1, \ \mathbf{Y}_1 \leftarrow \mathbf{1} \mathbf{dx} (\mathbf{a}[32k:32k+31]), \ \mathbf{1} \mathbf{dy} (\mathbf{b}[32l:32l+31]) \\ 6: \quad \mathbf{Z}[r:2:62+r] \leftarrow \mathbf{mac16} (\mathbf{Z}[r:2:62+r] + \mathbf{Y}_1^\mathsf{T} \mathbf{X}_1, \mathbf{columns} = 0:m-1) \\ 7: \ \mathbf{for} \ j < l \leq \lfloor (n-1)/32 \rfloor \ \mathbf{do} \\ 8: \quad \mathbf{X}_1, \ \mathbf{Y}_1 \leftarrow \mathbf{1} \mathbf{dx} (\mathbf{a}[n-32(l-1):n-32(l-1)+31]), \ \mathbf{1} \mathbf{dy} (\mathbf{b}[32l:32l+31]) \\ 9: \quad \mathbf{Z}[r:2:62+r] \leftarrow \mathbf{mac16} (\mathbf{Z}[r:2:62+r] + \mathbf{Y}_1^\mathsf{T} \mathbf{X}_1, \mathbf{columns} = 0:m-1) \\ \end{array}

```

earlier claim that the number of sum-reductions (shifts and flattenings) is cut approximately in half by integrating polynomial multiplication and reduction.

Algorithms 4.3 and 4.4 can be used to perform shifts and flattenings for columns 0 to 9 of the parallelogram; in this particular example, Algorithm 4.3 would be applied to the first two blocks (columns 0 to 3 and 4 to 7 of Figure 5(b)), and Algorithm 4.4 to columns 8 and 9 (although this would undesirably also include columns 10 and 11 in the result, in practice this issue can be worked around). Handling columns 10, 11 and 12, i.e. merging them with the main matrix as in Figure 5(c) (in this particular case with columns 0, 1 and 2, respectively) requires a new procedure, which we formalize as Algorithm 4.8.

Finally, we combine the new algorithms presented in this section, as well as those reused from Section 4.2, to obtain a procedure for integrated polynomial multiplication and reduction, formalized as Algorithm 4.9. This is the algorithm we use for the main polynomial multiplication routine in NTRU, i.e. the poly\_Rq\_mul() function.

**Algorithm 4.8** MERGEFIRSTANDLASTBLOCKS( $\mathbf{c}, j, r, n$ ): sum-reduction of columns from the two most significant multiplication sub-parallelograms.

```

Input: j (index of current sub-parallelogram)

Input: r \in \{0,1\} (indicates relative order of even and odd rows of Z)

Input: n (reduction polynomial is x^n - 1)

Output: c[0:31] (coefficients of x^0 through x^{31} of the polynomial multiplication result)

Notes: assumes that Z[1-r:2:63-r] and Z[r:2:62+r] contain the output of

Algorithm 4.7 for sub-parallelogram indices j-1 and j, respectively

1: \delta \leftarrow (-n) \mod 32

2: Z[r] \leftarrow ldz(c[0:31])

3: X_2 \leftarrow \text{extrh}(Z[3-r])

4: Z[r] \leftarrow mac16(Z[r] + X[95 - \delta : 126 - \delta])

5: i \leftarrow 1

6: while i < 31 - \delta \, \, \mathbf{do}

X_2, Y_2 \leftarrow \text{extrh}(Z[2i+3-r]), \text{ extrh}(Z[2i+5-r])

\mathbf{Z}[r] \leftarrow \mathtt{vecint}(\mathbf{Z}[r] + \mathbf{X}[95 - \delta - i : 126 - \delta - i] + \mathbf{Y}[94 - \delta - i : 125 - \delta - i])

i \leftarrow i + 2

10: while i < 31 do

X_1, X_2 \leftarrow \text{extrh}(Z[2i+2+r]), \text{ extrh}(Z[2i+3-r])

\mathbf{Y}_1, \ \mathbf{Y}_2 \leftarrow \mathtt{extrh}(\mathbf{Z}[2i+4+r]), \ \mathtt{extrh}(\mathbf{Z}[2i+5-r])

12:

\mathbf{Z}[r] \leftarrow \mathtt{vecint}(\mathbf{Z}[r] + \mathbf{X}[95 - \delta - i : 126 - \delta - i] + \mathbf{Y}[94 - \delta - i : 125 - \delta - i])

13:

i \leftarrow i + 2

14:

15: \mathbf{c}[0:31] \leftarrow \mathtt{stz}(\mathtt{Z}[r])

```

**Algorithm 4.9** POLYMODMUL( $\mathbf{c}, \mathbf{a}, \mathbf{b}, n$ ): modulo- $2^{16}$  multiplication of two n-coefficient polynomials using AMX, reduced modulo  $x^n - 1$ .

```

Input: a, b (arrays of n coefficients each of a(x) and b(x))

Output: c (array of n coefficients of c(x) = a(x)b(x))

Notes: since AMX stores 64 bytes (in this case, 32 coefficients of 16 bits each) at a time,

output array must be allocated with 32\lceil n/32\rceil coefficients

1: n' \leftarrow |(n-1)/32|

2: X_0, X_3, Y_0, Y_3 \leftarrow ldx([0, 0, ..., 0])

▷ load zeros to all indicated registers

3: ACCUMULATEOUTERPRODUCTSREDUCTION(\mathbf{a}, \mathbf{b}, 0, 0, n, 32)

4: ACCUMULATEOUTERPRODUCTSREDUCTION(\mathbf{a}, \mathbf{b}, 1, 1, n, 32)

5: FLATTENFIRSTTWOBLOCKS(c)

for i = 2 to n' - 2 do

7:

ACCUMULATEOUTERPRODUCTSREDUCTION(\mathbf{a}, \mathbf{b}, i, i \mod 2, n, 32)

FLATTENMIDDLEBLOCK(\mathbf{c}, i, i \mod 2)

9: ACCUMULATEOUTERPRODUCTSREDUCTION(\mathbf{a}, \mathbf{b}, n' - 1, (n' - 1) \mod 2, n, n \mod 32)

10: FLATTENMIDDLEBLOCK(\mathbf{c}, n'-1, (n'-1) \bmod 2)

11: MERGEFIRSTANDLASTBLOCKS(\mathbf{c}, n' - 1, (n' - 1) \mod 2, n)

```

## 4.4 Working around memory access slowdowns

An initial implementation of polynomial multiplication modulo  $x^n - 1$ , applying all optimizations mentioned in Sections 4.2 and 4.3, outperforms the analogous routines from the implementations of [NG21] and [CCHY23] when benchmarked in isolation. However, improvements were modest for the operations of the full scheme (key generation, encapsulation and decapsulation), with [CCHY23] still outperforming our NTRU implementation.

Handley [Han23] claims that load/store queues track AMX memory accesses at a granularity of memory pages, marking them as "interesting" for AMX, and concurrent CPU and AMX accesses to the same page will block. Inspection of the kem.c, owcpa.c and poly.c source files shows that polynomial coefficient arrays are allocated on the stack, next to other variables used exclusively by CPU code, and thus stored in adjacent addresses in memory, very likely in the same memory page. We conjectured this was the root cause of our performance issues, we switched to allocating one polynomial per memory page using the mmap() function. Benchmarks using this new memory allocation scheme led to our implementation outperforming those of [NG21] and [CCHY23] in all tested scenarios.

Johnson [Joh22b] suggests using CPU prefetch instructions, which (unlike AMX instructions) are executed out of order by the CPU, triggering memory accesses in advance of AMX load/store instructions and reducing latency. However, we saw no performance improvements from this. It appears this suggestion is targeted towards typical AMX applications with working sets too large to fit CPU caches, which is not the case for NTRU.

# 5 Experimental results

We benchmark our implementation on a 2020 Apple MacBook Air laptop with the Apple M1 SoC with nominal P-core clock speed of 3200 MHz, and a 2023 Apple MacBook Pro laptop with the Apple M3 Max SoC with nominal P-core clock speed of 4064 MHz. All implementations are compiled with Apple clang 15 using the -03 optimization flag.

We compare our implementation to the state-of-the-art ones of [CCHY23], which implements only HPS2048677 and HRSS701 (and holds the current speed record for these sets), and [NG21], which implements all parameter sets. We backport optimized polynomial inversion and constant-time sorting routines from [CCHY23] to [NG21], seeking

to highlight differences in polynomial multiplication performance only; we include this modified implementation in our GitHub repository. We also optimize NIST's AES-256 CTR-DRBG randombytes() function with AES instructions from ARMv8-A's Cryptographic Extensions, using software tests to verify that outputs are bit-identical to the NIST version.

All of these optimizations (polynomial inversion, constant-time sorting and random number generation) are also applied to our AMX implementation. We ensure Known Answer Tests for all implementations match those provided in the NTRU reference code.

Recall from Section 4.4 that our implementation uses a specific memory allocation strategy for arrays of polynomial coefficients. To ensure a fair comparison, we create stack and mmap() allocation variants for every implementation and report performance figures for both, computing speedups by comparing the fastest strategy for each implementation.

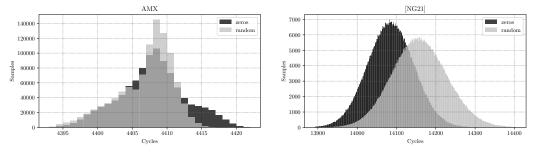

Performance measurements use the same cycle-counting harness found in [NG21] and [CCHY23]. To reduce timing variabilities, each routine is run for 1,024 times in a loop, measuring the cycle counts of each run individually, and the median value is reported.

#### 5.1 Performance measurements

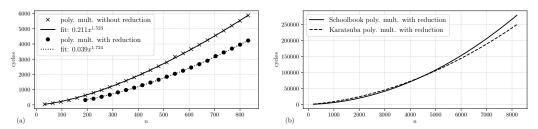

We present NTRU performance results in Table 4. We omit the tc variant of HPS2048677 included in [CCHY23], as tmvp always outperforms it.

**Table 4:** Cycle counts for NTRU KEM operations and polynomial multiplication. Speedups computed as a ratio of the best cycle counts for previous implementations and our implementation (in both cases, across different memory allocations types).

| Par. | Mem.   |                                  | Operation |        |       |       |       |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

|------|--------|----------------------------------|-----------|--------|-------|-------|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| set  | alloc. | $\mathbf{Work}$                  | Key       | gen.   | Enc   | aps.  | Dec   | aps.  | Poly. mult.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

| BCC  | anoc.  |                                  | M1        | M3     | M1    | M3    | M1    | M3    | M1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | M3    |

|      |        | [NG21]                           | 218938    | 215086 | 16314 | 15695 | 29876 | 28667 | 6352                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6351  |

|      | mmap   | Ours                             | 170334    | 163936 | 12620 | 11885 | 18976 | 17300 | 2281                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2009  |

| 509  | stack  | [NG21]                           | 218436    | 214434 | 16287 | 15805 | 29870 | 28780 | 6373                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6349  |

|      | Stack  | Ours                             | 181787    | 170648 | 19628 | 14327 | 26609 | 23810 | 3675                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3229  |

|      | Spee   | $\mathbf{dup}(x)$                | 1.28      | 1.31   | 1.29  | 1.32  | 1.57  | 1.66  | 2.78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3.16  |

|      |        | [NG21]                           | 364048    | 348559 | 23738 | 22591 | 44977 | 42912 | 10028                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10347 |

|      | mmap   | [CCHY23]                         | 307460    | 296025 | 19272 | 18586 | 31718 | 30620 | 5472                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7080  |

|      |        | Ours                             | 283023    | 266334 | 17324 | 16205 | 26443 | 24004 | M1         M3           6352         6351           2281         2009           6373         6349           3675         3229           2.78         3.16           10028         10347           5472         7080           3781         3715           9998         10308           5523         6056           4299         4303           1.63         1.81           13912         13911           4789         4414           13859         13911           5386         7100           2.89         3.15           12870         12603           6911         6860           3708         3367           12529         12300           6918         6858           5431         5876 |       |